#### **MAX25405**

## IR Gesture Sensor with Lens for Automotive Applications

#### **General Description**

The MAX25405 is a low-cost, data-acquisition system for gesture and proximity sensing. Detection distance is improved by integrating a complete optical system consisting of lens, aperture, visible light filter, and a 6x10 photodetector array. The MAX25405 recognizes the following independent gestures:

- Hand swipe gestures (left, right, up, down, wave)

- Air click

- Flicks

- Finger and hand rotation (clockwise and counter clockwise)

- Multizone proximity detection

- Linger to click

The proximity, hand detection, and gesture recognition functions of the MAX25405 operate by detecting the light reflected from the controlled IR-LED light source with an integrated 6x10-element optical sensor array. The MAX25405 can detect these gestures even when exposed to bright ambient light. A low-power, low-cost CPU, such as the MAX32630, is required to process the data from the sensor.

This discrete light source is created externally with one or more FETs driven directly from the MA25405. The light source's PWM duty cycle is programmable from 1/16 to 16/16. The LEDs are pulsed on one or more times in a programmable sequence repeated for every sample.

For flexibility, the MAX25405 supports two different serial communication protocols: I<sup>2</sup>C (400kHz) and SPI (6MHz).

The MAX25405 is available in a 4mm x 4mm, 20-pin, optical QFN package.

### **Applications**

- Central Information Display Control

- Rear-Seat Entertainment Systems

- Door, Moon Roof, and Trunk Control

- Mechanical Switch Replacement

- Occupant Detection

#### **Benefits and Features**

- Low-Cost, Flexible Gesture-Sensing Solution for Automotive Applications

- Low-Power, Low-Cost External CPU Processes Sensor Output

- Supports Swipe, Rotation, and Proximity Gestures

- Highly Integrated

- · Integrated Lens, Aperture, and Filter

- 60-Pixel IR Photodiode Array

- · Integrated LED Driver

- 400kHz I<sup>2</sup>C and 6MHz SPI Serial Interfaces

- Operates in 120k Lux Ambient Light

- AEC-Q100 Qualified

- -40°C to +85°C Operation

- MSL1

- Ultra-Low-Power Operation

- 1mA at 3.3V

- Compact 4mm x 4mm x 1.35mm, 20-Pin, Side-Wettable QFN Package

Ordering Information appears at the end of the data sheet.

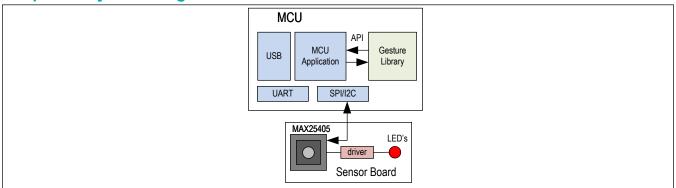

### **Simplified System Diagram**

### **TABLE OF CONTENTS**

| General Description                                     | 1  |

|---------------------------------------------------------|----|

| Applications                                            | 1  |

| Benefits and Features                                   | 1  |

| Simplified System Diagram                               | 2  |

| Absolute Maximum Ratings                                | 6  |

| Package Information                                     | 6  |

| 4mm x 4mm QFN                                           | 6  |

| Electrical Characteristics                              | 6  |

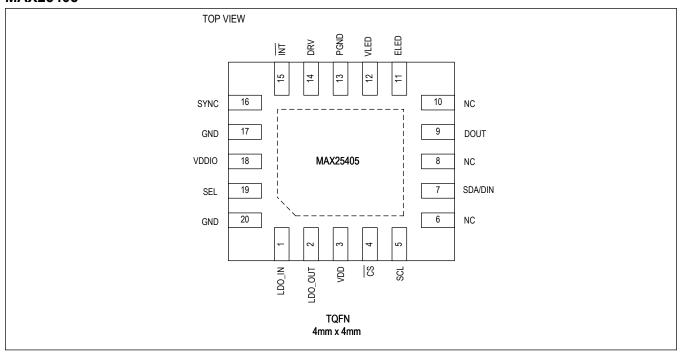

| Pin Configuration                                       |    |

| MAX25405                                                |    |

| Pin Description                                         | 9  |

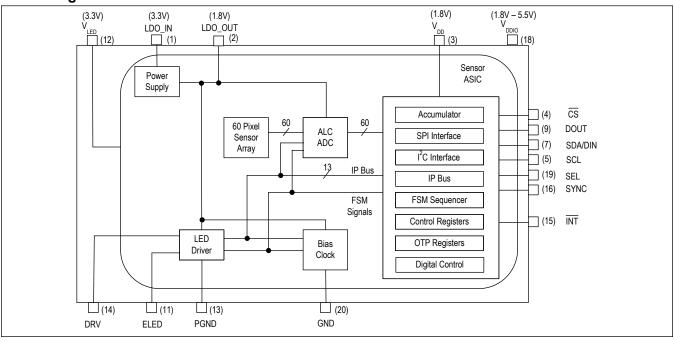

| Functional Diagrams                                     | 11 |

| Block Diagram                                           | 11 |

| Detailed Description                                    | 12 |

| Recommended Operating Conditions                        | 12 |

| Register Map                                            | 13 |

| MAX25405                                                | 13 |

| Register Details                                        | 16 |

| Applications Information                                | 29 |

| Principle of Operation                                  | 29 |

| Operation Mode                                          | 29 |

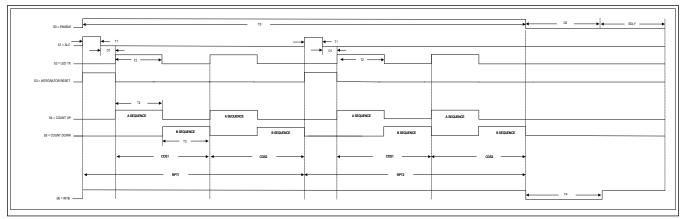

| CDS Mode 0                                              | 29 |

| CDS Mode 1                                              | 29 |

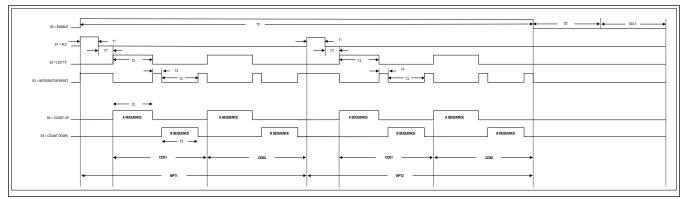

| MAX25405 Sample-Sequence Timing                         | 29 |

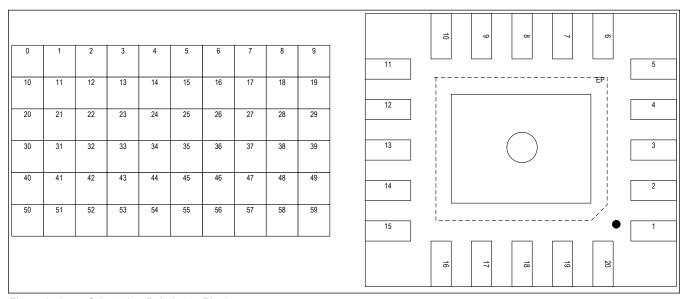

| Array Orientation                                       | 31 |

| I <sup>2</sup> C Serial Interface                       | 31 |

| Enabling I <sup>2</sup> C or SPI communications         | 31 |

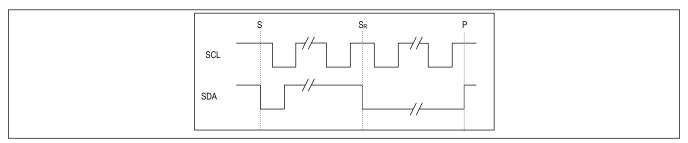

| START and STOP Conditions                               | 32 |

| Early STOP Conditions                                   | 32 |

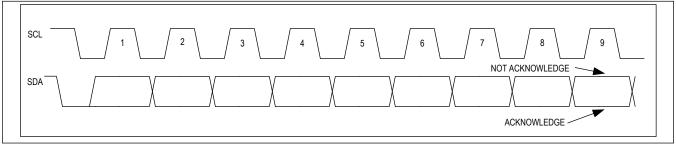

| Acknowledge                                             | 32 |

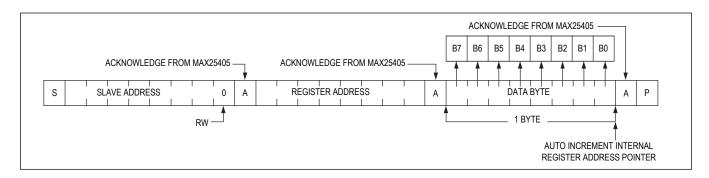

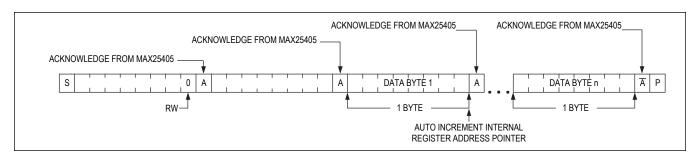

| Write Data Format                                       | 32 |

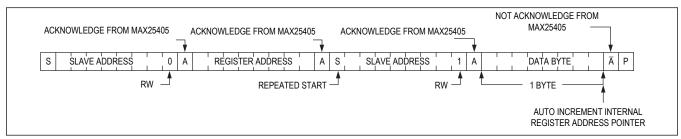

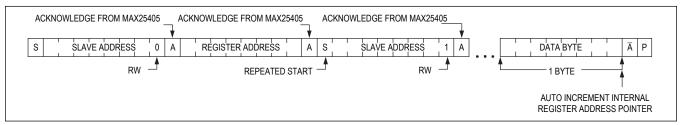

| Read Data Format                                        | 33 |

| SPI Interface                                           | 34 |

| Typical Application Circuits                            | 36 |

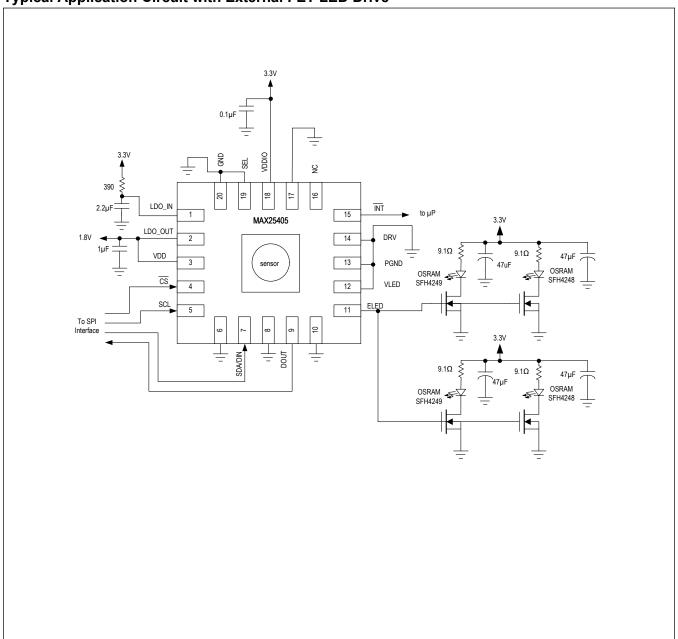

| Typical Application Circuit with External FET LED Drive | 36 |

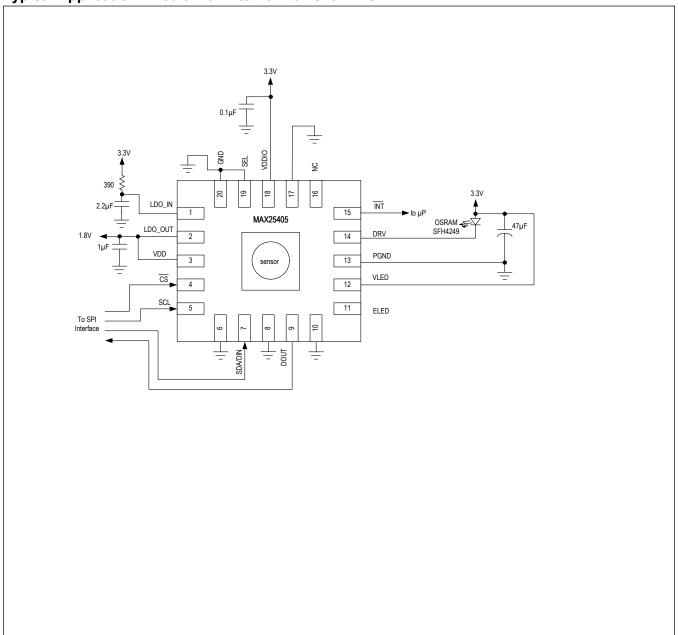

| Typical Application Circuit with Internal Current Drive | 37 |

| Ordering Information                                    | 38 |

| Revision History                                        | 39 |

### MAX25405

# IR Gesture Sensor with Lens for Automotive Applications

| LIST OF FIGURES                                        |    |

|--------------------------------------------------------|----|

| Figure 1. Timing Setting: NCDS = 2, NRPT = 2, CRST = 1 | 30 |

| Figure 2. Timing Setting: NCDS = 2, NRPT = 2, CRST = 0 | 30 |

| Figure 3. Array Orientation Relative to Pin 1          | 31 |

| Figure 4. START, REPEAT START, STOP Conditions         | 31 |

| Figure 5. ACKNOWLEDGE                                  | 32 |

| Figure 6. Reading 1 Byte of Indexed Data               | 34 |

| Figure 7. Reading N Bytes of Indexed Data              | 34 |

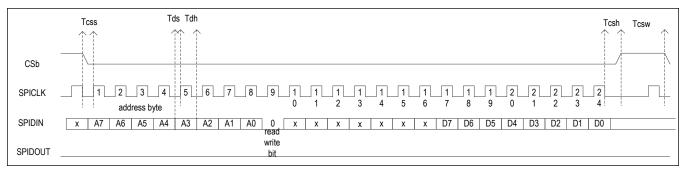

| Figure 8. SPI Write                                    | 35 |

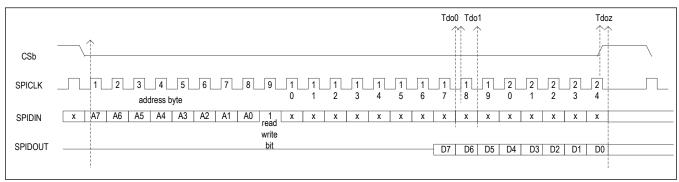

| Figure 9. SPI Read                                     | 35 |

### MAX25405

# IR Gesture Sensor with Lens for Automotive Applications

| LIST OF TABLES                            |    |

|-------------------------------------------|----|

| Table 1. Recommended Operating Conditions | 12 |

| Table 2. Sequence Timing Specification    | 30 |

| Table 3. I <sup>2</sup> C Slave Address   | 32 |

### **Absolute Maximum Ratings**

| LDO_IN to GND0.3V to +6.0V                                          | Short-Circuit Between DRV and GNDContinuous                              |

|---------------------------------------------------------------------|--------------------------------------------------------------------------|

| PGND to GND0.3V to +0.3V                                            | Continuous Power Dissipation (Multilayer Board) (T <sub>A</sub> = +70°C, |

| V <sub>LED</sub> , DRV to GND0.3V to 3.6V                           | derate 39.8 mW/°C above +70°C.) 0mW to 2191mW                            |

| LDO_OUT to GND0.3V to 2.2V                                          | Operating Temperature Range40°C to 85°C                                  |

| V <sub>DD</sub> to GND                                              | Operating Junction Temperature+125°C                                     |

| V <sub>DDIO</sub> to GND0.3V to 6V                                  | Storage Temperature Range40°C to +150°C                                  |

| CS, SCL, SDA, INT, SYNC, SEL to GND0.3V to V <sub>DDIO</sub> + 0.3V | Soldering Temperature (Reflow)260°C                                      |

| DOUT, ELED to GND0.3V to V <sub>DDIO</sub> + 0.3V                   | Lead Temperature (Soldering, 10s)300°C                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 4mm x 4mm QFN

| Package Code                           | Q2044Y+3         |

|----------------------------------------|------------------|

| Outline Number                         | <u>21-100562</u> |

| Land Pattern Number                    | 90-100083        |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 24.7 (C/W)       |

| Junction to Case $(\theta_{JC})$       | 4.7 (C/W)        |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(MAX25405 Typical Application Circuit,  $V_{DDIO}$  = 1.7V to 5.5V, LDO\_IN = 2.7V to 5.5V,  $V_{LED}$  = 2.7V to 3.6V, LDO\_OUT connected to  $V_{DD}$ .  $T_A$  = -40°C to +85°C. Typ values:  $V_{DDIO}$  = 3.3V, LDO\_IN = 3.3V,  $V_{LED}$  = 3.3V,  $V_{A}$  = +25°C. (Note 1) Default register settings (Note 3).)

| PARAMETER                      | SYMBOL              | CONDITIONS                                                               | MIN | TYP | MAX | UNITS |

|--------------------------------|---------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| DC Characteristics             |                     |                                                                          | •   |     |     |       |

| LDO_IN Supply Voltage          | LDO IN              | Note 2                                                                   | 2.7 | 3.3 | 5.5 | V     |

| LDO_OUT Supply<br>Voltage      | LDO_OUT             |                                                                          | 1.7 | 1.8 | 2.0 | V     |

| V <sub>DD</sub> Supply Voltage | V <sub>DD</sub>     | Note 2                                                                   | 1.7 | 1.8 | 2.0 | V     |

| Logic Supply Voltage           | V <sub>DDIO</sub>   | Note 2                                                                   | 1.7 | 3.3 | 5.5 | V     |

| LDO_IN Current                 | I <sub>LDO_IN</sub> | LDO_OUT connected to V <sub>DD</sub> .                                   |     | 8.0 |     | mA    |

| Shutdown Current               | I <sub>SHDN</sub>   | Register 0x02 Bit 7 = 1                                                  |     | 6   |     | μA    |

| Power-Up Time                  | T <sub>ON</sub>     | Note 4, $V_{LDO\_OUT} = V_{DD} = 1.7V$ , $V_{LDO\_IN} = V_{DDIO} = 2.7V$ |     | 6   |     | ms    |

### **Electrical Characteristics (continued)**

(MAX25405 Typical Application Circuit,  $V_{DDIO}$  = 1.7V to 5.5V, LDO\_IN = 2.7V to 5.5V,  $V_{LED}$  = 2.7V to 3.6V, LDO\_OUT connected to  $V_{DD}$ .  $T_A$  = -40°C to +85°C. Typ values:  $V_{DDIO}$  = 3.3V, LDO\_IN = 3.3V,  $V_{LED}$  = 3.3V,  $V_{A}$  = +25°C. (Note 1) Default register settings (Note 3).)

| PARAMETER                                             | SYMBOL           | CONDITIONS                               |                                                                                                                                                                                           | MIN                         | TYP   | MAX                        | UNITS  |  |

|-------------------------------------------------------|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|----------------------------|--------|--|

| IR LED DRIVER                                         |                  |                                          |                                                                                                                                                                                           |                             |       |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0000                                                                                                                                                                           |                             | 0     |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0001                                                                                                                                                                           |                             | 13.3  |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0010                                                                                                                                                                           |                             | 26.7  |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0011                                                                                                                                                                           |                             | 40    |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0100                                                                                                                                                                           |                             | 53.3  |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0101                                                                                                                                                                           |                             | 66.7  |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 0110                                                                                                                                                                           |                             | 80    |                            |        |  |

| LED Comment                                           |                  | DRV Voltage =                            | DRV[3:0] = 0111                                                                                                                                                                           |                             | 93.3  |                            | ]      |  |

| LED Current                                           | I <sub>LED</sub> | 1.8V                                     | DRV[3:0] = 1000                                                                                                                                                                           |                             | 106.7 |                            | mA     |  |

|                                                       |                  |                                          | DRV[3:0] = 1001                                                                                                                                                                           |                             | 120   |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1010                                                                                                                                                                           |                             | 133.3 |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1011                                                                                                                                                                           |                             | 146.7 |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1100                                                                                                                                                                           |                             | 160   |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1101                                                                                                                                                                           |                             | 173.3 |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1110                                                                                                                                                                           |                             | 186.7 |                            |        |  |

|                                                       |                  |                                          | DRV[3:0] = 1111                                                                                                                                                                           | 180                         | 200   | 220                        |        |  |

| LED Current Accuracy                                  |                  | I <sub>LED</sub> = 200mA, V <sub>D</sub> | <sub>RV</sub> = 0.8V to 3.6V                                                                                                                                                              | -10                         |       | 10                         | %      |  |

| IR RECEIVER CHARACT                                   | ERISTICS         |                                          |                                                                                                                                                                                           |                             |       |                            |        |  |

| Field of View                                         | FOV              |                                          |                                                                                                                                                                                           |                             | +/-30 |                            | Deg    |  |

| Optical Response                                      |                  | with irradiance = 3 scale = 8192 coun    | External 940nm collimated light source with irradiance = 37 µW/cm <sup>2</sup> . ADC full scale = 8192 counts. Optical response is the average response of the center four pixels. Note 5 |                             |       |                            | Counts |  |

| DIGITAL CHARACTERIS                                   | TICS             |                                          |                                                                                                                                                                                           |                             |       |                            |        |  |

| Output Low-Voltage<br>SDA, INT                        | $V_{OL}$         | I <sub>SINK</sub> = 6mA, oper            | n-drain outputs                                                                                                                                                                           |                             |       | 0.4                        | V      |  |

| Output Low-Voltage<br>DOUT, SYNC, ELED                | $V_{OL}$         | I <sub>SINK</sub> = 1mA, CMC             | OS outputs                                                                                                                                                                                |                             |       | 0.4                        | V      |  |

| Output High Voltage<br>DOUT, SYNC, ELED               | V <sub>OH</sub>  | I <sub>SOURCE</sub> = 1mA, (             | CMOS outputs                                                                                                                                                                              | 0.75 x<br>V <sub>DDIO</sub> |       |                            | V      |  |

| Leakage Current                                       |                  |                                          |                                                                                                                                                                                           |                             |       | 1.0                        | μA     |  |

| Input Low Voltage SDA/<br>DIN, SCL, SEL, CS,<br>SYNC  | V <sub>IL</sub>  |                                          |                                                                                                                                                                                           |                             |       | 0.3 x<br>V <sub>DDIO</sub> | V      |  |

| Input High Voltage SDA/<br>DIN, SCL, SEL, CS,<br>SYNC | V <sub>IH</sub>  |                                          |                                                                                                                                                                                           | 0.7 x<br>V <sub>DDIO</sub>  |       |                            | V      |  |

| Input Capacitance                                     |                  |                                          |                                                                                                                                                                                           |                             | 3     |                            | pF     |  |

### **Electrical Characteristics (continued)**

(MAX25405 Typical Application Circuit,  $V_{DDIO}$  = 1.7V to 5.5V, LDO\_IN = 2.7V to 5.5V,  $V_{LED}$  = 2.7V to 3.6V, LDO\_OUT connected to  $V_{DD}$ .  $T_A$  = -40°C to +85°C. Typ values:  $V_{DDIO}$  = 3.3V, LDO\_IN = 3.3V,  $V_{LED}$  = 3.3V,  $V_{A}$  = +25°C. (Note 1) Default register settings (Note 3).)

| PARAMETER                         | SYMBOL                                         | CONDITIONS      | MIN | TYP  | MAX  | UNITS |  |  |

|-----------------------------------|------------------------------------------------|-----------------|-----|------|------|-------|--|--|

| Internal Oscillator<br>Frequency  |                                                |                 | 2.5 | 2.56 | 2.62 | MHz   |  |  |

| I <sup>2</sup> C TIMING CHARACTE  | <sup>2</sup> C TIMING CHARACTERISTICS SDA, SCL |                 |     |      |      |       |  |  |

| I <sup>2</sup> C Clock Rate       | f <sub>SCL</sub>                               | Note 2          |     |      | 400  | kHz   |  |  |

| CCL Dulas Width                   | t <sub>LOW</sub>                               | Note 4          | 1.3 |      |      |       |  |  |

| SCL Pulse Width                   | t <sub>HIGH</sub>                              | Note 4          | 0.6 |      |      | - µs  |  |  |

| Data Hold Time                    | t <sub>HD</sub>                                | Note 4          | 0   |      | 900  | ns    |  |  |

| Data Setup Time                   | t <sub>SU</sub>                                | Note 4          | 100 |      |      | ns    |  |  |

| SPI TIMING CHARACTE               | RISTICS CS, SC                                 | L, DIN and DOUT | •   |      |      |       |  |  |

| SCL Frequency                     | f <sub>CLK</sub>                               | Note 2          |     |      | 6    | MHz   |  |  |

| SCL Pulse Width High              | t <sub>CH</sub>                                | Note 4          | 75  |      |      | ns    |  |  |

| SCL Pulse Width Low               | t <sub>CL</sub>                                | Note 4          | 75  |      |      | ns    |  |  |

| CS Fall to SCL Rise<br>Setup Time | tcss                                           | Note 4          | 25  |      |      | ns    |  |  |

| DIN to SCL Rise Setup<br>Time     | t <sub>DS</sub>                                | Note 4          | 20  |      |      | ns    |  |  |

| DIN to SCL Rise Hold<br>Time      | t <sub>DH</sub>                                | Note 4          | 10  |      |      | ns    |  |  |

| SCLK Fall to SD0<br>Transition    | t <sub>DOT</sub>                               |                 |     |      | 45   | ns    |  |  |

Note 1: Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Operation at  $T_A$  = -40°C is guaranteed by design and characterization.

Note 2: Condition of production test.

Note 3: Default register settings 0x01 = 0x04, 0x02 = 0x02, 0x03 = 0x24, 0x04 = 0x8C, 0x05 = 0x08, 0x06 = 0x0F, 0xC1 = 0x0A, 0xA5 = 0x88, 0xA6 = 0x88, 0xA7 = 0x88, 0xA8 = 0x88, 0xA9 = 0x88.

**Note 4:** Not production tested. Guaranteed by design and characterization.

Note 5: Count up A, eliminate B mode. Default register setting with the following exceptions: 0x04 = 0x8E, 0x05 = 0x00.

### **Pin Configuration**

#### MAX25405

### **Pin Description**

| PIN      | NAME            |                      | FUN                                                                                               | ICTION            | REF<br>SUPPLY       | TYPE       |

|----------|-----------------|----------------------|---------------------------------------------------------------------------------------------------|-------------------|---------------------|------------|

| 1        | LDO_IN          | 390Ω r               | ct to low-noise (V <sub>N</sub> < 150<br>esistor. Bypass with at le<br>pical Application Circuits | 3.3V              | Power               |            |

| 2        | LDO_OUT         | 1 ,                  | with a 1.0µF ceramic cas. Connect to V <sub>DD</sub> (Pin 3                                       | 1.8V              | Regulated<br>Output |            |

| 3        | V <sub>DD</sub> |                      | ct to LDO_OUT(Pin 2). V<br>circuitry.                                                             | 1.8V              | Power               |            |

| 4        | <del>CS</del>   | SPI Ch               | ip Select/I <sup>2</sup> C Address Se                                                             | V <sub>DDIO</sub> | Input               |            |

|          |                 | 0                    | 9E                                                                                                | Read Address 9F   | , DDIO              |            |

|          |                 | 1                    | A0                                                                                                | A1                |                     |            |

| 5        | SCL             | I <sup>2</sup> C Sei | rial Clock. For I <sup>2</sup> C operate                                                          | V <sub>DDIO</sub> | Input               |            |

| 6, 8, 10 | NC              | Connec               | ct to ground.                                                                                     |                   |                     | No Connect |

### **Pin Description (continued)**

| PIN    | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REF<br>SUPPLY     | TYPE               |

|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|

| 7      | SDA/DIN            | When the SEL pin is connected to $V_{DD}$ , Pin 7 becomes SDA for I <sup>2</sup> C communication. When the SEL pin is connected to GND, Pin 7 becomes DIN for SPI communication. For I <sup>2</sup> C operation, pull SDA up to $V_{DDIO}$ with 4.7k $\Omega$ .                                                                                                                                                                                                                            | V <sub>DDIO</sub> | Input/Output       |

| 9      | DOUT               | SPI Data Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>DDIO</sub> | Output             |

| 11     | ELED               | External LED CMOS Level Voltage PWM Drive Output. This pin drives the gate of either a p-channel FET or an n-channel FET. A resistor in series with the FET's drain limits the maximum pulse current supplied to the external LED. ELED output level for a logic low is 0V and for a logic high is V <sub>DDIO</sub> .  Note: When using a 1.8V V <sub>DDIO</sub> , a MOSFET with very low threshold voltage (V <sub>TH</sub> < 1V) should be used to ensure minimal R <sub>DS(ON)</sub> . | V <sub>DDIO</sub> | Output             |

| 12     | V <sub>LED</sub>   | ESD Protection for DRV Pin. Internal protection diodes clamp negative pulses to ground and positive pulses to the same supply used to supply the external LED. Bias $V_{LED}$ at 3.3V for typical applications. If the DRV pin is not used, it should be grounded to PGND.                                                                                                                                                                                                                 | $V_{LED}$         | Power              |

| 13     | PGND               | LED driver ground when DRV pin is used to drive LED                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   | GND                |

| 14     | DRV                | Direct LED Current Drive. When the MAX25405 is configured for direct LED drive, connect the DRV pin to the cathode of the LED. Connect the LED's anode to the LED supply to V <sub>LED</sub> for ESD protection. When external current drive is not used, DRV should be grounded along with the V <sub>LED</sub> pin.                                                                                                                                                                      | VLED              | Output             |

| 15     | ĪNT                | Interrupt Signal. At the end of a conversion sample sequence, the $\overline{\text{INT}}$ pin goes low. The host $\mu P$ can monitor this pin to determine when the ADC output registers are ready to be read. $\overline{\text{INT}}$ pin should be pulled up with a 4.7k $\Omega$ resistor to $V_{DDIO}$ . The status register 0x00 must be read once for the $\overline{\text{INT}}$ pin to become active.                                                                              | V <sub>DDIO</sub> | Input/Output       |

| 16     | SYNC               | External Synchronization Pin. Driving SYNC with a controlled logic signal prevents simultaneous flashing of LEDs in systems configured with two MAX25405 sensors.                                                                                                                                                                                                                                                                                                                          | $V_{DDIO}$        | Input/Output       |

| 18     | V <sub>DDIO</sub>  | Digital I/O Supply Pin. The digital I/O is compatible with 1.8V, 3.3V, or 5V CMOS logic levels.                                                                                                                                                                                                                                                                                                                                                                                            | $V_{\rm DDIO}$    | Power              |

| 19     | SEL                | Serial Interface Mode Select:  SEL = V <sub>DD</sub> : I <sup>2</sup> C  SEL = GND: SPI                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>DDIO</sub> | Input              |

| 17, 20 | GND                | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | GND                |

| EP     | Backside<br>Paddle | This pin must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   | Backside<br>Paddle |

### **Functional Diagrams**

#### **Block Diagram**

#### **Detailed Description**

The proximity, hand-detection, and gesture-recognition functions are achieved by detecting the light reflected from the controlled IR-LED light source while rejecting ambient light. An integrated 6x10-element optical sensor array performs the light measurements. This discrete light source is created externally with one or more FETs driven directly from the MA25405. The light source's PWM duty cycle is programmable from 1/16 to 16/16. The LEDs are pulsed on one or more times in a programmable sequence. This pulse sequence is repeated for every sample. A low-power, low-cost CPU, such as the MAX32630, is required to process the data from the sensor.

#### **Recommended Operating Conditions**

**Table 1. Recommended Operating Conditions**

| PARAMETER            | PIN NAME          | MIN | TYP | MAX | UNIT                                  |

|----------------------|-------------------|-----|-----|-----|---------------------------------------|

|                      | LDO_IN            | 2.7 | 3.3 | 5.5 |                                       |

| Supply Range         | $V_{DD}$          | 1.7 | 1.8 | 2   | V                                     |

|                      | V <sub>DDIO</sub> | 1.7 | 3.3 | 5.5 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Bias Range           | V <sub>LED</sub>  | 2.7 | 3.3 | 3.6 |                                       |

| Maximum Cumhi Naiga  | LDO_IN            |     | 150 |     | \/                                    |

| Maximum Supply Noise | $V_{DD}$          |     | 50  |     | mV <sub>P-P</sub>                     |

### **Register Map**

### MAX25405

| ADDRESS  | NAME                            | MSB  |                |            |       |           |             |             | LSB   |

|----------|---------------------------------|------|----------------|------------|-------|-----------|-------------|-------------|-------|

| STATUS   |                                 |      | •              | 1          | 1     | •         |             |             |       |

| 0x00     | INTERRUPT<br>STATUS[7:0]        | _    | _              | _          | PWRON | _         | EOCINT<br>S | _           | -     |

| CONFIGUR | ATION                           |      |                |            |       |           |             |             |       |

| 0x01     | MAIN<br>CONFIGURATION<br>1[7:0] | -    | E              | EXSYNC[2:0 | 0]    | _         | EOCINT<br>E | -           | -     |

| 0x02     | MAIN<br>CONFIGURATION<br>2[7:0] | SHDN | RESET          | _          | SYNC  | OSEN      | OSTRIG      | -           | -     |

| 0x03     | SEQ CONFIGURATION 1[7:0]        |      | SDL            | Y[3:0]     |       |           | TIM[2:0]    |             | _     |

| 0x04     | SEQ CONFIGURATION 2[7:0]        |      | NRPT[2:0]      |            |       | NCDS[2:0] |             | CDSMO<br>DE | _     |

| 0x05     | AFE<br>CONFIGURATION[7:0]       | _    | ALC_CO<br>ARSE | _          | _     | ALCEN     | _           | PGA         | [1:0] |

| 0x06     | LED<br>CONFIGURATION[7:0]       | _    | _              | -          | _     |           | DRV         | /[3:0]      |       |

| ADC      |                                 |      |                |            |       |           |             |             |       |

| 0x10     | ADC00H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x11     | ADC00L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x12     | ADC01H[7:0]                     | _    | _              | -          | _     | _         | _           | _           | -     |

| 0x13     | ADC01L[7:0]                     | -    | _              | -          | _     | _         | _           | -           | ı     |

| 0x14     | ADC02H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | ı     |

| 0x15     | ADC02L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x16     | ADC03H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x17     | ADC03L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x18     | ADC04H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x19     | ADC04L[7:0]                     | _    | _              | -          | _     | _         | _           | _           | _     |

| 0x1A     | ADC05H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x1B     | ADC05L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x1C     | ADC06H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x1D     | ADC06L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x1E     | ADC07H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x1F     | ADC07L[7:0]                     | _    | _              | -          | _     | _         | _           | _           | _     |

| 0x20     | ADC08H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x21     | ADC08L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x22     | ADC09H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x23     | ADC09L[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| 0x24     | ADC10H[7:0]                     | _    | _              | _          | _     | _         | _           | _           | _     |

| ADDRESS | NAME        | MSB |   |   |   |   |   |   | LSB |

|---------|-------------|-----|---|---|---|---|---|---|-----|

| 0x25    | ADC10L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x26    | ADC11H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x27    | ADC11L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x28    | ADC12H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x29    | ADC12L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2A    | ADC13H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2B    | ADC13L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2C    | ADC14H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2D    | ADC14L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2E    | ADC15H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x2F    | ADC15L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x30    | ADC16H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x31    | ADC16L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x32    | ADC17H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x33    | ADC17L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x34    | ADC18H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x35    | ADC18L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x36    | ADC19H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x37    | ADC19L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x38    | ADC20H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x39    | ADC20L[7:0] | _   | _ | - | - | - | _ | - | _   |

| 0x3A    | ADC21H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x3B    | ADC21L[7:0] | _   | _ | _ | _ | - | _ | - | _   |

| 0x3C    | ADC22H[7:0] | _   | _ | _ | _ | - | _ | - | _   |

| 0x3D    | ADC22L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x3E    | ADC23H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x3F    | ADC23L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x40    | ADC24H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x41    | ADC24L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x42    | ADC25H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x43    | ADC25L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x44    | ADC26H[7:0] | _   | _ | - | - | - | - | - | _   |

| 0x45    | ADC26L[7:0] | _   | _ | - | _ | _ | _ | _ | _   |

| 0x46    | ADC27H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x47    | ADC27L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x48    | ADC28H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x49    | ADC28L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x4A    | ADC29H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x4B    | ADC29L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x4C    | ADC30H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x4D    | ADC30L[7:0] |     | _ | _ | _ | _ | _ | _ | _   |

| ADDRESS | NAME        | MSB |   |   |   |   |   |   | LSB |

|---------|-------------|-----|---|---|---|---|---|---|-----|

| 0x4E    | ADC31H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x4F    | ADC31L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x50    | ADC32H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x51    | ADC32L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x52    | ADC33H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x53    | ADC33L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x54    | ADC34H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x55    | ADC34L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x56    | ADC35H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x57    | ADC35L[7:0] | _   | _ | - | _ | _ | _ | _ | _   |

| 0x58    | ADC36H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x59    | ADC36L[7:0] | _   | _ | - | _ | _ | _ | _ | _   |

| 0x5A    | ADC37H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x5B    | ADC37L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x5C    | ADC38H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x5D    | ADC38L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x5E    | ADC39H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x5F    | ADC39L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x60    | ADC40H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x61    | ADC40L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x62    | ADC41H[7:0] | _   | _ | - | _ | _ | - | _ | _   |

| 0x63    | ADC41L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x64    | ADC42H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x65    | ADC42L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x66    | ADC43H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x67    | ADC43L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x68    | ADC44H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x69    | ADC44L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x6A    | ADC45H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x6B    | ADC45L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x6C    | ADC46H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x6D    | ADC46L[7:0] | _   | _ | - | _ | _ | - | _ | _   |

| 0x6E    | ADC47H[7:0] | _   | _ | _ | - | - | - | _ | -   |

| 0x6F    | ADC47L[7:0] | _   | _ | - | _ | _ | _ | _ | _   |

| 0x70    | ADC48H[7:0] | _   | _ | _ | _ | - | _ | _ | _   |

| 0x71    | ADC48L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x72    | ADC49H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x73    | ADC49L[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x74    | ADC50H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| 0x75    | ADC50L[7:0] | _   | _ | _ | _ | - | _ | _ | _   |

| 0x76    | ADC51H[7:0] | _   | _ | _ | _ | _ | _ | _ | _   |

| ADDRESS     | NAME                      | MSB |       |         |   |             |        |             | LSB          |

|-------------|---------------------------|-----|-------|---------|---|-------------|--------|-------------|--------------|

| 0x77        | ADC51L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x78        | ADC52H[7:0]               | _   | -     | _       | _ | _           | _      | _           | _            |

| 0x79        | ADC52L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x7A        | ADC53H[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x7B        | ADC53L[7:0]               | _   | -     | -       | - | _           | _      | _           | -            |

| 0x7C        | ADC54H[7:0]               | -   | -     | -       | _ | -           | _      | -           | _            |

| 0x7D        | ADC54L[7:0]               | _   | -     | _       | _ | _           | _      | _           | _            |

| 0x7E        | ADC55H[7:0]               | _   | _     | -       | _ | _           | _      | _           | _            |

| 0x7F        | ADC55L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x80        | ADC56H[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x81        | ADC56L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x82        | ADC57H[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x83        | ADC57L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x84        | ADC58H[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x85        | ADC58L[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x86        | ADC59H[7:0]               | _   | _     | _       | _ | _           | _      | _           | _            |

| 0x87        | ADC59L[7:0]               | _   | -     | _       | _ | _           | _      | _           | _            |

| CHANNEL     | GAIN TRIMS                | •   |       |         |   | •           |        |             |              |

| 0xA5        | COLUMN GAIN 2.<br>1[7:0]  |     | CGAIN | N2[3:0] |   |             | CGAI   | N1[3:0]     |              |

| 0xA6        | COLUMN GAIN 4.<br>3[7:0]  |     | CGAIN | N4[3:0] |   |             | CGAI   | N3[3:0]     |              |

| 0xA7        | COLUMN GAIN 6.<br>5[7:0]  |     | CGAIN | N6[3:0] |   |             | CGAI   | N5[3:0]     |              |

| 0xA8        | COLUMN GAIN 8,<br>7[7:0]  |     | CGAIN | N8[3:0] |   |             | CGAI   | N7[3:0]     |              |

| 0xA9        | COLUMN GAIN 10,<br>9[7:0] |     | CGAIN | 10[3:0] |   | CGAIN9[3:0] |        |             |              |

| LED CONTROL |                           |     |       |         |   |             |        |             |              |

| 0xC1        | LED_CTRL[7:0]             | _   | _     | _       | _ | GAINSE<br>L | DRV_EN | ELED_E<br>N | ELED_P<br>OL |

### **Register Details**

### **INTERRUPT STATUS (0x00)**

| BIT            | 7 | 6 | 5 | 4         | 3 | 2         | 1 | 0 |

|----------------|---|---|---|-----------|---|-----------|---|---|

| Field          | _ | - | - | PWRON     | - | EOCINTS   | - | _ |

| Reset          | _ | - | - |           | - |           | - | _ |

| Access<br>Type | _ | _ | _ | Read Only | - | Read Only | _ | - |

| BITFIELD | BITS | DESCRIPTION                 | DECODE                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PWRON    | 4    | Power On Reset              | PWRON = 1 indicates that a power-up event occurred, either because the part was turned on, or because there was a power-supply voltage glitch. All interrupt threshold settings in the registers are reset to power-on-default states, and should be examined if necessary. The INT pin is also pulled low. Once this bit is set, the only way to clear this bit is to read this register.  PWRON = 0 indicates normal operation; no interrupt event occurred. |  |

|          |      |                             | EOCINTS = 1 indicates that the most recent sample cycle has ended, and the newest ADC values are readable. This bit is cleared in one of the following ways:  - Main Status Register is read.                                                                                                                                                                                                                                                                  |  |

|          |      |                             | - Any of the four gesture/proximity ADC output registers is read.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| EOCINTS  | 2    | End Of Conversion Interrupt | - A new sample cycle begins.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|          |      |                             | The INT pin is also cleared when EOCINTS = 1                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|          |      |                             | This bit is always set to $0$ if the EOCINTE bit is set to $0$ , and the external $\overline{\text{INT}}$ does not react to an end of conversion.                                                                                                                                                                                                                                                                                                              |  |

|          |      |                             | EOCINTS = 0 indicates that no interrupt trigger event occurred.                                                                                                                                                                                                                                                                                                                                                                                                |  |

#### **MAIN CONFIGURATION 1 (0x1)**

| BIT            | 7 | 6           | 5           | 4 | 3 | 2           | 1 | 0 |

|----------------|---|-------------|-------------|---|---|-------------|---|---|

| Field          | - |             | EXSYNC[2:0] |   | _ | EOCINTE     | _ | _ |

| Reset          | _ | 0b000       |             |   | _ | 0b1         | _ | - |

| Access<br>Type | _ | Write, Read |             |   | _ | Write, Read | _ | _ |

| BITFIELD | BITS                                     | DESCRIPTION   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DECODE                                                                                                                         |  |  |

|----------|------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |                                          |               | The 3 bits of EXSYNC[2:0] control the external synchronization feature of the MAX25405. This is required for the case where two MAX25405 devices are used in a system, and a means is needed to avoid simultaneous flashing of the two LEDs. If the host processor is available to perform this function, then the internal SNYC and one-shot modes described later can be used. If the host processor is not available to coordinate the sample timing, then the two MAX25405 parts in the system must self-coordinate by communicating through the SYNC pin. The 3 bits of EXSYNC control the operation of the SYNC pin for this purpose. |                                                                                                                                |  |  |

|          |                                          |               | EXSYNC[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Function                                                                                                                       |  |  |

| EXSYNC   | 6:4                                      | External Sync | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The SYNC pin is set to input, but has no function. Tie the pin to a logic-high, low voltage, or a pulldown or pullup resistor. |  |  |

|          |                                          |               | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The SYNC pin is set to input, and this MAX25405 functions as an LED SYNC slave                                                 |  |  |

|          |                                          |               | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The SYNC pin is set to output, and this MAX25405 functions as an LED SYNC master                                               |  |  |

|          |                                          |               | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Same as 000                                                                                                                    |  |  |

|          |                                          |               | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Same as 000                                                                                                                    |  |  |

|          |                                          |               | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Same as 000                                                                                                                    |  |  |

|          |                                          |               | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Same as 000                                                                                                                    |  |  |

|          |                                          |               | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Same as 000                                                                                                                    |  |  |

| EOCINTE  | NTE 2 End-of-Conversion Interrupt Enable |               | ECOINTE = 1 enables the end-of-conversion interrupt. An end-of-conversion event triggers a hardware interrupt in which the INT pin is pulled low and EOCINTS bit (register 0x00[2]) is set high Note: INT is cleared from the active state after six clock cycles if the processor does not clear it first by reading the status register.                                                                                                                                                                                                                                                                                                  |                                                                                                                                |  |  |

#### **MAIN CONFIGURATION 2 (0x2)**

| BIT            | 7           | 6           | 5 | 4           | 3           | 2           | 1 | 0 |

|----------------|-------------|-------------|---|-------------|-------------|-------------|---|---|

| Field          | SHDN        | RESET       | _ | SYNC        | OSEN        | OSTRIG      | - | - |

| Reset          | 0b0         | 0b0         | _ | 0b0         | 0b0         | 0b0         | _ | - |

| Access<br>Type | Write, Read | Write, Read | _ | Write, Read | Write, Read | Write, Read | - | - |

| BITFIELD | BITS | DESCRIPTION              | DECODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------|------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SHDN     | 7    | Shutdown Control         | SHDN = 1 places the MAX25405 into a power-save mode. While all registers remain accessible and retain data, ADC conversion data contained in them are previous values. Writable registers also remain accessible in shutdown. All interrupts are cleared.  SHDN = 0 places the MAX25405 in normal operation. When the part returns from shutdown,                                                                                                                                                                                                                                                                            |  |  |  |

|          |      |                          | the data in the registers is not current until the first conversion cycle is completed.  RESET = 1 triggers the power-on-reset sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| RESET    | 6    | Reset Control            | All configuration, threshold, and data registers are reset to power-on state by writing a 1 to this bit, and an internal hardware reset pulse is generated. This bit then automatically becomes 0 after the RESET sequence is completed. Post-reset, the PWRON Interrupt is triggered.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|          |      |                          | RESET = 0 configures the MAX25405 for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| SYNC     | 4    | Master Slave Synchronize | This bit is used for synchronizing and staggering LED pulses when multiple devices are used in the system. This prevents two devices from flashing their LEDs at the same time. This is a self-clearing bit. When set to 1, it resets to 0 after one I <sup>2</sup> C clock. The rising edge of this bit aborts the current ADC conversion cycle and starts a new ADC conversion cycle (ADC conversion cycle includes LED pulse, precharge, and ADC conversion/integration time). The ADC conversion cycles repeat after the delay set by SDLY[3:0].                                                                         |  |  |  |

|          |      |                          | Note 1: This scheme does not work for short SDLY settings. When multiple devices are used in a system, there is a limit on the minimum SDLY. The SDLY of the master must be larger than the integration time of the slave.  Note 2: The software may periodically execute the                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|          |      |                          | sync sequence to take care of clock drift and mismatch on multiple devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| OSEN     | 3    | One-Shot Mode Enable     | This bit enables one-shot mode. In this mode, the parameter SDLY is ignored, and no samples are automatically initiated. Instead, the system waits in idle mode until the bit OSTRIG (one-shot trigger) is set. This mode is used if the host processor requires full control over the timing of sample sequences, such as the case where there are multiple MAX25405 devices in one system. When combined with the EOCINT feature, the processor can be in full control of the start of a sample sequence, and then can be alerted when the sequence is done. When cleared to 0, the sequencer reverts to normal operation. |  |  |  |

| BITFIELD | BITS | DESCRIPTION      | DECODE                                                                                                                                                                                                                               |

|----------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |                  | The bit OSTRIG is used for initiating one ADC conversion cycle under software control when OSEN is set to 1. When OSEN is set to 0, OSTRIG is ignored.                                                                               |

| OSTRIG   | 2    | One-Shot Trigger | This is a self-clearing bit. When set to 1, it resets to 0 after one I <sup>2</sup> C clock. The rising edge of this bit starts an ADC conversion cycle. The cycle does not repeat until OSTRIG is cleared, and then set to 1 again. |

#### **SEQ CONFIGURATION 1 (0x3)**

| BIT            | 7 | 6      | 5      | 4 | 3 | 2 | 1 | 0 |

|----------------|---|--------|--------|---|---|---|---|---|

| Field          |   | SDL'   | Y[3:0] |   |   |   | - |   |

| Reset          |   | 0b0    | 111    |   |   | _ |   |   |

| Access<br>Type |   | Write, | Read   |   |   | _ |   |   |

| BITFIELD | BITS | DESCRIPTION             |                                                                                                                                                                                                                       | DE              | CODE                          |  |

|----------|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|--|

|          |      |                         | SDLY<br>[3:0]                                                                                                                                                                                                         | Clock<br>Counts | Delay Between<br>Samples (ms) |  |

|          |      |                         | 0000                                                                                                                                                                                                                  | 0               | 0                             |  |