# System Basis Chip with CAN FD, LDO Regulator and Wake-up Comparator

# NCV7451

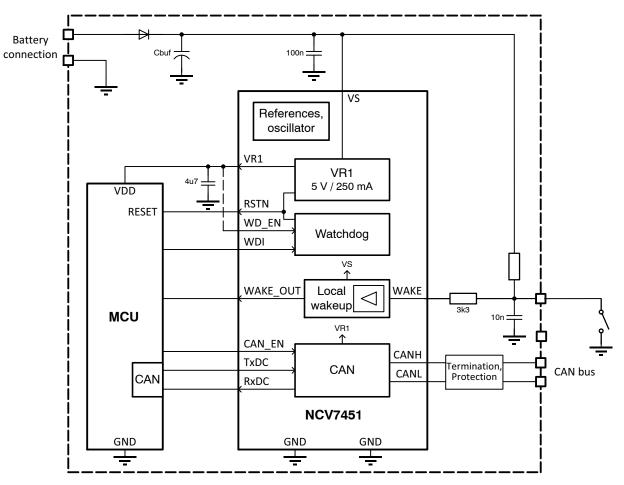

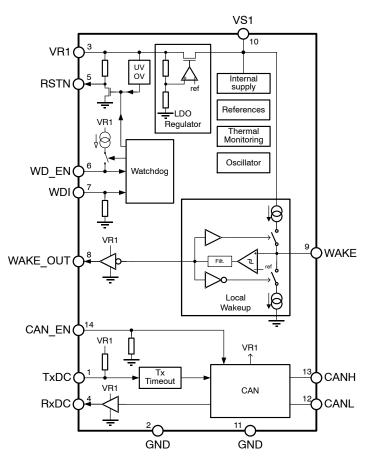

The system basis chip (SBC) NCV7451 integrates +5 V / 250 mA LDO regulator with a high-speed CAN FD transceiver and local wake-up comparator, directly controlled by dedicated pins.

# Features

- 5 V ±2% / 250 mA LDO

- Current Limitation with Fold-back

- ♦ Output Voltage Monitoring

- One High-Speed CAN FD Transceiver

- Compliant to ISO11898-2:2016

- CAN FD Timing Specified up to 5 Mbps

- Current Limitation, Reverse Current Protected

- TxDC Timeout

- Local Wake–up Comparator

- Integrated Pull-up / Pull-down Current Source

- Very Low Current Quiescent Consumption

- Window Watchdog

- Direct Control

- Thermal Shutdown Protection

- AEC-Q100 Qualified and PPAP Capable

- Wettable Flank Package for Enhanced Optical Inspection

- This is a Pb–Free Device

# **Typical Applications**

- Automotive

- Industrial Networks

# **ON Semiconductor®**

www.onsemi.com

DFNW14 4.5x3, 0.65P CASE 507AC

# **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NCV7451MW0R2G | DFNW14<br>(Pb-Free) | 5000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

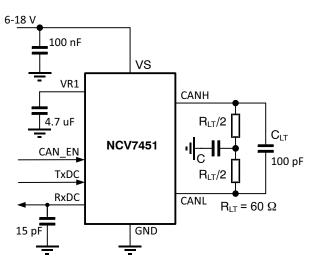

Figure 1. Simplified Application Diagram

Figure 2. Block Diagram

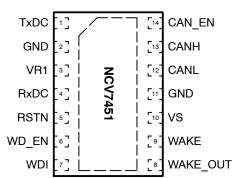

# **PIN FUNCTION DESCRIPTION**

| Pin<br>No. | Pin Name | Pin Type<br>(LV = Low Voltage; HV = High Voltage) | Description                                                  |

|------------|----------|---------------------------------------------------|--------------------------------------------------------------|

| 1          | TxDC     | LV digital input; internal pull-up                | CAN transmitter data input                                   |

| 2          | GND      | Ground connection                                 | Ground supply (all GND pins have to be connected externally) |

| 3          | VR1      | LV supply output                                  | Output of the 5 V / 250 mA low-drop regulator                |

| 4          | RxDC     | LV digital output; push-pull                      | CAN receiver data output                                     |

| 5          | RSTN     | LV digital output; open drain; internal pull-up   | Reset signal to the MCU                                      |

| 6          | WD_EN    | LV digital input; internal pull-up current        | Watchdog enable input                                        |

| 7          | WDI      | LV digital input; internal pull-down              | Watchdog trigger input                                       |

| 8          | WAKE_OUT | LV digital output                                 | WAKE pin output (inverted WAKE level)                        |

| 9          | WAKE     | HV input; pull-up/-down current                   | WAKE pin                                                     |

| 10         | VS       | HV supply input                                   | Main supply input                                            |

| 11         | GND      | Ground connection                                 | Ground supply (all GND pins have to be connected externally) |

| 12         | CANL     | CAN bus interface                                 | CANL line of the CAN bus                                     |

| 13         | CANH     | CAN bus interface                                 | CANH line of the CAN bus                                     |

| 14         | CAN_EN   | LV digital input; internal pull-down              | CAN transceiver enable input                                 |

|            | EP       | Exposed pad                                       | Substrate (has to be connected to all GND pins externally)   |

#### **MAXIMUM RATINGS**

| Symbol               | Rating                                                                                    |                              |       | Мах                                    | Unit |

|----------------------|-------------------------------------------------------------------------------------------|------------------------------|-------|----------------------------------------|------|

| VS                   | DC Power Supply Voltage (Note 1)                                                          |                              |       | +40                                    | V    |

| VR1                  | LDO Supply pin output voltage                                                             |                              | -0.3  | 6 or VS+0.3<br>(whichever<br>is lower) | V    |

| VdigIO               | DC voltage on digital pins (CAN_EN, WD_EN, WDI, R<br>WAKE_OUT)                            | STN, RxDC, TxDC,             | -0.3  | VR1+0.3                                | V    |

| WAKE                 | DC WAKE pin Input Voltage                                                                 |                              | - 40  | +40                                    | V    |

| CANH, CANL           | DC voltage on pin CANH and CANL                                                           |                              | - 40  | +40                                    | V    |

| Vdiff                | Differential DC voltage between any two pins (incl. CA                                    | NH and CANL)                 | - 40  | +40                                    | V    |

| V_ESD <sub>HBM</sub> | ESD capability, Device HBM, according to AEC-Q100-002 (EIA/JESD22-A114); (Note 2)         | Pins VS, CANH,<br>CANL, WAKE | -8    | +8                                     | kV   |

|                      |                                                                                           | Other pins                   | -4    | +4                                     |      |

| V_ESD <sub>MM</sub>  | ESD capability; MM, according to AEC-Q100-003 (El/<br>all pins                            | -200                         | +200  | V                                      |      |

| V_ESD <sub>CDM</sub> | ESD capability; CDM, according to AEC-Q100-011 (E all pins                                | IA/JESD22-C101);             | - 750 | +750                                   | V    |

| V_ESD <sub>IEC</sub> | ESD capability; System HBM, according to IEC61000-<br>pins VS, CANH, CANL, WAKE; (Note 3) | 4–2;                         | -6    | +6                                     | kV   |

| V_SCHAF              | Voltage transients, Test pulses According to                                              | Test pulse 1                 | - 100 | -                                      | V    |

|                      | ISO7637 – 2, Class D;<br>pins VS, CANH, CANL, WAKE                                        | Test pulse 2a                | -     | +75                                    | V    |

|                      |                                                                                           | Test pulse 3a                | - 150 | -                                      | V    |

|                      |                                                                                           | Test pulse 3b                | -     | +100                                   | V    |

| Tj                   | Junction Temperature Range                                                                |                              | - 40  | +150                                   | °C   |

| Tstg                 | Storage Temperature Range                                                                 |                              | - 55  | +150                                   | °C   |

| Tsld                 | Peak Soldering Temperature (Note 4)                                                       |                              | -     | 260                                    | °C   |

| MSL                  | Moisture Sensitivity Level                                                                |                              |       | 1                                      | _    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe

Operating parameters.

Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ resistor

Equivalent to discharging a 150 pF capacitor through a 330 Ω resistor; WAKE pin stressed through an external series resistor of 3.3 kΩ and with 10 nF capacitor on the module input, VS pin decoupled with 100 nF.

4. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

# **THERMAL CHARACTERISTICS**

| Symbol           | Rating                                                                                                                  | Value    | Unit |

|------------------|-------------------------------------------------------------------------------------------------------------------------|----------|------|

| R <sub>θJA</sub> | Thermal Characteristics,<br>Thermal Resistance, Junction-to-Air (Note 5)<br>Thermal Reference, Junction-to-Air (Note 6) | 77<br>52 | °C/W |

| R <sub>ψJC</sub> | Thermal Characteristics,<br>Thermal Resistance, Junction-to-Case                                                        | 7        | °C/W |

5. Value based on test board according to JESD51-3 standard, signal layer with 10% trace coverage.

6. Value based on test board according to JESD51-7 standard, signal layers with 20% trace coverage, inner planes with 90% coverage.

## RECOMMENDED OPERATING RANGES

| Symbol         | Rating                                                               | Min | Max | Unit |

|----------------|----------------------------------------------------------------------|-----|-----|------|

| VS             | Functional supply voltage                                            | 5.0 | 28  | V    |

|                | Supply voltage for valid parameter specification                     | 6.0 | 18  | V    |

| VR1            | VR1 regulator output voltage                                         | 4.9 | 5.1 | V    |

| I(VR1)         | VR1 regulator output current (including CAN transceiver consumption) | 0   | 250 | mA   |

| VdigIO         | Digital inputs/outputs voltage                                       | 0   | VR1 | V    |

| WAKE           | WAKE input voltage                                                   | 0   | VS  | V    |

| CANH, CANL     | CAN bus pins voltage                                                 | -40 | 40  | V    |

| TJ             | Junction Temperature                                                 | -40 | 150 | °C   |

| T <sub>A</sub> | Ambient Temperature                                                  | -40 | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

$6 \text{ V} \le \text{VS} \le 18 \text{ V}; -40^{\circ}\text{C} \le \text{Tj} \le 150^{\circ}\text{C}; 4.75 \text{ V} \le \text{VR1} \le 5.25 \text{ V}; \text{R}_{\text{LT}} = 60 \Omega, \text{C}_{\text{LT}} = 100 \text{ pF}, \text{C}_{\text{ST}} \text{ not used, unless otherwise specified.}$

| Symbol    | Parameter                 | Conditions                                                                                                                                        | Min | Тур | Max | Unit |

|-----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VS SUPPLY | ·                         |                                                                                                                                                   |     | •   | •   |      |

| VS_PORH   | VS POR threshold          | VS rising                                                                                                                                         | 3.4 | -   | 4.1 | V    |

| VS_PORL   | VS POR threshold          | VS falling                                                                                                                                        | 2.0 | -   | 3.5 | V    |

| ls_off    | VS consumption, low-power | VS = 14 V, VR1 on (not loaded), WAKE float-<br>ing, CAN bus recessive,<br>CAN_EN = Low, WD_EN = Low, Tj $\leq 85^{\circ}$ C                       | -   | 28  | 35  | μΑ   |

| ls_act    | VS consumption, active    | VS = 14 V, VR1 on (loaded by 100 mA, not<br>included in Is_act), WAKE floating, CAN bus<br>recessive,<br>CAN_EN = High, WD_EN = High, TxDC = High | _   | 3.7 | 5.0 | mA   |

#### VR1 VOLTAGE REGULATOR

| V_VR1         | Regulator output voltage                | 0 mA $\leq$ I(VR1) $\leq$ 250 mA (including internal CAN consumption), 6 V $\leq$ VS $\leq$ 28 V | 4.9  | 5.0               | 5.1 | V  |

|---------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|------|-------------------|-----|----|

| llim_VR1      | Regulator current limitation            | Maximum VR1 overload current,<br>VR1 > RES_VR1                                                   | 250  | -                 | 650 | mA |

| lshort_VR1    | Regulator short current                 | Maximum VR1 short current, VR1 < RES_VR1                                                         | 125  | 1/2 x<br>Ilim_VR1 | 325 | mA |

| Vdrop_VR1     | Dropout Voltage                         | I(VR1) = 100 mA, VS = 5 V                                                                        | -    | 0.2               | 0.4 | V  |

|               |                                         | I(VR1) = 100 mA, VS = 4.5 V                                                                      | -    | 0.2               | 0.5 |    |

|               |                                         | I(VR1) = 50 mA, VS = 4.5 V                                                                       | -    | 0.1               | 0.4 |    |

| Loadreg_VR1   | Load Regulation                         | $1 \text{ mA} \leq I(VR1) \leq 100 \text{ mA}$                                                   | -50  | -                 | 50  | mV |

| Linereg_VR1   | Line Regulation                         | $I(VR1) \leq 100 \text{ mA}$                                                                     | -40  | -                 | 40  | mV |

| Cload_VR1     | VR1 load capacity                       | ESR < 200 m $\Omega$ , ceramic capacitor recommended                                             | 1.0  | 4.7               | -   | μF |

| RES_VR1       | VR1 Reset threshold                     | VR1 voltage decreasing                                                                           | 4.3  | 4.5               | 4.7 | V  |

| RES_hyst_VR1  | VR1 Reset threshold hysteresis          |                                                                                                  | 0.05 | 0.1               | 0.2 | V  |

| tfilt_RES_VR1 | VR1 undervoltage filter time            |                                                                                                  | -    | 15                | -   | μs |

| OV_VR1        | VR1 overvoltage threshold               | VR1 voltage increasing / decreasing                                                              | 5.5  | -                 | 6.0 | V  |

| OV_hyst_VR1   | VR1 overvoltage threshold<br>hysteresis |                                                                                                  | -    | 0.06              | -   | V  |

| tfilt_OV_VR1  | VR1 overvoltage filter time             |                                                                                                  | -    | 15                | -   | μs |

| toff_VR1      | VR1 off time after TSD                  |                                                                                                  | -    | 1.0               | -   | s  |

|               | •                                       |                                                                                                  |      |                   |     |    |

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \text{ (continued)} \\ 6 \text{ V} \leq \text{ VS} \leq 18 \text{ V}; -40^{\circ}\text{C} \leq \text{Tj} \leq 150^{\circ}\text{C}; 4.75 \text{ V} \leq \text{ VR1} \leq 5.25 \text{ V}; \text{ R}_{LT} = 60 \ \Omega, \text{ C}_{LT} = 100 \text{ pF}, \text{ C}_{ST} \text{ not used, unless otherwise specified.} \end{array}$

| Symbol                                     | Parameter                                                                                         | Conditions                                                                                                                                                             | Min          | Тур              | Max        | Unit |

|--------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|------------|------|

| VR1 VOLTAGE RE                             | EGULATOR                                                                                          |                                                                                                                                                                        |              |                  |            |      |

| ls_add_VR1                                 | VS consumption adder of VR1                                                                       | (Note 7)                                                                                                                                                               | -            | 0.01 x<br>I(VR1) | -          | А    |

| CAN BUS LINES                              | (Pins CANH and CANL)                                                                              |                                                                                                                                                                        |              |                  |            |      |

| I <sub>o(rec)</sub>                        | Recessive output current at<br>pins CANH and CANL                                                 | CAN enabled;<br>-27 V < V <sub>CANH</sub> , V <sub>CANL</sub> < 32 V                                                                                                   | -5.0         | -                | 5.0        | mA   |

| Ι <sub>LI</sub>                            | Input leakage current                                                                             | $\begin{array}{l} 0 \; \Omega \; \leq \; R(VR1 \; to \; GND) < 1 \; M\Omega; \\ V_{CANH} = V_{CANH} = 5 \; V \end{array}$                                              | -5.0         | 0                | 5.0        | μΑ   |

| $V_{o(rec)(CANH)}$                         | Recessive output voltage at<br>pin CANH                                                           | CAN enabled; TxDC = High; no load                                                                                                                                      | 2.0          | 2.5              | 3.0        | V    |

| $V_{o(rec)(CANL)}$                         | Recessive output voltage at<br>pin CANL                                                           | CAN enabled; TxDC = High; no load                                                                                                                                      | 2.0          | 2.5              | 3.0        | V    |

| V <sub>o(off)(CANH)</sub>                  | Recessive output voltage at<br>pin CANH                                                           | CAN disabled; no load                                                                                                                                                  | -0.1         | 0                | 0.1        | V    |

| V <sub>o(off)(CANL)</sub>                  | Recessive output voltage at<br>pin CANL                                                           | CAN disabled; no load                                                                                                                                                  | -0.1         | 0                | 0.1        | V    |

| $V_{o(off)(diff)}$                         | Differential bus output volt-<br>age in off mode<br>(V <sub>CANH</sub> – V <sub>CANL</sub> )      | CAN disabled; no load                                                                                                                                                  | -0.2         | 0                | 0.2        | V    |

| V <sub>o(dom)</sub> (CANH)                 | Dominant output voltage at<br>pin CANH                                                            | $\begin{array}{l} \mbox{CAN enabled; 50 } \Omega \leq \mbox{R}_{LT} \leq \mbox{65 } \Omega; \\ \mbox{TxDC} = \mbox{Low; } t < t_{\mbox{dom}(\mbox{TxDC})} \end{array}$ | 2.75         | 3.5              | 4.5        | V    |

| V <sub>o(dom)</sub> (CANL)                 | Dominant output voltage at<br>pin CANL                                                            | $\begin{array}{l} \mbox{CAN enabled; 50 } \Omega \leq \mbox{R}_{LT} \leq \mbox{65 } \Omega; \\ \mbox{TxDC} = \mbox{Low; } t < t_{\mbox{dom}(\mbox{TxDC})} \end{array}$ | 0.5          | 1.5              | 2.25       | V    |

| V <sub>o(sym)</sub>                        | Driver output voltage<br>symmetry (V <sub>CANH</sub> + V <sub>CANL</sub> )                        | CAN enabled; $C_{ST}$ = 4.7 nF; TxDC driven by square wave up to 1 MHz                                                                                                 | 0.9          | _                | 1.1        | VR1  |

| V <sub>o(dom)(diff)</sub>                  | Differential bus output<br>voltage (V <sub>CANH</sub> – V <sub>CANL</sub> )                       | CAN enabled; 45 $\Omega \le R_{LT} \le 65 \Omega$ ;<br>TxDC = Low; dominant                                                                                            | 1.5          | 2.25             | 3.0        | V    |

| V <sub>o(dom)(diff)_arb</sub>              | Differential bus output<br>voltage during arbitration<br>(V <sub>CANH</sub> – V <sub>CANL</sub> ) | CAN enabled; R <sub>LT</sub> = 2240 Ω;<br>TxDC = Low; dominant; (Note 7)                                                                                               | 1.5          | -                | 5.0        | V    |

| $V_{o(rec)(diff)}$                         | Differential bus output<br>voltage (V <sub>CANH</sub> – V <sub>CANL</sub> )                       | CAN enabled; no load;<br>V <sub>TxDC</sub> = High; recessive                                                                                                           | -50          | 0                | 50         | mV   |

| I <sub>o(sc)</sub> (CANH)                  | Short circuit output current at<br>pin CANH                                                       | CAN enabled; TxDC = Low;<br>$V_{CANH} = -3 V$<br>$-3 V \le V_{CANH} \le 18 V$                                                                                          | -100<br>-100 | -70              | -40<br>2.0 | mA   |

| I <sub>o(sc)</sub> (CANL)                  | Short circuit output current at<br>pin CANL                                                       | CAN enabled; TxDC = Low;<br>$V_{CANL} = 36 V$<br>$-3 V \le V_{CANL} \le 18 V$                                                                                          | 40<br>-1.5   | 70               | 100<br>100 | mA   |

| V <sub>i(rec)(diff)_NM</sub>               | Differential input voltage range                                                                  | CAN enabled; no load;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                                | 3.0          | -                | 0.5        | V    |

| V <sub>i(rec)(diff)_LP</sub>               | <ul> <li>recessive state</li> </ul>                                                               | CAN disabled; no load;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                               | -3.0         | -                | 0.4        | V    |

| V <sub>i(dom)(diff)_NM</sub>               | Differential input voltage range                                                                  | CAN enabled; no load;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                                | 0.9          | -                | 8.0        | V    |

| $V_{i(dom)(diff)\_LP}$                     | dominant state                                                                                    | CAN disabled; no load;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                               | 1.05         | -                | 8.0        | V    |

| $V_{i(\text{diff})(\text{th})\_\text{NM}}$ | Differential receiver threshold voltage in normal mode                                            | CAN enabled;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                                         | 0.5          | -                | 0.9        | V    |

| Vi(diff)(th)_LP                            | Differential receiver threshold<br>voltage in wake-up-detec-<br>tion mode                         | CAN disabled;<br>-12 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ 12 V                                                                                        | 0.4          | -                | 1.05       | V    |

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \text{ (continued)} \\ 6 \text{ V} \leq \text{ VS} \leq 18 \text{ V}; -40^{\circ}\text{C} \leq \text{Tj} \leq 150^{\circ}\text{C}; 4.75 \text{ V} \leq \text{ VR1} \leq 5.25 \text{ V}; \text{ R}_{\text{LT}} = 60 \ \Omega, \text{ C}_{\text{LT}} = 100 \text{ pF}, \text{ C}_{\text{ST}} \text{ not used, unless otherwise specified.} \end{array}$

| Symbol                      | Parameter                                                                                           | Conditions                                                                          | Min  | Тур  | Max | Unit |

|-----------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|-----|------|

| CAN BUS LINES               | (Pins CANH and CANL)                                                                                |                                                                                     | •    |      |     |      |

| R <sub>i(cm)(CANH)</sub>    | Common-mode input resis-<br>tance at pin CANH                                                       | $-2 \text{ V} \leq \text{V}_{\text{CANH}}, \text{V}_{\text{CANL}} \leq 7 \text{ V}$ | 15   | 25   | 37  | kΩ   |

| R <sub>i(cm)(CANL)</sub>    | Common-mode input resis-<br>tance at pin CANL                                                       | $-2 \text{ V} \leq \text{V}_{\text{CANH}}, \text{V}_{\text{CANL}} \leq 7 \text{ V}$ | 15   | 25   | 37  | kΩ   |

| R <sub>i(cm)(m)</sub>       | Matching between pin CANH<br>and pin CANL common<br>mode input resistance                           | V <sub>CANH</sub> = V <sub>CANL</sub> = 5 V                                         | -1.0 | 0    | 1.0 | %    |

| R <sub>i(diff)</sub>        | Differential input resistance                                                                       |                                                                                     | 25   | 50   | 75  | kΩ   |

| C <sub>i(CANH)</sub>        | Input capacitance at pin<br>CANH                                                                    | TxDC = High; (Note 7)                                                               | -    | 7.5  | 20  | pF   |

| C <sub>i(CANL)</sub>        | Input capacitance at pin<br>CANL                                                                    | TxDC = High; (Note 7)                                                               | -    | 7.5  | 20  | pF   |

| C <sub>i(diff)</sub>        | Differential input capacitance                                                                      | TxDC = High; (Note 7)                                                               | -    | 3.75 | 10  | pF   |

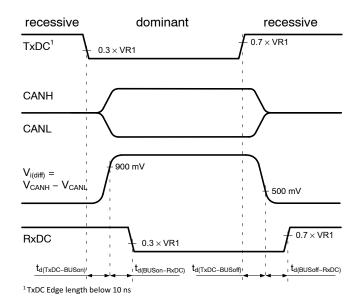

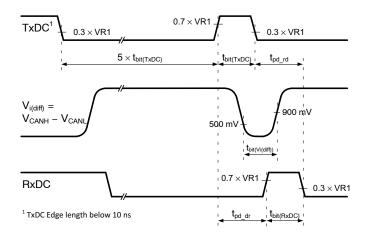

| TIMING CHARAC               | TERISTICS (see Figure 3, Figure                                                                     | 4 and Figure 5)                                                                     |      |      |     |      |

| t <sub>d(TxDC-BUSon)</sub>  | Propagation delay TxDC to bus active                                                                | CAN enabled                                                                         | -    | 65   | -   | ns   |

| t <sub>d(TxDC-BUSoff)</sub> | Propagation delay TxDC to<br>bus inactive                                                           | CAN enabled                                                                         | -    | 90   | -   | ns   |

| t <sub>d(BUSon-RxDC)</sub>  | Propagation delay bus active to RxDC                                                                | CAN enabled                                                                         | -    | 60   | -   | ns   |

| t <sub>d(BUSoff-RxDC)</sub> | Propagation delay bus inac-<br>tive to RxDC                                                         | CAN enabled                                                                         | -    | 65   | -   | ns   |

| t <sub>pd_dr</sub>          | Propagation delay TxDC to<br>RxDC dominant to recessive<br>transition                               | CAN enabled                                                                         | 50   | 100  | 170 | ns   |

| t <sub>pd_rd</sub>          | Propagation delay TxDC to<br>RxDC recessive to dominant<br>transition                               | CAN enabled                                                                         | 50   | 120  | 170 | ns   |

| t <sub>wake_filt</sub>      | Dominant time for wake-up<br>via bus                                                                | CAN_EN = Low                                                                        | 0.15 | -    | 1.8 | μs   |

| t <sub>dwakerd</sub>        | Delay to flag wake event (re-<br>cessive to dominant transi-<br>tions)                              | CAN_EN = Low; Valid bus wake-up event                                               | 0.5  | -    | 6.0 | μs   |

| t <sub>dwakedr</sub>        | Delay to flag wake event<br>(dominant to recessive tran-<br>sitions)                                | CAN_EN = Low; Valid bus wake-up event                                               | 0.5  | -    | 6.0 | μs   |

| t <sub>wake_to</sub>        | Bus time for wake-up time-<br>out                                                                   | CAN_EN = Low                                                                        | 1.0  | _    | 10  | ms   |

| t <sub>dom(TxDC)</sub>      | TxDC dominant time for time-<br>out                                                                 | CAN_EN = High; TxDC = Low                                                           | 1.0  | -    | 10  | ms   |

| t <sub>Bit(RxDC)</sub>      | Bit time on RxDC pin                                                                                | t <sub>Bit(TxDC)</sub> = 500 ns                                                     | 400  | _    | 550 | ns   |

|                             |                                                                                                     | t <sub>Bit(TxDC)</sub> = 200 ns                                                     | 120  | -    | 220 | ns   |

| t <sub>Bit(Vi(diff))</sub>  | Bit time on bus pins<br>(CANH – CANL)                                                               | t <sub>Bit(TxDC)</sub> = 500 ns                                                     | 435  | -    | 530 | ns   |

|                             |                                                                                                     | t <sub>Bit(TxDC)</sub> = 200 ns                                                     | 155  | -    | 210 | ns   |

| $\Delta t_{Rec}$            | Receiver timing symmetry<br>Δt <sub>Rec</sub> = t <sub>Bit(RxDC)</sub> – t <sub>Bit(Vi(diff))</sub> | t <sub>Bit(TxDC)</sub> = 500 ns                                                     | -65  | -    | 40  | ns   |

|                             |                                                                                                     | t <sub>Bit(TxDC)</sub> = 200 ns                                                     | -45  | _    | 15  | ns   |

# ELECTRICAL CHARACTERISTICS (continued)

$6~V~\leq~VS~\leq~18~V;~-40^{\circ}C~\leq~Tj~\leq~150^{\circ}C;~4.75~V~\leq~VR1~\leq~5.25~V;~R_{LT}$  = 60  $\Omega,~C_{LT}$  = 100 pF,  $C_{ST}$  not used, unless otherwise specified.

| Symbol                                                       | Parameter                                                     | Conditions               | Min | Тур | Мах | Unit |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------|--------------------------|-----|-----|-----|------|--|--|--|

| TIMING CHARACTERISTICS (see Figure 3, Figure 4 and Figure 5) |                                                               |                          |     |     |     |      |  |  |  |

| t <sub>d(LP-NM)</sub>                                        | Mode change delay from<br>wake-up detection to normal<br>mode | $CAN\_EN = Low \to High$ | -   | 25  | 47  | μs   |  |  |  |

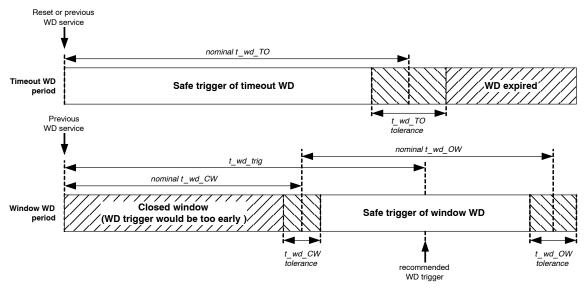

| WATCHDOG TIMI                                                | WATCHDOG TIMING                                               |                          |     |     |     |      |  |  |  |

| twd_acc | Watchdog timing accuracy                                    |                                                             | -15 | -   | 15  | %  |

|---------|-------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|----|

| t_wd_TO | Timeout watchdog period                                     | After WD_EN low $\rightarrow$ high transition or RSTN pulse | 56  | 65  | 74  | ms |

| t_wd_CW | Window watchdog closed win-<br>dow                          |                                                             | 5.1 | 6.0 | 6.9 | ms |

| t_wd_OW | Window watchdog open window                                 |                                                             | 85  | 100 | 115 | ms |

| t_WDI   | Minimum WDI pulse width ac-<br>cepted as a watchdog service |                                                             | 6.0 | _   | -   | μS |

# WAKE INPUT

| Vth_WAKE   | WAKE pin threshold            |               | 2.0 | - | 4.0  | V  |

|------------|-------------------------------|---------------|-----|---|------|----|

| Vhys_WAKE  | WAKE pin threshold hysteresis |               | 0.1 | - | 0.7  | V  |

| tfilt_WAKE | WAKE wake-up filter time      |               | 10  | - | 50   | μs |

| Ipu_WAKE   | Pull-up current on WAKE pin   | V(WAKE) = 4 V | -11 | - | -3.0 | μA |

| Ipd_WAKE   | Pull-down current on WAKE pin | V(WAKE) = 2 V | 3.0 | - | 11   | μA |

#### DIGITAL OUTPUTS, RxDC, WAKE\_OUT

| loutL_pinx | Low-level output driving current       | pinx is logical Low, forced V(pinx) = 0.4 V           | 1.0  | 6.0  | 12   | mA |

|------------|----------------------------------------|-------------------------------------------------------|------|------|------|----|

| loutH_pinx | High-level output driving cur-<br>rent | pinx is logical High,<br>forced V(pinx) = VR1 – 0.4 V | -8.0 | -3.0 | -1.0 | mA |

#### DIGITAL OUTPUT RSTN

| loutL_RSTN | Low-level output driving current                                    | RSTN is active (logical Low),<br>forced V(RSTN) = 0.4 V | 2.0 | 5.0  | 12  | mA |

|------------|---------------------------------------------------------------------|---------------------------------------------------------|-----|------|-----|----|

| VoutL_RSTN | Low-level output voltage,                                           | VR1 > 4.7 V, I(RSTN) = 0.6 mA                           | -   | 0.2  | 0.4 | V  |

|            | low VR1/VS                                                          | VR1 > 2 V, VS < VR1, I(RSTN) = 0.1 mA                   | -   | 0.2  | 0.4 |    |

|            |                                                                     | VR1 = 0 V, VS > 2 V, I(RSTN) = 0.2 mA                   | -   | 0.2  | 0.4 |    |

| Rpu_RSTN   | Internal pull-up resistor to VR1                                    |                                                         | 5.0 | 10.0 | 19  | kΩ |

| t_RSTN     | Reset pulse length after VR1<br>undervoltage or watchdog<br>failure |                                                         | 6.8 | 8.0  | 9.2 | kΩ |

#### DIGITAL INPUTS TxDC, CAN\_EN, WD\_EN, WDI

| VinL_pinx    | Low-level input voltage (logical<br>"Low")                 |                                               | -   | -   | 0.8 | V  |

|--------------|------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|----|

| VinH_pinx    | High-level input voltage (logical<br>"High")               |                                               | 2.0 | -   | -   | V  |

| Vin_hys_pinx | Input voltage hysteresis                                   |                                               | -   | 200 | -   | mV |

| Rpu_pinx     | Internal pull-up resistor to VR1;<br>pin TxDC              |                                               | 55  | 100 | 185 | kΩ |

| Rpd_pinx     | Internal pull-down resistor to<br>ground; pins CAN_EN, WDI |                                               | 55  | 100 | 185 | kΩ |

| lpu_WD_EN    | Internal pull-up current to VR1,<br>pin WD_EN              | V(WD_EN) = 0 V, pull-up current source active | 50  | 100 | 200 | μΑ |

| tper_pu_WDEN | WD_EN pull-up current source activation period             | WD_EN = CAN_EN = Low                          | -   | 610 | -   | μs |

#### ELECTRICAL CHARACTERISTICS (continued)

$6~V \leq VS \leq 18~V; -40^{\circ}C \leq Tj \leq 150^{\circ}C; 4.75~V \leq VR1 \leq 5.25~V; R_{LT} = 60~\Omega, C_{LT} = 100~pF, C_{ST}~not~used, unless otherwise specified.$

| Symbol           | Parameter                                       | Conditions           | Min | Тур | Max | Unit |

|------------------|-------------------------------------------------|----------------------|-----|-----|-----|------|

| DIGITAL INPUTS T | xDC, CAN_EN, WD_EN, WDI                         |                      |     |     |     |      |

| ton_pu_WDEN      | WD_EN pull-up current source activation on-time | WD_EN = CAN_EN = Low | -   | 5.0 | -   | μs   |

| THERMAL PROTE    | CTION                                           |                      |     |     |     |      |

| Tsd     | Thermal shutdown level                 | Temperature increasing | 155 | 165 | 175 | °C |

|---------|----------------------------------------|------------------------|-----|-----|-----|----|

| Tsd_hys | Thermal shutdown level hys-<br>teresis | Temperature decreasing | -   | 10  | -   | °C |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Not tested in production, guaranteed by design.

Figure 3. Test Circuit for CAN Timing Characteristics

Figure 4. CAN Transceiver Timing Diagram – Propagation Delays

Figure 5. CAN Transceiver Timing Diagram – Loop Delay and Recessive Bit Time

Figure 6. Watchdog Modes Timing

# FUNCTIONAL DESCRIPTION

#### Supply Concept

The device has one battery supply pin VS, supplying the VR1 regulator and logic control. The supply line has to be properly decoupled by filtering capacitors close to the device pin.

# VR1 Low-drop Regulator

VR1 is a low-drop output regulator providing 5 V voltage derived from the VS main supply. It is able to deliver up to 250 mA and is primarily intended to supply the on-chip CAN transceiver, the application microcontroller unit (MCU) and related 5 V loads (e.g. its own MCU-related digital inputs/outputs). An external capacitor needs to be connected on VR1 pin in order to ensure the regulator's stability and to filter the disturbances caused by the connected loads.

VR1 voltage supplies all the digital low-voltage input/output pins.

The protection and monitoring of the VR1 regulator consist of the following features:

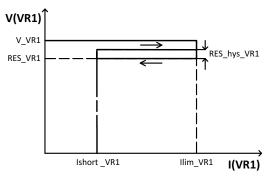

- VR1 Current Limitation the two-level current limitation controlled by VR1 reset comparator to reduce the power dissipation in case of shorts to ground by the current fold-back (see Figure 7)

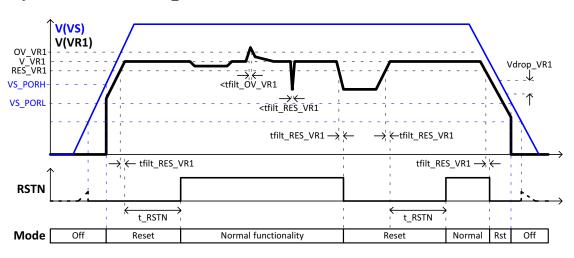

- VR1 Reset Comparator the VR1 regulator output is compared with a reset level RES\_VR1. If the VR1

level drops below this level for longer than *tfilt\_RES\_VR1*, a reset towards the MCU is generated through the RSTN pin and the CAN transceiver is disabled.

- VR1 Overvoltage Reset Comparator the VR1 regulator output is compared with an overvoltage level OV\_VR1. If the VR1 level crosses this threshold for longer than *tfilt\_OV\_VR1*, a reset towards the MCU is generated through the RSTN pin and the CAN transceiver is disabled.

- Temperature (see Figure 14)

Figure 7. VR1 Current Fold-back

Figure 8. VS1 and VR1 Monitoring

## **CAN Transceiver**

The SBC contains one high-speed CAN transceiver compliant with ISO11898–2:2016. The transceiver consists of the following sub-blocks: transmitter, receiver, and wake-up detector.

If enabled (CAN\_EN = High), the CAN transceiver is ready to provide the full-speed interface between the bus and a CAN controller connected on pins RxDC (received data) and TxDC (data to transmit). In order to prevent a faulty node from blocking the bus traffic, the maximum length of the transmitted dominant symbol is limited by a time-out counter to  $t_{dom(TxDC)}$ . In case the TxDC Low signal exceeds the timeout value, the transmitter returns automatically to the recessive state. The transmission is again de-blocked when TxDC pin returns to high (recessive) state.

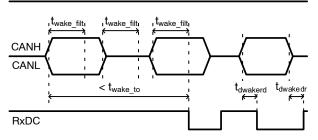

If the CAN block is disabled (CAN\_EN = Low) or RSTN pin active (Low) due to failed watchdog service or VR1

undervoltage / overvoltage, the CAN transceiver is in its wake–up detection state. Logical level on TxDC is ignored and pin RxDC is kept high until a CAN bus wake–up is detected. The CAN bus wake–up corresponds to a pattern consisting of dominant – recessive – dominant symbols of at least  $t_{wake_filt}$  each. The RxDC starts following the CAN bus afterwards. The pattern must be received within  $t_{wake_to}$  to be recognized as a valid wake–up event, otherwise internal wake–up logic is reset.

Figure 9. CAN Wake-up Pattern

#### **WAKE Comparator**

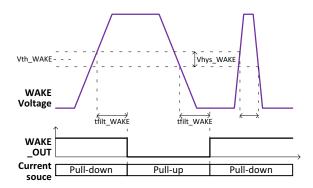

WAKE pin is a high-voltage input typically used to monitor an external contact or switch. The inverted logical level on pin WAKE can be polled via WAKE\_OUT output push-pull pin.

A stable logical level of the WAKE signal is ensured even without an external connection:

• if the WAKE level is High for longer than *tfilt\_WAKE*, an internal pull-up current source is connected to WAKE pin • if the WAKE level stays Low for longer than *tfilt\_WAKE*, an internal pull-down current source is connected to WAKE pin

Figure 10. WAKE Pin Functionality

## Watchdog

The on-chip watchdog requires that the MCU software "triggers" or "services" the watchdog in a specified time frame. A correct watchdog service consists of high-to-low transition on the WDI input. The watchdog timer re-starts immediately after a successful trigger is received.

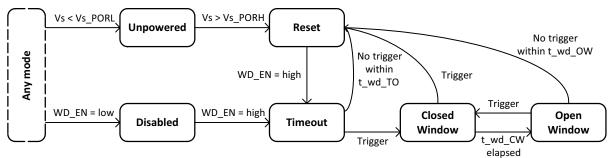

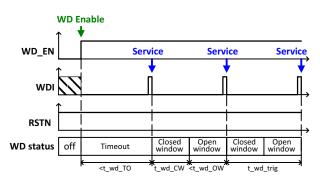

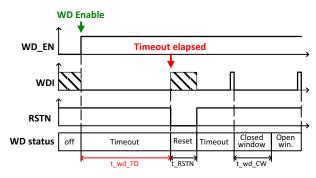

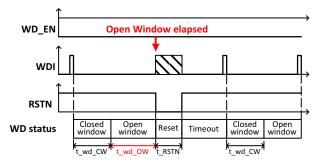

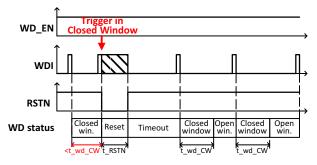

After any Reset event (power–up, watchdog failure, VR1 under–/overvoltage, thermal shutdown) or watchdog enable (WD\_EN = Low  $\rightarrow$  High), the watchdog always starts in a timeout mode. The MCU software must serve the watchdog any time before the time–out expiration. After the watchdog is triggered for the first time, it starts working in a window mode operation: the watchdog time is split to two distinct parts – a closed window, where the watchdog may not be triggered, is followed by an open window where the MCU must send a valid watchdog trigger (see Figure 12).

Figure 11. Watchdog Operating Modes

Figure 12. Correct Watchdog Services

In case the watchdog is not triggered before the timeout or open window elapses (Figure 13, Figure 14), or trigger is sent within the closed window (Figure 15), RSTN signal is generated and then watchdog restarted in the timeout mode again.

Figure 13. Missed Watchdog in Timeout Mode

Figure 14. Missed Watchdog in Window Mode

Figure 15. Watchdog Service during Closed Window

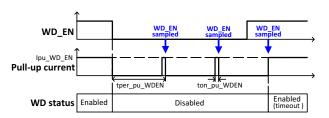

The WD\_EN pin has an integrated pull-up source to enable the watchdog in case the pin is disconnected from the application. To reduce the power consumption in the low-power mode (watchdog and CAN disabled), the WD\_EN pull-up current source is switched on for *ton\_pu\_WDEN* time with period of *tper\_pu\_WDEN*. The pin state is sampled in the end of the current source activation. Once High level is detected on the WD\_EN pin, the current source is activated permanently.

To ensure the High level is correctly detected if the pin becomes floating, external WD\_EN capacitance should stay below 50 pF.

After the rising edge on WD\_EN pin, the MCU should wait *tper\_pu\_WDEN* before the first watchdog service.

Figure 16. WD\_EN Pull-up Current Source Activation

## **Thermal Protection**

A thermal protection circuit protects the IC from damage by complete device de-activation if the junction temperature exceeds a value of *Tsd*.

The device recovers automatically after the junction temperature drops below *Tsd* level lowered by hysteresis *Tsd\_hys* and *toff\_VR1* (typ. 1 second) expires.

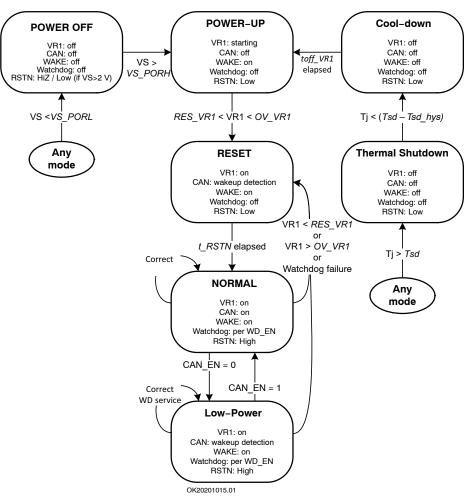

# **Operating Modes**

The device operating modes are directly controlled by CAN\_EN input pin and failure events (see Figure 17).

Figure 17. Operating Modes Diagram

# ISO11898-2:2016 PARAMETER CROSS-REFERENCE TABLE

| ISO 11898–2:2016 Specification                                               |                                          | NCV7451 Datashee                                       |

|------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------|

| Parameter                                                                    | Notation                                 | Symbol                                                 |

| DOMINANT OUTPUT CHARACTERISTICS                                              |                                          |                                                        |

| Single ended voltage on CAN_H                                                | V <sub>CAN_H</sub>                       | V <sub>o(dom)(CANH)</sub>                              |

| Single ended voltage on CAN_L                                                | V <sub>CAN_L</sub>                       | V <sub>o(dom)(CANL)</sub>                              |

| Differential voltage on normal bus load                                      | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)</sub>                              |

| Differential voltage on effective resistance during arbitration              | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)_arb</sub>                          |

| Differential voltage on extended bus load range (optional)                   | V <sub>Diff</sub>                        | NA                                                     |

| DRIVER SYMMETRY                                                              |                                          |                                                        |

| Driver symmetry                                                              | V <sub>SYM</sub>                         | V <sub>o(sym)</sub>                                    |

| DRIVER OUTPUT CURRENT                                                        |                                          |                                                        |

| Absolute current on CAN_H                                                    | I <sub>CAN_H</sub>                       | I <sub>o(SC)(CANH)</sub>                               |

| Absolute current on CAN_L                                                    | I <sub>CAN_L</sub>                       | I <sub>o(SC)(CANL)</sub>                               |

| RECEIVER OUTPUT CHARACTERISTICS, BUS BIASING ACTIVE                          |                                          | •                                                      |

| Single ended output voltage on CAN_H                                         | V <sub>CAN_H</sub>                       | V <sub>o(rec)(CANH)</sub>                              |

| Single ended output voltage on CAN_L                                         | V <sub>CAN_L</sub>                       | V <sub>o(rec)(CANL)</sub>                              |

| Differential output voltage                                                  | V <sub>Diff</sub>                        | V <sub>o(rec)(diff)</sub>                              |

| RECEIVER OUTPUT CHARACTERISTICS, BUS BIASING INACTIVE                        |                                          |                                                        |

| Single ended output voltage on CAN_H                                         | V <sub>CAN_H</sub>                       | V <sub>o(off)(CANH)</sub>                              |

| Single ended output voltage on CAN_L                                         | V <sub>CAN_L</sub>                       | V <sub>o(off)(CANL)</sub>                              |

| Differential output voltage                                                  | V <sub>Diff</sub>                        | V <sub>o(off)(dif)</sub>                               |

| TRANSMIT DOMINANT TIMEOUT                                                    |                                          |                                                        |

| Transmit dominant timeout, long                                              | t <sub>dom</sub>                         | t <sub>dom(TxDC)</sub>                                 |

| Transmit dominant timeout, short                                             | t <sub>dom</sub>                         | NA                                                     |

| STATIC RECEIVER INPUT CHARACTERISTICS, BUS BIASING ACTIVE                    |                                          | 1                                                      |

| Recessive state differential input voltage range                             | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_NM</sub>                           |

| Dominant state differential input voltage range                              | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)_NM</sub>                           |

| STATIC RECEIVER INPUT CHARACTERISTICS, BUS BIASING INACTIVE                  |                                          | (                                                      |

| Recessive state differential input voltage range                             | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_LP</sub>                           |

| Dominant state differential input voltage range                              | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)_LP</sub>                           |

| RECEIVER INPUT RESISTANCE                                                    |                                          | .()()                                                  |

| Differential internal resistance                                             | R <sub>Diff</sub>                        | R <sub>i(diff)</sub>                                   |

| Single ended internal resistance                                             | R <sub>CAN_H</sub><br>R <sub>CAN_L</sub> | R <sub>i(cm)</sub> (CANH)<br>R <sub>i(cm)</sub> (CANL) |

| RECEIVER INPUT RESISTANCE MATCHING                                           |                                          |                                                        |

| Matching a of internal resistance                                            | m <sub>R</sub>                           | R <sub>i(cm)(m)</sub>                                  |

| IMPLEMENTATION LOOP DELAY REQUIREMENT                                        |                                          | .(/()                                                  |

| Loop delay                                                                   | t <sub>Loop</sub>                        | <sup>t</sup> pd_rd<br><sup>t</sup> pd_dr               |

| DATA SIGNAL TIMING REQUIREMENTS for use with bit rates above 1 Mbit/s and up | o to 2 Mbit/s                            | • -                                                    |

| Transmitted recessive bit width @ 2 Mbit/s                                   | t <sub>Bit(Bus)</sub>                    | t <sub>Bit(Vi(diff))</sub>                             |

| Received recessive bit width @ 2 Mbit/s                                      | t <sub>Bit(RXD)</sub>                    | t <sub>Bit(RxDC)</sub>                                 |

|                                                                              | 2                                        |                                                        |

# ISO11898-2:2016 PARAMETER CROSS-REFERENCE TABLE (continued)

| ISO 11898-2:2016 Specification                                                              | NCV7451 Datashee                           |                            |  |  |  |  |

|---------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------|--|--|--|--|

| Parameter                                                                                   | Notation                                   | Symbol                     |  |  |  |  |

| DATA SIGNAL TIMING REQUIREMENTS for use with bit rates above 2 Mbit/s and up to 5 Mbit/s    |                                            |                            |  |  |  |  |

| Transmitted recessive bit width @ 5 Mbit/s                                                  | t <sub>Bit(Bus)</sub>                      | t <sub>Bit(Vi(diff))</sub> |  |  |  |  |

| Transmitted recessive bit width @ 5 Mbit/s                                                  | t <sub>Bit(RXD)</sub>                      | t <sub>Bit(RxDC)</sub>     |  |  |  |  |

| Received recessive bit width @ 5 Mbit/s                                                     | $\Delta t_{Rec}$                           | $\Delta t_{Rec}$           |  |  |  |  |

| MAXIMUM RATINGS OF V <sub>CAN_H</sub> , V <sub>CAN_L</sub> AND V <sub>DIFF</sub>            |                                            |                            |  |  |  |  |

| Maximum rating V <sub>Diff</sub>                                                            | V <sub>Diff</sub>                          | Vdiff                      |  |  |  |  |

| General maximum rating $V_{CAN\_H}$ and $V_{CAN\_L}$                                        | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub>   | CANH<br>CANL               |  |  |  |  |

| Optional: Extended maximum rating $V_{\mbox{CAN}\_\mbox{H}}$ and $V_{\mbox{CAN}\_\mbox{L}}$ | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub>   | NA                         |  |  |  |  |

| MAXIMUM LEAKAGE CURRENTS ON CAN_H AND CAN_L, UNPOWERED                                      |                                            |                            |  |  |  |  |

| Leakage current on CAN_H, CAN_L                                                             | I <sub>CAN_H</sub> ,<br>I <sub>CAN_L</sub> | ILI                        |  |  |  |  |

| BUS BIASING CONTROL TIMINGS                                                                 |                                            |                            |  |  |  |  |

| CAN activity filter time, long                                                              | t <sub>Filter</sub>                        | NA                         |  |  |  |  |

| CAN activity filter time, short                                                             | t <sub>Filter</sub>                        | t <sub>wake_filt</sub>     |  |  |  |  |

| Optional: Wake-up timeout, short                                                            | t <sub>Wake</sub>                          | NA                         |  |  |  |  |

| Optional: Wake-up timeout, long                                                             | t <sub>Wake</sub>                          | t <sub>wake_to</sub>       |  |  |  |  |

| Timeout for bus inactivity (Required for selective wake-up implementation only)             | t <sub>Silence</sub>                       | NA                         |  |  |  |  |

| Bus Bias reaction time (Required for selective wake-up implementation only)                 | t <sub>Bias</sub>                          | NA                         |  |  |  |  |

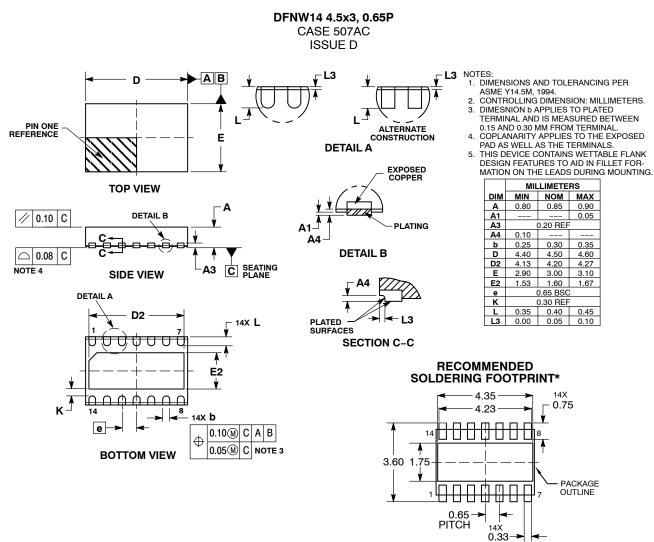

# PACKAGE DIMENSIONS

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products harmlese against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of pe

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative