**User manual**

#### **Document information**

| Information | Content                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | RDGD3160I3PH5EVB, GD3160, MPC5777C-DEVB, MPC5744P, MPC5775B/<br>E-EVB, S32S Design Studio SDK, FreeMASTER, AMMCL, MCAT                                                                                                         |

| Abstract    | This document is the user guide for the RDGD3160I3PH5EVB reference design and is intended for the engineers involved in the evaluation, design, implementation, and validation of single-channel gate driver for IGBT, GD3160. |

## **Revision History**

| Revision history     |          |                 |

|----------------------|----------|-----------------|

| Rev                  | Date     | Description     |

| RDGD3160I3PH5EVB v.1 | 20210812 | Initial version |

## Important notice

NXP provides the enclosed product(s) under the following conditions:

This reference design is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This reference design may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

## 1 Introduction

This document is the user guide for the RDGD3160I3PH5EVB reference design. This document is intended for the engineers involved in the evaluation, design, implementation, and validation of single-channel gate driver for IGBT, GD3160.

The scope of this document is to provide the user with information to evaluate the single channel gate driver for IGBT, GD3160. This document covers connecting the hardware, installing the software and tools, configuring the environment and using the kit.

The RDGD3160I3PH5EVB is a fully functional three-phase inverter evaluation board populated with six GD3160 gate drivers with fault management and supporting circuitry. This board supports SPI daisy chain communication for programming and communication with three high-side gate drivers and three low-side gate drivers independently.

This board has low-voltage and high-voltage isolation in conjunction with gate drive integrated galvanic signal isolation. Other supporting features on the board include desaturation short-circuit detection, IGBT temperature sensing, DC Link bus voltage monitoring, phase current sensing, and motor resolver excitation and signal processing connection circuitry. See GD3160 data sheet for additional gate drive features.

## 2 Finding kit resources and information on the NXP web site

The NXP analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal and power solutions. They incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost and improved performance in powering state-of-the-art systems.

NXP Semiconductors provides online resources for this reference design and its supported device(s) on <u>http://www.nxp.com</u>.

The information page for RDGD3160I3PH5EVB reference design is at www.nxp.com/ RDGD3160I3PH5EVB. The information page provides overview information, technical and functional specifications, ordering information, documentation, and software. The Get Started provides quick-reference information applicable to using the RDGD3160I3PH5EVB reference design, including the downloadable assets.

## 3 Getting started

Working with the RDGD3160I3PH5EVB requires the kit contents, additional hardware, and a Windows PC workstation with installed software.

## 3.1 Kit contents

- Assembled and tested RDGD3160I3PH5EVB (three-phase inverter populated with 5.0 V compatible gate driver devices) board in an anti-static bag

- Quick Start Guide

## 3.2 Additional hardware

In addition to the kit contents, the following hardware is necessary or beneficial when working with this kit.

- Microcontroller for SPI communication

- IGBT module Infineon HP Drive part FS820R08A6P2B

- DC link capacitor compatible with IGBT part FS820R08A6P2B

- HV power supply with protection shield and hearing protection

- · Current sensors for monitoring each phase current

- 12 V, 1.0 A DC power supply

- High sample rate digital oscilloscope with probes

- High-voltage differential voltage probe

## 3.3 Windows PC workstation

This reference design requires a Windows PC workstation. Meeting these minimum specifications should produce great results when working with this reference design.

• USB-enabled computer with Windows 7 or Windows 10

### 3.4 Software

Installing software is necessary to work with this reference design. All listed software is available on the reference design's information page at <u>http://www.nxp.com/</u> <u>RDGD3160I3PH5EVB</u>.

- S32S Design Studio IDE for power architecture

- Automotive Math and Motor Control Library (AMMCL)

- FreeMaster 2.0 runtime debugging tool

- Motor Control Application Tuning (MCAT)

- GD3160 Device Driver example code REV1.2

## 4 Getting to know the hardware

### 4.1 Kit overview

#### 4.1.1 RDGD3160I3PH5EVB features

- Capability to connect to HP Drive IGBT modules for full three-phase evaluation and development

- Daisy chain SPI communication (three high-side and three low-side gate drivers)

- Power supply which is jumper configurable for VEE negative or GND reference

- · Easy access power, ground, and signal test points

- 2 × 2 32 PCIe socket for interfacing MCU control

- Note: INTA pin is a new feature added to the GD3160. Not connected to MCU interface. See GD3160 data sheet for pin usage/features.

- Optional connection for DC bus voltage monitoring

- Compatible with MPC5777C-DEVB, MPC5775B/E-EVB, MPC5744P

### 4.1.2 Voltage domains, GD3160 pinout, logic header, and IGBT pinout

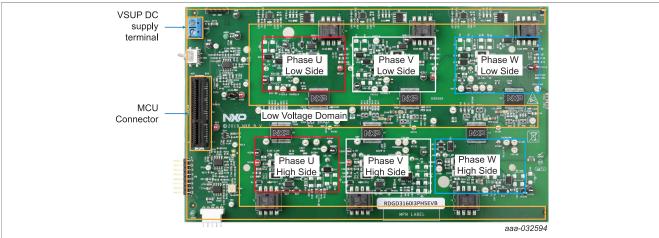

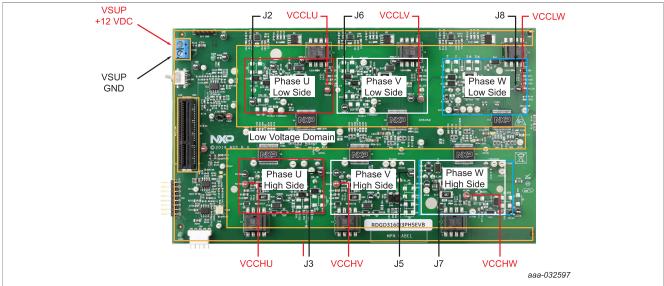

Low-voltage domain is an externally supplied 12 V DC (VSUP) primary supply for nonisolated circuits, typically supplied by vehicle battery. The low-voltage domain includes the interface between the MCU and GD3160 control registers and logic control.

Low-side driver and high-side driver domains are isolated high-voltage driver control domains for IGBT single phase connections and control circuits. Pins on bottom of board are designed to easily connect to three-phase IGBT module.

Figure 1. RDGD3160I3PH5EVB three-phase inverter board voltage domains and interfaces

#### 4.2 Featured components

#### 4.2.1 Advanced IGBT gate driver

#### 4.2.1.1 General description

The GD3160 is an advanced single channel gate driver for IGBTs. Integrated Galvanic isolation and low on-resistance drive transistors provide high charging and discharging current, low dynamic saturation voltage, and rail-to-rail gate voltage control.

Current and temperature sense minimizes IGBT stress during faults. Accurate and configurable under voltage lockout (UVLO) provides protection while ensuring sufficient gate drive voltage headroom.

The GD3160 autonomously manages severe faults and reports faults and status via the INTB pin and a SPI interface. It is capable of directly driving gates of most IGBTs. Self-test, control, and protection functions are included for design of high reliability systems (ASIL C/D). It meets the stringent requirements of automotive applications and is fully AEC-Q100 grade 1 qualified.

#### 4.2.1.2 GD3160 features

- · Compatible with current sense and temp sense IGBTs

- Fast short circuit protection for IGBT/SiC with DESAT and current sense feedback

- · Compliant with ASIL D ISO 26262 functional safety requirements

- · SPI interface for safety monitoring, programmability, and flexibility

- Integrated Galvanic signal isolation

- Integrated gate drive power stage capable of 15 A peak source and sink

- · Interrupt pin for fast response to faults

- Compatible with negative gate supply

- Compatible with 200 V to 1700 V IGBTs, power range > 125 kW

- AEC-Q100 grade 1 qualified

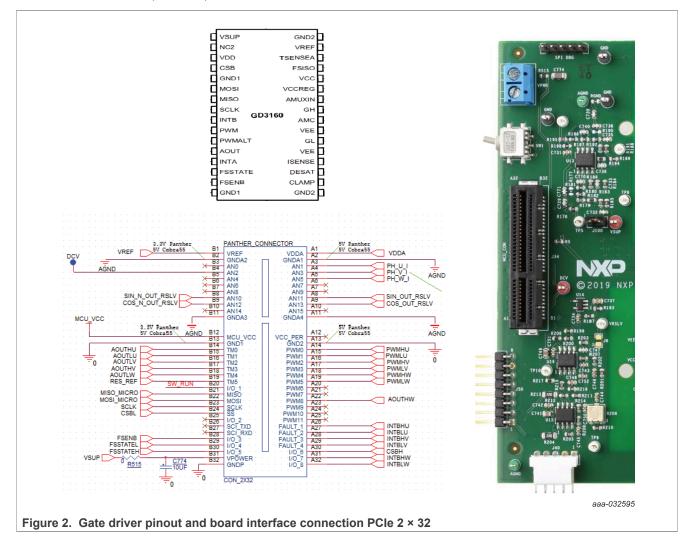

### 4.2.2 GD3160 pinout and MCU interface pinout

See GD3160 advanced IGBT/SiC gate driver data sheet for specific information about pinout, pin descriptions, specifications, and operating modes.

VSUP DC supply terminal is a low voltage input connection for supplying power to the low voltage non-isolated die and related circuitry. Typically supplied by vehicle battery +12 V DC.

MCU connector is a 2×32-pin PCIe interface connector for use with either MPC5744P, MPC5775B/E-EVB or MPC5777C 32-bit MCU board or any other MCU of preference. An MCU is needed for SPI communication and control of advanced IGBT gate drive devices (GD3160).

## RDGD3160I3PH5EVB Reference Design

| Table 1. PCle connect | or pin definitions |                                                          |

|-----------------------|--------------------|----------------------------------------------------------|

| Pin                   | Name               | Function                                                 |

| A1                    | VDDA               | Voltage reference resolver circuit                       |

| A2                    | GNDA1              | Analog ground                                            |

| A3                    | PH_U_I             | Current feedback phase U                                 |

| A4                    | PH_V_I             | Current feedback phase V                                 |

| A5                    | PH_W_I             | Current feedback phase W                                 |

| A6                    | n.c.               | not connected                                            |

| A7                    | n.c.               | not connected                                            |

| A8                    | SIN_OUT_RSLV       | Sine resolver signal                                     |

| A9                    | COS_OUT_RSLV       | Cosine resolver signal                                   |

| A10                   | n.c.               | not connected                                            |

| A11                   | GNDA4              | Analog ground                                            |

| A12                   | n.c.               | not connected                                            |

| A13                   | GND2               | Ground                                                   |

| A14                   | PWMHU              | Pulse width modulation high-side phase U                 |

| A15                   | PWMLU              | Pulse width modulation low-side phase U                  |

| A16                   | PWMHV              | Pulse width modulation high-side phase V                 |

| A17                   | PWMLV              | Pulse width modulation low-side phase V                  |

| A18                   | PWMHW              | Pulse width modulation high-side phase W                 |

| A19                   | PWMLW              | Pulse width modulation low-side phase W                  |

| A20                   | n.c.               | not connected                                            |

| A21                   | n.c.               | not connected                                            |

| A22                   | AOUTHW             | Analog output signal high-side phase W                   |

| A23                   | n.c.               | not connected                                            |

| A24                   | n.c.               | not connected                                            |

| A25                   | n.c.               | not connected                                            |

| A26                   | INTBHU             | GD3160 fault reporting pin for high-side phase U         |

| A27                   | INTBLU             | GD3160 fault reporting pin for low-side phase U          |

| A28                   | INTBHV             | GD3160 fault reporting pin for high-side phase V         |

| A29                   | INTBLV             | GD3160 fault reporting pin for low-side phase V          |

| A30                   | CSBH               | Chip select bar to high gate drive devices               |

| A31                   | INTBHW             | GD3160 fault reporting pin for high-side phase W         |

| A32                   | INTBLW             | GD3160 fault reporting pin for low-side phase W          |

| B1                    | VREF               | Voltage reference from MCU                               |

| B2                    | GNDA2              | Analog ground                                            |

| В3                    | NC                 | not connected                                            |

| B4                    | DCV                | Optional DC bus voltage monitoring (not used by default) |

| В5                    | n.c.               | not connected                                            |

| B6                    | n.c.               | not connected                                            |

| В7                    | n.c.               | not connected                                            |

| B8                    | SIN_N_OUT_RSLV     | Sine resolver signal                                     |

|                       |                    |                                                          |

## Table 1. PCIe connector pin definitions

UM11653

© NXP B.V. 2021. All rights reserved.

## RDGD3160I3PH5EVB Reference Design

| Pin | Name           | Function                                      |

|-----|----------------|-----------------------------------------------|

| В9  | COS_N_OUT_RSLV | Cosine resolver signal                        |

| B10 | n.c.           | not connected                                 |

| B11 | GNDA3          | Analog ground                                 |

| B12 | MCU_VCC        | MCU VCC regulator voltage                     |

| B13 | GND1           | Ground                                        |

| B14 | AOUTHU         | GD3160 analog output signal high-side U phase |

| B15 | AOUTLU         | GD3160 analog output signal low-side U phase  |

| B16 | AOUTLV         | GD3160 analog output signal low-side V phase  |

| B17 | AOUTHV         | GD3160 analog output signal high-side V phase |

| B18 | AOUTLW         | GD3160 analog output signal low-side W phase  |

| B19 | RES_REF        | Resolver reference voltage                    |

| B20 | SW_RUN         | Signal from onboard switch demo mode          |

| B21 | MISO_MICRO     | SPI slave out signal                          |

| B22 | MOSI_MICRO     | SPI slave in signal                           |

| B23 | SCLK           | SPI clock                                     |

| B24 | CSBL           | Chip select bar to low-side gate drivers      |

| B25 | n.c.           | not connected                                 |

| B26 | n.c.           | not connected                                 |

| B27 | n.c.           | not connected                                 |

| B28 | FSENB          | Fail-safe state enable bar                    |

| B29 | FSSTATEL       | Fail-safe state low-side                      |

| B30 | FSSATEH        | Fail-safe state high-side                     |

| B31 | VSUP           | 12 V voltage supply (low voltage domain)      |

| B32 | GNDP           | Ground connection (low voltage domain)        |

#### Table 1. PCle connector pin definitions...continued

## 4.2.3 Test points

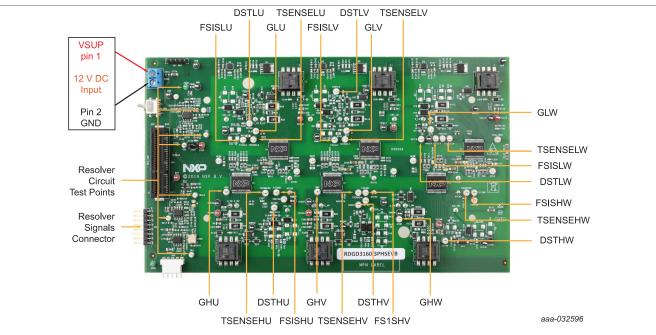

All test points are clearly marked on the board. The following figure shows the location of various test points.

### RDGD3160I3PH5EVB Reference Design

### Figure 3. RDGD3160I3PH5EVB test points

| Test point name  | Function                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| DCV              | Micro DC voltage                                                                                                           |

| DSTHU            | DESAT high-side U phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                             |

| DSTHV            | DESAT high-side V phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                             |

| DSTHW            | DESAT high-side W phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                             |

| DSTLU            | DESAT low-side U phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                              |

| DSTLV            | DESAT low-side V phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                              |

| DSTLW            | DESAT low-side W phase $V_{CE}$ desaturation connected to DESAT pin circuitry                                              |

| FSISHU           | Not used – for test purposes only                                                                                          |

| FSISHV           | Not used – for test purposes only                                                                                          |

| FSISLU           | Not used – for test purposes only                                                                                          |

| FSISLV           | Not used – for test purposes only                                                                                          |

| FSISLW           | Not used – for test purposes only                                                                                          |

| GHU              | Gate high-side U phase which is the charging pin of IGBT gate                                                              |

| GHV              | Gate high-side V phase which is the charging pin of IGBT gate                                                              |

| GHW              | Gate high-side W phase which is the charging pin of IGBT gate                                                              |

| GLU              | Gate low-side U phase which is the charging pin of IGBT gate                                                               |

| GLV              | Gate low-side V phase which is the charging pin of IGBT gate                                                               |

| GLW              | Gate low-side W phase which is the charging pin of IGBT gate                                                               |

| NCLU – NCHW      | INTA test point connections to respective gate drive devices.<br>INTA fault reporting and real time VGE or VCE monitoring. |

| Resolver circuit | Test points for internal signals of resolver circuit (see schematic for more information)                                  |

| SPI DBG          | SPI signal port for analyzing SPI signals (see schematic for signals)                                                      |

| TSENSEHU         | TSENSE high-side U phase connected to NTC temperature sense                                                                |

| TSENSEHV         | TSENSE high-side V phase connected to NTC temperature sense                                                                |

| JM11653          | All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved            |

#### RDGD3160I3PH5EVB Reference Design

| Test point name | Function                                                    |  |

|-----------------|-------------------------------------------------------------|--|

| TSENSEHW        | TSENSE high-side W phase connected to NTC temperature sense |  |

| TSENSELU        | TSENSE low-side U phase                                     |  |

| TSENSELV        | TSENSE low-side V phase                                     |  |

| TSENSELW        | TSENSE low-side W phase                                     |  |

## 4.2.4 Indicators

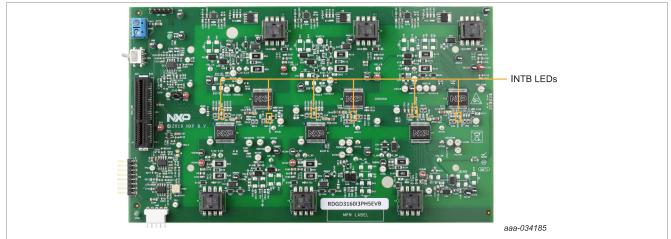

The RDGD3160I3PH5EVB evaluation board contains LEDs as visual indicators on the board.

Figure 4. RDGD3160I3PH5EVB indicator locations

#### Table 2. RDGD3160I3PH5EVB indicator descriptions

| Name      | Description                                                        |

|-----------|--------------------------------------------------------------------|

| INTB LEDs | Indicate a GD3160 interrupt has occurred on that gate drive device |

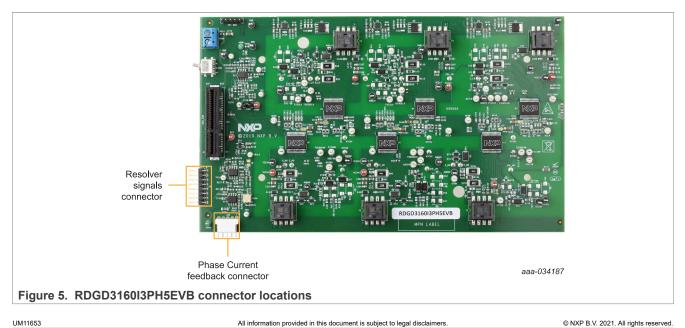

## 4.2.5 Connectors

### RDGD3160I3PH5EVB Reference Design

| Table 3. RDGD3160I3PH5EVB connector descriptions |                                                                  |  |

|--------------------------------------------------|------------------------------------------------------------------|--|

| Name                                             | Description                                                      |  |

| Phase current feedback connector                 | Current feedback connections from U, V, and W phases             |  |

| Resolver signals connector                       | Resolver excitation signals (see schematic for more information) |  |

## 4.2.6 Power supply and jumper configuration

#### Figure 6. Power supply and jumper locations

| Name       | Function                                                                                                                                                                                                  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2         | <ul> <li>Low-side phase U VEE select. Negative voltage supply for gate of IGBT.</li> <li>1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V</li> <li>2-3 VEE voltage equal to GND2</li> </ul>  |

| 13         | <ul> <li>High-side phase U VEE select. Negative voltage supply for gate of IGBT.</li> <li>1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V</li> <li>2-3 VEE voltage equal to GND2</li> </ul> |

| J5         | <ul> <li>High-side phase V VEE select. Negative voltage supply for gate of IGBT.</li> <li>1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V</li> <li>2-3 VEE voltage equal to GND2</li> </ul> |

| Je         | Low-side phase V VEE select. Negative voltage supply for gate of IGBT.<br>• 1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V<br>• 2-3 VEE voltage equal to GND2                              |

| J7         | <ul> <li>High-side phase W VEE select. Negative voltage supply for gate of IGBT.</li> <li>1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V</li> <li>2-3 VEE voltage equal to GND2</li> </ul> |

| 8L         | <ul> <li>Low-side phase W VEE select. Negative voltage supply for gate of IGBT.</li> <li>1-2 negative VEE voltage (default) typically -5.0 V to -8.0 V</li> <li>2-3 VEE voltage equal to GND2</li> </ul>  |

| J100       | Used for routing DC voltage from VSUP connection terminal                                                                                                                                                 |

| SJ1 to SJ6 | Solder jumpers used for 5.0 V operation connecting VSUP to VDD on each gate drive device                                                                                                                  |

| SW1        | Not used (internal purposes only)                                                                                                                                                                         |

| VCCHU      | High-side phase U VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V)                                                                                                               |

### RDGD3160I3PH5EVB Reference Design

| Name          | Function                                                                                    |

|---------------|---------------------------------------------------------------------------------------------|

| VCCHV         | High-side phase V VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V) |

| VCCHW         | High-side phase W VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V) |

| VCCLU         | Low-side phase U VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V)  |

| VCCLV         | Low-side phase V VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V)  |

| VCCLW         | Low-side phase W VCC voltage test point<br>Isolated positive voltage supply (15 V to 18 V)  |

| VSUP +12 V DC | VSUP low voltage positive supply connection (+12 V DC)                                      |

| VSUP GND      | VSUP low voltage supply ground connection (GND1)                                            |

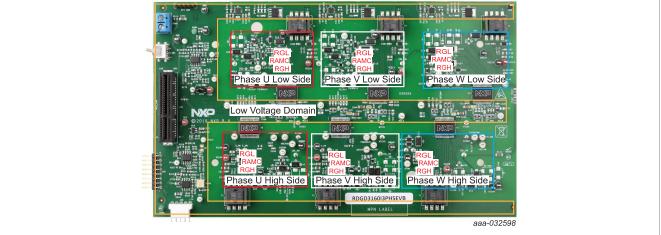

### 4.2.7 Gate drive resistors

- RGH gate high resistor in series with the GH pin at the output of the GD3160 highside driver and IGBT gate that controls the turn on current for IGBT gate.

- RGL gate low resistor in series with the GL pin at the output of the GD3160 low-side driver and IGBT gate that controls the turn off current for IGBT gate.

- RAMC series resistor between IGBT gate and AMC input pin of the GD3160 highside/low-side driver for gate sensing and Active Miller clamping.

Figure 7. Gate drive resistors for each phase high-side and low-side

### RDGD3160I3PH5EVB Reference Design

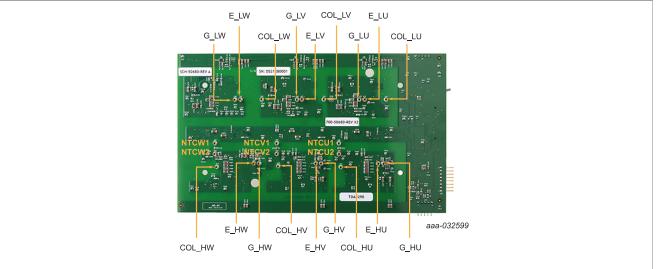

## 4.2.8 IGBT pin connections

### Figure 8. IGBT connection pins

| Connection name | Pin description                                                           |

|-----------------|---------------------------------------------------------------------------|

| COL_HU          | Collector high-side U phase                                               |

| COL_HV          | Collector high-side V phase                                               |

| COL_HW          | Collector high-side W phase                                               |

| COL_LU          | Collector low-side U phase                                                |

| COL_LV          | Collector low-side V phase                                                |

| COL_LW          | Collector low-side W phase                                                |

| E_HU            | Emitter high-side U phase                                                 |

| E_HV            | Emitter high-side V phase                                                 |

| E_HW            | Emitter high-side W phase                                                 |

| E_LU            | Emitter low-side U phase                                                  |

| E_LV            | Emitter low-side V phase                                                  |

| E_LW            | Emitter low-side W phase                                                  |

| G_HU            | Gate high-side U phase                                                    |

| G_HV            | Gate high-side V phase                                                    |

| G_HW            | Gate high-side W phase                                                    |

| G_LU            | Gate low-side U phase                                                     |

| G_LV            | Gate low-side V phase                                                     |

| G_LW            | Gate low-side W phase                                                     |

| NTC1            | Negative temperature coefficient resistor connections 1 U, V, and W phase |

| NTC2            | Negative temperature coefficient resistor connections 2 U, V, and W phase |

## 4.3 Schematic, board layout, and bill of materials

The schematic, board layout, and bill of materials for the RDGD3160I3PH5EVB reference design are available at <u>http://www.nxp.com/RDGD3160I3PH5EVB</u>.

### RDGD3160I3PH5EVB Reference Design

## 5 Configuring the hardware for startup

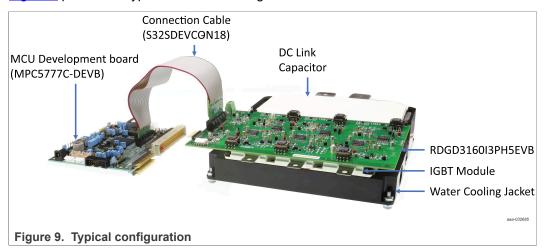

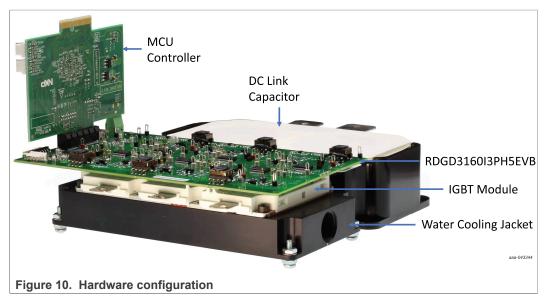

Figure 9 presents a typical hardware configuration.

To configure the hardware as illustrated in Figure 9, complete the following procedure:

- Assemble IGBT module with water cooling jacket if desired and properly attach to DC Link capacitor positive and negative high-voltage supply connections across U, V, and W phases.

- 2. WARNING

#### **Operational hazard – DC link capacitors**

DC link capacitors store a high amount of energy.

- Observe all proper safety precautions on all applicable equipment.

- Use proper PPE (personal protective equipment).

- Observe proper isolation techniques for all measurements.

- Attach RDGD3160I3PH5EVB to the IGBT module. Ensure that all board socket connection pins are properly seated onto the IGBT pin connections. The board socket pins are intended for easy attachment and deattachment to IGBT module without damaging IGBT connection pins.

- 4. Connect motor:

- a. Connect output of IGBT module each phase U, V, and W to each of the respective U, V, W connections on the desired three-phase motor.

- b. For running motor in closed loop motor control, connect resolver signals from motor resolver connection to the resolver pin connections on the RDGD3160I3PH5EVB. See schematics for J50 header signal connections on the RDGD3160I3PH5EVB board.

- c. For running motor in closed loop motor control, connect current sensors from each phase U, V, and W (current sensors are not included with RDGD3160I3PH5EVB) and connect the respective signals from the current sensors to the phase current feedback pin connections of the RDGD3160I3PH5EVB. See schematics for J40 header signal connections on the RDGD3160I3PH5EVB board.

- 5. Connect DC power:

- a. Connect a low voltage DC power supply to the RDGD3160I3H5EVB at the VSUP connection terminal (12 V DC with a minimum 1.0 A supply). Ensure that J100 jumper is in place.

- b. Connect a low voltage DC supply to MCU controller board and connect USB cable from MCU controller to desired computer for software driven motor control.

- C. WARNING

#### Lethal voltage and fire ignition hazard

The non-insulated high voltages that are present when operating this product, constitute a risk of electric shock, personal injury, death and/or ignition of fire. This product is intended for evaluation purposes only. It shall be operated in a designated test area by personnel qualified according to local requirements and labor laws to work with non-insulated mains voltages and highvoltage circuits. This product shall never be operated unattended.

- d. Connect high voltage/high current DC supply (use recommended voltage and current for desired motor) to positive and negative connections on DC Link capacitor to supply three-phase motor DC link voltage.

- Attach 2x32 PCIe cable (S32SDEV-CON18) supplied with kit to the RDGD3160I3PH5EVB and MCU controller board such as the MPC5777C-DEVB. This cable is keyed and is compatible with interface port on MPC5777C-DEVB.

## 6 Installing and configuring software and tools

## 6.1 Software development tools

NXP has software development tools available for use with the NXP MPC5777C development board (DEVB). The development board is intended to provide a platform for easy customer evaluation of the MPC5777C microcontroller and to facilitate hardware and software development. The development board can be used for Powertrain/ Inverters/BMS/Automotive Ethernet, etc. The latest product information is available at www.nxp.com/MPC5777C.

List of Development software:

- S32S Design Studio IDE for power architecture: The **S32S design studio for power architecture** IDE installed on a Windows PC workstation enables editing, compiling and debugging of source code designs. SDK supports several devices including MPC5777C. For more information, refer to S32DS-PA SDK for power architectures at <u>http://www.nxp.com/S32SDK-PA</u>.

- Automotive Math and Motor Control Library (AMMCL): Automotive Math and Motor Control Library (AMMCL) is a precompiled software library containing the building blocks for a wide range of motor control and general mathematical applications. For more information and to download AMMCL, refer to Automotive Math and Motor Control Library Set for MPC577xC at <u>http://www.nxp.com/</u> <u>AUTOMCLIB</u>.

- FreeMaster 2.0 runtime debugging tool: FreeMASTER runtime debugging tool is a separate download and can also be used in conjunction with the MCU code developed with S32DS as a user-friendly realtime debug monitor, graphical control panel, and data visualization tool for application development and information management. See FreeMASTER runtime debugging tool at http://www.nxp.com/freemaster.

- Motor Control Application Tuning (MCAT): Motor Control Application Tuning (MCAT) is a FreeMASTER plug-in tool intended for the development of PMSM FOC and BLDC motor control applications. For more information and to download MCAT, refer to MCAT at <a href="http://www.nxp.com/MCAT">http://www.nxp.com/MCAT</a>.

- Example code, GD3160 Device Driver notes and GD3160 Device Driver Reference notes:

**GD3160 Device Driver example code REV1.2** provides a basis to get started and begin software development for the desired motor control. See GD3160 Device Driver Example Code (REV 1.2 or later) at <u>http://www.nxp.com/GD3160-DRIVER</u>.

## 7 References

[1] **RDGD3160I3PH5EVB** — detailed information on this board, including documentation, downloads, and software and tools

http://www.nxp.com/RDGD3160I3PH5EVB

- [2] **GD3160** product information on Advanced single-channel gate driver for Insulated Gate Bipolar Transistors <u>http://www.nxp.com/GD3160</u>

- [3] MPC5777C ultra-reliable MCU for automotive and industrial engine management <u>http://www.nxp.com/MPC5777C</u>

- [4] **MPC5744P** ultra-reliable MCU for automotive and industrial safety applications <u>https://www.nxp.com/MPC574xP</u>

- [5] MPC5775B/E-EVB <u>http://www.nxp.com/MPC5775b-e-evb</u>

#### RDGD3160I3PH5EVB Reference Design

## 8 Legal information

## 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## 8.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial

sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Hazardous voltage** — Although basic supply voltages of the product may be much lower, circuit voltages up to 60 V may appear when operating this product, depending on settings and application. Customers incorporating or otherwise using these products in applications where such high voltages may appear during operation, assembly, test etc. of such application, do so at their own risk. Customers agree to fully indemnify NXP Semiconductors for any damages resulting from or in connection with such high voltages. Furthermore, customers are drawn to safety standards (IEC 950, EN 60 950, CENELEC, ISO, etc.) and other (legal) requirements applying to such high voltages.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 8.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

UM11653

© NXP B.V. 2021. All rights reserved.

RDGD3160I3PH5EVB Reference Design

NXP — wordmark and logo are trademarks of NXP B.V.

## RDGD3160I3PH5EVB Reference Design

## **Tables**

| Tab. 1. | PCIe connector pin definitions8 |

|---------|---------------------------------|

| Tab. 2. | RDGD3160I3PH5EVB indicator      |

|         | descriptions11                  |

## Figures

| Fig. 1. | RDGD3160I3PH5EVB three-phase inverter   |

|---------|-----------------------------------------|

|         | board voltage domains and interfaces    |

| Fig. 2. | Gate driver pinout and board interface  |

|         | connection PCIe 2 × 327                 |

| Fig. 3. | RDGD3160I3PH5EVB test points 10         |

| Fig. 4. | RDGD3160I3PH5EVB indicator locations 11 |

| Fig. 5. | RDGD3160I3PH5EVB connector locations 11 |

| Tab. 3. | RDGD3160I3PH5EVB connector |    |

|---------|----------------------------|----|

|         | descriptions               | 12 |

| Fig. 6.  | Power supply and jumper locations         | .12  |

|----------|-------------------------------------------|------|

| Fig. 7.  | Gate drive resistors for each phase high- |      |

|          | side and low-side                         | . 13 |

| Fig. 8.  | IGBT connection pins                      | .14  |

| Fig. 9.  | Typical configuration                     | .15  |

| Fig. 10. | Hardware configuration                    | . 16 |

## RDGD3160I3PH5EVB Reference Design

## Contents

| 1       | Introduction                             | 4  |

|---------|------------------------------------------|----|

| 2       | Finding kit resources and information on |    |

|         | the NXP web site                         | 4  |

| 3       | Getting started                          | 4  |

| 3.1     | Kit contents                             | 4  |

| 3.2     | Additional hardware                      | 5  |

| 3.3     | Windows PC workstation                   | 5  |

| 3.4     | Software                                 | 5  |

| 4       | Getting to know the hardware             |    |

| 4.1     | Kit overview                             |    |

| 4.1.1   | RDGD3160I3PH5EVB features                | 5  |

| 4.1.2   | Voltage domains, GD3160 pinout, logic    |    |

|         | header, and IGBT pinout                  | 6  |

| 4.2     | Featured components                      | 6  |

| 4.2.1   | Advanced IGBT gate driver                | 6  |

| 4.2.1.1 | General description                      | 6  |

| 4.2.1.2 | GD3160 features                          | 6  |

| 4.2.2   | GD3160 pinout and MCU interface pinout   | 7  |

| 4.2.3   | Test points                              | 9  |

| 4.2.4   | Indicators                               | 11 |

| 4.2.5   | Connectors                               | 11 |

| 4.2.6   | Power supply and jumper configuration    |    |

| 4.2.7   | Gate drive resistors                     | 13 |

| 4.2.8   | IGBT pin connections                     | 14 |

| 4.3     | Schematic, board layout, and bill of     |    |

|         | materials                                |    |

| 5       | Configuring the hardware for startup     | 15 |

| 6       | Installing and configuring software and  |    |

|         | tools                                    |    |

| 6.1     | Software development tools               |    |

| 7       | References                               |    |

| 8       | Legal information                        | 18 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 12 August 2021 Document identifier: UM11653