# 5 kV<sub>rms</sub> 4.5-A/9-A Isolated Dual Channel Gate Driver

# NCV51561

The NCV51561 are isolated dual-channel gate drivers with 4.5-A/9-A source and sink peak current respectively. They are designed for fast switching to drive power MOSFETs, and SiC MOSFET power switches. The NCV51561 offers short and matched propagation delays.

Two independent and 5 kV $_{rms}$  internal galvanic isolation from input to each output and internal functional isolation between the two output drivers allows a working voltage of up to 1500 V $_{DC}$ . This driver can be used in any possible configurations of two low side, two high–side switches or a half–bridge driver with programmable dead time.

An ENA/DIS pin shutdowns both outputs simultaneously when set low or high for ENABLE or DISABLE mode respectively.

The NCV51561 offers other important protection functions such as independent under-voltage lockout for both gate drivers and a Dead Time adjustment function.

#### **Features**

- 4.5 A Peak Source, 9 A Peak Sink Output Current Capability

- Flexible: Dual Low-Side, Dual High-Side or Half-Bridge Gate Driver

- Independent UVLO Protections for Both Output Drivers

- Output Supply Voltage from 6.5 V to 30 V with 5-V and 8-V for MOSFET, 13-V and 17-V UVLO for SiC, Thresholds

- Common Mode Transient Immunity CMTI > 200 V/ns

- Propagation Delay Typical 36 ns with

- 5 ns Max Delay Matching per Channel

- 5 ns Max Pulse-Width Distortion

- User Programmable Input Logic

- Single or Dual-Input Modes via ANB

- ENABLE or DISABLE Mode

- User Programmable Dead–Time

- AEC-Q100 Qualified for Automotive Application Requirements

- Isolation & Safety

- ◆ 5 kV<sub>RMS</sub> Isolation for 1 Minute (per UL1577 Requirements) and 1500 V Peak Differential Voltage between Output Channels

- ♦ 8000 V<sub>PK</sub> Reinforced Isolation Voltage (per VDE0884–11 Requirements)

- ◆ CQC Certification per GB4943.1-2011

- ◆ SGS FIMO Certification per IEC 62386-1

- These are Pb-Free Devices

## **Typical Applications**

- On-board Chargers

- xEV DC-DC Converters

- Traction Inverters

- Charging Stations

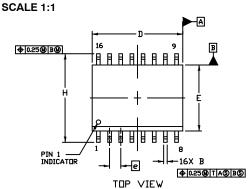

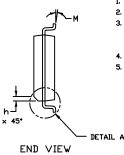

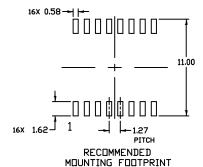

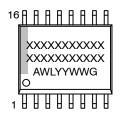

#### **MARKING DIAGRAM**

NCV51561 = Specific Device Code

X = A or B or C or D for UVLO Option Y = A or B for ENABLE/DISABLE

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

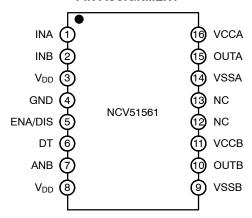

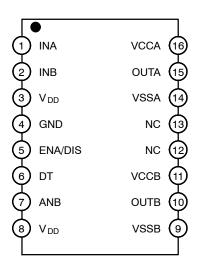

#### **PIN ASSIGNMENT**

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 31 of this data sheet.

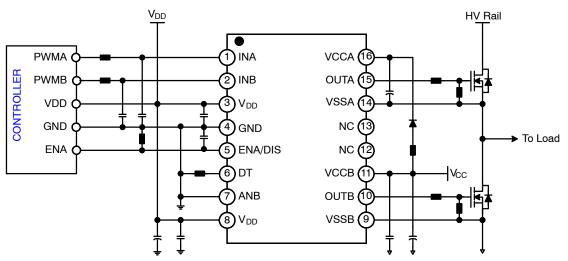

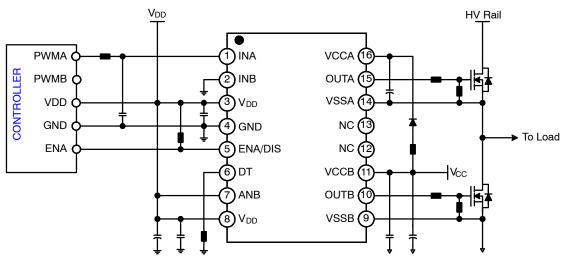

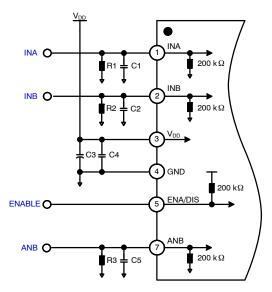

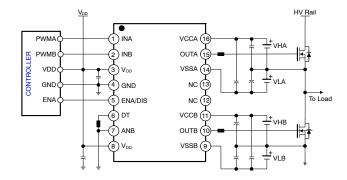

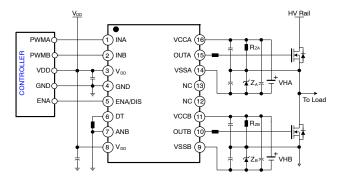

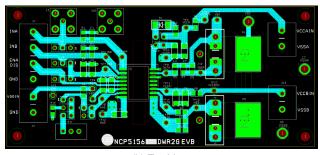

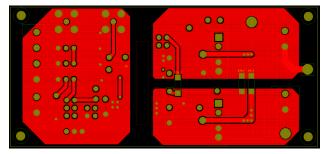

# TYPICAL APPLICATION CIRCUIT

(a) High and Low Side MOSFET Gate Drive for ENABLE Version

(b) High and Low Side MOSFET Gate Drive for DISABLE Version

(c) High and Low Side MOSFET Gate Drive with PWM Controller for ENABLE Version

Figure 1. Application Schematic

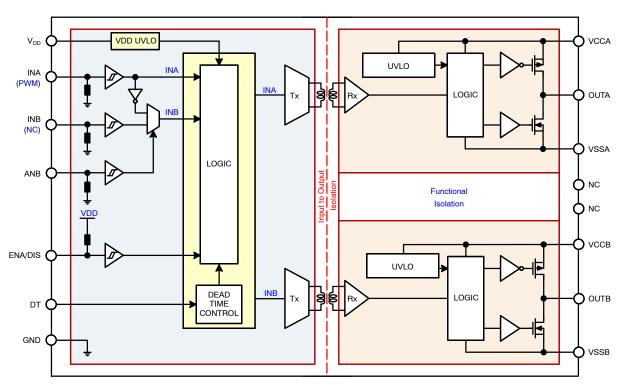

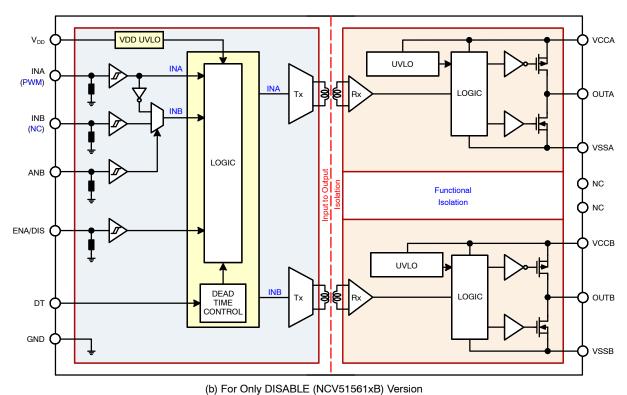

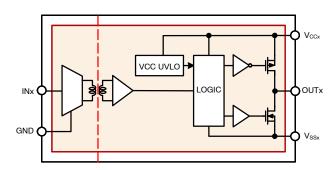

# **FUNCTIONAL BLOCK DIAGRAM**

(a) For Only ENABLE (NCV51561xA) Version

Figure 2. Simplified Block Diagram

# **FUNCTIONAL TABLE**

|         |          | INPUT |     |     |                                  | UVLO                             |                                  |            | GATE DRIVE OUTPUT |  |  |

|---------|----------|-------|-----|-----|----------------------------------|----------------------------------|----------------------------------|------------|-------------------|--|--|

| ENA/DIS | (Note 3) |       |     |     |                                  | Outpu                            | ıt Side                          |            |                   |  |  |

| ENABLE  | DISABLE  | ANB   | INA | INB | Input Side<br>(V <sub>DD</sub> ) | Channel A<br>(V <sub>CCA</sub> ) | Channel B<br>(V <sub>CCB</sub> ) | OUTA       | ОИТВ              |  |  |

| Х       | Х        | Х     | Х   | Х   | Active                           | Х                                | Х                                | L          | L                 |  |  |

| Х       | Х        | Х     | Х   | Х   | Х                                | Active                           | Active                           | L          | L                 |  |  |

| Н       | L        | L     | Х   | L   | Inactive                         | Active                           | Inactive                         | L          | L                 |  |  |

| Н       | L        | L     | Х   | Н   | Inactive                         | Active                           | Inactive                         | L          | Н                 |  |  |

| Н       | L        | L     | L   | Х   | Inactive                         | Inactive                         | Active                           | L          | L                 |  |  |

| Н       | L        | L     | Н   | Х   | Inactive                         | Inactive                         | Active                           | Н          | L                 |  |  |

| L       | Н        | L     | Х   | Х   | Inactive                         | Inactive                         | Inactive                         | L          | L                 |  |  |

| Н       | L        | L     | L   | L   | Inactive                         | Inactive                         | Inactive                         | L          | L                 |  |  |

| Н       | L        | L     | L   | Н   | Inactive                         | Inactive                         | Inactive                         | L          | Н                 |  |  |

| Н       | L        | L     | Н   | Н   | Inactive                         | Inactive                         | Inactive                         | L (Note 5) | L (Note 5)        |  |  |

|         |          |       |     |     | Inactive                         | Inactive                         | Inactive                         | H (Note 6) | H (Note 6)        |  |  |

| Н       | L        | Н     | L   | Х   | Inactive                         | Active                           | Inactive                         | L          | Н                 |  |  |

| Н       | L        | Н     | Н   | Х   | Inactive                         | Active                           | Inactive                         | L          | L                 |  |  |

| Н       | L        | Н     | L   | Х   | Inactive                         | Inactive                         | Active                           | L          | L                 |  |  |

| Н       | L        | Н     | Н   | Х   | Inactive                         | Inactive                         | Active                           | Н          | L                 |  |  |

| L       | Н        | Н     | Х   | Х   | Inactive                         | Inactive                         | Inactive                         | L          | L                 |  |  |

| Н       | L        | Н     | L   | Х   | Inactive                         | Inactive                         | Inactive                         | L          | Н                 |  |  |

| Н       | L        | Н     | Н   | Х   | Inactive                         | Inactive                         | Inactive                         | Н          | L                 |  |  |

- "L" means that LOW, "H" means that HIGH and X: Any Status

Inactive means that V<sub>DD</sub>, V<sub>CCA</sub>, and V<sub>CCB</sub> are above UVLO threshold voltage (Normal operation)

Active means that UVLO disables the gate driver output stage.

Disables both gate drive output when the ENA/DIS pin is LOW in ENABLE version, which is default is HIGH, if this pin is open.

Enables both gate drive output when the ENA/DIS pin is LOW in DISABLE version, which is default is LOW, if this pin is open.

When the ANB pin is HIGH, OUTA and OUTB are complementary outputs from PWM input signal on the INA pin regardless the INB signal.

- 5. DT pin is left open or programmed with R<sub>DT</sub>.

- 6. DT pin pulled to V<sub>DD</sub>.

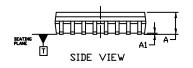

# **PIN CONNECTIONS**

Figure 3. Pin Connections – SOIC-16 WB (Top View)

## **PIN DESCRIPTION**

| Pin No. | Symbol           | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INA              | Input  | Logic Input for Channel A with internal pull-down resistor to GND                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2       | INB              | Input  | Logic Input for Channel B with internal pull-down resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3, 8    | $V_{DD}$         | Power  | Input-side Supply Voltage. It is recommended to place a bypass capacitor from V <sub>DD</sub> to GND.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4       | GND              | Power  | Ground Input-side. (all signals on input-side are referenced to this pin)                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5       | ENA/DIS          | Input  | Logic Input High Enables Both Output Channels with Internal pull-up resistor for an ENABLE version. Conversely, Logic Input High disables Both Output Channels with Internal pull-down resistor for the DISABLE version.                                                                                                                                                                                                                                                                                   |

| 6       | DT               | Input  | Input for programmable Dead–Time It provides three kind of operating modes according to the DT pin voltage as below.                                                                                                                                                                                                                                                                                                                                                                                       |

| 7       | ANB              | Input  | Logic Input to change the input signal configuration with internal pull-down resistor to GND. OUTA and OUTB work as complementary outputs from INA PWM input signal regardless of the INB signal when the ANB pin is high. It is recommended to tie this pin to GND or floating (not recommended) if the ANB pin is not used to achieve better noise immunity. The ANB pin has a typical 3.3 $\mu$ s internal filter to improve noise immunity but we recommend to tie to GND, if the ANB pin is not used. |

| 9       | VSSB             | Power  | Ground for Channel B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10      | OUTB             | Output | Output for Channel B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11      | V <sub>CCB</sub> | Power  | Supply Voltage for Output Channel B. It is recommended to place a bypass capacitor from V <sub>CCB</sub> to VSSB.                                                                                                                                                                                                                                                                                                                                                                                          |

| 12, 13  | NC               | -      | No Connection; Keep pin floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14      | VSSA             | Power  | Ground for Channel A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15      | OUTA             | Output | Output of Channel A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16      | V <sub>CCA</sub> | Power  | Supply Voltage for Output Channel A. It is recommended to place a bypass capacitor from V <sub>CCA</sub> to VSSA.                                                                                                                                                                                                                                                                                                                                                                                          |

# **SAFETY AND INSULATION RATINGS**

| Symbol |                                                                                                                               | Parameter                                            |             | Min.            | Тур.      | Max. | Unit             |

|--------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------|-----------------|-----------|------|------------------|

|        |                                                                                                                               |                                                      | < 150 VRMS  |                 | I–IV      |      |                  |

|        | Table 1 Rated Ma                                                                                                              | ifications per DIN VDE 0110/1.89<br>ains Voltage     | < 300 VRMS  |                 | I–IV      |      |                  |

|        |                                                                                                                               |                                                      | < 450 VRMS  |                 | I–IV      |      |                  |

|        |                                                                                                                               |                                                      | < 600 VRMS  |                 | I–IV      |      |                  |

|        |                                                                                                                               |                                                      | < 1000 VRMS |                 | 1–111     |      |                  |

|        | Comparative Trac                                                                                                              | arative Tracking Index (DIN IEC 112/VDE 0303 Part 1) |             |                 |           |      |                  |

| СТІ    | Climatic Classification                                                                                                       |                                                      |             |                 | 40/125/21 |      |                  |

|        | Pollution Degree                                                                                                              |                                                      | 2           |                 |           |      |                  |

| VPR    | Input – to – Output Test Voltage, Method b, VIORM × 1.875 = VPR, 100% Production Test with tm = 1 s, Partial Discharge < 5 pC |                                                      |             | 2250            |           |      | V <sub>PK</sub>  |

| VIORM  | Maximum Repeti                                                                                                                | tive Peak Isolation Voltage                          |             | 1200            |           |      | $V_{PK}$         |

| VIOWM  | Maximum Workin                                                                                                                | ng Isolation Voltage                                 |             | 1200            |           |      | $V_{DC}$         |

| VIOTM  | Maximum Transie                                                                                                               | ent Isolation Voltage                                |             | 8000            |           |      | $V_{PK}$         |

| ECR    | External Creepag                                                                                                              | де                                                   |             | 8.0             |           |      | mm               |

| Ecl    | External Clearan                                                                                                              | ce                                                   |             | 8.0             |           |      | mm               |

| DTI    | Insulation Thickn                                                                                                             | ess                                                  |             | 17.3            |           |      | um               |

| Rio    | Insulation Resistance at T <sub>S</sub> , VIO = 500 V                                                                         |                                                      |             | 10 <sup>9</sup> |           |      | Ω                |

| JL1577 | •                                                                                                                             |                                                      |             |                 | l l       |      |                  |

| Viso   | Withstand isolation voltage                                                                                                   |                                                      |             | 5000            |           |      | V <sub>RMS</sub> |

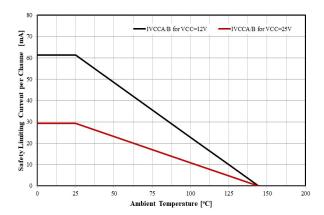

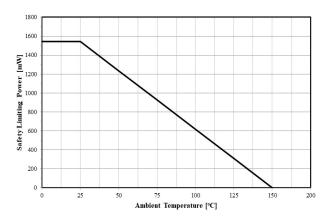

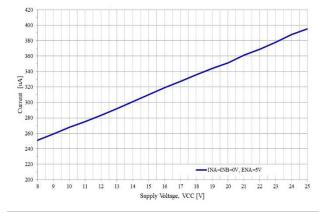

## **SAFETY LIMITING VALUE**

| Symbol         | Parameter                    | Test Condition                                                                           | Side                  | Min. | Тур. | Max. | Unit |

|----------------|------------------------------|------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| I <sub>S</sub> | Safety output supply current | $R_{\theta JA}$ = 81 °C/W, VCCA = VCCB = 12 V, $T_A$ = 25 °C, $T_J$ =150 °C See Figure 4 | DRIVER A,<br>DRIVER B |      |      | 61   | mA   |

|                |                              | $R_{\theta JA}$ = 81 °C/W, VCCA = VCCB = 25 V, $T_A$ = 25 °C, $T_J$ =150 °C See Figure 4 | DRIVER A,<br>DRIVER B |      |      | 29   | mA   |

| P <sub>S</sub> | Safety supply power          | $R_{\theta JA} = 81  ^{\circ}C/W, T_A = 25  ^{\circ}C, T_J = 150  ^{\circ}C$             | INPUT                 |      |      | 60   | mW   |

|                |                              | See Figure 5                                                                             | DRIVER A              |      |      | 720  |      |

|                |                              |                                                                                          | DRIVER A              |      |      | 720  |      |

|                |                              |                                                                                          | TOTAL                 |      |      | 1500 |      |

| T <sub>S</sub> | Safety temperature           |                                                                                          |                       |      |      | 150  | °C   |

## **MAXIMUM RATINGS**

| Sym                      | nbol                             | Parameter                                   | Min  | Max                                               | Unit |

|--------------------------|----------------------------------|---------------------------------------------|------|---------------------------------------------------|------|

| V <sub>DD</sub> to       | GND                              | Power Supply Voltage – Input Side (Note 8)  | -0.3 | 5.5                                               | V    |

| V <sub>CCA</sub> – VSSA, | V <sub>CCB</sub> – VSSB          | Power Supply Voltage – Driver Side (Note 9) | -0.3 | 33                                                | V    |

| OUTA to VSSA,            | OUTB to VSSB                     | Driver Output Voltage (Note 9)              | -0.3 | V <sub>CCA</sub> + 0.3,<br>V <sub>CCB</sub> + 0.3 | V    |

|                          | OUTB to VSSB,<br>00 ns (Note 10) |                                             | -2   | V <sub>CCA</sub> + 0.3,<br>V <sub>CCB</sub> + 0.3 | V    |

| INA, INB,                | and ANB                          | Input Signal Voltages (Note 8)              | -0.3 | 20                                                | V    |

| ,                        | sient for 50 ns<br>e 10)         |                                             | -5   | 20                                                | V    |

| ENA                      | /DIS                             | Input Signal Voltages (Note 8)              | -0.3 | 5.5                                               | V    |

| ENA/DIS Tran<br>(Note    | nsient for 50ns<br>e 10)         |                                             | -5   | 5.5                                               | V    |

| D                        | T                                | Dead Time Control (Note 8)                  | -0.3 | V <sub>DD</sub> + 0.3                             | V    |

| VSSA-VSSB,               | VSSB-VSSA                        | Channel to Channel Voltage                  | 1500 | -                                                 | V    |

| Т                        | J                                | Junction Temperature                        | -40  | +150                                              | °C   |

| Т                        | S                                | Storage Temperature                         | -65  | +150                                              | °C   |

| Electrostatic            | HBM (Note 11)                    | Human Body Model                            | -    | ±2                                                | kV   |

| Discharge<br>Capability  | CDM (Note 11)                    | Charged Device Model                        | -    | ±1                                                | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 7. Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 8. All voltage values are given with respect to GND pin.

- 9. All voltage values are given with respect to VSSA or VSSB pin.

10. This parameter verified by design and bench test, not tested in production.

- 11. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101)

- Latch up Current Maximum Rating: ≤100 mA per JEDEC standard: JESD78F.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol                              | Rating                                              |                   | Min  | Max  | Unit |

|-------------------------------------|-----------------------------------------------------|-------------------|------|------|------|

| V <sub>DD</sub>                     | Power Supply Voltage – Input Side                   |                   | 3.0  | 5.0  | V    |

| V <sub>CCA</sub> , V <sub>CCB</sub> | Power Supply Voltage – Driver Side 5–V UVLO Version |                   | 6.5  | 30   | V    |

|                                     |                                                     | 8-V UVLO Version  | 9.5  | 30   | V    |

|                                     |                                                     | 13-V UVLO Version | 14.5 | 30   | V    |

|                                     |                                                     | 17-V UVLO Version | 18.5 | 30   | V    |

| V <sub>IN</sub>                     | Logic Input Voltage at Pins INA, INB, and ANB       |                   | 0    | 18   | V    |

| V <sub>ENA/DIS</sub>                | Logic Input Voltage at Pin ENA/DIS                  |                   | 0    | 5.0  | V    |

| T <sub>A</sub>                      | Ambient Temperature                                 | -40               | +125 | °C   |      |

| TJ                                  | Junction Temperature                                |                   | -40  | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### THERMAL CHARACTERISTICS

| Symbol          | Rating                                                                        | Condition                                                                                                              | Value      | Unit |

|-----------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------|------|

| $R_{\theta JA}$ | Thermal Characteristics, (Note 13) Thermal Resistance Junction–Air 16–SOIC–WB | 100 mm <sup>2</sup> , 1 oz Copper, 1 Surface Layer (1S0P)<br>100 mm <sup>2</sup> , 2 oz Copper, 1 Surface Layer (1S0P) | 120<br>81  | °C/W |

| $R_{\theta JC}$ | Thermal Resistance Junction-Case                                              | 100 mm <sup>2</sup> , 1 oz Copper, 1 Surface Layer (1S0P)                                                              | 38         | °C/W |

| $\Psi_{JT}$     | Thermal Resistance Junction-to-Top                                            |                                                                                                                        | 18         | °C/W |

| $\Psi_{JB}$     | Thermal Resistance Junction-to-Board                                          |                                                                                                                        | 55         | °C/W |

| P <sub>D</sub>  | Power Dissipation (Note 13)<br>16–SOIC–WB                                     | 100 mm <sup>2</sup> , 1 oz Copper, 1 Surface Layer (1S0P)<br>100 mm <sup>2</sup> , 2 oz Copper, 1 Surface Layer (1S0P) | 0.8<br>1.5 | W    |

<sup>12.</sup> Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

#### **ISOLATION CHARACTERISTICS**

| Symbol                           | Parameter                         | Condition                                                                                                            | Min              | Тур | Max | Unit             |

|----------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------------------|

| V <sub>ISO,INPUT</sub> TO OUTPUT | Input to Output Isolation Voltage | $T_A = 25^{\circ}\text{C}$ , Relative Humidity < 50%,<br>t = 1.0 minute, $I_{I-O}$ 10 A, 50 Hz<br>(Notes 14, 15, 16) | 5000             |     |     | V <sub>RMS</sub> |

| V <sub>ISO,OUTA</sub> TO<br>OUTB | OUTA to OUTB Isolation Voltage    | Impulse Test > 10 ms (Notes 14, 15)                                                                                  | 1500             |     |     | $V_{DC}$         |

| R <sub>ISO</sub>                 | Isolation Resistance              | V <sub>I_O</sub> = 500 V (Note 14)                                                                                   | 10 <sup>11</sup> |     |     | Ω                |

<sup>14.</sup> Device is considered a two – terminal device: pins 1 to 8 are shorted together and pins 9 to 16 are shorted together for input to output isolation test, and pins 9 to 11 are shorted together and pins 14 to 16 are shorted together for between channel isolation test.

<sup>13.</sup> JEDEC standard: JESD51-2, and JESD51-3.

<sup>15.5,000</sup> V<sub>RMS</sub> for 1 – minute duration is equivalent to 6,000 V<sub>RMS</sub> for 1 – second duration for input to output isolation test, and Impulse Test > 10 ms; sample tested for between channel isolation test.

<sup>16.</sup> The input – output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input – output continuous voltage rating. For the continuous working voltage rating, refer to equipment – level safety specification or DIN VDE V 0884 – 11 Safety and Insulation Ratings Table

**ELECTRICAL CHARACTERISTICS** ( $V_{DD} = 5 \text{ V}, V_{CCA} = V_{CCB} = 12 \text{ V}, \text{ or } 20 \text{ V}$  (Note 18) and VSSA = VSSB, for typical values  $T_J = T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise specified. (Note 17)

| Symbol                                       | Parameter                                                                              | Condition                                                                                  | Min | Тур  | Max  | Unit |

|----------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|------|------|------|

| PRIMARY PO                                   | WER SUPPLY SECTION (V <sub>DD</sub> )                                                  |                                                                                            |     |      |      |      |

| $I_{QVDD}$                                   | V <sub>DD</sub> Quiescent Current                                                      | $V_{INA} = V_{INB} = 0 \text{ V}, V_{ENABLE} = V_{DD}$<br>or $V_{DISABLE} = 0 \text{ V}$   | 500 | 780  | 1000 | μΑ   |

|                                              |                                                                                        | $V_{INA} = V_{INB} = 5 \text{ V}, V_{ENABLE} = 0 \text{ V}$ or $V_{DISABLE} = V_{DD}$      | 500 | 820  | 1000 | μΑ   |

|                                              |                                                                                        | $V_{INA} = V_{INB} = 5 \text{ V}, V_{ENABLE} = V_{DD}$<br>or $V_{DISABLE} = 0 \text{ V}$   | 7   | 12   | 16   | mA   |

| $I_{VDD}$                                    | V <sub>DD</sub> Operating Current                                                      | f <sub>IN</sub> = 500 kHz, 50% duty cycle,<br>C <sub>OUT</sub> = 100 pF                    | 5.0 | 7.15 | 9.0  | mA   |

| V <sub>DDUV+</sub>                           | V <sub>DD</sub> Supply Under–Voltage Positive–Going Threshold                          | V <sub>DD</sub> = Sweep                                                                    | 2.7 | 2.8  | 2.9  | >    |

| V <sub>DDUV</sub> _                          | V <sub>DD</sub> Supply Under-Voltage Negative-Going Threshold                          | V <sub>DD</sub> = Sweep                                                                    | 2.6 | 2.7  | 2.8  | >    |

| $V_{DDHYS}$                                  | V <sub>DD</sub> Supply Under-Voltage Lockout Hysteresis                                | V <sub>DD</sub> = Sweep                                                                    | -   | 0.1  | -    | V    |

|                                              | POWER SUPPLY SECTION (VCCA AND VCCB                                                    | 3)                                                                                         |     |      |      |      |

| IQVCCA                                       | V <sub>CCA</sub> and V <sub>CCB</sub> Quiescent Current                                | V <sub>INA</sub> = V <sub>INB</sub> = 0 V, per channel                                     | 200 | 280  | 500  | μΑ   |

| IQVCCB                                       |                                                                                        | V <sub>INA</sub> = V <sub>INB</sub> = 5 V, per channel                                     | 300 | 410  | 600  | μA   |

| I <sub>VCCA</sub><br>I <sub>VCCB</sub>       | V <sub>CCA</sub> and V <sub>CCB</sub> Operating Current                                | Current per channel (f <sub>IN</sub> = 500 kHz, 50% duty cycle), C <sub>OUT</sub> = 100 pF | 2.0 | 3.0  | 5.5  | mA   |

| VCCA and VC                                  | CCB UVLO THRESHOLD (5-V UVLO VERSION)                                                  |                                                                                            |     | •    | •    |      |

| V <sub>CCAUV+</sub><br>V <sub>CCBUV+</sub>   | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Positive-Going Threshold |                                                                                            | 5.7 | 6.0  | 6.3  | V    |

| V <sub>CCAUV</sub> -<br>V <sub>CCBUV</sub> - | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Negative-Going Threshold |                                                                                            | 5.4 | 5.7  | 6.0  | V    |

| V <sub>CCHYS</sub>                           | Under-Voltage Lockout Hysteresis                                                       |                                                                                            | -   | 0.3  | -    | V    |

| tuvflt                                       | Under-Voltage Debounce Time (Note 19)                                                  |                                                                                            | -   | -    | 10   | μs   |

| VCCA and VC                                  | CCB UVLO THRESHOLD (8-V UVLO VERSION)                                                  |                                                                                            |     |      |      |      |

| V <sub>CCAUV+</sub><br>V <sub>CCBUV+</sub>   | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Positive-Going Threshold |                                                                                            | 8.3 | 8.7  | 9.2  | V    |

| V <sub>CCAUV</sub> -<br>V <sub>CCBUV</sub> - | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Negative-Going Threshold |                                                                                            | 7.8 | 8.2  | 8.7  | V    |

| V <sub>CCHYS</sub>                           | Under-Voltage Lockout Hysteresis                                                       |                                                                                            | _   | 0.5  | -    | V    |

| t <sub>UVFLT</sub>                           | Under-Voltage Debounce Time (Note 19)                                                  |                                                                                            | -   | _    | 10   | μs   |

| VCCA and VC                                  | CCB UVLO THRESHOLD (13-V UVLO VERSION                                                  | l)                                                                                         |     |      |      |      |

| V <sub>CCAUV+</sub><br>V <sub>CCBUV+</sub>   | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Positive-Going Threshold |                                                                                            | 12  | 13   | 14   | V    |

| V <sub>CCAUV</sub> -<br>V <sub>CCBUV</sub> - | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Negative-Going Threshold |                                                                                            | 11  | 12   | 13   | V    |

| V <sub>CCHYS</sub>                           | Under-Voltage Lockout Hysteresis                                                       |                                                                                            | _   | 1    | -    | V    |

| t <sub>UVFLT</sub>                           | Under-Voltage Debounce Time (Note 19)                                                  |                                                                                            | -   | -    | 10   | μs   |

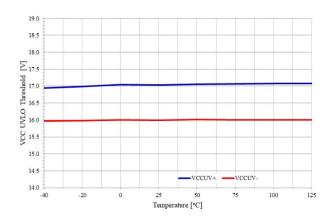

| VCCA and VC                                  | CCB UVLO THRESHOLD (17-V UVLO VERSION                                                  | )<br>                                                                                      |     |      |      |      |

| V <sub>CCAUV+</sub><br>V <sub>CCBUV+</sub>   | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Positive-Going Threshold |                                                                                            | 16  | 17   | 18   | V    |

| V <sub>CCAUV</sub> -<br>V <sub>CCBUV</sub> - | V <sub>CCA</sub> and V <sub>CCB</sub> Supply Under-Voltage<br>Negative-Going Threshold |                                                                                            | 15  | 16   | 17   | V    |

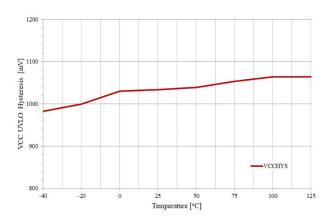

| V <sub>CCHYS</sub>                           | Under-Voltage Lockout Hysteresis                                                       |                                                                                            | -   | 1    | -    | V    |

| t <sub>UVFLT</sub>                           | Under-Voltage Debounce Time (Note 19)                                                  |                                                                                            |     | -    | 10   | μs   |

| LOGIC INPUT                                  | SECTION (INA, INB, AND ANB)                                                            |                                                                                            |     |      |      |      |

| V <sub>INH</sub>                             | High Level Input Voltage                                                               |                                                                                            | 1.4 | 1.6  | 1.8  | ٧    |

| V <sub>INL</sub>                             | Low Level Input Voltage                                                                |                                                                                            | 0.9 | 1.1  | 1.3  | V    |

**ELECTRICAL CHARACTERISTICS** ( $V_{DD} = 5 \text{ V}, V_{CCA} = V_{CCB} = 12 \text{ V}, \text{ or } 20 \text{ V}$  (Note 18) and VSSA = VSSB, for typical values  $T_J = T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise specified. (Note 17) (continued)

| Symbol                                               | Parameter                                                        | Condition                                                                                                                   | Min                      | Тур                 | Max                      | Unit |

|------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------|------|

| LOGIC INPUT                                          | SECTION (INA, INB, AND ANB)                                      |                                                                                                                             |                          |                     |                          |      |

| V <sub>INHYS</sub>                                   | Input Logic Hysteresis                                           |                                                                                                                             | ı                        | 0.5                 | -                        | V    |

| I <sub>IN+</sub>                                     | High Level Logic Input Bias Current                              | V <sub>IN</sub> = 5 V                                                                                                       | 20                       | 25                  | 33                       | μΑ   |

| $I_{IN-}$                                            | Low Level Logic Input Bias Current                               | V <sub>IN</sub> = 0 V                                                                                                       | i                        | -                   | 1.0                      | μΑ   |

| LOGIC INPUT                                          | SECTION (for ENABLE Version only)                                |                                                                                                                             |                          |                     |                          |      |

| V <sub>ENAH</sub>                                    | Enable High Voltage                                              |                                                                                                                             | 1.4                      | 1.6                 | 1.8                      | V    |

| $V_{ENAL}$                                           | Enable Low Voltage                                               |                                                                                                                             | 0.9                      | 1.1                 | 1.3                      | V    |

| V <sub>ENAHYS</sub>                                  | Enable Logic Hysteresis                                          |                                                                                                                             | -                        | 0.5                 | -                        | V    |

| OGIC INPUT                                           | SECTION (for DISABLE Version only)                               |                                                                                                                             |                          |                     |                          |      |

| V <sub>DISH</sub>                                    | Disable High Voltage                                             |                                                                                                                             | 1.4                      | 1.6                 | 1.8                      | V    |

| V <sub>DISL</sub>                                    | Disable Low Voltage                                              |                                                                                                                             | 0.9                      | 1.1                 | 1.3                      | V    |

| V <sub>DISHYS</sub>                                  | Disable Logic Hysteresis                                         |                                                                                                                             | -                        | 0.5                 | -                        | V    |

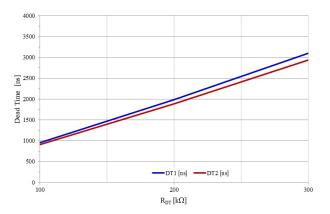

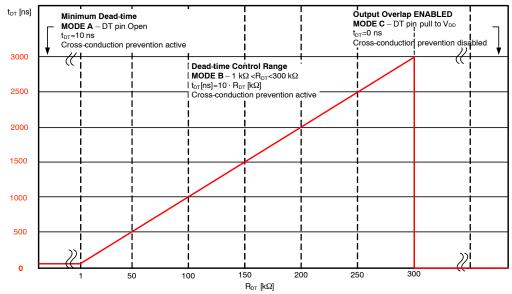

|                                                      | AND OVERLAP SECTION                                              |                                                                                                                             |                          |                     |                          | •    |

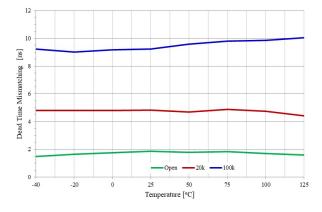

| t <sub>DT,MIN</sub>                                  | Minimum Dead-Time                                                | DT pin is left open                                                                                                         | 0                        | 10                  | 29                       | ns   |

| t <sub>DT</sub>                                      | Dead-Time                                                        | R <sub>DT</sub> = 20 kΩ                                                                                                     | 145                      | 200                 | 255                      | ns   |

| = •                                                  |                                                                  | R <sub>DT</sub> = 100 kΩ                                                                                                    | 800                      | 1000                | 1200                     | ns   |

| $\Delta t_{DT}$                                      | Dead-Time Mismatch between OUTB $ ightarrow$ OUTA                |                                                                                                                             | -30                      | _                   | 30                       | ns   |

| ٥.                                                   | and OUTA → OUTB                                                  | R <sub>DT</sub> = 100 kΩ                                                                                                    | -150                     | -                   | 150                      | ns   |

| V <sub>DT,SHORT</sub>                                | DT Threshold Voltage for OUTA & OUTB Overlap                     | DT pin Pulled to VDD                                                                                                        | 0.85x<br>V <sub>DD</sub> | 0.9xV <sub>DD</sub> | 0.95x<br>V <sub>DD</sub> | V    |

| GATE DRIVE                                           | SECTION                                                          |                                                                                                                             |                          |                     |                          |      |

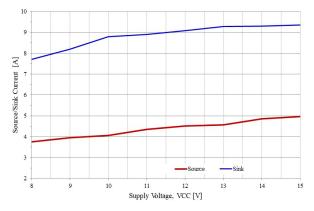

| I <sub>OUTA+,</sub><br>I <sub>OUTB+</sub>            | OUTA and OUTB Source Peak Current (Note 19)                      | $\begin{split} &V_{INA} = V_{INB} = 5 \text{ V, PW} \leq 5  \mu\text{s,} \\ &V_{CCA} = V_{CCB} =  12 \text{ V} \end{split}$ | 2.6                      | 4.5                 | _                        | Α    |

| I <sub>OUTA-,</sub><br>I <sub>OUTB-</sub>            | OUTA and OUTB Sink Peak Current (Note 19)                        | $V_{INA} = V_{INB} = 5 \text{ V, PW} \le 5 \mu s$<br>$V_{CCA} = V_{CCB} = 12 \text{ V}$                                     | 7.0                      | 9.0                 | -                        | Α    |

| R <sub>OH</sub>                                      | Output Resistance at High State                                  | I <sub>OUTH</sub> = 100 mA                                                                                                  | -                        | 1.4                 | 2.7                      | Ω    |

| R <sub>OL</sub>                                      | Output Resistance at Low State                                   | I <sub>OUTL</sub> = 100 mA                                                                                                  | _                        | 0.5                 | 1.0                      | Ω    |

| V <sub>OHA</sub> , V <sub>OHB</sub>                  | High Level Output Voltage (V <sub>CC</sub> - V <sub>OUT</sub> )  | I <sub>OUT</sub> = 100 mA                                                                                                   | ı                        | -                   | 270                      | mV   |

| V <sub>OLA</sub> , V <sub>OLB</sub>                  | Low Level Output Voltage (V <sub>OUT</sub> - V <sub>SS</sub> )   | I <sub>OUT</sub> = 100 mA                                                                                                   | -                        | -                   | 100                      | mV   |

| DYNAMIC ELI                                          | ECTRICAL CHARACTERISTICS                                         |                                                                                                                             |                          |                     |                          |      |

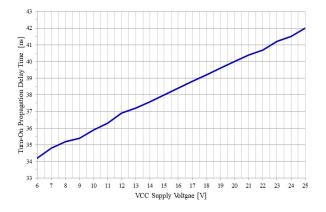

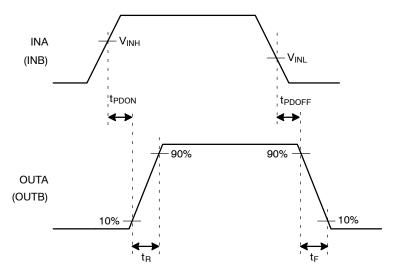

| t <sub>PDON</sub>                                    | Turn-On Propagation Delay from INx to OUTx                       | $V_{CCA} = V_{CCB} = 12 \text{ V}, C_{LOAD} = 0 \text{ nF}$                                                                 | 22                       | 36                  | 55                       | ns   |

|                                                      |                                                                  | $V_{CCA} = V_{CCB} = 20 \text{ V}, C_{LOAD} = 0 \text{ nF}$                                                                 | 25                       | 39                  | 58                       | ns   |

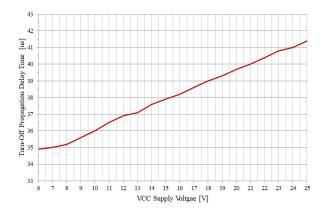

| t <sub>PDOFF</sub>                                   | Turn-Off Propagation Delay from INx to OUTx                      | $V_{CCA} = V_{CCB} = 12 \text{ V}, C_{LOAD} = 0 \text{ nF}$                                                                 | 22                       | 36                  | 55                       | ns   |

|                                                      |                                                                  | V <sub>CCA</sub> = V <sub>CCB</sub> = 20 V, C <sub>LOAD</sub> = 0 nF                                                        | 25                       | 39                  | 58                       | ns   |

| t <sub>PWD</sub>                                     | Pulse Width Distortion (t <sub>PDON</sub> – t <sub>PDOFF</sub> ) |                                                                                                                             | -5                       | -                   | 5                        | ns   |

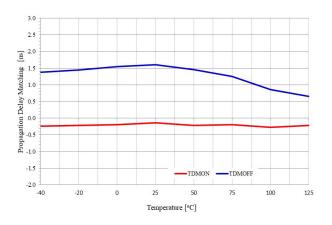

| t <sub>DM</sub>                                      | Propagation Delay Mismatching between Channels                   | INA and INB shorted,<br>f <sub>IN</sub> = 100 kHz                                                                           | -5                       | -                   | 5                        | ns   |

| t <sub>R</sub>                                       | Turn-On Rise Time                                                | V <sub>CCA</sub> = V <sub>CCB</sub> = 12 V,<br>C <sub>LOAD</sub> = 1.8 nF                                                   | -                        | 9                   | 16                       | ns   |

|                                                      |                                                                  | V <sub>CCA</sub> = V <sub>CCB</sub> = 20 V,<br>C <sub>LOAD</sub> = 1.8 nF                                                   | -                        | 11                  | 19                       | ns   |

| t <sub>F</sub>                                       | Turn-Off Fall Time                                               | $V_{CCA} = V_{CCB} = 12 \text{ V},$<br>$C_{LOAD} = 1.8 \text{ nF}$                                                          | -                        | 8                   | 16                       | ns   |

|                                                      |                                                                  | $V_{CCA} = V_{CCB} = 20 \text{ V},$<br>$C_{LOAD} = 1.8 \text{ nF}$                                                          | ı                        | 10                  | 19                       | ns   |

| T <sub>ENABLE,OUT,</sub><br>T <sub>DISABLE,OUT</sub> | ENABLE or DISABLE to OUTx Turn-On/Off<br>Propagation Delay       | V <sub>CCA</sub> = V <sub>CCB</sub> = 12 V                                                                                  | 22                       | 36                  | 55                       | ns   |

| · DISABLE,UUI                                        |                                                                  | V <sub>CCA</sub> = V <sub>CCB</sub> = 20 V                                                                                  | 25                       | 39                  | 58                       | ns   |

**ELECTRICAL CHARACTERISTICS** ( $V_{DD} = 5 \text{ V}, V_{CCA} = V_{CCB} = 12 \text{ V}, \text{ or 20 V}$  (Note 18) and VSSA = VSSB, for typical values  $T_J = T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise specified. (Note 17) (continued)

| Symbol               | Parameter                                          | Condition                                                                                              | Min | Тур | Max | Unit |

|----------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| DYNAMIC EL           | DYNAMIC ELECTRICAL CHARACTERISTICS                 |                                                                                                        |     |     |     |      |

| t <sub>PW</sub>      | Minimum Input Pulse Width that Change Output State | C <sub>LOAD</sub> = 0 nF                                                                               | ı   | 15  | 30  | ns   |

| T <sub>FLT,ANB</sub> | Glitch Filter on the ANB Pin                       |                                                                                                        | 2.0 | 3.3 | 4.5 | μs   |

| CMTI                 | Common Mode Transient Immunity (Note 19)           | Slew rate of GND versus VSSA and VSSB. INA and INB both are tied to $V_{DD}$ or GND. $V_{CM}$ = 1500 V | 200 | -   | -   | V/ns |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>17.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}C$ . 18.  $V_{CCA} = V_{CCB} = 12 \text{ V}$  is used for the test condition of 5–V and 8–V UVLO,  $V_{CCA} = V_{CCB} = 20 \text{ V}$  is used for 13–V and 17–V UVLO. 19. These parameters are verified by bench test only and not tested in production.

# **INSULATION CHARACTERISTICS CURVES**

Figure 4. Thermal Derating Curve for Safety-related Limiting Current (Current in Each Channel with Both Channels Running Simultaneously)

Figure 5. Thermal Derating Curve for Safety-related Limiting Power

#### TYPICAL CHARACTERISTIC

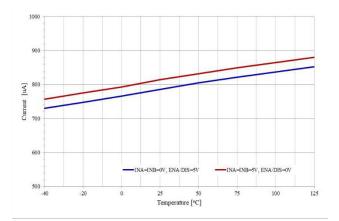

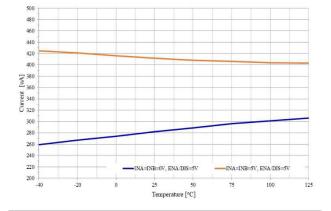

Figure 6. Quiescent  $V_{DD}$  Supply Current vs. Temperature ( $V_{DD}$  = 5 V, INA = INB = 0 V, ENA/DIS = 5 V or, INA = INB = 5 V, ENA/DIS = 0 V and No Load)

Figure 7. Quiescent  $V_{DD}$  Supply Current vs. Temperature ( $V_{DD}$  = 5 V, INA = INB = ENA/DIS = 5 V and No Load)

Figure 8. V<sub>DD</sub> Operating Current vs. Temperature (V<sub>DD</sub> = 5 V, No Load, and Switching Frequency = 500 kHz)

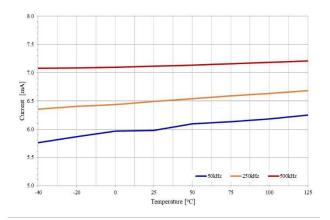

Figure 9. V<sub>DD</sub> Operating Current vs. Temperature (V<sub>DD</sub> = 5 V, No Load, and Different Switching Frequency)

Figure 10. Per Channel  $V_{DD}$  Operating Current vs. Temperature ( $V_{DD}$  = 5 V, No Load, and Different Switching Frequency

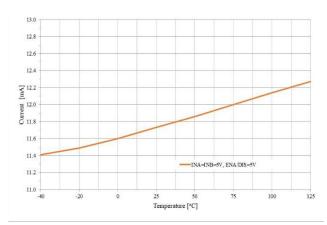

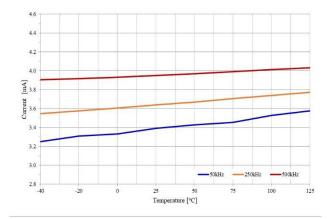

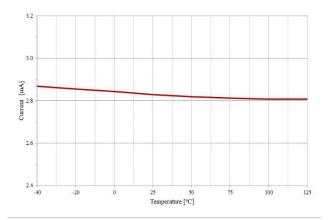

Figure 11. Per Channel Quiescent  $V_{CC}$  Supply Current vs. Temperature (INA = INB = 0 V or 5 V, ENA/DIS = 5 V and No Load

Figure 12. Per Channel V<sub>CC</sub> Operating Current vs. Temperature (No Load and Switching Frequency = 500 kHz

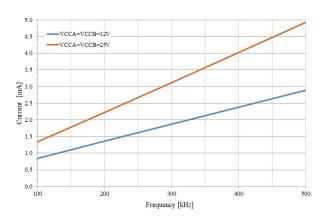

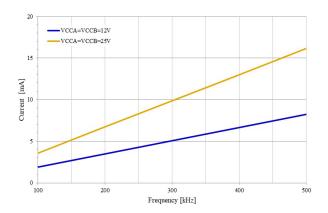

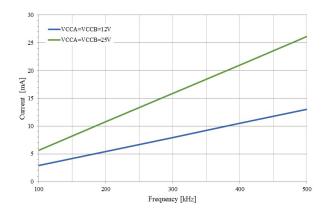

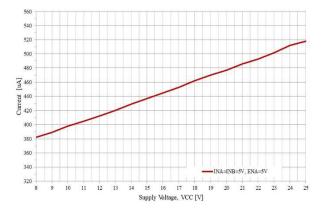

Figure 13. Per Channel Operating Current vs. Frequency (No Load,  $V_{CCA} = V_{CCB} = 12 \text{ V}$ , or 25 V)

Figure 14. Per Channel Operating Current vs. Frequency ( $C_{LOAD}$  = 1 nF,  $V_{CCA}$  =  $V_{CCB}$  = 12 V, or 25 V)

Figure 15. Per Channel Operating Current vs. Frequency ( $C_{LOAD}$  = 1.8 nF,  $V_{CCA}$  =  $V_{CCB}$  = 12 V, or 25 V)

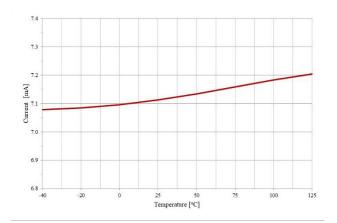

Figure 16. Per Channel  $V_{CC}$  Quiescent Current vs.  $V_{CC}$  Supply Voltage (INA = INB = 0 V, ENA = 5 V)

Figure 17. Per Channel  $V_{CC}$  Quiescent Current vs.  $V_{CC}$  Supply Voltage (INA = INB = 5 V, ENA = 5 V)

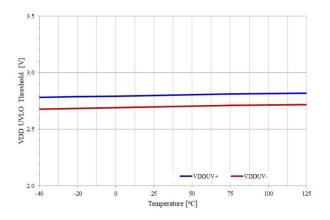

Figure 18.  $V_{DD}$  UVLO Threshold vs. Temperature

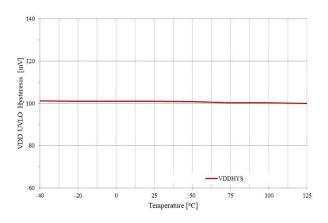

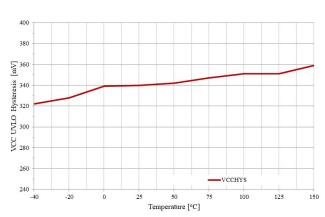

Figure 19.  $V_{DD}$  UVLO Hysteresis vs. Temperature

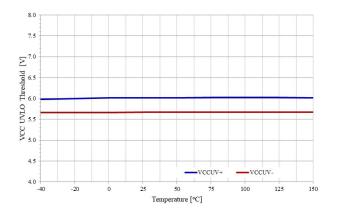

Figure 20.  $V_{CC}$  5-V UVLO Threshold vs. Temperature

Figure 21. V<sub>CC</sub> 5-V UVLO Hysteresis vs. Temperature

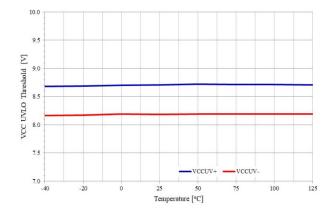

Figure 22. V<sub>CC</sub> 8-V UVLO Threshold vs. Temperature

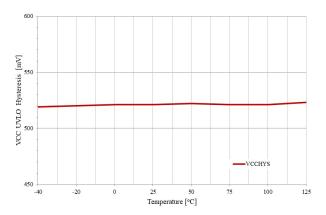

Figure 23. V<sub>CC</sub> 8-V UVLO Hysteresis vs. Temperature

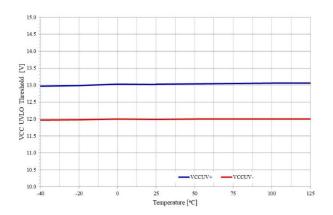

Figure 24. V<sub>CC</sub> 13-V UVLO Threshold vs. Temperature

Figure 25.  $V_{CC}$  13-V UVLO Hysteresis vs. Temperature

Figure 26.  $V_{CC}$  17-V UVLO Threshold vs. Temperature

Figure 27.  $V_{CC}$  17-V UVLO Hysteresis vs. Temperature

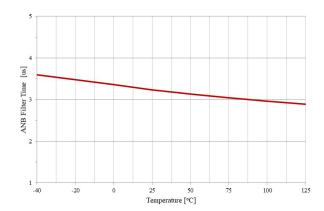

Figure 29. ANB Filter Time vs. Temperature

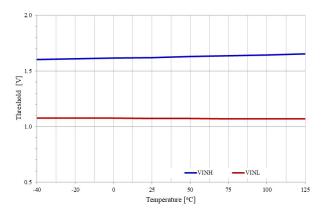

Figure 30. Input Logic Threshold vs. Temperature (INA, INB, and ANB)

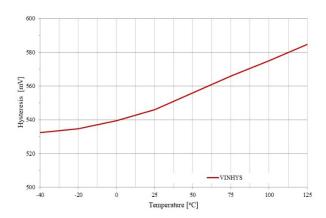

Figure 31. Input Logic Hysteresis vs. Temperature (INA, INB, and ANB)

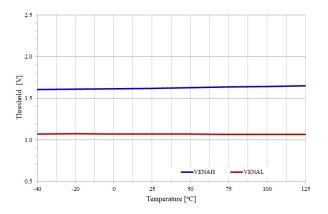

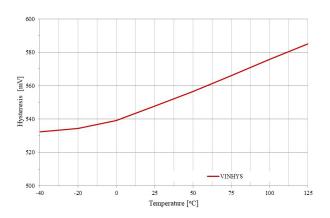

Figure 32. ENA/DIS Threshold vs. Temperature (ENABLE, and DISABLE)

Figure 33. ENA/DIS Hysteresis vs. Temperature (ENABLE, and DISABLE)

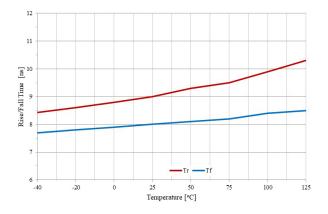

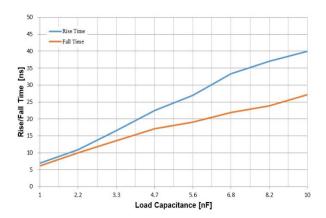

Figure 34. Rise/Fall Time vs. Temperature  $(C_{LOAD} = 1.8 \text{ nF})$

Figure 35. Rise/Fall Time vs. Temperature ( $V_{CC}$  = 12 V, and Different Load)

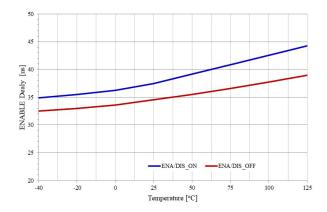

Figure 36. ENA/DIS Delay Time vs. Temperature

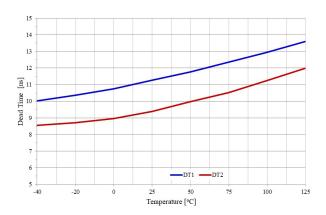

Figure 37. Dead Time vs. Temperature (R<sub>DT</sub> = Open)

Figure 38. Dead Time vs. Temperature  $(R_{DT}=20k\Omega)$

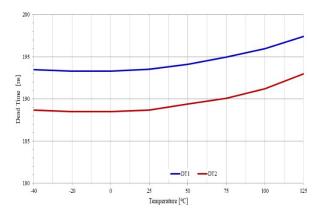

Figure 39. Dead Time vs. Temperature  $(R_{DT} = 100 \text{ k}\Omega)$

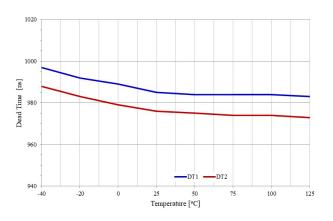

Figure 40. Dead Time Mismatching vs. Temperature

Figure 41. Dead Time vs. R<sub>DT</sub>

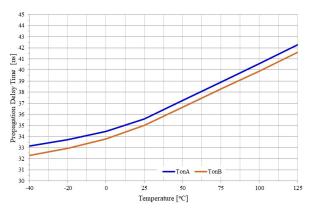

Figure 42. Turn-on Propagation Delay vs.

Temperature

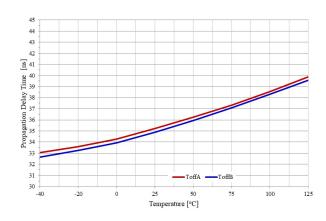

Figure 43. Turn-off Propagation Delay vs. Temperature

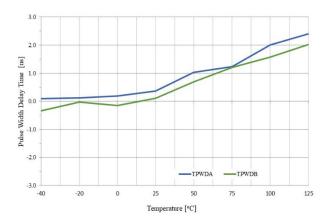

Figure 44. Pulse Width Distortion vs. Temperature

Figure 45. Propagation Delay Matching vs. Temperature

Figure 46. Turn-on Propagation Delay vs. V<sub>CC</sub> Supply Voltage

Figure 47. Turn-off Propagation Delay vs. V<sub>CC</sub> Supply Voltage

#### PARAMETER MEASUREMENT DEFINITION

## **Switching Time Definitions**

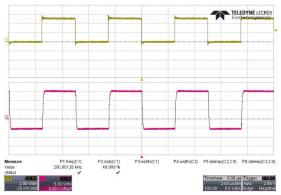

Figure 48 shows the switching time definitions of the turn-on  $(t_{PDON})$  and turn-off  $(t_{PDOFF})$  propagation delay time among the driver's two input signals INA, INB and two

output signals OUTA, OUTB. The typical values of the propagation delay (t<sub>PDON</sub>, T<sub>PDOFF</sub>), pulse width distortion (t<sub>PWD</sub>) and delay matching between channels times are specified in the electrical characteristics table.

Figure 48. Switching Time Definitions

#### **Enable and Disable Function**

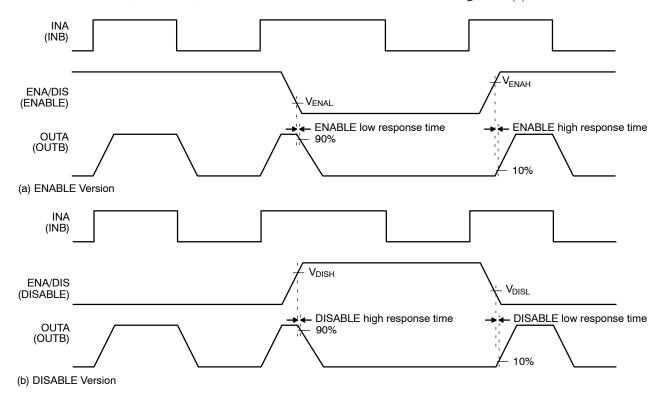

Figure 49 shows the response time according to an ENABLE or the DISABLE operating modes. If the ENA/DIS pin voltage goes to LOW state, i.e.  $V_{ENA} \le 1.1~V$  shuts down both outputs simultaneously and Pull the ENA/DIS pin HIGH (or left open), i.e.  $V_{ENA} \ge 1.6~V$  to

operate normally in an ENABLE mode as shown in Figure 49 (a). Conversely, if the ENA/DIS pin voltage goes to HIGH state, i.e.  $V_{DIS} \ge 1.6 \text{ V}$  shuts down both outputs simultaneously and Pull the ENA/DIS pin LOW (or left open), i.e.  $V_{DIS} \le 1.1 \text{ V}$  operate normally in the DISABLE mode as shown in Figure 49 (b).

Figure 49. Timing Chart of Enable and Disable Function

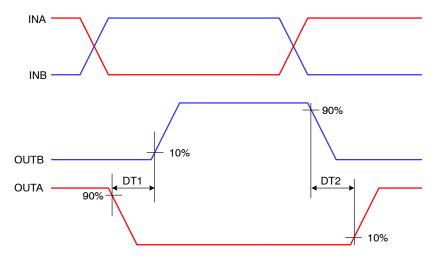

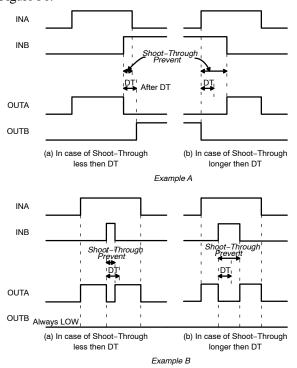

# Programmable Dead-Time

Dead time is automatically inserted whenever the dead time of the external two input signals (between INA and INB signals) is shorter than internal setting dead times (DT1 and DT2). Otherwise, if the external input signal dead times are larger than internal dead– time, the dead time is not modified by the gate driver and internal dead–time definition as shown in Figure 50.

Figure 50. Internal Dead-Time Definitions

Figure 51 shows the definition of internal dead time and shoot–through prevention when input signals applied at same time.

Figure 51. Internal Dead-Time Definitions

## **DEVICE INFORMATION**

## **Input to Output Operation Definitions**

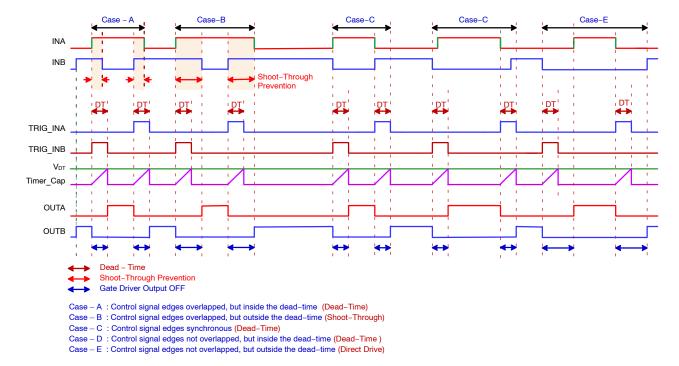

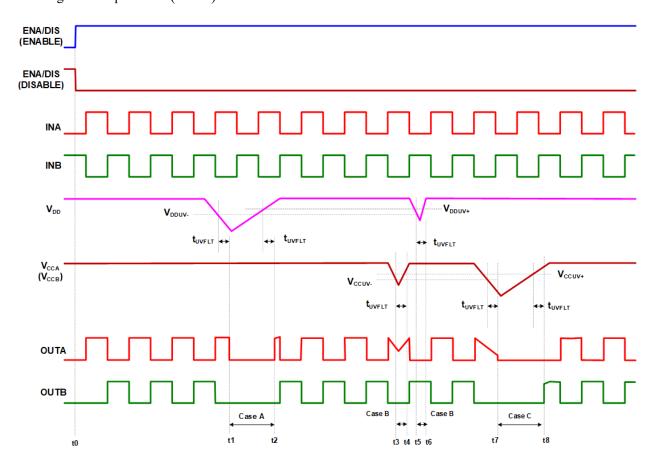

The NCV51561 provides important protection functions such as independent under-voltage lockout for both gate driver; enable or disable function and dead-time control function. Figure 52 shows an overall input to output timing diagram when shutdown mode via ENA/DIS pin in the

CASE-A, and Under-Voltage Lockout protection on the primary- and secondary-sides power supplies events in the CASE-B. The gate driver output (OUTA and OUTB) were turn-off when cross-conduction event at the dead time control mode in the CASE-C.

Figure 52. Overall Operating Waveforms Definitions at the Dead-Time Control Mode

## Input and Output Logic Table

Table 1 shows an input to output logic table according to the dead time control modes and an enable or the disable operation mode.

**Table 1. INPUT AND OUTPUT LOGIC TABLE**

|           |           | INPUT          |                | OUT  | PUT  |                                                       |

|-----------|-----------|----------------|----------------|------|------|-------------------------------------------------------|

|           |           | ENA            | /DIS           |      |      |                                                       |

| INA       | INB       | ENABLE         | DISABLE        | OUTA | OUTB | NOTE                                                  |

| L         | L         | H or Left open | L or Left open | L    | L    | Programmable dead time control with R <sub>DT</sub> . |

| L         | Н         | H or Left open | L or Left open | L    | Н    |                                                       |

| Н         | L         | H or Left open | L or Left open | Н    | L    |                                                       |

| Н         | Н         | H or Left open | L or Left open | L    | L    | DT pin is left open Or programmed with $R_{ m DT}$ .  |

| Н         | Н         | H or Left open | L or Left open | Н    | Н    | DT pin pulled to V <sub>DD</sub> .                    |

| Left open | Left open | H or Left open | L or Left open | L    | L    |                                                       |

| Х         | Х         | L              | Н              | L    | L    |                                                       |

20. "X" means L, H or left open.

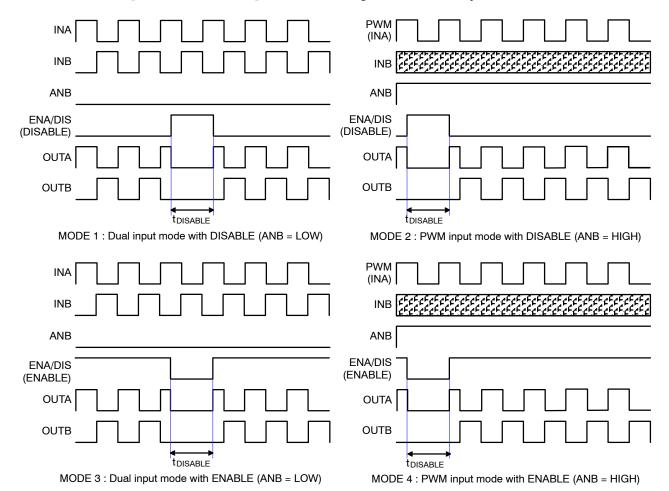

#### **Input Signal Configuration**

The NCV51561 allows to set the input signal configuration through the ANB pin for user convenience. There are four operating modes that allow to change the configuration of the input to output channels (e.g. single input – dual output, or dual input – dual output), and select

the shutdown function (e.g. Disable or Enable mode) as below Table 2. Unused input pins (e.g. INA, INB, and ANB) should be tied to GND to achieve better noise immunity. In addition, the ANB pin has an internal filter time typically 3.3 µs to achieve the noise immunity.

**Table 2. INPUT SIGNAL CONFIGURATION LOGIC TABLE**

|      | Functional Input Pin |     |     |         |                                                                    |

|------|----------------------|-----|-----|---------|--------------------------------------------------------------------|

| Mode | INA                  | INB | ANB | ENA/DIS | Input Configuration                                                |

| 1    | INA                  | INB | L   | DISABLE | Dual-Input, Dual-Output with disable mode (ENA/DIS = LOW)          |

| 2    | INA                  | Х   | Н   | DISABLE | Single-Input (INA), Dual-Output with disable mode(ENA/DIS = LOW)   |

| 3    | INA                  | INB | L   | ENABLE  | Dual-Input, Dual-Output with enable mode (ENA/DIS = HIGH)          |

| 4    | INA                  | Х   | Н   | ENABLE  | Single-Input (INA), Dual-Output with enable mode (ENA/DISE = HIGH) |

Figure 53 shows an operating timing chart of input to output and shutdown function according to the ANB and ENA/DIS pins. The ENA/DIS and ANB pins are only functional when  $V_{DD}$  stays above the specified UVLO threshold. It is recommended to tie these pins to Ground if the ENA/DIS and ANB pins are not used to achieve better noise immunity, and it is recommended to bypass using a 1 nF low ESR/ESL capacitor close to these pins for the

DISABLE (e.g. NCV51561xB) mode. When it is not possible to connect ANB to GND then external pull-down resistor few ten  $k\Omega$  (e.g. 10 ~47  $k\Omega$ ) is recommended to prevent unwanted ANB activation by external interference as despite its internal 3.3  $\mu$ s filter.

The OUTA and OUTB works as complementary outputs from PWM input signal on the INA pin regardless the INB signal when the ANB pin is HIGH.

Figure 53. Timing Chart of ENABLE and DISABLE Modes

#### PROTECTION FUNCTION

The NCV51561 provides the protection features include enable function, Cross Conduction Protection, and Under-Voltage Lockout (UVLO) of power supplies on primary-side ( $V_{\rm DD}$ ), and secondary-side both channels ( $V_{\rm CCA}$ , and  $V_{\rm CCB}$ ).

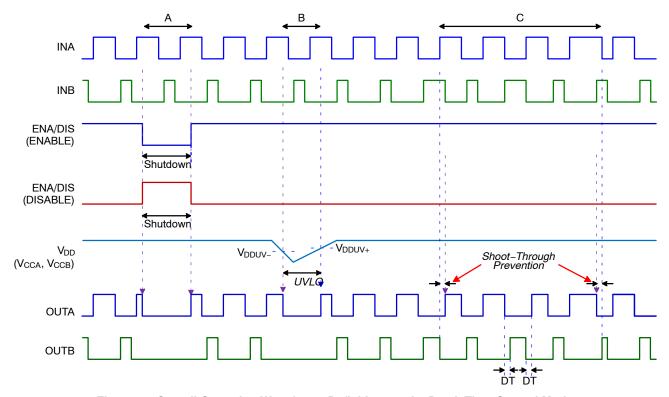

# Under-Voltage Lockout Protection $V_{DD}$ and $V_{CCx}$

The NCV51561 provides the Under-Voltage Lockout (UVLO) protection function for  $V_{DD}$  in primary-side and both gate drive output for  $V_{CCA}$  and  $V_{CCB}$  in secondary-side as shown in Figure 54.

The gate driver is running when the  $V_{DD}$  supply voltage is greater than the specified under-voltage lockout threshold voltage (e.g. typically 2.8 V) and ENA/DIS pin is HIGH or LOW states for an ENABLE (e.g. NCV51561xA) or the DISABLE (e.g. NCV51561xB) mode respectively.

In addition, both gate output drivers have independent under voltage lockout protection (UVLO) function and each channel supply voltages in secondary–side (e.g.  $V_{CCA}$ , and  $V_{CCB}$ ) need to be greater than specified UVLO threshold level in secondary–side to let the output operate per input signal. The typical  $V_{CCx}$  UVLO threshold voltage levels for each option are per below Table 3.

Table 3. V<sub>CCx</sub> UVLO OPTION TABLE

| Option | V <sub>CC</sub> UVLO Level | Unit |

|--------|----------------------------|------|

| 5-V    | 6.0                        | V    |

| 8–V    | 8.7                        | V    |

| 13-V   | 13                         | V    |

| 17-V   | 17                         | V    |

UVLO protection has an hysteresis to provide immunity to short  $V_{CC}$  drops that can occur.

Figure 54. Timing Chart Under-Voltage Lockout Protection

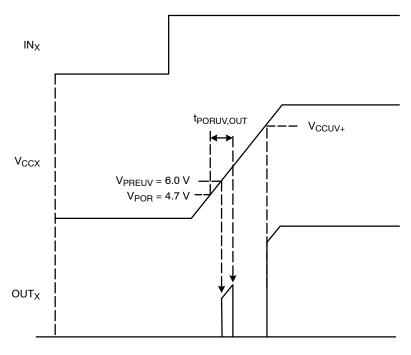

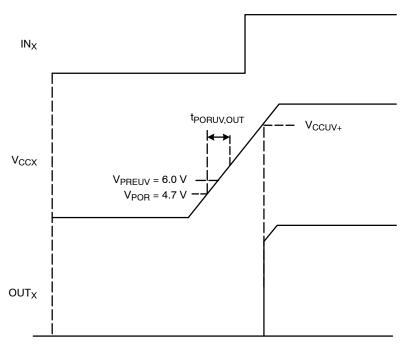

# $V_{CCX}$ Power-Up and $IN_X$ Signal

To provide a variety of Under–Voltage Lockout (UVLO) thresholds NCV51561 has an internal settling time ( $t_{PORUV,OUT} = 18~\mu s$ , typical) during initial  $V_{CCX}$  start–up or after POR event.

In case  $IN_X$  pins are active when  $V_{CCX}$  is above 4.7 V, outputs would occur until settling time has elapsed as shown in Figure 55 (A). If  $IN_X$  are only active after settling time has expired, outputs won't be active until  $V_{CCX}$  cross NCV51561 specific  $V_{CCUV+}$  as shown in Figure 55 (B).

(A) Power Up with PWM Signals during Preset

(B) Power Up without PWM Signals during Preset

Figure 55. V<sub>CCX</sub> Power-up

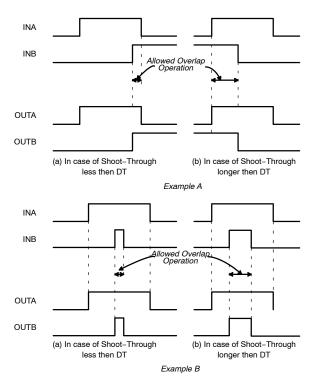

# Cross-Conduction Prevention and Allowed Overlapped Operation

The cross conduction prevents both high– and low–side switches from conducting at the same time when the dead time (DT) control mode is in half–bridge type, as shown in Figure 56.

Figure 56. Concept of Shoot-Through Prevention

# **Programmable Dead Time Control**

Cross-conduction between both driver outputs (OUTA, and OUTB) is not allowed with minimum dead time ( $t_{DTMIN}$ ) typically 10 ns when the DT pin is open in the MODE-A. External resistance ( $R_{DT}$ ) controls dead time when the DT pin resistor between 1 k $\Omega$  and 300 k $\Omega$  in the

For full topologies flexibility, cross conduction can be allowed both high– and low–side switches conduct at the same time when the DT pin is pulled to  $V_{DD}$  for example, as shown in Figure 57.

Figure 57. Concept of Allowed the Shoot-Through

**MODE–B**. Overlap is not allowed when the dead time (DT) control mode is activated.

The dead time (DT) between both outputs is set according to: DT (in ns) =  $10 \times R_{DT}$  (in k $\Omega$ ).

Overlap is allowed for both outputs when the DT pin is pulled to VDD in the **MODE-C**, as shown in Figure 58.

Figure 58. Timing Chart of Dead-Time Mode Control

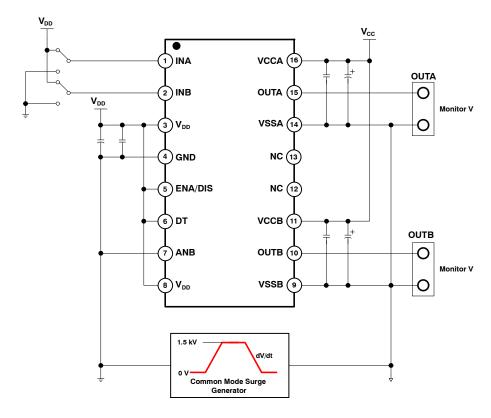

# **Common Mode Transient Immunity Testing**

Figure 59 is a simplified diagram of the Common Mode Transient Immunity (CMTI) testing configuration.

CMTI is the maximum sustainable common–mode voltage slew rate while maintaining the correct output.

CMTI applies to both rising and falling common-mode voltage edges. CMTI is tested with the transient generator connected between GND and VSSA and VSSB. ( $V_{CM} = 1500~V$ )

Figure 59. Common Mode Transient Immunity Test Circuit

#### APPLICATION INFORMATION

This section provides application guidelines when using the NCV51561.

## **Power Supply Recommendations**

It is important to remember that during the Turn-On of switch the output current to the Gate is drawn from the  $V_{\rm CCA}$  and  $V_{\rm CCB}$  supply pins. The  $V_{\rm CCA}$  and  $V_{\rm CCB}$  pins should be bypassed with a capacitor with a value of at least ten times the Gate capacitance, and no less than 100 nF and located as close to the device as possible for the purpose of decoupling. A low ESR, ceramic surface mount capacitor is necessary. We recommend using 2 capacitors; a 100 nF ceramic surface-mount capacitor which can be very close to the pins of the device, and another surface-mount capacitor of few microfarads added in parallel.

## **Input Stage**

The input signal pins (INA, INB, ANB, and ENA/DIS) of the NCV51561 are based on the TTL compatible input-threshold logic that is independent of the V<sub>DD</sub> supply voltage. The logic level compatible input provides a typically high and low threshold of 1.6 V and 1.1 V respectively. The input signal pins impedance of the NCV51561 is 200 k $\Omega$  typically and the INA, INB, and ANB pins are pulled to GND pin and ENA/DIS pin pulled to V<sub>DD</sub> pin for an ENABLE mode as shown in Figure 60. Conversely, ENA/DIS pin pulled to GND pin for the DISABLE version. It is recommended that ENA/DIS pin should be tie to VDD or GND pins for ENABLE and DISABLE versions respectively if the ENA/DIS pin is not used to achieve better noise immunity because the ENA/DIS pin is quite responsive, as far as propagation delay and other switching parameters are concerned.

An RC filter is recommended to be added on the input signal pins to reduce the impact of system noise and ground bounce, the time constant of the RC filter. Such a filter should use an  $R_{IN}$  in the range of 0  $\Omega$  to 100  $\Omega$  and a  $C_{IN}$  between 10 pF and 100 pF. In the example, an  $R_{IN}$  = 51  $\Omega$  and a  $C_{IN}$  = 33 pF are selected, with a corner frequency of approximately 100 MHz. When selecting these components, it is important to pay attention to the trade–off between good noise immunity and propagation delay.

Figure 60. Schematic of Input Stage

#### **Output Stage**

The output driver stage of the NCV51561 features a pull up structure and a pull down structure.

The pull up structure of the NCV51561 consists of a PMOS stage ensuring to pull all the way to the  $V_{CC}$  rail. The pull down structure of the NCV51561 consists of a NMOS device as shown in Figure 61.

The output impedance of the pull up and pull down switches shall be able to provide about +4.5 A and -9 A peak currents typical at 25°C and the minimum sink and source peak currents at 125°C are -7 A sink and +2.6 A source.

Figure 61. Schematic of Output Stage

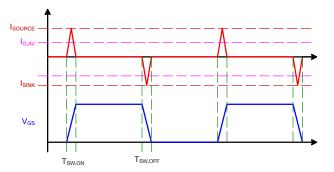

## **Consideration of Driving Current Capability**

Peak source and sink currents ( $I_{SOURCE}$ , and  $I_{SINK}$ ) capability should be larger than average current ( $I_{G, AV}$ ) as shown in Figure 62.

Figure 62. Definition of Current Driving Capability

The approximate maximum gate charge  $Q_G$  that can be switched in the indicated time for each driver current rating may be calculate: Needed driver current ratings depend on what gate charge  $Q_G$  must be moved in what switching time  $t_{SW-ON/OFF}$  because average gate current during switching is  $I_G$ .

$$I_{\text{G.AV}} = \frac{Q_{\text{G}}}{t_{\text{SW,ON/OFF}}} \tag{eq. 1} \label{eq:eq. 1}$$

The approximate gate driver source and sink peak currents can be calculated as below equations

At turn-on (Sourcing current)

$$I_{SOURCE} \ge 1.5 \times \frac{Q_{G}}{t_{SW,ON}}$$

(eq. 2)

At turn-off (Sinking current)

$$I_{SINK} \ge 1.5 \times \frac{Q_G}{t_{SWOFF}}$$

(eq. 3)

where,

$Q_G$  = Gate charge at  $V_{GS}$  =  $V_{CC}$ t<sub>SW, ON/OFF</sub> = Switch On / Off time 1.5 = empirically determined factor

(Influenced by I<sub>G,AV</sub> vs. I<sub>DRV</sub>, and circuit parasitic)

## **Consideration of Gate Resistor**

The gate resistor is also sized to reduce ringing voltage by parasitic inductances and capacitances. However, it limits the current capability of the gate driver output. The limited current capability value induced by turn-on and off gate resistors can be obtained with below equation.

$$I_{SOURCE} = \frac{V_{CC} - V_{OH}}{R_{G,ON}}$$

$$I_{SINK} = \frac{V_{CC} - V_{OL}}{R_{G,OFF}}$$

(eq. 4)

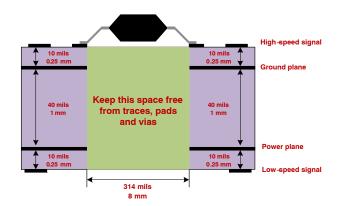

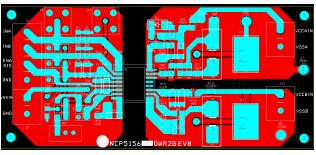

where: