#### RAA271082

Automotive PMIC with Three Synchronous Buck Regulators and One Low Dropout Linear Regulator

The RAA271082 is a versatile multi-rail power IC comprised of a primary high voltage synchronous buck regulator, two secondary low voltage synchronous buck regulators, and an LDO regulator. It offers four overvoltage and undervoltage monitors, I<sup>2</sup>C communications, a general-purpose I/O pin, and a dedicated reset output/fault indicator. RAA271082 was designed using an ASIL-D ISO-26262 development process and is intended to meet ASIL-B device metrics. The RAA271082 includes a second bandgap reference for the OV/UV monitors, built-in self-test at power-up, independent OV/UV monitoring, and continuous CRC error checking on internal registers and I<sup>2</sup>C communications.

Requiring few external components and minimal board space, the RAA271082 provides a high-density power solution. It offers an extensive feature set configured using internal One-Time Programmable (OTP) memory. Nearly all device options such as each output voltage selection, power sequencing, and OV/UV thresholds are internally configured and require no external components for selection. The regulators also offer internal compensation. The bucks are synchronous to achieve high efficiency and are capable of operating in harsh environments requiring high ambient temperature.

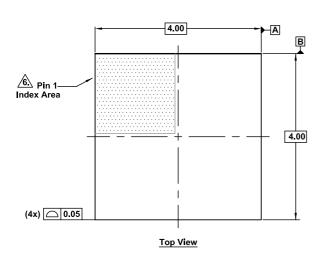

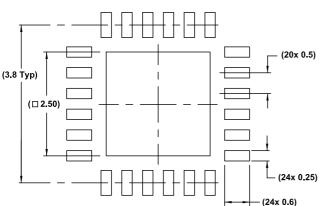

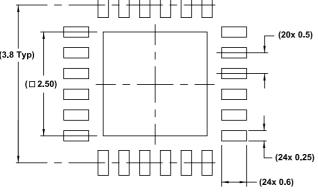

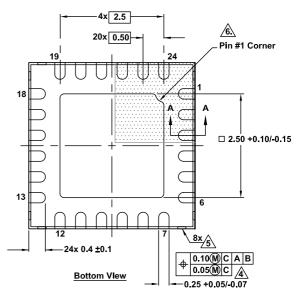

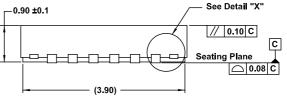

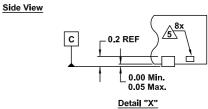

The RAA271082 is available in a 4mm×4mm 24-lead Step Cut QFN (SCQFN) package with an exposed pad for improved thermal performance. It is AEC-Q100 qualified to Grade 1 and operates across an ambient temperature range of -40°C to 125°C and is electrically specified across a junction temperature range of -40°C to 150°C. Automotive PMIC for 32-bit Microcontrollers in BMS, Zone Controller, Domain Controller, and Gateway applications.

### **Applications**

- Driver monitoring cameras

- Rear and surround view HD automotive cameras

- Microcontroller PMIC for battery management systems

- Microcontroller PMIC for zone and domain controllers

- Microcontroller PMIC for gateway units

#### **Features**

- ASIL-D ISO26262 Development Process

- VIN Operating Range from 4.0 to 42V

- Start Range 4.5 to 42V

- Fixed Switching frequency: 2.2MHz with optional pseudo-random spread spectrum

- Three synchronous bucks with internal compensation and one LDO

- Buck1 output range: 2.8V to 5.05V, up to 1A

- Buck2/3 output range: 0.85V to 3.3V, up to 1A

- LDO4 output range: 2.7V to 3.4V, up to 300mA

- OTP UV/OV Thresholds: ±4%, ±6%, ±8%, ±12%

- OTP power up/down sequence and delay

- Optional output discharge on Buck2, Buck3, and LDO4

- Configurable GPIO pin

- Dual EN pins

- Protection Features

- · Input Voltage UVLO

- Output OV/UV

- Overcurrent protection on internal and output LDOs

- · Over-temperature shutdown

- Functional Safety Features

- · Built-in Self Test (BIST) at power up

- Dual Bandgap/Reference Chains

- Independent UV/OV sense path for Buck1 Output

- Configurable Window Watchdog Timer (WWDT)

- Continuous CRC checking of OTP shadow registers

- CRC protected I<sup>2</sup>C communication

- · Configurable fault manager

- AEC-Q100 Qualified, Grade 1: -40°C to +125°C (T<sub>.l</sub> = 150°C)

# **Contents**

| 1. | Over       | Overview 5                                                          |      |  |  |  |

|----|------------|---------------------------------------------------------------------|------|--|--|--|

|    | 1.1<br>1.2 | Typical Application Schematic                                       |      |  |  |  |

| 2. | Pin lı     | nformation                                                          | 7    |  |  |  |

|    | 2.1<br>2.2 | Pin Assignments                                                     |      |  |  |  |

| 3. | Spec       | ifications                                                          | . 10 |  |  |  |

|    | 3.1        | Absolute Maximum Ratings                                            | . 10 |  |  |  |

|    | 3.2        | ESD Ratings                                                         |      |  |  |  |

|    | 3.3        | Thermal Information                                                 |      |  |  |  |

|    | 3.4        | Recommended Operation Conditions                                    | . 11 |  |  |  |

|    | 3.5        | Electrical Specifications                                           | . 11 |  |  |  |

|    |            | 3.5.1 Buck1 Electrical Specifications                               | . 13 |  |  |  |

|    |            | 3.5.2 Buck2 and Buck3 Electrical Specifications                     |      |  |  |  |

|    |            | 3.5.3 LDO4 Electrical Specifications                                |      |  |  |  |

|    |            | 3.5.4 Digital I/O Specifications                                    |      |  |  |  |

|    |            | 3.5.5 I <sup>2</sup> C Interface Specifications                     |      |  |  |  |

| 4. | Typic      | cal Performance Curves                                              | . 18 |  |  |  |

|    | 4.1        | Efficiency, Input Current                                           | . 18 |  |  |  |

|    | 4.2        | Load Regulation                                                     |      |  |  |  |

|    | 4.3        | Line Regulation, Switching Waveforms                                |      |  |  |  |

|    | 4.4        | Load and Line Transient Response                                    | . 21 |  |  |  |

| 5. | Func       | tional Descriptions                                                 | . 22 |  |  |  |

|    | 5.1        | I <sup>2</sup> C Programming Options                                | . 22 |  |  |  |

|    |            | 5.1.1 Voltage Options                                               | . 22 |  |  |  |

|    |            | 5.1.2 Sequence and Switching Options                                |      |  |  |  |

|    |            | 5.1.3 Fault Detection Options                                       |      |  |  |  |

|    |            | 5.1.4 Fault Response Options                                        |      |  |  |  |

|    |            | 5.1.5 Status Indicators                                             |      |  |  |  |

|    | 5.2        | Programmable Output Voltages                                        |      |  |  |  |

|    | 5.3        | Undervoltage and Overvoltage Protection Thresholds                  |      |  |  |  |

|    | 5.4        | Protection Features                                                 |      |  |  |  |

|    | 5.5<br>5.6 | Built-In Self Test (BIST) and CRC Recheck  VIN Undervoltage Lockout |      |  |  |  |

|    | 5.7        | Output Sequencing at Startup and Shutdown                           |      |  |  |  |

|    | 5.8        | Output Soft-Start Ramp                                              |      |  |  |  |

|    | 5.9        | Output Pull-Downs                                                   |      |  |  |  |

|    | 5.10       | I <sup>2</sup> C Programmability                                    |      |  |  |  |

|    | 5.11       | I <sup>2</sup> C and GPIO Bus Connection                            |      |  |  |  |

|    | 5.12       | CRC Fault Detection on Registers and I <sup>2</sup> C Transactions  |      |  |  |  |

|    | 5.13       | Option Programming                                                  |      |  |  |  |

|    | 5.14       | EN Input                                                            |      |  |  |  |

|    | 5.15       | EN_LV Input                                                         | . 33 |  |  |  |

|    | 5.16       | Buck1                                                               | . 33 |  |  |  |

|    | 5.17       | Buck2 and Buck3                                                     | . 33 |  |  |  |

|    | 5.18       | LDO4                                                                | . 34 |  |  |  |

|    |            |                                                                     |      |  |  |  |

### RAA271082 Datasheet

|    | 5.20<br>5.21       | RSTB .<br>GPIO .      | or and Spread Spectrum      | 34<br>36 |

|----|--------------------|-----------------------|-----------------------------|----------|

|    | 5.22               | Window                | ed Watchdog Timer           | 38       |

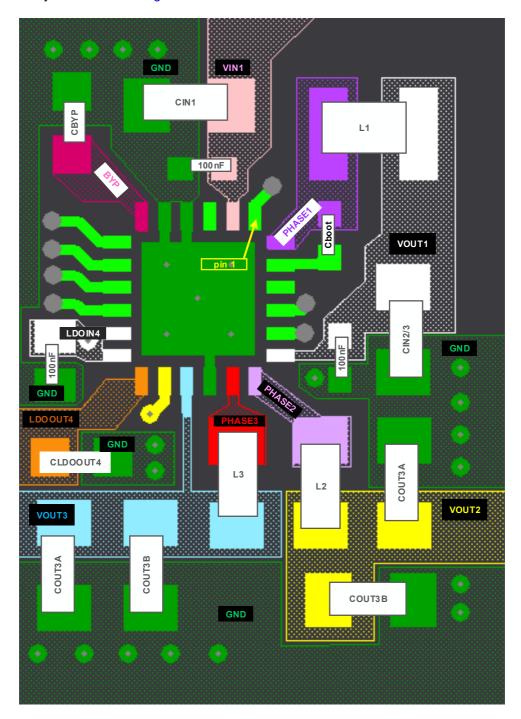

| 6. | Layo               | ut Guide              | lines                       | 40       |

| 7. | I <sup>2</sup> C B | us Opera              | ation                       | 43       |

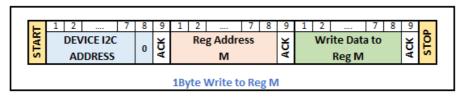

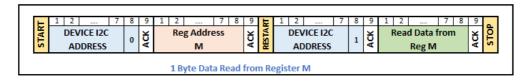

|    | 7.1                | Write Op              | peration                    | 43       |

|    | 7.2                | Read Op               | peration                    | 43       |

|    | 7.3                | I <sup>2</sup> C Timi | ng                          | 44       |

| 8. | Regis              | ster Infor            | mation                      | 45       |

|    | 8.1                | Register              | Address Map                 | 45       |

|    | 8.2                | Register              | Descriptions                | 47       |

|    |                    | 8.2.1                 | DEV_ID_LO_BYTE - 0x60       | 47       |

|    |                    | 8.2.2                 | DEV_ID_HI_BYTE - 0x61       |          |

|    |                    | 8.2.3                 | DEV_REV_LO_BYTE - 0x62      |          |

|    |                    | 8.2.4                 | DEV_REV_HI_BYTE - 0x63      |          |

|    |                    | 8.2.5                 | BUCK_LDO_STATUS1 - 0x64     |          |

|    |                    | 8.2.6                 | BUCK_LDO_STATUS2 - 0x65     |          |

|    |                    | 8.2.7                 | BUCK_LDO_REG_STATE - 0x66   |          |

|    |                    | 8.2.8                 | BUCK_LDO_EN - 0x67          |          |

|    |                    | 8.2.9                 | VIN1_UV_THRESH_OPT - 0x70   |          |

|    |                    | 8.2.10                | VOUT1_VOLTAGE_OPT - 0x71    |          |

|    |                    | 8.2.11                | VOUT1_THRESH_OPT - 0x72     |          |

|    |                    | 8.2.12                | VOUT2_VOLTAGE_OPT - 0x73    |          |

|    |                    | 8.2.13                | VOUT2_THRESH_OPT - 0x74     |          |

|    |                    | 8.2.14                | VOUT3_VOLTAGE_OPT - 0x75    |          |

|    |                    | 8.2.15<br>8.2.16      | VOUT3_THRESH_OPT - 0x76     |          |

|    |                    | 8.2.17                | VOUT4_VOLTAGE_OPT - 0x77    |          |

|    |                    | 8.2.18                | SEQUENCE OPT - 0x79         |          |

|    |                    | 8.2.19                | SS OPT - 0x7A               |          |

|    |                    | 8.2.20                | MISC1 OPT - 0x7B            |          |

|    |                    | 8.2.21                | MISC2_OPT - 0x7C            |          |

|    |                    | 8.2.22                | MISC3 OPT - 0x7D            |          |

|    |                    | 8.2.23                | TRIM CRC LOW - 0x7E         |          |

|    |                    | 8.2.24                | TRIM_CRC_HIGH - 0x7F        |          |

|    |                    | 8.2.25                | FLT STATUS 1 - 0x80         |          |

|    |                    | 8.2.26                | FLT STATUS 2 - 0x81         |          |

|    |                    | 8.2.27                | FLT_STATUS_3 - 0x82         |          |

|    |                    | 8.2.28                | FLT_STATUS_4 - 0x83         | 63       |

|    |                    | 8.2.29                | FLT_LATCHOFF_RESTART - 0x84 | 63       |

|    |                    | 8.2.30                | FLT_RESP_MASK1 - 0x85       | 64       |

|    |                    | 8.2.31                | FLT_RESP_MASK2 - 0x86       | 65       |

|    |                    | 8.2.32                | FLT_RESP_MASK3 - 0x87       | 66       |

|    |                    | 8.2.33                | FLT_GPIO_EN1 - 0x8A         | 66       |

|    |                    | 8.2.34                | FLT_GPIO_EN2 - 0x8B         |          |

|    |                    | 8.2.35                | FLT_GPIO_EN3 - 0x8C         |          |

|    |                    | 8.2.36                | FLT_RSTB_EN - 0x8D          | 69       |

### RAA271082 Datasheet

| 8.2.37 WWDT_CFG - 0xA0           | <br> | 71<br>71 |

|----------------------------------|------|----------|

| 8.2.39 WWDT_LLW - 0xA2           | <br> | 71       |

| <del>-</del>                     |      |          |

| 8 2 40 KICK REG - 0xA3           |      |          |

| 0.2.40 1101_1100 0010            | <br> | 72       |

| 8.2.41 GPIO_CTRL - 0xA4          | <br> | 72       |

| 8.2.42 RSTB_CTRL - 0xA5          | <br> | 72       |

| 8.2.43 CRC_RESULT_LO_BIT - 0xB6  |      |          |

| 8.2.44 CRC_RESULT_HI_BITS - 0xB7 | <br> | 73       |

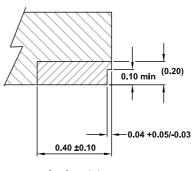

| 9. Package Outline Drawing       | <br> | 74       |

| 10. Ordering Information         | <br> | 75       |

| 11. Revision History             | <br> | 75       |

### 1. Overview

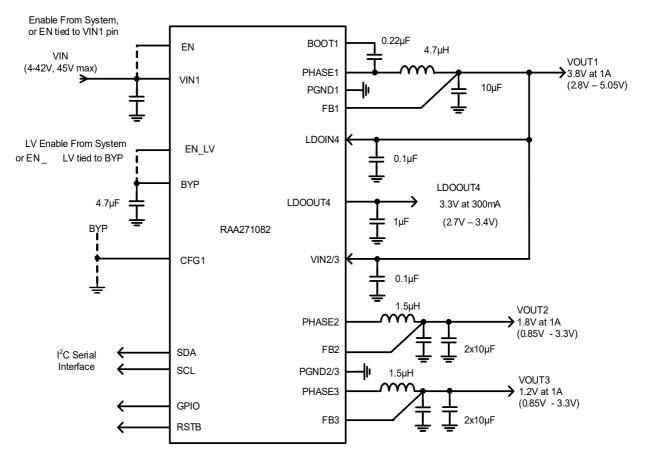

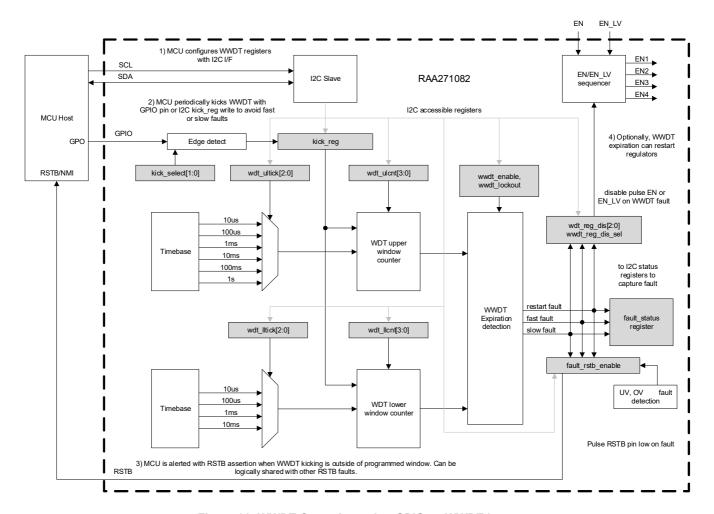

# 1.1 Typical Application Schematic

Figure 1. Typical Application Schematic

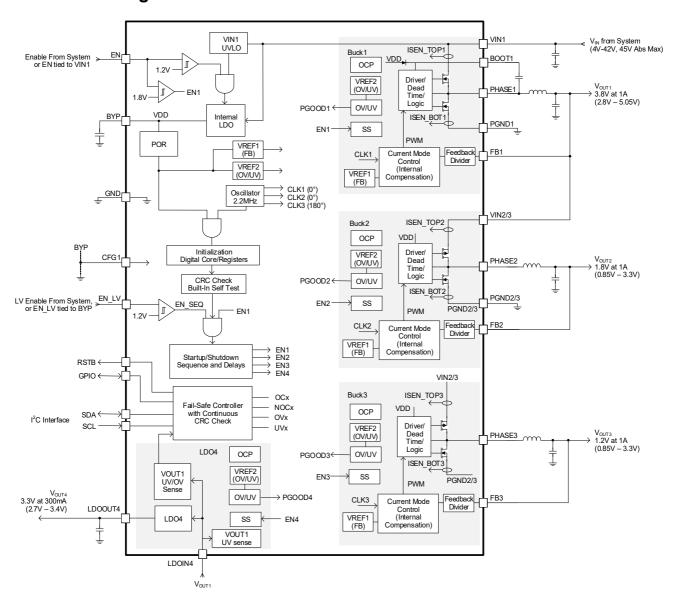

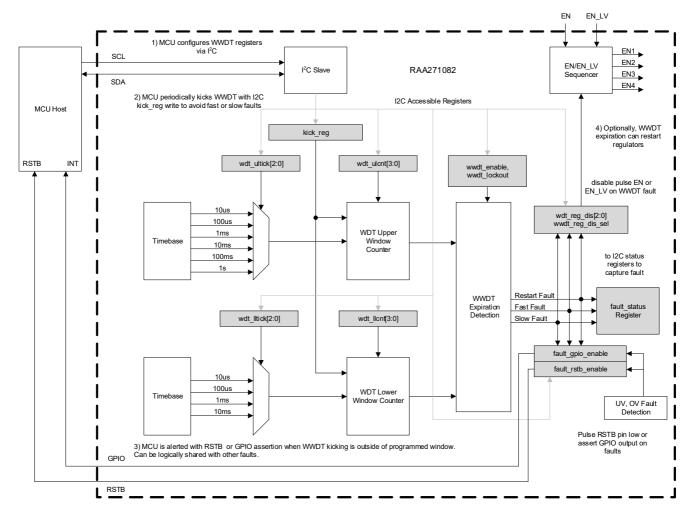

# 1.2 Block Diagram

Figure 2. Block Diagram

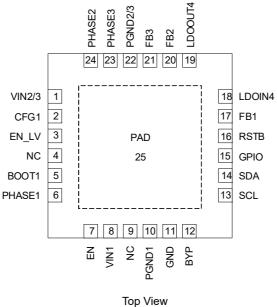

# 2. Pin Information

# 2.1 Pin Assignments

iop vi

## 2.2 Pin Descriptions

| Pin<br>Name |   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN2/3      | 1 | Supply input for Buck2 and Buck3. VIN2/3 must be connected to VOUT1. VIN2/3 is the input to the Buck2 and Buck3 switching regulators. Place a ceramic decoupling capacitor (10µF) from VIN2/3 to PGND2/3, located as close as possible. The DC voltage applied to VIN2/3 should not exceed 5.5V during normal operation.                                                                                                                       |

| CFG1        | 2 | Buck1 configuration input. CFG1 is a tri-level input that configures the Buck1 regulator loop compensation. For details see Configure Pin in Buck1 Electrical Specifications. The three levels are (a) tied low to GND, (b) tied to BYP, and (c) open or floating. In the floating state, the CFG1 voltage is internally pulled to 50% (typical) of the BYP supply voltage.  Note: The CFG1 pin state is read once and latched during Startup. |

| EN_LV       | 3 | Enable Input for Low Voltage Outputs. EN_LV is the enable input that controls the low voltage outputs (Buck2, Buck3, and LDO4). When EN_LV is high, the low voltage regulator startup sequence begins. When EN_LV is set low, the low voltage outputs turn off in reverse sequence. The EN_LV pin has an input range of 0V to VBYP.  Note: The EN_LV pin is ignored when VOUT1 is off.                                                         |

| NC          | 4 | No connection. Not internally connected.  Note: This pin must be unconnected to provide spatial clearance between high-voltage and low-voltage pins on the IC. Do not connect this pin to any net nor to GND.                                                                                                                                                                                                                                  |

| BOOT1       | 5 | Buck1 high-side MOSFET driver supply. BOOT1 provides bias voltage for the Buck1 high-side MOSFET driver. Place a 0.22µF ceramic capacitor between the BOOT1 and PHASE1 pins. The internal bootstrap circuit recharges the boot capacitor when the Buck1 low-side switch is on.                                                                                                                                                                 |

| PHASE1      | 6 | Switching node of Buck1. PHASE1 is the connection point of the high-side N-channel MOSFET and low-side N-channel MOSFET switches of Buck1.                                                                                                                                                                                                                                                                                                     |

| Pin<br>Name | Pin# | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN          | 7    | Enable control input. EN is a tri-level input.  When EN is below 0.95V, the IC is disabled and all faults are cleared.  When EN is between 1.2V and 1.6V, the device enters Standby Mode. The BYP LDO is enabled and factory OTP registers are scanned, but all outputs and switching are disabled. Standby Mode allows changes to be made to the Option Registers using the I <sup>2</sup> C interface.  When EN exceeds 1.85V, the HV Buck1 is enabled and switching begins. The LV outputs (Buck2, Buck3, and LDO4) are also enabled if the EN_LV input is logic high.  The DC voltage applied to EN should not exceed 42V during normal operation. The EN pin can withstand transients up to 45V. |

| VIN1        | 8    | Supply input for the IC and Buck1 switching regulator. VIN1 supplies the Buck1 switching regulator and also supplies the BYP regulator that powers IC circuits. Place a minimum 2.2µF ceramic capacitor in parallel with a 0.1µF ceramic capacitor from VIN1 to PGND1, located as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                                                                        |

| NC          | 9    | <b>No connection.</b> Not internally connected. This pin must be unconnected to provide spatial clearance between high-voltage and low-voltage pins on the IC. Do not connect this pin to any net nor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PGND1       | 10   | <b>Ground return of Buck1.</b> Provides the return path for the low-side MOSFET and drivers of Buck1. The traces connecting this pin to the decoupling capacitor between VIN1 and PGND1 should be as short as possible. Any sensitive signal traces should not connect directly to this ground path. Connect this pin to the ground copper plane and add multiple ground vias close to this pin.                                                                                                                                                                                                                                                                                                      |

| GND         | 11   | <b>System ground.</b> Analog ground pin for internal sensitive analog circuits. Connect GND to a large copper ground plane free from large noisy signals. Connect this pin to PGND1 (pin 10) directly at the pins, with separate ground islands for PGND1 and GND for the associated components. In layout power flow planning, divert any noisy high currents away from the area around this pin and the analog sense pins of the IC.                                                                                                                                                                                                                                                                |

| ВҮР         | 12   | <b>BYP LDO bypass.</b> Bypass/output node of the BYP regulator that supplies bias voltage for the IC. Connect a 4.7μF ceramic capacitor between this pin and PGND1. The BYP LDO supplies a fixed 4.3V bias but the bias operating range is 3V to 5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCL         | 13   | <b>Digital clock input.</b> The serial clock input to the I <sup>2</sup> C interface. Requires external pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDA         | 14   | <b>Digital Data input/output.</b> Serial data input/output to I <sup>2</sup> C interface. Requires external pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

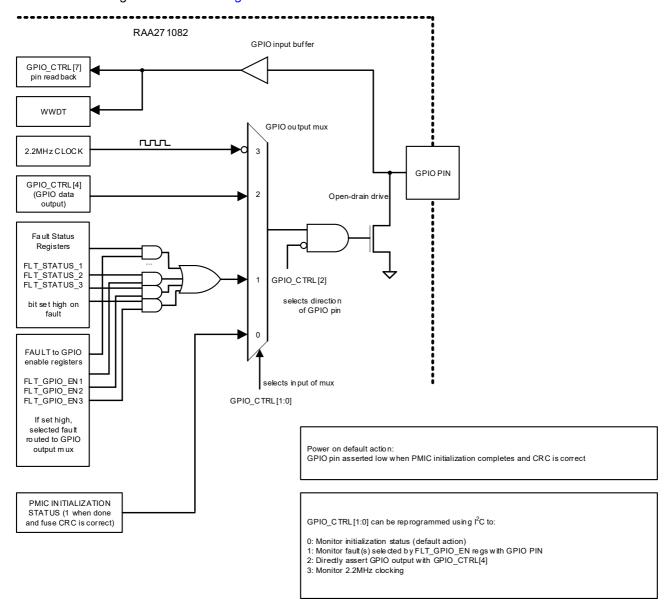

| GPIO        | 15   | <b>Digital general-purpose I/O.</b> The GPIO pin is an open-drain pin that can serve as a status monitor, windowed watchdog timer, or general-purpose I/O. At power-up, the pin is low while the device initializes. When initialization is complete, the GPIO remains low and the outputs begin switching. The GPIO pin function can then be reassigned through the I <sup>2</sup> C interface using register 0xA4.                                                                                                                                                                                                                                                                                  |

| RSTB        | 16   | System reset output. The RSTB is an active low/active high output that provides a reset (low) signal to the system MCU when a fault occurs. Faults that trigger the RSTB output are listed in the RSTB information section. Any faults detected can be read from the Fault Status Registers.  Note: When the RSTB output is high, it is internally driven to the BYP voltage, typically 4.3V. Devices connected to this pin must be able to tolerate signal levels up to the BYP voltage or use a resistor divider to reduce the voltage at the receiving end.                                                                                                                                        |

| FB1         | 17   | Buck1 output voltage sensing input. Connect FB1 to the output of Buck1 to provide the feedback sense voltage for the Buck1 regulator. The Buck1 output voltage is factory-programmable from 2.8V to 5.05V. The Buck1 UV/OV thresholds are factory-programmable also. Route the FB1 trace away from noisy or high-dV/dt signals.  Note: Buck1 UV/OV is sensed through the LDOIN4 input, not through the FB1 input.                                                                                                                                                                                                                                                                                     |

| LDOIN4      | 18   | Input to LDO4. LDOIN4 is the input of the low-dropout linear regulator LDO4. LDO4IN must be connected to the output of Buck1. (The Buck1 output voltage is sensed at FB1, the pin adjacent to LDO4IN.)  Note: LDOIN4 also functions as the UV/OV sense point for Buck1.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LDOOUT4     | 19   | Output of LDO4. LDOOUT4 is the output of the low-dropout linear regulator LDO4. The output voltage is factory-programmable from 2.7V to 3.4V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### RAA271082 Datasheet

| Pin<br>Name | Pin# | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FB2         | 20   | <b>Buck2 output voltage sensing input.</b> Connect FB2 to the output of Buck2 to provide the feedback sense voltage for the Buck2 regulator. The FB2 pin is also the sense point for the Buck2 UV and OV comparators. Route the FB2 trace away from noisy or high-dV/dt signals.                                                                                                                     |

| FB3         | 21   | <b>Buck3 output voltage sensing input.</b> Connect FB3 to the output of Buck3 to provide the feedback sense voltage for the Buck3 regulator. The FB3 pin is also the sense point for the Buck3 UV and OV comparators. Route the FB3 trace away from noisy or high-dV/dt signals.                                                                                                                     |

| PGND2/3     | 22   | Shared ground return for Buck2 & Buck3. Return path for the low-side MOSFETs and gate drivers of Buck2 and Buck3. The decoupling capacitor between VIN2/3 and PGND2/3 should be routed using direct, short PCB traces. Any sensitive signal traces should not share traces with this PGND2/3 return path. Connect this pin to the ground copper plane and add multiple ground vias close to the pin. |

| PHASE3      | 23   | Switching node of Buck3. Connection point of the high-side and low-side MOSFET switches of Buck3.                                                                                                                                                                                                                                                                                                    |

| PHASE2      | 24   | Switching node of Buck2. Connection point of the high-side and low-side MOSFET switches of Buck2.                                                                                                                                                                                                                                                                                                    |

| PAD         | -    | Package thermal pad. PAD must be soldered to a large ground plane on the PCB. Use multiple vias to provide a heat path for the IC package. PAD is not connected internally.                                                                                                                                                                                                                          |

# 3. Specifications

### 3.1 Absolute Maximum Ratings

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                         | Minimum  | Maximum      | Unit |

|-----------------------------------|----------|--------------|------|

| Buck1 Power                       | 1        |              |      |

| VIN1 to PGND1                     | -0.3     | +45          | V    |

| PHASE1 to PGND1 (DC)              | -0.3     | VIN + 0.3    | V    |

| PHASE1 to PGND1 (20ns)            | -2       | VIN + 0.3    | V    |

| BOOT1 to PHASE1                   | -0.3     | +6.0         | V    |

| Buck2, Buck3, LDO4 Power          | <u>'</u> |              |      |

| VIN2/3 to PGND2/3 (DC)            | -0.3     | 5.8          | V    |

| VIN2/3 to PGND2/3 (20ns)          | -0.3     | 7.0          | V    |

| PHASE2, PHASE3 to PGND2/3 (DC)    | -0.3     | VIN2/3 + 0.3 | V    |

| PHASE2, PHASE3 to PGND2/3 (20ns)  |          | 7.0          | V    |

| PHASE2, PHASE3 to PGND2/3 (100ns) | -2.0     |              | V    |

| LDOIN4, LDOOUT4 to PGND2/3        | -0.3     | 5.8          | V    |

| Analog and Digital I/O            | <u>'</u> |              | 1    |

| EN to GND                         | -0.3     | +45          | V    |

| BYP, FB1, FB2, FB3 to GND         | -0.3     | +6.5         | V    |

| SCL, SDA, GPIO to GND             | -0.3     | +6.5         | V    |

| EN_LV, CFG1, RSTB to GND          | -0.3     | BYP + 0.3    | V    |

# 3.2 ESD Ratings

| ESD Model/Test                                       | Pins     | Ratings | Unit |

|------------------------------------------------------|----------|---------|------|

| Human Body Model (Tested per AEC-Q100-002)           | All Pins | 2       | kV   |

| Charged Device Model (Tested per AEC-Q100-011)       | Corner   | 750     | V    |

| Charged Device Model (Tested per AEC-Q 100-011)      | Other    | 500     | V    |

| Latch-Up (Tested per AEC-Q100-004; Class 2, Level A) | -        | 100     | mA   |

### 3.3 Thermal Information

| Thermal Resistance (Typical) | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JC</sub> (°C/W) <sup>[2]</sup> |

|------------------------------|---------------------------------------|---------------------------------------|

| 24 Ld SCQFN Package          | 35.6                                  | 1.2                                   |

<sup>1.</sup> θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features.

<sup>2.</sup> For  $\theta_{\text{JC}}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                  | Minimum   | Maximum | Unit |

|----------------------------|-----------|---------|------|

| Junction Temperature Range | -55       | +150    | °C   |

| Storage Temperature Range  | -65       | +150    | °C   |

| Pb-Free Reflow Profile     | See TB493 |         |      |

# 3.4 Recommended Operation Conditions

| Parameter                               | Minimum | Maximum | Unit |

|-----------------------------------------|---------|---------|------|

| V <sub>IN1</sub> Supply Voltage         | 4[1]    | 42      | V    |

| EN to GND                               | 0       | 42      | V    |

| EN_LV to GND                            | 0       | 5.5     | V    |

| V <sub>IN2/3</sub> Supply Voltage Range | 2.8     | 5.5     | V    |

| Buck1 Output Current                    | 0       | 1.0     | А    |

| Buck2, Buck3 Output Current             | 0       | 1.0     | А    |

| LDO4 Output Current                     | 0       | 0.3     | А    |

| Operating Junction Temperature Range    | -40     | +150    | °C   |

| Ambient Temperature Range               | -40     | +125    | °C   |

| CFG1 to GND                             | 0       | BYP     | V    |

<sup>1.</sup> Minimum VIN1 voltage for startup is 4.5V. After startup, the device can operate down to 4.0V.

# 3.5 Electrical Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V.

| Parameter                                       | Symbol               | Test Conditions                                                                           | Min  | Тур                    | Max  | Unit |

|-------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------|------------------------|------|------|

|                                                 |                      | VIN1 rising<br>(Factory Options)                                                          | -5%  | 4.5<br>(5.0, 6.5, 7.0) | 5%   | V    |

| VIN1 Startup Threshold Voltage                  | V <sub>IN1(UV)</sub> | VIN1 falling                                                                              | 3.45 | 3.60                   | 3.77 | V    |

|                                                 |                      | VIN1 hysteresis                                                                           |      |                        |      |      |

| VIN1 Operating Voltage Range                    | V <sub>IN1</sub>     |                                                                                           | 4    |                        | 42   | V    |

| VIN1 Supply Shutdown Current                    | I <sub>SD</sub>      | EN ≤ 0.4V, VIN1 = 12V                                                                     |      | 1.6                    | 10   | μA   |

| VIN1 Supply Standby Current                     |                      | EN = 1.5V, VIN1 = 12V, EN_LV = GND                                                        |      | 4                      |      | mA   |

| VIN1 Supply Operating<br>Current <sup>[1]</sup> |                      | Figure 1. EN = VIN1 = 12V,<br>EN_LV = BYP. No load on BYP,<br>VOUT1, VOUT2, VOUT3, VOUT4. |      | 17                     |      | mA   |

| EN Pin                                          |                      |                                                                                           |      |                        |      |      |

| EN Shutdown Threshold<br>Voltage                | V <sub>EN(OFF)</sub> |                                                                                           |      |                        | 0.4  | V    |

|                                                 |                      | EN Rising (Standby)                                                                       | 0.71 | 1.2                    | 1.70 | V    |

| EN Enable Standby Threshold Voltage             | V <sub>EN(LDO)</sub> | EN Falling (Standby)                                                                      | 0.52 | 0.86                   | 1.23 | V    |

|                                                 |                      | Falling Hysteresis                                                                        |      | -340                   |      | mV   |

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V. (Cont.)

| Parameter                                            | Symbol               | Test Conditions                                                          | Min  | Тур      | Max  | Unit |

|------------------------------------------------------|----------------------|--------------------------------------------------------------------------|------|----------|------|------|

|                                                      |                      | EN Rising (Buck1 On)                                                     | 1.72 | 1.78     | 1.83 | V    |

| EN Enable Buck1 Threshold<br>Voltage                 | V <sub>EN(BK1)</sub> | EN Falling (Buck1 On)                                                    | 1.54 | 1.59     | 1.64 | V    |

| · chage                                              |                      | Falling Hysteresis                                                       |      | -190     |      | mV   |

| EN Disable Off-Delay                                 |                      | Delay from EN falling edge to commencing shutdown sequence.              |      | 300      |      | μs   |

| EN Pin Input Leakage                                 |                      | EN = 4V to 42V                                                           |      | 0.01     |      | μA   |

| EN_LV Pin                                            |                      |                                                                          | 1    |          | 1    | -1   |

| EN_LV Input Leakage Current                          |                      |                                                                          | -1   |          | 1    | μA   |

| EN_LV Low-Level Input Voltage                        | V <sub>IL</sub>      | (Schmitt input)                                                          |      |          | 0.5  | V    |

| EN 13/15-b 1 15 43/-14                               | V <sub>IH</sub>      |                                                                          | 1.7  |          |      | V    |

| EN_LV High-Level Input Voltage                       |                      | Falling Hysteresis                                                       |      | 315      |      | mV   |

| EN_LV Off-Delay                                      |                      | Delay from EN_LV falling edge to commencing VOUT2/3/4 shutdown sequence. |      | 300      |      | μs   |

| Internal LDO (BYP)                                   |                      |                                                                          |      |          |      | -    |

| Internal LDO Voltage (BYP Pin)                       | V                    | VIN1 = 12V, EN = 1.6V, I <sub>BYP</sub> = 0mA                            | 4.0  | 4.3      | 4.5  | V    |

| iliterilai EDO Voltage (BTF Fili)                    | V <sub>DD(INT)</sub> | VIN1 = 12V, EN = 1.6V, I <sub>BYP</sub> = 20mA                           | 4.0  | 4.3      | 4.5  | V    |

| Internal LDO Dropout Voltage (VDROPOUT = VIN1 – BYP) |                      | VIN1 = 4V, EN = 1.6V, I <sub>BYP</sub> = 20mA                            |      | 71       | 145  | mV   |

|                                                      |                      | BYP Falling                                                              | 2.80 | 3.15     | 3.50 | V    |

| Power-On Reset Threshold Voltage (BYP Pin)           | V <sub>POR</sub>     | BYP Rising                                                               | 3.42 | 3.60     | 3.85 | V    |

| 3 (2                                                 |                      | Rising Hysteresis                                                        |      | 450      |      | mV   |

| Thermal Shutdown <sup>[1]</sup>                      | T <sub>SD</sub>      | Temperature Rising                                                       | 151  | 160      | 170  | °C   |

| memai Shuldowni i                                    | T <sub>SD(HYS)</sub> | Falling Hysteresis                                                       |      | 15       |      | °C   |

| Switching Frequency                                  | f <sub>SW</sub>      | Spread Spectrum Disabled                                                 | 1.98 | 2.20     | 2.42 | MHz  |

| Fault Protection Hiccup Mode<br>Interval             | tHICCUP              | Hiccup Timeout Period                                                    | 180  | 200      | 220  | ms   |

| Buck2 On-Edge to Buck1<br>On-Edge Phase Relationship |                      |                                                                          |      | 0        |      | ۰    |

| Buck3 On-Edge to Buck1<br>On-Edge Phase Relationship |                      | Factory default, (0° option available)                                   |      | 180, (0) |      | 0    |

<sup>1.</sup> Assured by design.

## 3.5.1 Buck1 Electrical Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V.

| Parameter                                                     | Symbol               | Test Conditions                                                                                                       | Min              | Тур                 | Max              | Unit   |

|---------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------|

| Configure Pin                                                 |                      |                                                                                                                       | I                | I                   |                  |        |

| CFG1 Input Low Voltage                                        |                      |                                                                                                                       | 1.283            | 1.498               | 1.685            | V      |

| CFG1 Input Open Voltage                                       |                      | DC voltage measured at open pin                                                                                       | 2.119            | 2.187               | 2.255            | V      |

| CFG1 Input High Voltage                                       |                      |                                                                                                                       | 2.615            | 2.854               | 3.026            | V      |

| CFG1 Leakage                                                  |                      | CFG1 driven by DC source, 0V to BYP.                                                                                  | -29.3            |                     | +31              | μA     |

| FB1 Pin Input Impedance                                       | R <sub>FB1</sub>     |                                                                                                                       |                  | 89                  |                  | kΩ     |

| FB1 Pin Voltage Accuracy<br>at VOUT1 = 3.8V <sup>[1][2]</sup> | V <sub>FB1</sub>     | T <sub>J</sub> = -40°C to +150°C, I <sub>VOUT1</sub> = 0mA<br>Factory Programmed.<br>Other voltage options available. | 3.743<br>[-1.5%] | 3.8                 | 3.857<br>[+1.5%] | V      |

| Buck1 Soft-Start Ramp Time                                    |                      | VOUT1 = from 0% to 95%,<br>(factory options, see Output Soft-Start<br>Ramp)                                           |                  | 1.2                 |                  | ms     |

| Upper Pulse-Skipping                                          |                      | VIN1 rising                                                                                                           | 18.99            | 19.55               | 20.14            | V      |

| Threshold                                                     |                      | VIN1 falling Hysteresis                                                                                               |                  | 1.0                 |                  | V      |

| Undervoltage Threshold                                        | V <sub>FB1(UV)</sub> | VFB1 falling<br>(Factory options)                                                                                     | -1.5             | -8<br>(-4, -6, -12) | +1.5             | %      |

|                                                               | (- ,                 | VFB1 rising hysteresis                                                                                                | +0.4%            | +0.8%               | +1.2%            | %      |

| Severe Undervoltage Threshold                                 |                      | VFB1 Falling                                                                                                          | -24              | -20                 | -16              | %      |

| Undervoltage Fault Delay                                      |                      | FB1 < V <sub>FB1(UV)</sub><br>(Factory options additional delay)                                                      |                  | 2<br>(10, 25, 45)   |                  | μs     |

| Overvoltage Threshold                                         | V <sub>FB1(OV)</sub> | VFB1 rising<br>(Factory options)                                                                                      | -1.5             | +8<br>(+4, +6, +12) | +1.5             | %      |

|                                                               |                      | VFB1 falling hysteresis                                                                                               | -0.4             | -0.8                | -1.2             | %      |

| Overvoltage Fault Delay                                       |                      |                                                                                                                       |                  | 2                   |                  | μs     |

| Severe Undervoltage Threshold                                 |                      | VFB1 falling                                                                                                          | -24              | -20                 | -16              | %      |

| Severe Overvoltage Threshold                                  |                      | VFB1 rising                                                                                                           | -16              | +20                 | 24               | %      |

| Buck1 Output Current Protection                               | on                   |                                                                                                                       | 1                | 1                   |                  |        |

| OC1 Overcurrent Limit,<br>Cycle-by-Cycle                      | I <sub>1(OC1)</sub>  | Factory programmed. (Factory options)                                                                                 | 1.2              | 1.5<br>(1.2, 1.75)  | 1.8              | Α      |

| Overcurrent Limit Blanking Time                               |                      |                                                                                                                       |                  | 75                  | 105              | ns     |

| OC2 Overcurrent Limit,<br>Hiccup/Latch-Off                    | I <sub>1(OC2)</sub>  |                                                                                                                       | 1.61             | 2.00                | 2.42             | Α      |

| Overcurrent Hiccup Delay                                      |                      | Consecutive cycles on I <sub>1(OC2)</sub>                                                                             |                  | 7                   |                  | cycles |

| Negative Current Limit Detection                              | I <sub>1(NLIM)</sub> | Factory programmed. (Factory options)                                                                                 |                  | -0.80<br>(-1.0)     |                  | А      |

| High-side Switch<br>On-Resistance                             | R <sub>HDS</sub>     | I <sub>PHASE1</sub> = 100mA, VIN1 = 12V,<br>BYP = 3.8V, BOOT = 3.8V                                                   |                  | 430                 |                  | mΩ     |

| Low-side Switch On-Resistance                                 | R <sub>LDS</sub>     | I <sub>PHASE1</sub> = 100mA, VIN1 = 12V,<br>BYP = 3.8V                                                                |                  | 336                 |                  | mΩ     |

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V. (Cont.)

| Parameter                       | Symbol             | Test Conditions                            | Min | Тур | Max | Unit |

|---------------------------------|--------------------|--------------------------------------------|-----|-----|-----|------|

| Minimum On-Time <sup>[3]</sup>  | t <sub>ON</sub>    | VIN1 = 5.5V                                | 20  | 35  | 49  | ns   |

| Minimum Off-Time <sup>[3]</sup> | t <sub>OFF</sub>   |                                            | 24  | 36  | 49  | ns   |

| PHASE1 Rise Time <sup>[1]</sup> | t <sub>RISE1</sub> | Figure 1. VIN1 = 12V, V <sub>OUT1</sub> at |     | 4   |     | ns   |

| PHASE1 Fall Time [1]            | t <sub>FALL1</sub> | 200mA load.                                |     | 4   |     | ns   |

| PHASE1 Leakage Current          |                    | VOUT1 not switching                        |     |     | 460 | nA   |

- 1. Buck1 not in Pulse Skipping Mode and Buck1 On-time is greater than the minimum on-time.

- 2. Electrical Specification limits apply only for the factory-programmed settings.

- 3. Minimum on-time and minimum off-time required to maintain loop stability and output regulation.

### 3.5.2 Buck2 and Buck3 Electrical Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C VIN1 = 12V.

| Parameter                                         | Symbol                 | Test Conditions                                                                                                            | Min              | Тур                   | Max              | Unit |

|---------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|------------------|------|

| Input Supply                                      |                        |                                                                                                                            | 1                |                       |                  |      |

| VIN2/3 Voltage Range                              |                        | Internal compensation                                                                                                      | 2.8              |                       | 5.5              | V    |

| VIN2/3 Undervoltage                               |                        | Rising. No output load.                                                                                                    |                  | 2.42                  | 2.60             | V    |

| Threshold                                         | V <sub>IN2/3_UV</sub>  | Falling. No output load.                                                                                                   | 2.10             | 2.30                  |                  | V    |

| VIN2/3 Quiescent Supply<br>Current <sup>[1]</sup> | I <sub>VIN2/3</sub>    | Figure 1 VIN1 = 12V, f <sub>SW</sub> = 2.2MHz.<br>VIN2/3 = 3.8V. VOUT2 = 1.8V,<br>VOUT3 = 1.2V. No load on all<br>outputs. | V. VOUT2 = 1.8V, |                       | mA               |      |

| VIN2/3 Shutdown Supply<br>Current                 | I <sub>SD_VIN2/3</sub> | EN_LV = 0V, VIN2/3 = 5.5V                                                                                                  |                  | 11                    | 18.3             | μA   |

| Output Regulation                                 | 1.                     |                                                                                                                            | 1                | I                     | I                |      |

| FB2 Pin Voltage Accuracy at VOUT2 = 1.8V          | V <sub>FB2</sub>       | $T_J$ = -40°C to +150°C, $I_{VOUT2}$ = 0mA (Factory options)                                                               | 1.773<br>[-1.5%] | 1.8<br>(0.85V – 3.3V) | 1.827<br>[-1.5%] | V    |

| FB3 Pin Voltage Accuracy at VOUT3 = 1.8V          | V <sub>FB3</sub>       | $T_J$ = -40°C to +150°C, $I_{VOUT3}$ = 0mA (Factory options)                                                               | 1.182<br>[+1.5%] | 1.2<br>(0.85V – 3.3V) | 1.218<br>[+1.5%] | V    |

| Buck2 Soft-Start Ramp Time                        |                        | V <sub>OUT2</sub> = 1.8V, from 0% to 95%<br>(factory options, see Output Soft-<br>Start Ramp)                              |                  | 1.2                   |                  | ms   |

| Buck3 Soft-Start Ramp Time                        |                        | V <sub>OUT3</sub> = 1.2V, from 0% to 95%<br>(factory options, see Output Soft-<br>Start Ramp)                              |                  | 0.82                  |                  | ms   |

| Output Voltage Protection                         |                        |                                                                                                                            | 1                |                       |                  |      |

|                                                   |                        | V <sub>FB2</sub> falling<br>(Factory options)                                                                              | -1.5             | -8<br>(-4, -6, -12)   | +1.5             | %    |

| Undervoltage Threshold <sup>[1]</sup>             | V <sub>FB2(UV)</sub>   | V <sub>FB2</sub> Undervoltage tolerance<br>With respect to Programmed UV<br>target                                         | -1.5             |                       | +1.5             | %    |

|                                                   |                        | V <sub>FB2</sub> Undervoltage Hysteresis                                                                                   | +0.4             | +0.8                  | +1.2             | %    |

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C VIN1 = 12V. (Cont.)

| Parameter                              | Symbol                                         | Test Conditions                                                                             | Min   | Тур                 | Max   | Unit   |

|----------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|-------|---------------------|-------|--------|

|                                        |                                                | V <sub>FB2</sub> rising<br>(Factory options)                                                | -1.5  | +8<br>(+4, +6, +12) | +1.5  | %      |

| Overvoltage Threshold <sup>[1]</sup>   | V <sub>FB2(OV)</sub>                           | V <sub>FB2</sub> Overvoltage tolerance<br>With respect to Programmed OV<br>target           | -1.5  |                     | +1.5  | %      |

|                                        |                                                | V <sub>FB2</sub> Overvoltage Hysteresis                                                     | -0.4% | -0.8%               | -1.2% | %      |

|                                        |                                                | V <sub>FB3</sub> falling<br>(Factory options)                                               | -1.5  | -8<br>(-4, -6, -12) | +1.5  | %      |

| Undervoltage Threshold <sup>[1]</sup>  | V <sub>FB3(UV)</sub>                           | V <sub>FB3</sub> Undervoltage tolerance<br>With respect to Programmed UV<br>target          | -1.5  |                     | +1.5  | %      |

|                                        |                                                | V <sub>FB3</sub> Undervoltage Hysteresis                                                    | +0.4  | +0.8                | +1.2  | %      |

|                                        |                                                | V <sub>FB3</sub> rising<br>(Factory options)                                                | -1.5  | +8<br>(+4, +6, +12) | +1.5  | %      |

| Overvoltage Threshold <sup>[1]</sup>   | V <sub>FB3(OV)</sub>                           | V <sub>FB3</sub> Overvoltage tolerance<br>With respect to Programmed OV<br>target           | -1.5  |                     | +1.5  | %      |

|                                        |                                                | V <sub>FB3</sub> Overvoltage Hysteresis                                                     | -0.4% | -0.8%               | -1.2% | %      |

|                                        |                                                | FB2 < V <sub>FB2</sub> (UV)<br>(Factory options)                                            |       | 2<br>(10, 25, 45)   |       | μs     |

| Undervoltage Fault Delay               |                                                | FB3 < V <sub>FB3</sub> (UV)<br>(Factory options)                                            |       | 2<br>(10, 25, 45)   |       | μs     |

| Output Current Protection              |                                                | I                                                                                           |       |                     |       |        |

| Overcurrent Limit,<br>Cycle-by-cycle   | I <sub>2(LIM)</sub> ,<br>I <sub>3(LIM)</sub>   | Buck2 and Buck3<br>(Factory options: Buck2 and Buck3<br>overcurrent limits are independent) |       | 1.2<br>(0.96, 1.56) |       | А      |

| Overcurrent Fault Delay                |                                                |                                                                                             |       | 100                 |       | cycles |

| Negative Current Limit                 | I <sub>2(NLIM)</sub> ,<br>I <sub>3(NLIM)</sub> |                                                                                             | -1.30 | -0.88               | -0.49 | А      |

| Feedback Pin                           | ı                                              |                                                                                             |       | ,                   |       | •      |

| FB2, FB3 Pin Input<br>Impedance        | R <sub>FB2</sub> , R <sub>FB3</sub>            |                                                                                             |       | 64                  |       | kΩ     |

| Power MOSFETs                          | ·                                              |                                                                                             |       | ,                   |       | 1      |

| High-side PMOS Switch<br>On-Resistance |                                                | I <sub>PHASE2,3</sub> = 100mA, VIN2/3 = 3.8V                                                |       | 372                 |       | mΩ     |

| Low-side NMOS Switch<br>On-Resistance  |                                                | I <sub>PHASE2,3</sub> = 100mA, VIN2/3 = 3.8V                                                |       | 161                 |       | mΩ     |

| PHASE2, PHASE3<br>Maximum Duty         |                                                |                                                                                             |       | 90                  |       | %      |

| PHASE2, PHASE3 Minimum<br>On-Time      |                                                |                                                                                             |       |                     | 100   | ns     |

<sup>1.</sup> Undervoltage and Overvoltage factory programmed selections for VOUT1, VOUT2, VOUT3, and LDO4 are independent.

## 3.5.3 LDO4 Electrical Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V.

| Parameter                                   | Symbol                | Test Conditions                                                                                                                     | Min              | Тур                  | Max              | Unit |

|---------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|------------------|------|

| Input Supply                                |                       | 1                                                                                                                                   |                  |                      |                  |      |

| Input Voltage Range                         | V <sub>IN4</sub>      | Connected to VOUT1, VIN2/3                                                                                                          | 2.6              |                      | 5.5              | V    |

| Output Regulation                           | I.                    |                                                                                                                                     | - 11.            | 1                    |                  |      |

| Output Voltage                              | V <sub>LDOOUT4</sub>  | VIN2/3 = 3.8V, V <sub>LDOOUT4</sub> = 3.3V<br>(Factory options)                                                                     | 3.251<br>[-1.5%] | 3.300<br>(2.7V-3.4V) | 3.350<br>[+1.5%] | V    |

| Dropout Voltage                             |                       | V <sub>LDOOUT4</sub> = 3.3V,<br>I <sub>LDOOUT4</sub> = 300mA, 2% drop at<br>V <sub>LDOOUT4</sub>                                    |                  | 112                  | 240              | mV   |

| Power Supply Rejection Ratio <sup>[1]</sup> |                       | At 1kHz, $T_A$ = 25°C, VIN2/3 = 3.8V,<br>Typical Application Schematic on<br>page 3, $V_{LDOOUT4}$ = 3.3V,<br>$I_{LDOOUT4}$ = 300mA |                  | 55                   |                  | dB   |

| LDOOUT4 Soft-Start Ramp Time                |                       | V <sub>OUT4</sub> = 3.3V, from 0% to 95%                                                                                            |                  | 1.55                 |                  | ms   |

| Output Voltage Protection                   |                       |                                                                                                                                     |                  |                      |                  |      |

|                                             |                       | V <sub>LDOOUT4</sub> falling<br>(Factory options)                                                                                   |                  | -8<br>(-4, -6, -12)  |                  | %    |

| Undervoltage Threshold <sup>[2]</sup>       | V <sub>LDO4(UV)</sub> | V <sub>LDOOUT4</sub> Undervoltage tolerance<br>With respect to Programmed UV<br>target                                              | -1.5%            |                      | +1.5%            |      |

|                                             |                       | V <sub>LDOOUT4</sub> rising Hysteresis                                                                                              | +0.4%            | +0.8                 | +1.2%?           | %    |

|                                             |                       | V <sub>LDOOUT4</sub> rising<br>(Factory options)                                                                                    |                  | +8<br>(+4, +6, +12)  |                  | %    |

| Overvoltage Threshold <sup>[2]</sup>        | V <sub>LDO4(OV)</sub> | V <sub>LDOOUT4</sub> Overvoltage tolerance<br>With respect to Programmed OV<br>target                                               | -1.5%            |                      | +1.5%            |      |

|                                             |                       | V <sub>LDOOUT4</sub> falling Hysteresis                                                                                             | -0.4%            | -0.8%                | -1.2%            | %    |

| Undervoltage Fault Delay                    |                       | V <sub>LDOOUT4</sub> < V <sub>LDO4(UV)</sub> (Factory options)                                                                      |                  | 2<br>(10, 25, 45)    |                  | μs   |

| Output Current Protection                   |                       |                                                                                                                                     | •                |                      | •                |      |

| Overcurrent Limit                           | I <sub>4(LIM)</sub>   |                                                                                                                                     | 322              | 422                  | 526              | mA   |

<sup>1.</sup> Assured by design.

<sup>2.</sup> Undervoltage and Overvoltage factory programmed selections for FB1, FB2, FB3, and LDO4 are independent.

### 3.5.4 Digital I/O Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V.

| Parameter                                 | Symbol                | Test Conditions                                                         | Min  | Тур | Max  | Unit |

|-------------------------------------------|-----------------------|-------------------------------------------------------------------------|------|-----|------|------|

| RSTB Output High r <sub>DS(ON)</sub>      |                       | BYP = 4.0V RSTB source current 2mA                                      |      | 60  |      | mΩ   |

| RSTB Output Low r <sub>DS(ON)</sub>       |                       | BYP = 4.6V RSTB sink current 2mA                                        |      | 97  |      | mΩ   |

| GPIO Input High Threshold                 | VIH <sub>(GPIO)</sub> | BYP = 4.3V, GPIO configured as input                                    | 2.24 |     |      | V    |

| GPIO Input Low Threshold                  | VIL <sub>(GPIO)</sub> | BYP = 4.3V, GPIO configured as input                                    |      |     | 1.60 | V    |

| GPIO Output Open-Drain Leakage<br>Current | I <sub>(GPIOLK)</sub> | GPIO configured as output, GPIO pull-up voltage 3.8V.                   |      |     | 1    | μА   |

| GPIO Output Low Voltage                   | VOL <sub>(GPIO)</sub> | GPIO configured as output,<br>BYP = 4.0V<br>GPIO pin sink current = 5mA |      |     | 0.4  | V    |

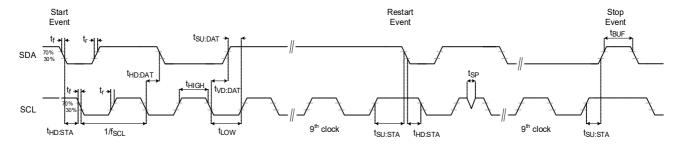

### 3.5.5 I<sup>2</sup>C Interface Specifications

$T_J$  = -40°C to +150°C, VIN1 = 4V to 42V, unless otherwise noted. Typical values are at  $T_J$  = +50 °C and VIN1 = 12V.

| Parameter                                     | Symbol               | Test Conditions        | Min  | Тур | Max | Unit |

|-----------------------------------------------|----------------------|------------------------|------|-----|-----|------|

| SCL, SDA Input High Threshold                 |                      |                        | 1.14 |     |     | V    |

| SCL, SDA Input Low Threshold                  |                      |                        |      |     | 0.8 | V    |

| SCL, SDA Input Hysteresis                     |                      |                        |      | 134 |     | mV   |

| SCL Clock Frequency                           |                      |                        |      |     | 400 | kHz  |

| SCL Falling Edge to SDA Valid<br>Time         |                      |                        |      | 1   |     | μs   |

| SCL, SDA Output Open-Drain<br>Leakage Current |                      | V <sub>SCL</sub> = 5V  |      |     | 1   | μA   |

| SCL, SDA Pin Capacitance                      |                      |                        |      | 5   |     | pF   |

| SDA Output Low Voltage                        | VOL <sub>(SDA)</sub> | SDA sink current = 3mA |      |     | 0.5 | V    |

### 4. Typical Performance Curves

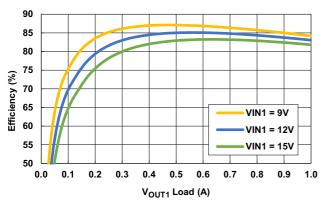

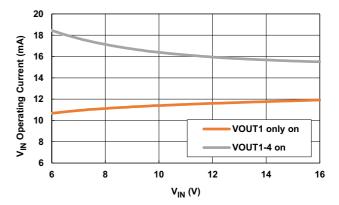

### 4.1 Efficiency, Input Current

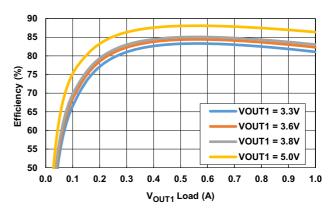

Figure 3.  $V_{IN}$  to  $V_{OUT1}$  = 3.8V, Efficiency vs Load

Figure 4.  $V_{IN}$  = 12V to  $V_{OUT1}$ , Efficiency vs Load

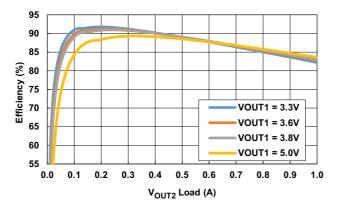

Figure 5. V<sub>OUT1</sub> to V<sub>OUT2</sub> = 1.8V, Efficiency vs Load

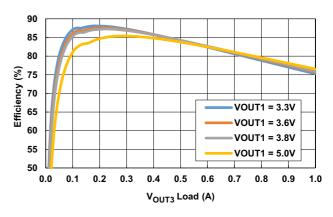

Figure 6. V<sub>OUT1</sub> to V<sub>OUT3</sub> = 1.2V, Efficiency vs Load

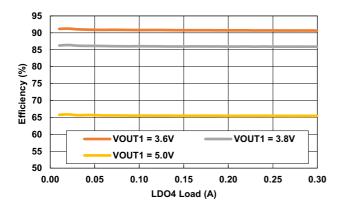

Figure 7. V<sub>OUT1</sub> to LDO4 = 3.3V, Efficiency vs Load

Figure 8. V<sub>IN</sub> Operating Current, No Load

### 4.2 Load Regulation

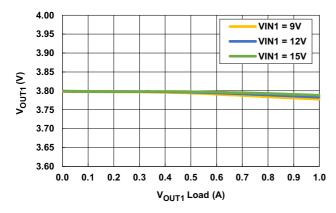

Figure 9. V<sub>OUT1</sub> = 3.8V, Load Regulation

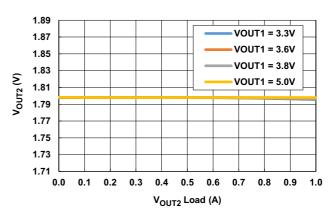

Figure 10. V<sub>OUT2</sub> = 1.8V, Load Regulation

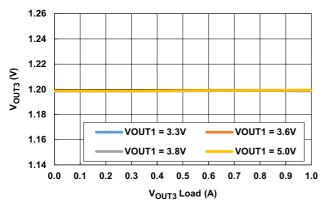

Figure 11. V<sub>OUT3</sub> = 1.2V, Load Regulation

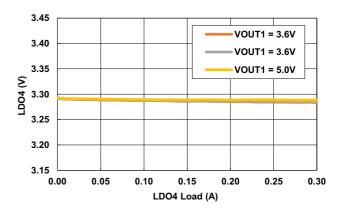

Figure 12. LDO4 = 3.3V, Load Regulation

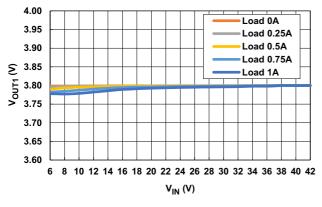

Figure 13. V<sub>OUT1</sub> = 3.8V, Line Regulation

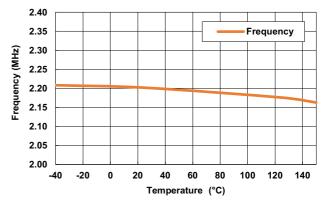

Figure 14. Frequency vs Temperature

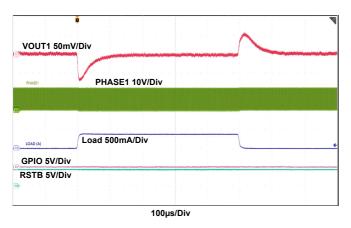

## 4.3 Line Regulation, Switching Waveforms

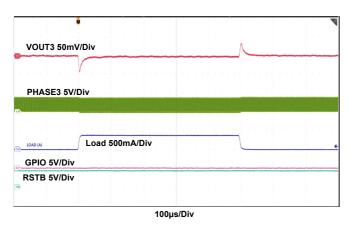

VOUT2 50mV/Div

PHASE2 5V/Div

Load 500mA/Div

GPIO 5V/Div

RSTB 5V/Div

100µs/Div

Figure 15. V<sub>OUT1</sub> Load Transient, 0A to 0.375A

Figure 16. V<sub>OUT2</sub> Load Transient, 0A to 0.375A

Figure 17. V<sub>OUT3</sub> Load Transient, 0A to 0.375A

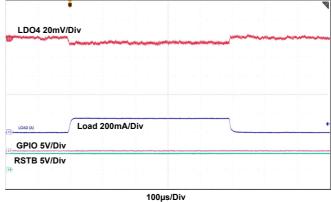

Figure 18. V<sub>OUT4</sub> Load Transient, 0A to 0.375A

Figure 19. V<sub>IN</sub> Transient, 12V to 42V, No Load

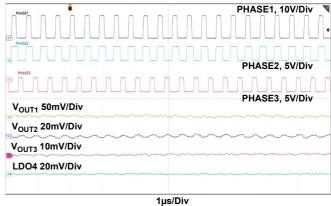

Figure 20. Switching Operation

### 4.4 Load and Line Transient Response

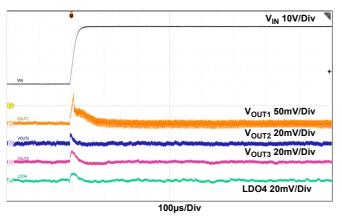

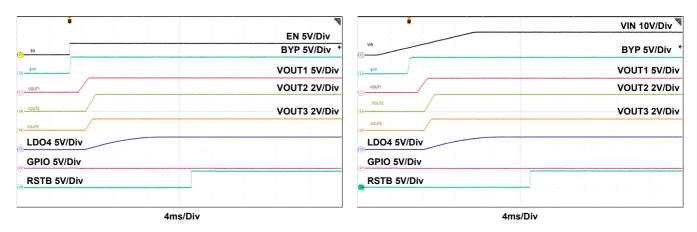

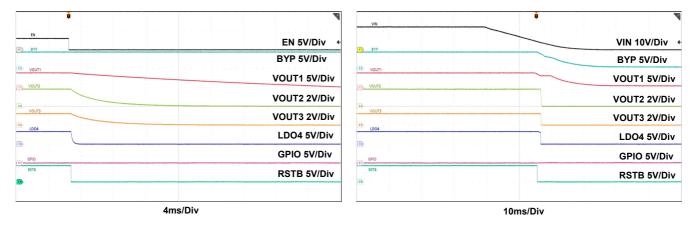

Figure 21. Startup using EN toggle,  $V_{IN} = 12V$

Figure 22. Startup using  $V_{\text{IN}}$  Ramp, EN Connected to VIN

Figure 23. Shutdown using EN toggle,  $V_{IN}$  = 12V

Figure 24. Shutdown using  $V_{\text{IN}}$  ramp, EN connected to  $V_{\text{IN}}$

# 5. Functional Descriptions

### 5.1 I<sup>2</sup>C Programming Options

The RAA271082 multi-rail regulator has numerous options which are factory-set through one-time-programming (OTP). Additionally, the device contains an I<sup>2</sup>C interface that allows the user to select other options, enabling the device to be tested in different configurations. Most of the OTP options cannot be changed unless the device is first placed in Standby mode, in which the required options can be selected using I<sup>2</sup>C commands, and then reenable the outputs. The following are the options that can be changed using the I<sup>2</sup>C interface.

An OTP creation tool is available to aid in the selection of programming options.

### 5.1.1 Voltage Options

• Output voltage options for Buck1, Buck2, Buck3, LDO4. All options are independently selectable.

#### 5.1.2 Sequence and Switching Options

- Output Sequencing, Startup delay, and Shutdown delay. All options are independently selectable.

- Direct startup and shutdown control of each output (disable the internal output sequencing).

- Enable/disable output discharge for Buck2, Buck3, LDO4. All options are independently selectable.

- Spread Spectrum (Off or seven options for spread spectrum).

- Phase shift between Buck1 and Buck3 (0° or 180°).

#### 5.1.3 Fault Detection Options

All Fault Detection options can be disabled except for over-temperature. Disabling detection masks the fault from affecting the RSTB or GPIO pins but does not disable the response to the fault. Some fault responses can be changed or disabled, as listed in Table 1.

**Table 1. Fault Detection Options**

| Fault                                                               | Options                                                                                  | Register(s)                                                                      |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Output Overvoltage All OV thresholds are independently selectable.  | +4%, +6%, +8% (default), +12%                                                            | 0x72 (Buck1) 0x74 (Buck2)<br>0x76 (Buck3) 0x78 (LDO4)<br>Bits 1:0, all registers |

| Output Undervoltage All UV thresholds are independently selectable. | -4%, -6%, -8% (default), -12%                                                            | 0x72 (Buck1) 0x74 (Buck2)<br>0x76 (Buck3) 0x78 (LDO4)<br>Bits 5:4, all registers |

| Buck1 Severe OV, Buck1 Severe UV                                    | Fixed +20% (OV) and -20% (UV). Fault detection and shutdown response cannot be disabled. | N/A                                                                              |

| UV detection delay                                                  | 0 (default), 10, 25, 45 μs<br>(all are added to fixed 2 μs delay)                        | 0x7B Bits 5:4                                                                    |

| Negative Overcurrent, Buck1                                         | -0.8A (default), -1.0A                                                                   | 0x7C Bit 2                                                                       |

| Buck1 Overcurrent                                                   | 1.2A, 1.5A (default), 1.75A                                                              | 0x7C Bits 1:0                                                                    |

| Buck2 Overcurrent                                                   | 0.96A, 1.20A (default), 1.56A                                                            | 0x7D Bits 5:4                                                                    |

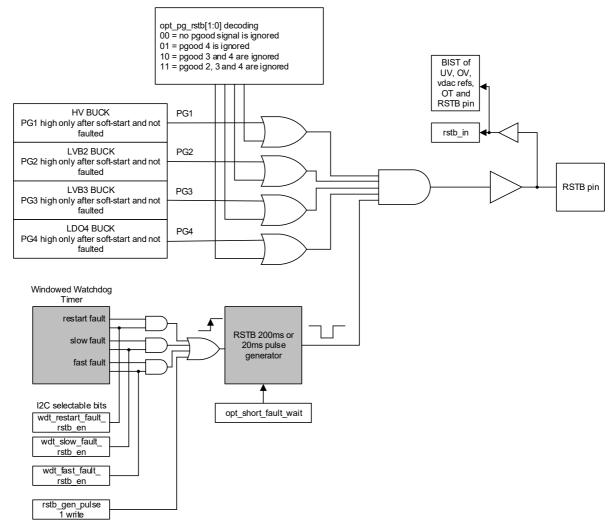

| Buck3 Overcurrent                                                   | 0.96A, 1.20A (default), 1.56A                                                            | 0x7C Bits 7:6                                                                    |