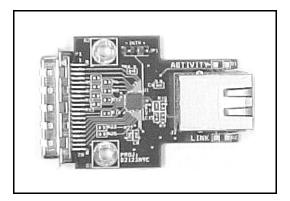

# 78Q21x3-DB *MicroPHY*<sup>™</sup> MII Evaluation Board

# **DEMO BOARD MANUAL**

February 2006

#### DESCRIPTION

The 78Q21x3-DB is a design example for a 10/100BASE-TX Mbit/second Fast Ethernet MII Interface adaptor. A **78Q2123 or 78Q2133 MicroPHY** transceiver from Teridian provides the network physical interface and MII (Medium Independent Interface) interface.

Teridian Semiconductor's MicroPHY is an autosensing, auto-switching 10/100BASE-TX Fast Ethernet transceiver with full duplex operation capability. The device interfaces directly to the IEEE-802.3u MII port. Full-featured MII management functions are included along with an extended register set. The MicroPHY five bit PHY address is defaulted to 0x001. The MicroPHY interfaces to CAT5 UTP cable via a 1:1 transformer.

The transceiver's transmitter includes on-chip the pulse shaper and low power line driver. The receiver incorporates a sophisticated combination of real-time adaptive equalization, an adaptive DC offset adjustment circuit and baseline wander correction. Smart squelch circuitry further improves the receiver's noise rejection. Full featured autonegotiation or parallel detect modes are supported.

The demo board requires operation with a +3.3V power supply.

# **Design Kit contains:**

- √ MicroPHY MII Demo Board

- √ Demo Board Parts List

- √ P.C.B. Gerber Files

- √ Demo Board schematic

- √ MicroPHY Data Sheet

#### 10/100Base-TX Interface

RJ45 Pin Assignment

| <u>Pin</u> | Signal | <u>Pin</u> | Signal |

|------------|--------|------------|--------|

| 1          | TX+    | 5          | N/C    |

| 2          | TX-    | 6          | RX-    |

| 3          | RX+    | 7          | N/C    |

| 4          | N/C    | 8          | N/C    |

#### MII: Medium Independent Interface

Pin Assignment:

(40 Pin Male Subminiature D, 0.050)

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 1          | +3.3V         | 21         | +3.3V         |

| 2          | MDIO          | 22         | COMMON        |

| 3          | MDC           | 23         | COMMON        |

| 4          | RXD3          | 24         | COMMON        |

| 5          | RXD2          | 25         | COMMON        |

| 6          | RXD1          | 26         | COMMON        |

| 7          | RXD0          | 27         | COMMON        |

| 8          | RXDV          | 28         | COMMON        |

| 9          | RXCLK         | 29         | COMMON        |

| 10         | RXER          | 30         | COMMON        |

| 11         | TXER          | 31         | COMMON        |

| 12         | TXCLK         | 32         | COMMON        |

| 13         | TXEN          | 33         | COMMON        |

| 14         | TXD0          | 34         | COMMON        |

| 15         | TXD1          | 35         | COMMON        |

| 16         | TXD2          | 36         | COMMON        |

| 17         | TXD3          | 37         | COMMON        |

| 18         | COL           | 38         | COMMON        |

| 19         | CRS           | 39         | COMMON        |

| 20         | +3.3V         | 40         | +3.3V         |

|            |               |            |               |

| Ordering Number | Description             |  |  |

|-----------------|-------------------------|--|--|

| 78Q21x3-DB      | MicroPHY MII Demo Board |  |  |

#### MII ADAPTOR WITH MICROPHY

#### Use With the Netcom Smart-Bits

The Netcom expects to be the master and defaults to 100BASE-TX Half-Duplex operation. Fast-Ether Windows may require the reconfiguration of the MicroPHY's control register MR0 bits for similar operation. The MicroPHY defaults to auto-negotiate with full capabilities.

After initialization the MicroPHY defaults to 100BASE-TX Full-Duplex operation. When connected to another fully capable transceiver the transceivers will be in full-duplex mode. The default configuration of the Netcom is 100BASE-TX Half-Duplex operation. If data transfers were to commence, the Netcom would display Collision errors (because it does not automatically read the transceivers and reconfigure).

The default MII PHY address for the MicroPHY is 0x001. Additionally, the MicroPHY will respond to the broadcast address 0x000.

If a transceiver is used which defaults to 100BASE-TX Half-Duplex operation, the MicroPHY will adjust itself for half-duplex operation (assuming the MicroPHY is setup for the proper technologies).

To establish proper operation between the MicroPHY and the Netcom, click on the "Options" button followed by selecting "Full Duplex MII". Repeat selecting "Full Duplex MII" twice to ensure that everything is configured identically.

The MicroPHY can be configured for half-duplex operation to minimize incompatibilities with other transceivers and the Netcom.

- 2 -

# 10/100Mbps Transformer Selection

The line interface for the MicroPHY requires a pair of 1:1 isolation transformers. Integrated common-mode chokes are recommended for satisfying FCC radiated EMI requirements. Additional filtering is not required with the MicroPHY due to internal waveform shaping circuitry. The line transformer characteristics are outlined below:

| Name                      | Value         | Condition       |

|---------------------------|---------------|-----------------|

| Turns Ratio               | 1 CT : 1 CT   |                 |

| Open-Circuit Inductance   | 350 μH (min)  | @ 10 mV, 10 kHz |

|                           | See Note 1.   |                 |

| Leakage Inductance        | 0.40 µH (max) | @ 1 MHz (min)   |

| Inter-Winding Capacitance | 25 pF (max)   |                 |

| D.C. Resistance           | 0.9 ohm (max) |                 |

| Insertion Loss            | 1.1 dB (typ)  | 0 - 100 MHz     |

| HIPOT                     | 1500 Vrms     |                 |

Note 1: The receive line transformer's Open-Circuit Inductance can be as low as  $100 \, \mu H$  for the MicroPHY. The MicroPHY incorporates baseline wander correction circuitry, which allows the receiver to track the incoming data signal when there is excessive transformer droop.

#### For Commercial Temperature (0°C ~ 70°C)

Teridian Semiconductor has performed line testing with the following transformers and found their performance acceptable with the MicroPHY:

| <u>Manufacturer</u> | <u>Part Number</u> |  |  |

|---------------------|--------------------|--|--|

| TDK                 | TLA-6T103          |  |  |

| Bel-Fuse            | S558-5999-46       |  |  |

| Halo                | TG22-3506ND        |  |  |

| Pulse               | PE-68515           |  |  |

| Valor               | ST6118             |  |  |

| YCL                 | 20PMT04            |  |  |

The following transformers are low profile packages (0.100 in/2.5 mm or less).

TDK TLA-6T118 Halo TG110-S050 PCA EPF8023G

The following devices integrate the transformers with the RJ45 connector.

TDK TLA-6T704

Delta RJS-1A08T089A

The following devices integrate the transformers, RJ45 connector, LEDs and termination resistors.

Pulse J0011D21B/E

The above evaluations were performed using Netcom's Smart-Bits Fast Ethernet Analyzer. The Teridian Semiconductor MicroPHY MII Adapter and Lancast Fast Ethernet Adapter were attached to the Netcom's Ports A & B respectively. Twisted pair Category 5 General Cable P/N 459360 was used to connect the two transceivers. 100 Mbps performance was measured using cable lengths of both 12 inches and 115 meters. 10 Mbps performance was evaluated using 100 meters of Category 3 cable.

The Netcom was configured to use the Baseline Wander Packet file. Packet length was 1500 bytes.

All transformers listed above met or exceeded IEEE's 802.3 Bit Error Rate requirements of 10<sup>-8</sup>.

# 78Q21x3-DB *MicroPHY*<sup>™</sup> MII Evaluation Board DEMO BOARD MANUAL

# For Industrial Temperature (-40°C ~ +85°C)

Now most of the transformer vendors also offer industrial temp transformer, which will work with the 78Q2133. Here is the recommended industrial temp transformer list:

| <u>Manufacturer</u> | Part Number  |  |  |

|---------------------|--------------|--|--|

| Belfuse             | S558-5999-U5 |  |  |

| Pulse               | HX1148       |  |  |

| Halo                | TG110-E050N5 |  |  |

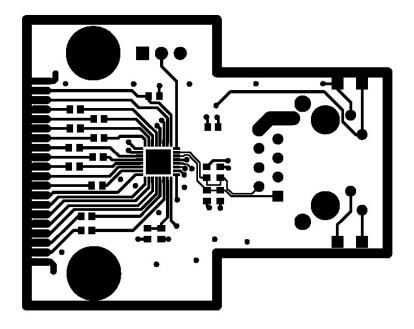

# **PCB Layout Considerations**

The following recommendations enhance the MicroPHY's performance while minimizing EMC emissions:

- 1. The transformer to transceiver signal traces must be  $100\Omega$  differential transmission lines.

- 2. Place the termination network components near the input data pins of the transceiver or transformer.

- Make all differential signal pairs short and of the same length.

- 4. Decouple the transceiver thoroughly with 0.01µF and 0.1µF capacitors.

- 5. Locate these decoupling capacitors as close as possible to the respective transceiver VCC and GND pins.

- 6. All decoupling capacitor and transceiver VCC and GND connections should tie immediately to a VCC or GND plane via with minimum trace inductance.

- 7. Total decoupling capacitance should be greater than the load capacitance that the digital output drivers must drive.

- 8. Use low inductance, ceramic surface mount decoupling capacitors.

- 9. Use a multi-layer PCB with the inner layers dedicated to GND and VCC.

- 10. A single VCC and GND plane is recommended for optimum performance. The lowest possible series impedance is required between the analog and digital VCC and GND pins respectively of the transceiver.

- 11. The outer layers of a 4 layer PCB are to be used for signal routing.

- 12. Place the highest speed signals on the layer adjacent to the GND plane.

- 13. Physically separate the analog signals from the digital signals by placing them on opposite layers or routing them away from each other.

- 14. Additional component and solder side ground layers may be added for maximum EMC containment.

- 15. The GND plane should extend out to the transceiver side of the transformer. Remove the VCC and GND planes from the line side of the transformer to the RJ-45 connector.

- 16. Do not allow the chassis ground plane to cross over the transceiver GND plane. Minimum separation must accommodate over 1.5kV.

- 17. Provide onboard termination of the unused signal pairs in the CAT-5 cable.

- 18. Use a shielded RJ-45 connector with its case stakes soldered to the chassis ground.

- 19. Locate the transformer adjacent to the RJ-45 to minimize the shunt capacitance to the line.

- 20. Minimize RF current fringing by making the VCC plane 0.10 inch smaller than the GND plane. If multiple transceivers are used, provide partitions in the VCC and GND planes between the analog sections. Maintain the partition from the transformer up to the transceiver's analog interface. Do not cross these partitions with signal traces, in particular any digital signals from adjacent transceivers.

- 21. Add series resistors on all transceiver MII outputs to minimize digital output driver peak currents.

- 22. Minimize the use of vias when routing the analog signal traces.

- 23. Isolate the crystal and its capacitors from the analog signals with a guard ring.

- 24. The crystal compensation capacitor value (C2 & C3) must be selected to trim the oscillator's frequency to 25.0000 MHz  $\pm$ 50ppm. The optimum value will be layout dependent. A mere  $\pm$ 4pF can shift the 25MHz  $\pm$ 100Hz. The 25.0000 MHz  $\pm$ 50ppm is specified by the IEEE.

Note: System vendors need to select the proper crystal according to their applications, such as operating environment, product lifetime, and etc since crystal aging, operating temperature, and other factors can affect the crystal frequency tolerance.

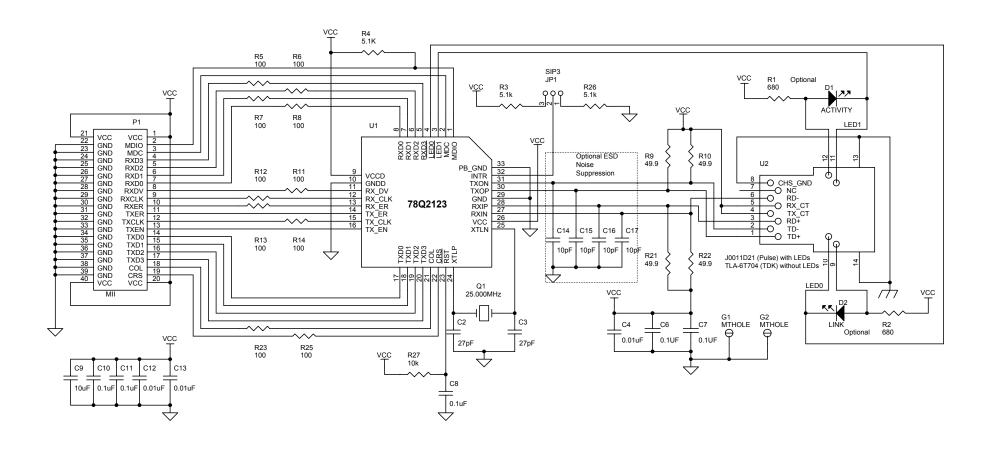

# **MicroPHY Evaluation Board Schematic**

# **MicroPHY MII Demo Board Parts List**

| QTY | REFERENCE NUMBER                        | DESCRIPTION                           | PARTNUMBER             | PACKAGE | MANUFACTURER |

|-----|-----------------------------------------|---------------------------------------|------------------------|---------|--------------|

| 1   | U1                                      | IC, 10/100Mbps LAN<br>Transceiver     | TSC 78Q2123            | QFN32   | TSC          |

| 1   | J2                                      | RJ45, XFRM, LED,<br>10BaseT/100BaseTX | J0011D21B<br>with LEDs |         | PULSE        |

|     |                                         |                                       | TLA-6T704 without LEDs |         | TDK          |

| 1   | Q1                                      | CRYSTAL, 25.000MHZ                    | ECCM1-25.000MHZ        | ECCM1   | ECLIPTEK     |

| 2   | D1,D2                                   | LED, Optional                         | LU20125                | R/A     | LUMEX        |

| 7   | R5,R6,R7,R8,R11,R12,R13,R14,<br>R23,R25 | RES, 100                              |                        | CC0603  |              |

| 2   | R1,R2                                   | RES, 680, Optional                    |                        | CC0603  |              |

| 3   | R3,R4,R26                               | RES, 5.1K                             |                        | CC0603  |              |

| 1   | R27                                     | RES, 10K                              |                        | CC0603  |              |

| 4   | R9,R10,R21,R22                          | RES, 49.9, 1%                         |                        | CC0603  |              |

| 4   | C14,C15,C16,C17                         | CAP, CER, 10PF, Optional              |                        | CC0603  |              |

| 2   | C2,C3                                   | CAP, CER, 27PF                        |                        | CC0603  |              |

| 3   | C4,C12,C13                              | CAP, CER, 0.01UF                      |                        | CC0603  |              |

| 10  | C6,C7,C8,C10,C11                        | CAP, CER, 0.1UF                       | C1608Y51H104Z          | CC0603  | TDK          |

| 1   | C9                                      | CAP, CER, 10UF                        |                        | CC0805  |              |

| 1   | P1                                      | CONN, MALE, 40 PIN                    | FCN-238P040-G/F        |         | FUJITSU      |

| 1   |                                         | P.C.B.                                |                        |         |              |

|     |                                         |                                       |                        |         |              |

|     |                                         |                                       |                        |         |              |

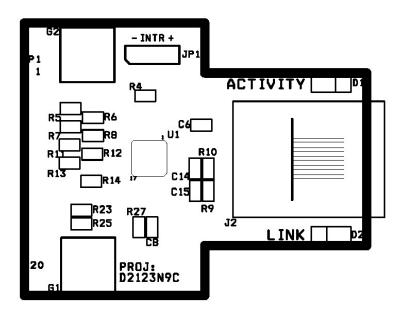

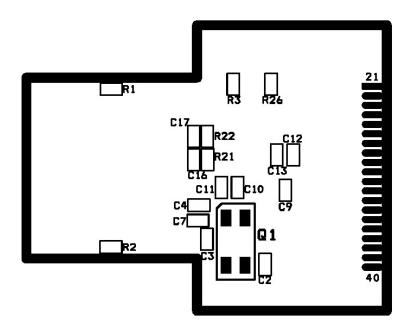

**Top Silkscreen**

- 8 -

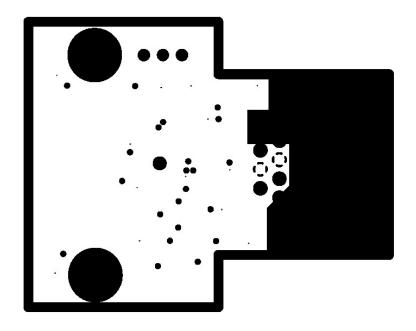

**Top Layer**

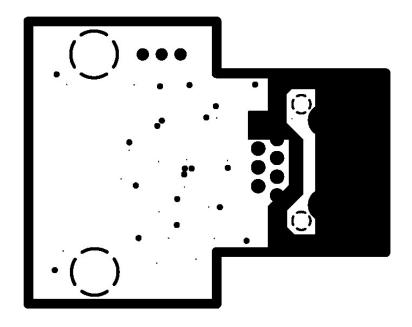

**VCC** Layer

**Ground Layer**

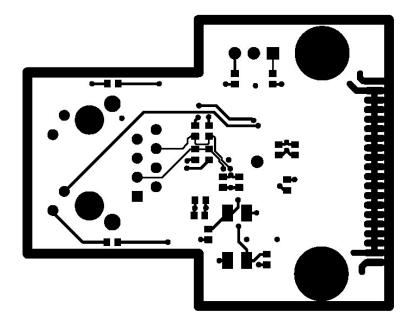

**Bottom Layer**

**Bottom Silkscreen**

No responsibility is assumed by Teridian Semiconductor Corporation for use of this product or for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Teridian Semiconductor Corporation, and the company reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Teridian Semiconductor Corporation, 6440 Oak Canyon, Irvine, CA 92618-5201 TEL: (714) 508-8800, FAX: (714) 508-8877