# Microwave Wideband Synthesizer with Integrated VCO

## **FEATURES**

- ▶ Output frequency range: 800 MHz to 12.8 GHz

- ▶ Jitter = 18 fs<sub>RMS</sub> (integration bandwidth: 100 Hz to 100 MHz)

- ▶ Jitter = 27 fs<sub>RMS</sub> (ADC SNR method)

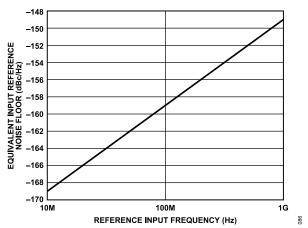

- ▶ Wideband noise floor: -160 dBc/Hz at 12 GHz

- ▶ PLL specifications

- ▶ -239 dBc/Hz: normalized in-band phase noise floor

- ▶ -147 dBc/Hz: normalized in-band 1/f noise

- ▶ Phase detector frequency up to 500 MHz

- ▶ Reference input frequency up to 1000 MHz

- ► Typical spurious f<sub>PFD</sub>: -95 dBc at f<sub>OUT</sub> = 12 GHz

- ▶ Reference input to output delay specifications

- ▶ Device-to-device standard deviation: 3 ps

- ▶ Temperature coefficient: 0.03 ps/°C

- ▶ Adjustment step size: < ±0.1 ps</p>

- ▶ Multichip output phase alignment

- ▶ 3.3 V and 5 V power supplies

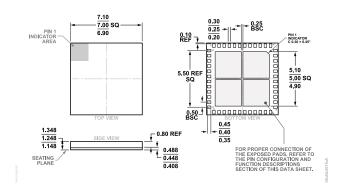

- ▶ 7 mm × 7 mm 48-lead LGA

## **APPLICATIONS**

- ▶ High performance data converter and MxFE clocking

- ▶ Wireless infrastructure (MC-GSM, 5G)

- ► Test and measurement

## **GENERAL DESCRIPTION**

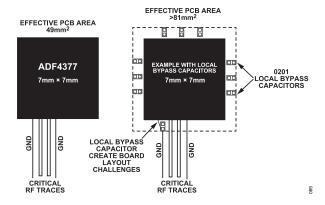

The ADF4377 is a high performance, ultralow jitter, dual output integer-N phased locked loop (PLL) with an integrated voltage controlled oscillator (VCO) ideally suited for data converter and mixed signal front end (MxFE) clock applications. The high performance PLL has a figure of merit of −239 dBc/Hz, ultralow 1/f noise, and a high phase frequency detector (PFD) frequency that can achieve ultralow in-band noise and integrated jitter. The fundamental VCO and output divider of the ADF4377 generate frequencies from 800 MHz to 12.8 GHz. The ADF4377 integrates all necessary power supply bypass capacitors, saving board space on compact boards.

For multiple data converter and MxFE clock applications, the ADF4377 simplifies clock alignment and calibration routines required with other clock solutions by implementing the automatic reference to output synchronization feature, the matched reference to output delays across process, voltage, and temperature feature, and the less than  $\pm 0.1$  ps, jitter free reference to output delay adjustment capability feature.

These features allow for predictable and precise multichip clock and system reference (SYSREF) alignment. JESD204B and JESD204C Subclass 1 solutions are supported by pairing the ADF4377 with an integrated circuit (IC) that distributes pairs of reference and SYSREF signals.

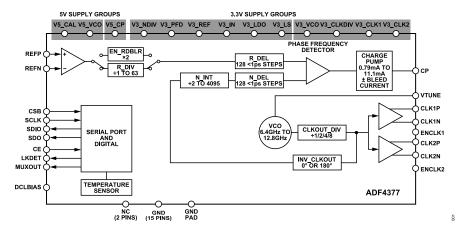

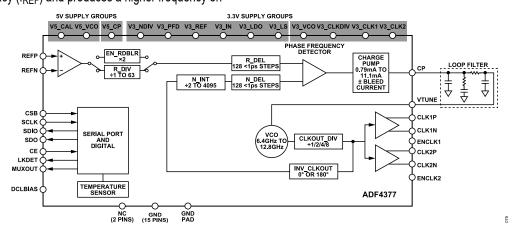

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Specifications                              | 3  |

| Serial Interface Timing Characteristics     | 7  |

| Absolute Maximum Ratings                    | 9  |

| Transistor Count                            | 9  |

| Thermal Resistance                          | 9  |

| Electrostatic Discharge (ESD) Ratings       | 9  |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 12 |

| Theory of Operation                         | 21 |

| Introduction                                | 21 |

| Output Frequency                            | 22 |

| Circuit Description                         | 22 |

| Applications Information                    | 32 |

| Loop Filter Design                          | 32 |

| <del>-</del>                                |    |

| Reference Source Considerations             | 32   |

|---------------------------------------------|------|

| Output Phase Noise Characteristics          | 33   |

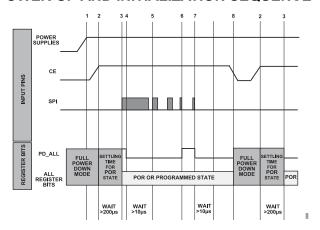

| Power-Up and Initialization Sequence        | 34   |

| Power Supply and Bypassing                  | 34   |

| Design and Programming Example 1:           |      |

| Single ADF4377                              | 35   |

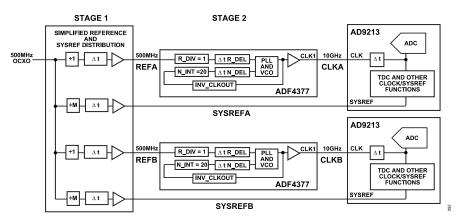

| Aligning Multiple ADF4377 Output Phases     | 39   |

| Design Example 2: JESD204B/C Multichip      |      |

| Clock and SYSREF Alignment                  | 40   |

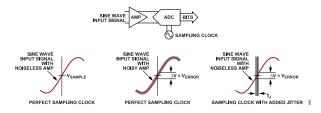

| ADC Clock and Jitter Considerations         | 43   |

| Measuring Differential Spurs With A Single- |      |

| Ended Test Instrument                       | 46   |

| Application Circuits                        | 46   |

| Register Map                                | 48   |

| Register Details                            |      |

| Outline Dimensions                          | . 79 |

| Ordering Guide                              | 79   |

| Evaluation Boards                           | 79   |

# **REVISION HISTORY**

10/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 79

# **SPECIFICATIONS**

3.3 V Supply Group 1 pins voltage ( $V_{3.3V\_1}$ ) = 3.3 V Supply Group 2 pins voltage ( $V_{3.3V\_2}$ ) = 3.15 V to 3.45 V,  $V_{V5\_VCO}$  =  $V_{V5\_CP}$  =  $V_{V5\_CAL}$  = 4.75 V to 5.25 V, all voltages are with respect to GND,  $T_A$  =  $-40^{\circ}$ C to  $+105^{\circ}$ C, operating temperature range, unless otherwise noted.

Table 1.

| Parameter                                          | Symbol                | Min | Тур     | Max  | Unit     | Test Conditions/Comments                                                                                                                 |

|----------------------------------------------------|-----------------------|-----|---------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE INPUTS (REFP, REFN)                      |                       |     |         |      |          |                                                                                                                                          |

| Input Frequency                                    | f <sub>REF</sub>      | 10  |         | 1000 | MHz      |                                                                                                                                          |

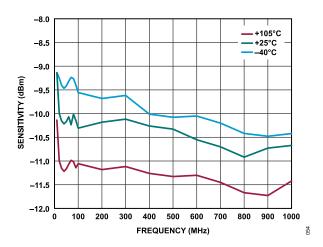

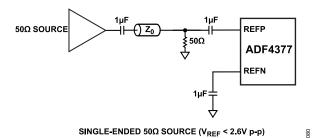

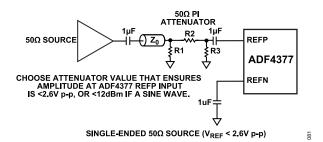

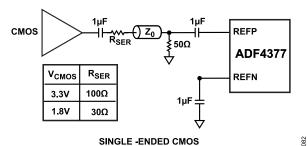

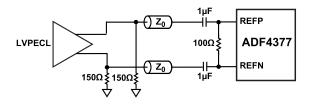

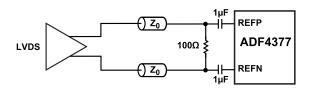

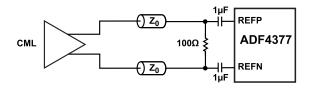

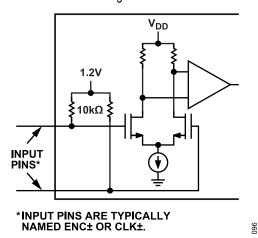

| Input Signal Level                                 | V <sub>REF</sub>      | 0.5 |         | 2.6  | V p-p    | Refer to Figure 61                                                                                                                       |

| Minimum Input Slew Rate                            |                       |     | 100     |      | V/µs     |                                                                                                                                          |

| Input Duty Cycle                                   |                       |     | 50      |      | %        |                                                                                                                                          |

| Self-Bias Voltage                                  |                       |     | 1.85    |      | V        |                                                                                                                                          |

| Input Resistance                                   |                       |     | 3       |      | kΩ       | Differential                                                                                                                             |

| Input Capacitance                                  |                       |     | 1       |      | pF       | Differential                                                                                                                             |

| Input Current                                      |                       |     | -2      |      | μA       |                                                                                                                                          |

| Reference Peak Detector                            |                       |     |         |      |          |                                                                                                                                          |

| Input Frequency                                    |                       | 10  |         | 1000 | MHz      |                                                                                                                                          |

| Minimum Input Signal Detected (REF_OK Bit = 1)     |                       |     | 200     | 1000 | mV p-p   | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                                                                       |

| Maximum Input Signal Not Detected (REF_OK Bit = 1) |                       |     | 160     |      | mV p-p   | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                                                                       |

| 0)                                                 |                       |     | 100     |      | IIIV p-p | IREF = 100 WITZ, SITISIC-CHICCO SITIC WAVE                                                                                               |

| REFERENCE DIVIDER                                  |                       | 1   |         | 63   |          | All integers included                                                                                                                    |

| REFERENCE DOUBLER                                  |                       |     |         |      |          |                                                                                                                                          |

| Input Frequency                                    |                       | 10  |         | 250  | MHz      | EN_RDBLR = 1                                                                                                                             |

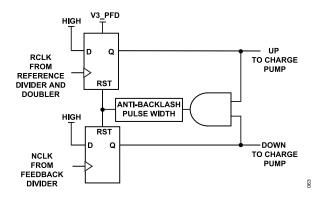

| PHASE/FREQUENCY DETECTOR (PFD)                     |                       | 1.4 |         |      |          | 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                  |

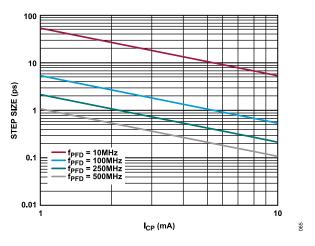

| Input Frequency                                    | f <sub>PFD</sub>      | 3   |         | 500  | MHz      |                                                                                                                                          |

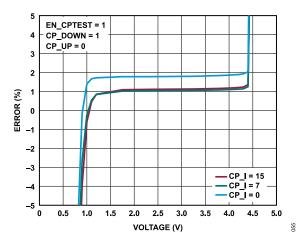

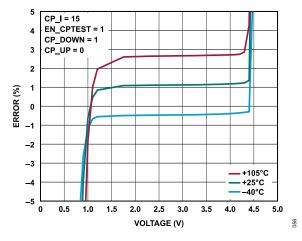

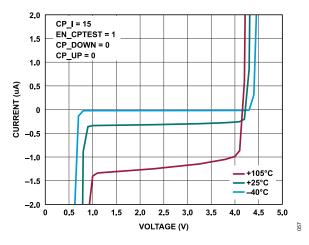

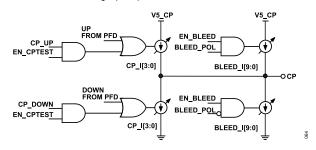

| CHARGE PUMP (CP)                                   | יררט                  |     |         |      | 111112   |                                                                                                                                          |

| Output Current Range                               | I <sub>CP</sub>       |     | 0.79 to |      | mA       | Set by CP_I bit fields                                                                                                                   |

| Supar Sunsin Hangs                                 | 'CP                   |     | 11.1    |      | "" (     | octor of _f bit flows                                                                                                                    |

| Output Current Source/Sink Accuracy                |                       |     | ±2      |      | %        | All CP_I bit field settings, V <sub>CP</sub> = V <sub>V5 CP</sub> /2                                                                     |

| Output Current Source/Sink Matching                |                       |     | ±2      |      | %        | All CP_I bit field settings, $V_{CP} = V_{V5 CP}/2$                                                                                      |

| Output Current vs. Output Volt Sensitivity         |                       |     | 0.2     |      | %/V      | V <sub>CP</sub> <sup>1</sup>                                                                                                             |

| Output Current vs. Temperature                     |                       |     | 280     |      | ppm/°C   | V <sub>CP</sub> = V <sub>V5 CP</sub> /2                                                                                                  |

| Output High-Z Leakage Current                      |                       |     | -0.01   |      | μA       | Minimum I <sub>CP</sub> , V <sub>CP</sub> <sup>1</sup>                                                                                   |

| 5 54 mm 3 1 = mm 3 1 = m                           |                       |     | -0.3    |      | μA       | Maximum I <sub>CP</sub> , V <sub>CP</sub> <sup>1</sup>                                                                                   |

| VCO                                                |                       |     |         |      | Fr. 1    |                                                                                                                                          |

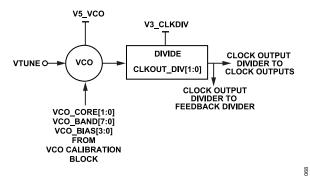

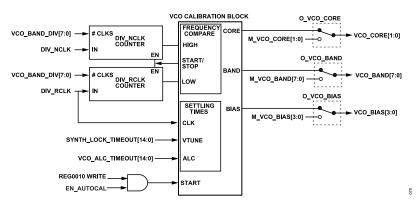

| Frequency Range                                    | f <sub>VCO</sub>      | 6.4 |         | 12.8 | GHz      |                                                                                                                                          |

| Tuning Sensitivity                                 | K <sub>VCO</sub>      |     | 0.75 to |      | %Hz/V    | K <sub>VCO</sub> <sup>2</sup> , <sup>3</sup>                                                                                             |

| ranning conductivy                                 | 1.000                 |     | 1.25    |      | 7011274  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                  |

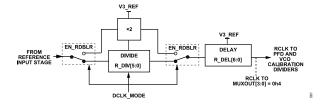

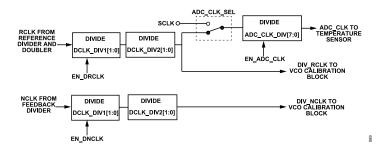

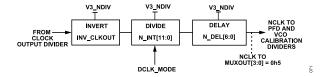

| VCO Calibration Frequency                          | f <sub>DIV_RCLK</sub> |     |         | 125  | MHz      | Must set DCLK_MODE = 1, when f <sub>DIV_RCLK</sub> >                                                                                     |

| FFFDRACK DIVIDED (NV AND CLOCK OUTDUT              |                       |     |         |      |          | 80 MHz                                                                                                                                   |

| FEEDBACK DIVIDER (N) AND CLOCK OUTPUT DIVIDER (O)  |                       |     |         |      |          |                                                                                                                                          |

| N N                                                |                       | 2   |         | 4095 |          | All integers included                                                                                                                    |

| 0                                                  |                       | 1   |         | 8    |          | 1, 2, 4, 8                                                                                                                               |

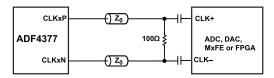

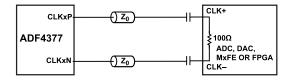

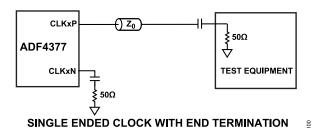

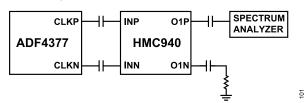

| CLOCK OUTPUTS (CLK1P and CLK1N, CLK2P and          |                       | '   |         |      |          | Differential termination = 100 Ω for all clock                                                                                           |

| CLK2N)                                             |                       |     |         |      |          | output specifications unless noted                                                                                                       |

| Output Frequency                                   | f <sub>OUT</sub>      | 0.8 |         | 12.8 | GHz      |                                                                                                                                          |

| Output Differential Voltage                        | V <sub>OD</sub>       |     | 320     |      | mV       | V <sub>OH</sub> – V <sub>OL</sub> measurement across a differential pair with output driver not toggling and CLKOUT1_OP = CLKOUT2_OP = 0 |

|                                                    |                       |     | 420     |      | mV       | V <sub>OH</sub> – V <sub>OL</sub> measurement across a differential pair with output driver not toggling and CLKOUT1_OP = CLKOUT2_OP = 1 |

analog.com Rev. 0 | 3 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                                          | Symbol                                 | Min                     | Тур                                         | Max             | Unit     | Test Conditions/Comments                                                                                                                        |

|----------------------------------------------------|----------------------------------------|-------------------------|---------------------------------------------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    |                                        |                         | 530                                         |                 | mV       | V <sub>OH</sub> – V <sub>OL</sub> measurement across a differential pair with output driver not toggling and CLKOUT1_OP = CLKOUT2_OP = 2        |

|                                                    |                                        |                         | 640                                         |                 | mV       | V <sub>OH</sub> – V <sub>OL</sub> measurement across a differential pair with output driver not toggling and CLKOUT1_OP = CLKOUT2_OP = 3        |

| Output Resistance                                  |                                        |                         | 100                                         |                 | Ω        | Differential                                                                                                                                    |

| Output Common Mode                                 |                                        |                         | V <sub>CLK</sub> – 1.2<br>× V <sub>OD</sub> |                 | V        |                                                                                                                                                 |

| Output Rise Time                                   | t <sub>R</sub>                         |                         | 15                                          |                 | ps       | 20% to 80%, CLKOUT1_OP = CLKOUT2_OP = 1                                                                                                         |

| Output Fall Time                                   | t <sub>F</sub>                         |                         | 15                                          |                 | ps       | 80% to 20%, CLKOUT1_OP = CLKOUT2_OP = 1                                                                                                         |

| Output Duty Cycle                                  |                                        |                         | 50                                          |                 | %        |                                                                                                                                                 |

| Skew, CLK1P to CLK2P                               |                                        |                         | ±0.5                                        |                 | ps       |                                                                                                                                                 |

| REFERENCE INPUT TO OUTPUT DELAY                    |                                        |                         |                                             |                 |          | Device setup <sup>4</sup> for all delay specifications unless noted, measure rising reference edge at REFP input to rising edge at CLK1P output |

| Propagation Delay Temperature Coefficient          | t <sub>PD-TC</sub>                     |                         | 0.03                                        |                 | ps/°C    | REF_SEL = 0                                                                                                                                     |

| Propagation Delay                                  | t <sub>PD</sub>                        |                         | 104                                         |                 | ps       | $f_{OUT}$ = 12 GHz, $f_{REF}$ = 200 MHz, $f_{PFD}$ = 200 MHz, $R_{L}$ = 1, REF_SEL = 0                                                          |

|                                                    |                                        |                         | 112                                         |                 | ps       | $f_{OUT}$ = 6 GHz, $f_{REF}$ = 200 MHz, $f_{PFD}$ = 200 MHz, $R_{L}$ = 1, REF_SEL = 0                                                           |

|                                                    |                                        |                         | 110                                         |                 | ps       | f <sub>OUT</sub> = 3 GHz, f <sub>REF</sub> = 200 MHz, f <sub>PFD</sub> = 200<br>MHz, R_DIV = 1, REF_SEL = 0                                     |

|                                                    |                                        |                         | 110                                         |                 | ps       | $f_{OUT}$ = 1.6 GHz, $f_{REF}$ = 200 MHz, $f_{PFD}$ = 200 MHz, $R_{DIV}$ = 1, $REF_{SEL}$ = 0                                                   |

|                                                    |                                        |                         | 122                                         |                 | ps       | f <sub>OUT</sub> = 3 GHz, f <sub>REF</sub> = 100 MHz, f <sub>PFD</sub> = 200<br>MHz, EN_RDBLR = 1, REF_SEL = 0                                  |

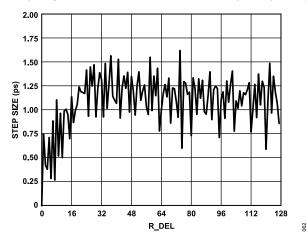

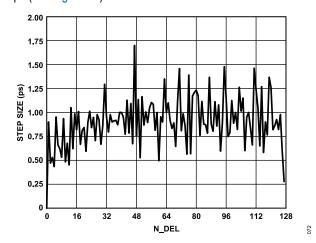

| N_DEL, R_DEL Step Size                             |                                        |                         | 1                                           |                 | ps       |                                                                                                                                                 |

| N_DEL Range                                        |                                        |                         | 110                                         |                 | ps       | N_DEL = 127, R_DEL = 0                                                                                                                          |

| R_DEL Range                                        |                                        |                         | 127                                         |                 | ps       | N_DEL = 0, R_DEL = 127                                                                                                                          |

| LOGIC INPUTS (CSB, SCLK, SDIO, ENCLK1, and ENCLK2) |                                        |                         |                                             |                 |          |                                                                                                                                                 |

| Input High Voltage                                 | V <sub>INH</sub>                       | 1.2                     |                                             |                 | V        |                                                                                                                                                 |

| Input Low Voltage                                  | V <sub>INL</sub>                       |                         |                                             | 0.6             | V        |                                                                                                                                                 |

| Input Current                                      | I <sub>IH</sub> /I <sub>IL</sub>       |                         |                                             | ±1              | μA       |                                                                                                                                                 |

| Input Capacitance (CSB, SCLK, ENCLK1, ENCLK2)      | C <sub>IN</sub>                        |                         | 1                                           |                 | pF       |                                                                                                                                                 |

| SDIO                                               | C <sub>IN-SDIO</sub>                   |                         | 2                                           |                 | pF       |                                                                                                                                                 |

| LOGIC INPUT (CE Pin)                               |                                        |                         |                                             |                 |          |                                                                                                                                                 |

| Input High Voltage                                 | V <sub>INH-CE</sub>                    | 1.8                     |                                             |                 | V        |                                                                                                                                                 |

| Input Low Voltage                                  | V <sub>INL-CE</sub>                    |                         |                                             | 0.8             | V        |                                                                                                                                                 |

| Input Current                                      | I <sub>IH-CE</sub> /I <sub>IL-CE</sub> |                         |                                             | ±1              | μA       |                                                                                                                                                 |

| Input Capacitance                                  | C <sub>IN-CE</sub>                     |                         | 1                                           |                 | pF       |                                                                                                                                                 |

| LOGIC OUTPUTS (SDIO, SDO, LKDET, MUXOUT)           | 111 02                                 |                         |                                             |                 | <u>'</u> |                                                                                                                                                 |

| Output High Voltage (1.8 V Mode)                   | V <sub>OH</sub>                        | 1.5                     | 1.8                                         |                 | V        | $I_{OH}$ = 500 $\mu$ A, 1.8 V output selected (default setting)                                                                                 |

| Output High Voltage (3.3 V Mode)                   | V <sub>OH-3V</sub>                     | V <sub>3.3V</sub> - 0.4 |                                             |                 |          | I <sub>OH</sub> = 500 μA, 3.3 V output selected, set by voltage on V3_LDO pin                                                                   |

| • • • • • • • • • • • • • • • • • • • •            | V <sub>OL</sub>                        |                         |                                             | 0.4             | V        | I <sub>OL</sub> = 500 μA                                                                                                                        |

| Output Low Voltage                                 | VOI                                    |                         |                                             | U. <del>4</del> | V        | 101 - 200 hy                                                                                                                                    |

analog.com Rev. 0 | 4 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                              | Symbol              | Min  | Тур             | Max  | Unit              | Test Conditions/Comments                                                                                             |

|----------------------------------------|---------------------|------|-----------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLIES                         |                     |      | · · · · ·       |      |                   | Device setup <sup>5</sup> for all supply current specifications, unless noted                                        |

| V5_VCO Supply Range                    | V <sub>V5_VCO</sub> | 4.75 | 5               | 5.25 | V                 |                                                                                                                      |

| V5_CAL Supply Range                    | V <sub>V5 CAL</sub> | 4.75 | 5               | 5.25 | V                 |                                                                                                                      |

| V5_CP Supply Range                     | V <sub>V5_CP</sub>  | 4.75 | 5               | 5.25 | V                 |                                                                                                                      |

| V <sub>3.3V_1</sub> Supply Range       | V <sub>3.3V_1</sub> | 3.15 | 3.3             | 3.45 | V                 | 3.3 V Power Supply Group 1 (V3_LS, V3_LDO, V3_REF, V3_PFD, V3_NDIV, V3_IN                                            |

| V <sub>3.3V_2</sub> Supply Range       | V <sub>3.3V_2</sub> | 3.15 | 3.3             | 3.45 | V                 | 3.3 V Power Supply Group 2 (V3_CLK1, V3_CLK2, V3_VCO, V3_CLKDIV)                                                     |

| V5_VCO Supply Current                  | I <sub>V5_VCO</sub> |      | 90              | 135  | mA                | f <sub>OUT</sub> = 12.8 GHz                                                                                          |

|                                        | -                   |      | 170             | 220  | mA                | f <sub>OUT</sub> = 6.4 GHz, CLKOUT_DIV = 0                                                                           |

| V5_CAL Supply Current                  | I <sub>V5_CAL</sub> |      | 50              | 160  | μA                |                                                                                                                      |

|                                        | _                   |      | 8               |      | mA                | During VCO calibration                                                                                               |

| V5_CP Supply Current                   | I <sub>V5_CP</sub>  |      | 55              | 65   | mA                | CP current (I <sub>CP</sub> ) = 11.1 mA, CP_I = 15                                                                   |

|                                        | _                   |      | 26              |      | mA                | I <sub>CP</sub> = 0.79 mA, CP_I = 0                                                                                  |

|                                        |                     |      | 55.2            |      | mA                | CP_I = 15, EN_BLEED = 1, BLEED_I[1:0] = 512                                                                          |

| V <sub>3.3V 1</sub> Supply Current     | I <sub>3.3V_1</sub> |      | 173             | 200  | mA                |                                                                                                                      |

| -                                      | _                   |      | 173             |      | mA                | R_DEL = 127                                                                                                          |

|                                        |                     |      | 176             |      | mA                | REF_SEL = BST_REF = FILT_REF = 1                                                                                     |

|                                        |                     |      | 173             |      | mA                | PD_RDET = 1                                                                                                          |

|                                        |                     |      | 189             |      | mA                | During VCO calibration, EN_DRCLK = EN_DNCLK = EN_ADC_CLK = 1                                                         |

| V <sub>3.3V_2</sub> Supply Current     | I <sub>3.3V_2</sub> |      | 195             |      | mA                | CLKOUT1_OP = CLKOUT2_OP = 0,<br>CLKOUT_DIV = 3                                                                       |

|                                        |                     |      | 169             |      | mA                | CLKOUT1_OP = CLKOUT2_OP = 0                                                                                          |

|                                        |                     |      | 179             |      | mA                | CLKOUT1_OP = CLKOUT2_OP = 1                                                                                          |

|                                        |                     |      | 188             |      | mA                | CLKOUT1_OP = CLKOUT2_OP = 2                                                                                          |

|                                        |                     |      | 197             |      | mA                | CLKOUT1_OP = CLKOUT2_OP = 3,                                                                                         |

|                                        |                     |      | 139             | 160  | mA                | ENCLK2 = low                                                                                                         |

| Typical Power Dissipation              | P <sub>DIS</sub>    |      | 1.75 to 1.9     |      | W                 | ENCLK2 = low, V <sub>3.3V_1</sub> = V <sub>3.3V_2</sub> = 3.3 V,<br>V <sub>V5 VCO</sub> = 5 V, VCO Core 2 and Core 3 |

|                                        |                     |      | 1.95 to<br>2.15 |      | W                 | ENCLK2 = low, V <sub>3.3V_1</sub> = V <sub>3.3V_2</sub> = 3.3 V,<br>V <sub>V5 VCO</sub> = 5 V, VCO Core 0 and Core 1 |

| Typical Power Down Current             |                     |      |                 |      |                   | 1 2 1                                                                                                                |

| 3.3 V Supplies                         |                     |      | 11              | 15   | mA                | PD_ALL = 1, I <sub>3.3V_1</sub> + I <sub>3.3V_2</sub>                                                                |

| 5 V Supplies                           |                     |      | 350             | 750  | μA                | PD_ALL = 1, I <sub>V5_VCO</sub> + I <sub>V5_CAL</sub> + I <sub>V5_CP</sub>                                           |

| Typical Disable Current                |                     |      |                 |      |                   |                                                                                                                      |

| 3.3 V Supplies                         |                     |      | 0.1             | 1.5  | mA                | CE = low, I <sub>3.3V 1</sub> + I <sub>3.3V 2</sub>                                                                  |

| 5 V Supplies                           |                     |      | 350             | 750  | μA                | CE = low, I <sub>V5_VCO</sub> + I <sub>V5_CAL</sub> + I <sub>V5_CP</sub>                                             |

| CLOCK OUTPUT NOISE CHARACTERISTICS     |                     |      |                 |      |                   | 10_00                                                                                                                |

| 12 GHz Output Frequency                |                     |      |                 |      |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 12 GHz                                                                |

| Phase Noise Floor                      |                     |      | -160            |      | dBc/Hz            |                                                                                                                      |

| RMS Jitter                             |                     |      |                 |      |                   |                                                                                                                      |

| 12 kHz to 20 MHz Integration           |                     |      | 17.6            |      | fs <sub>rms</sub> |                                                                                                                      |

| 100 Hz to 100 MHz Integration          |                     |      | 18              |      | fs <sub>rms</sub> |                                                                                                                      |

| Equivalent ADC SNR Method <sup>7</sup> |                     |      | 27              |      | fs <sub>rms</sub> |                                                                                                                      |

| 10 GHz Output Frequency                |                     |      |                 |      |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 10 GHz                                                                |

| Phase Noise Floor                      |                     |      | -159.5          |      | dBc/Hz            | . 33.                                                                                                                |

| RMS Jitter                             |                     |      |                 |      |                   |                                                                                                                      |

analog.com Rev. 0 | 5 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                                         | Symbol                  | Min | Тур    | Max | Unit              | Test Conditions/Comments                                                                          |

|---------------------------------------------------|-------------------------|-----|--------|-----|-------------------|---------------------------------------------------------------------------------------------------|

| 12 kHz to 20 MHz Integration                      |                         |     | 18.5   |     | fs <sub>rms</sub> |                                                                                                   |

| 100 Hz to 100 MHz Integration                     |                         |     | 18.7   |     | fs <sub>rms</sub> |                                                                                                   |

| Equivalent ADC SNR Method <sup>7</sup>            |                         |     | 30     |     | fs <sub>rms</sub> |                                                                                                   |

| 8 GHz Output Frequency                            |                         |     |        |     |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 8 GHz                                              |

| Phase Noise Floor                                 |                         |     | -160.5 |     | dBc/Hz            |                                                                                                   |

| RMS Jitter                                        |                         |     |        |     |                   |                                                                                                   |

| 12 kHz to 20 MHz Integration                      |                         |     | 18     |     | fs <sub>rms</sub> |                                                                                                   |

| 100 Hz to 100 MHz Integration                     |                         |     | 18.3   |     | fs <sub>rms</sub> |                                                                                                   |

| Equivalent ADC SNR Method <sup>7</sup>            |                         |     | 30     |     | fs <sub>rms</sub> |                                                                                                   |

| 6 GHz Output Frequency                            |                         |     |        |     |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 6 GHz                                              |

| Phase Noise Floor                                 |                         |     | -163   |     | dBc/Hz            |                                                                                                   |

| RMS Jitter                                        |                         |     |        |     |                   |                                                                                                   |

| 12 kHz to 20 MHz Integration                      |                         |     | 17.7   |     | fs <sub>rms</sub> |                                                                                                   |

| 100 Hz to 100 MHz Integration                     |                         |     | 18.3   |     | fs <sub>rms</sub> |                                                                                                   |

| Equivalent ADC SNR Method <sup>7</sup>            |                         |     | 27     |     | fs <sub>rms</sub> |                                                                                                   |

| 3 GHz Output Frequency                            |                         |     |        |     |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 3 GHz                                              |

| Phase Noise Floor                                 |                         |     | -165.7 |     | dBc/Hz            |                                                                                                   |

| RMS Jitter                                        |                         |     |        |     |                   |                                                                                                   |

| 12 kHz to 20 MHz Integration                      |                         |     | 17.7   |     | fs <sub>rms</sub> |                                                                                                   |

| 100 Hz to 100 MHz Integration                     |                         |     | 18.3   |     | fs <sub>rms</sub> |                                                                                                   |

| Equivalent ADC SNR Method <sup>7</sup>            |                         |     | 28     |     | fs <sub>rms</sub> |                                                                                                   |

| 1.5 GHz Output Frequency                          |                         |     |        |     |                   | Device setup <sup>6</sup> , f <sub>OUT</sub> = 1.5 GHz                                            |

| Phase Noise Floor                                 |                         |     | -169.5 |     | dBc/Hz            | , 22.                                                                                             |

| RMS Jitter                                        |                         |     |        |     |                   |                                                                                                   |

| 12 kHz to 20 MHz Integration                      |                         |     | 19.5   |     | fs <sub>rms</sub> |                                                                                                   |

| 100 Hz to 100 MHz Integration                     |                         |     | 20.5   |     | fs <sub>rms</sub> |                                                                                                   |

| Equivalent ADC SNR Method <sup>7</sup>            |                         |     | 29     |     | fs <sub>rms</sub> |                                                                                                   |

| Normalized In-Band Phase Noise Floor <sup>8</sup> | L <sub>NORM</sub>       |     | -239   |     | dBc/Hz            |                                                                                                   |

| Normalized 1/f Phase Noise Floor <sup>8</sup>     | L <sub>1/f</sub>        |     | -287   |     | dBc/Hz            | Normalized to 1 Hz                                                                                |

|                                                   | L <sub>1/f_1G_10k</sub> |     | -147   |     | dBc/Hz            | Normalized to 1 GHz at 10 kHz offset                                                              |

| Spurious                                          | //I_IG_IUK              |     | ••     |     |                   |                                                                                                   |

| f <sub>REF</sub>                                  |                         |     | -105   |     | dBc               | LOCKED bit = 1, f <sub>REF</sub> = 100 MHz, f <sub>PFD</sub> = 200                                |

| INEI                                              |                         |     |        |     |                   | MHz, f <sub>OUT</sub> = 12 GHz                                                                    |

| f <sub>PFD</sub>                                  |                         |     | -95    |     | dBc               | LOCKED bit = 1, f <sub>REF</sub> = 100 MHz, f <sub>PFD</sub> = 200 MHz, f <sub>OUT</sub> = 12 GHz |

analog.com Rev. 0 | 6 of 79

## **SPECIFICATIONS**

Table 1.

| Parameter                   | Symbol                  | Min | Тур | Max | Unit | Test Conditions/Comments |

|-----------------------------|-------------------------|-----|-----|-----|------|--------------------------|

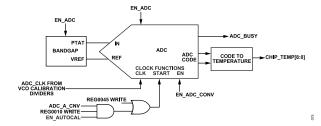

| TEMPERATURE SENSOR (ADC)    |                         |     |     |     |      |                          |

| ADC Clock Frequency         | f <sub>ADC_CLK</sub>    |     |     | 400 | kHz  | ADC clock divider output |

| ADC Clock Divider Frequency | f <sub>ADC</sub> CLKDIV |     |     | 125 | MHz  | ADC clock divider input  |

| Resolution                  | _                       |     |     | 8   | Bits |                          |

$<sup>^{1}</sup>$  1.2 V <  $V_{CP}$  < 3.4 V.

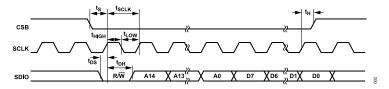

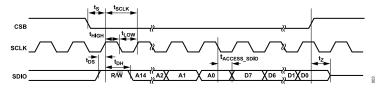

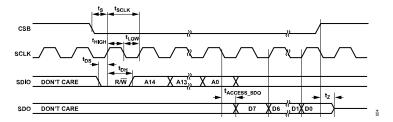

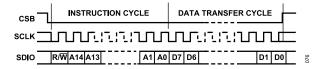

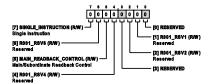

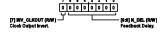

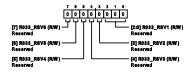

## SERIAL INTERFACE TIMING CHARACTERISTICS

$V_{3.3V_1} = V_{3.3V_2} = 3.15 \text{ V}$  to 3.45 V,  $V_{V5\_VCO} = V_{V5\_CP} = V_{V5\_CAL} = 4.75 \text{ V}$  to 5.25 V, all voltages are with respect to GND,  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , operating temperature range, unless otherwise noted.

Table 2.

| Parameter                                | Symbol                   | Min | Тур | Max | Unit | Test Conditions/Comments                |

|------------------------------------------|--------------------------|-----|-----|-----|------|-----------------------------------------|

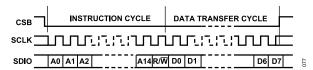

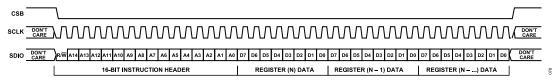

| SERIAL INTERFACE (CSB, SCLK, SDIO, SDO)  |                          |     |     |     |      | See Figure 2, Figure 3, and Figure 4    |

| SCLK Frequency                           | f <sub>SCLK</sub>        |     |     | 65  | MHz  | f <sub>SCLK</sub> = 1/t <sub>SCLK</sub> |

| SCLK Pulse Width High                    | t <sub>HIGH</sub>        | 7.6 |     |     | ns   |                                         |

| SCLK Pulse Width Low                     | t <sub>LOW</sub>         | 7.6 |     |     | ns   |                                         |

| SDIO Setup Time                          | t <sub>DS</sub>          | 3   |     |     | ns   |                                         |

| SDIO Hold Time                           | t <sub>DH</sub>          | 3   |     |     | ns   |                                         |

| SCLK Fall Edge to SDIO Valid Prop Delay  | t <sub>ACCESS_SDIO</sub> | 7.6 |     |     | ns   |                                         |

| SCLK Fall Edge to SDO Valid Prop Delay   | t <sub>ACCESS_SDO</sub>  | 7.6 |     |     | ns   |                                         |

| CSB Rising Edge to SDIO High-Z           | t <sub>Z</sub>           | 7.6 |     |     | ns   |                                         |

| CSB Falling Edge to SCLK Rise Setup Time | t <sub>S</sub>           | 3   |     |     | ns   |                                         |

| SCLK Rising Edge to CSB Rise Hold Time   | t <sub>H</sub>           | 3   |     |     | ns   |                                         |

# **Timing Diagrams**

Figure 2. Write Timing Diagram

analog.com Rev. 0 | 7 of 79

<sup>&</sup>lt;sup>2</sup> Valid for 1.60 V ≤ V<sub>VTUNE</sub> ≤ 2.85 V with device calibrated after a power cycle or software power-on reset.

Based on characterization.

Device setup: f<sub>REF</sub> = 200 MHz, f<sub>PFD</sub> = 200 MHz, f<sub>OUT</sub> = 3000 MHz, ENCLK1 = ENCLK2 = CE = HIGH. Bit fields: R\_DEL = 0, N\_DEL = 0, CP\_I = 15, CLKOUT1\_OP = 1, CLKOUT2\_OP = 1, REF\_SEL = 0, EN\_BLEED = 0, PD\_RDET = 0, PD\_ADC = 0, LOCKED = 1.

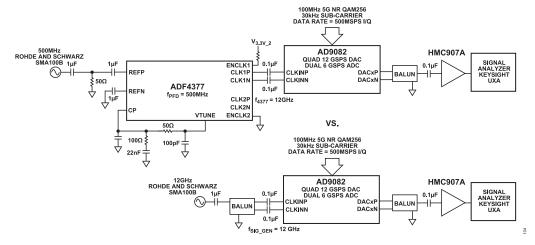

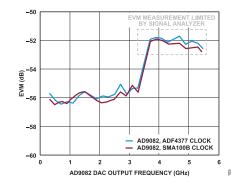

Device Setup: f<sub>REF</sub> = 100 MHz, f<sub>PFD</sub> = 200 MHz, f<sub>OUT</sub> = 12.8 GHz, ENCLK1 = ENCLK2 = CE = HIGH. Bit fields: R\_DEL= 0, N\_DEL = 0, CP\_I = 15, CLKOUT1\_OP = 1, CLKOUT2\_OP = 1, REF\_SEL = 0, EN\_BLEED = 0, PD\_RDET = 0, PD\_ADC = 0, PD\_LD = 0, LOCKED = 1, EN\_DNCLK = EN\_DRCLK = EN\_ADC\_CLK = 0.

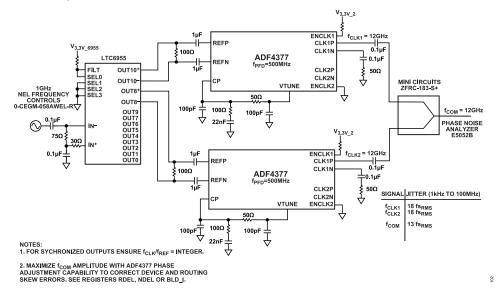

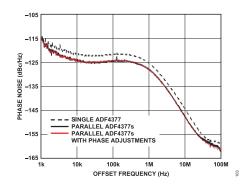

Device Setup: f<sub>REF</sub> = 1000 MHz, f<sub>PFD</sub> = 500 MHz, ENCLK1 = ENCLK2 = CE = HIGH. Bit fields: R\_DEL = 0, N\_DEL\_0, CP\_I = 15, CLKOUT1\_OP = 1, CLKOUT2\_OP = 1, REF\_SEL = 0, EN\_BLEED = 0, PD\_RDET = 0, PD\_ADC = 0, PD\_LD = 0, LOCKED = 1, the reference oscillator is the 0-CEGM-058AWEL-R-1GHz from NEL Frequency Control.

Phase integration range 1 kHz to f<sub>OUT</sub> produces the same result as when clocking an ADC.

<sup>&</sup>lt;sup>8</sup> Refer to Equation 18 through Equation 22. These values are modeled in ADIsimPLL<sup>™</sup>.

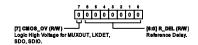

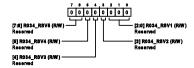

# **SPECIFICATIONS**

Figure 3. 3-Wire Read Timing Diagram (SDO\_ACTIVE = 0)

Figure 4. 4-Wire Read Timing Diagram (SDO\_ACTIVE = 1)

analog.com Rev. 0 | 8 of 79

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3. Absolute Maximum Ratings

| Parameter                                                              | Rating                                                                            |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| V <sub>3.3V_1</sub> (V3_LS, V3_LDO, V3_REF, V3_PFD,<br>V3_NDIV) to GND | -0.3 V to +3.6 V                                                                  |

| V <sub>3.3V_2</sub> (V3_VCO, V3_CLKDIV, V3_CLK1,<br>V3_CLK2) to GND    | -0.3 V to +3.6 V                                                                  |

| V <sub>5V</sub> (V5_CAL, V5_VCO, V5_CP) to GND                         | -0.3 V to +5.5 V                                                                  |

| Voltage on CP Pin                                                      | $-0.3 \text{ V to V}_{V5\_CP} + 0.3 \text{ V}$                                    |

| Digital Outputs (MUXOUT, LKDET, SDO, SDIO)                             | 5 mA                                                                              |

| CLK1P, CLK1N, CLK2P, CLK2N                                             | Maximum (GND - 0.3 V, V <sub>3.3V_2</sub> - 1.2 V) to V <sub>3.3V_2</sub> + 0.3 V |

| REFP, REFN                                                             | -0.65 V to V <sub>3.3V 1</sub> + 0.65 V                                           |

| Voltage on All Other Pins                                              | -0.3 V to V <sub>3.3V 1</sub> + 0.3 V                                             |

| REFP to REFN, when $V_{3.3V-1} > 3 \text{ V}$                          | ±1.35 V                                                                           |

| Operating Junction Temperature Range <sup>1</sup>                      | -40°C to +125°C                                                                   |

| Storage Temperature Range                                              | -40°C to +125°C                                                                   |

| Maximum Junction Temperature                                           | 125°C                                                                             |

| Reflow Soldering                                                       |                                                                                   |

| Peak Temperature                                                       | 260°C                                                                             |

| Time at Peak Temperature                                               | 30 s                                                                              |

Device is guaranteed to meet the specified performance limits over the full operating junction temperature range.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### TRANSISTOR COUNT

The transistor count for the ADF4377 is 114258 (CMOS) and 2941 (bipolar).

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.  $\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 4. Thermal Resistance

| Package |               |                          | θ <sub>JC-</sub> |               |                |             |      |

|---------|---------------|--------------------------|------------------|---------------|----------------|-------------|------|

| Type    | $\theta_{JA}$ | $\theta_{\text{JC-TOP}}$ | воттом           | $\theta_{JB}$ | $\Psi_{ m JT}$ | $\Psi_{JB}$ | Unit |

| CC-48-6 | 28.7          | 25.8                     | 6.3              | 13.1          | 2.6            | 13.7        | °C/W |

Test Condition 1: thermal impedance simulated values are based on use of a 4-layer PCB with the thermal impedance paddle soldered to a ground plane.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDDEC JS-001. Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

# **ESD Ratings for ADF4377**

Table 5. ADF4377, 48-Lead LGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 3500                    | 2     |

| CDM       | 1250                    | C3    |

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 9 of 79

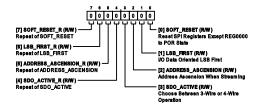

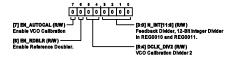

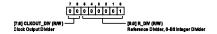

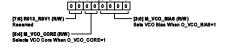

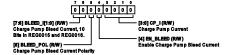

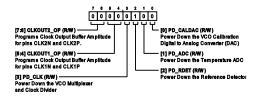

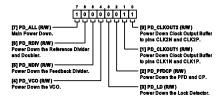

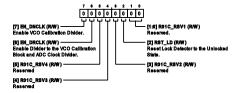

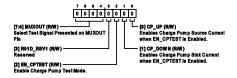

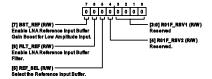

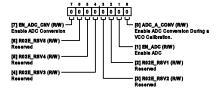

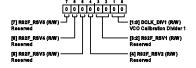

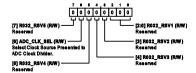

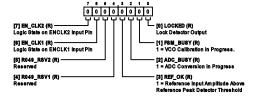

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

Table 6. Pin Function Descriptions

| Pin No.                                                          | Mnemonic     | Description                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 10, 12,<br>14, 16, 18, 19,<br>21, 23, 25, 26,<br>41, 48 | GND          | Negative Power Supply (Ground). These pins must be tied directly to the ground pad.                                                                                                                                                                                                                                                                                         |

| 3                                                                | V3_NDIV      | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Feedback Divider Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                          |

| 5                                                                | V3_VCO       | 3.15 V to 3.45 V Positive Power Supply Pin for the 3.3 V Portion of the VCO Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 2.                                                                                                                                                                                                                      |

| 6                                                                | DCLBIAS      | Do not connect to this pin.                                                                                                                                                                                                                                                                                                                                                 |

| 7                                                                | VTUNE        | VCO Tuning Input. This frequency control pin is normally connected to the external loop filter.                                                                                                                                                                                                                                                                             |

| 8                                                                | V5_CAL       | 4.75 V to 5.25 V Positive Power Supply Pin for VCO Calibration Circuitry. This pin can be shorted to the V5_VCO supply plane.                                                                                                                                                                                                                                               |

| 9                                                                | V5_VCO       | 4.75 V to 5.25 V Positive Power Supply Pin for the 5 V Portion of the VCO Circuitry.                                                                                                                                                                                                                                                                                        |

| 11                                                               | V3_CLKDIV    | 3.15 V to 3.45 V Positive Power Supply Pin for the Output Divider Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                |

| 13                                                               | V3_CLK2      | 3.15 V to 3.45 V Positive Power Supply Pin for the Clock 2 Buffer Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                |

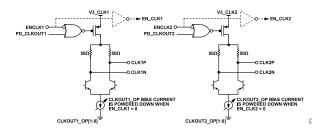

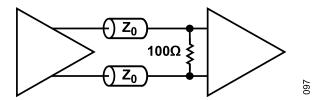

| 15, 17                                                           | CLK2N, CLK2P | Clock 2 Output Signal. The VCO output divider is buffered and presented differentially on these pins. The outputs have 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port. |

| 20, 22                                                           | CLK1N, CLK1P | Clock 1 Output Signal. The VCO output divider is buffered and presented differentially on these pins. The outputs have 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port. |

| 24                                                               | V3_CLK1      | 3.15 V to 3.45 V Positive Power Supply Pin for the Clock 1 Buffer Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                |

| 27                                                               | LKDET        | PLL Lock Detect. This output presents the lock status of the PLL. PLL is locked when the LKDET pin is a logic high.                                                                                                                                                                                                                                                         |

| 28                                                               | ENCLK2       | Enable Clock 2 Output Buffer. 1.8 V and 3.3 V compatible CMOS input. When ENCLK1 = high, the CLK2P and CLK2N output buffer is active. When ENCLK2 = low, the CLK2P and CLK2N output buffer is powered down.                                                                                                                                                                 |

| 29                                                               | ENCLK1       | Enable Clock 1 Output Buffer. 1.8 V and 3.3 V compatible CMOS input. When ENCLK1 = high, the CLK1P and CLK1N output buffer is active. When ENCLK1 = low, the CLK1P and CLK1N output buffer is powered down.                                                                                                                                                                 |

| 30                                                               | V3_LS        | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal Level Shift Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                          |

| 31                                                               | CE           | Chip Enable. 3.3 V CMOS input. Does not support 1.8 V CMOS levels. This CMOS input enables the device when driven high. A logic low disables the device, putting the device in a full power-down state, causing the registers to reset. Conversely, the PD_ALL bit powers down the device, but does not reset the registers.                                                |

| 32                                                               | CSB          | Serial Port Chip Select. 1.8 V and 3.3 V compatible CMOS input. This CMOS input initiates a serial port communication burst when driven low, ending the burst when driven back high.                                                                                                                                                                                        |

analog.com Rev. 0 | 10 of 79

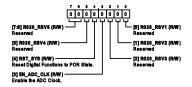

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

# Table 6. Pin Function Descriptions

| Pin No.     | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 33          | SDIO       | Serial Data Input/Output. 1.8 V and 3.3 V programmable CMOS input/output. When configured as an input, the serial port uses this CMOS input for data. In 3-wire readback mode (default mode), this pin outputs data from the serial port during a read communication burst.                                                                                                                                                                                              |  |

| 34          | SCLK       | Serial Port Clock. 1.8 V and 3.3 V compatible. This CMOS input clocks serial port input data on its rising edge.                                                                                                                                                                                                                                                                                                                                                         |  |

| 35          | SDO        | Optional Serial Data Output. 1.8 V and 3.3 V programmable CMOS output. In 3-wire mode (default mode), this three state CMOS pin remains in a high impedance state. In 4-wire readback mode, this pin presents data from the serial port during a read communication purst. When the $\overline{\text{CS}}$ is deasserted, SDO returns to a high impedance. Optionally, attach a resistor of > 200 kΩ to prevent a floating output.                                       |  |

| 36          | V3_LDO     | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal LDO Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                               |  |

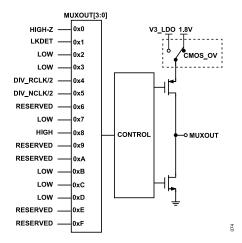

| 37          | MUXOUT     | Internal Device Mux Output. This output pin can be connected to multiple internal nodes for factory test and debug purposes.                                                                                                                                                                                                                                                                                                                                             |  |

| 38, 39      | NC         | No Connect or GND. These pins are connected internally to ESD diodes.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 40          | V3_IN      | 3.15 V to 3.45 V Positive Power Supply. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                                                                  |  |

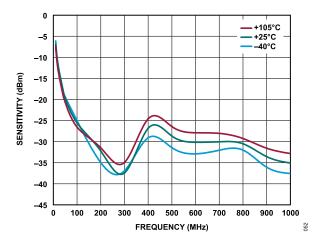

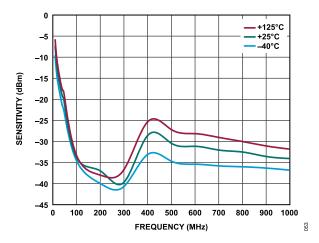

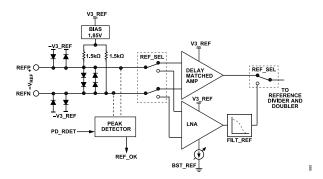

| 42, 43      | REFP, REFN | Reference Input Signal. This differential input is buffered with a delay matched amplifier (DMA) for well controlled reference to output propagation delays (default mode, REF_SEL = 0). For low slew rate reference input signals, an alternate low noise amplifier (LNA) can be selected via the serial port (REF_SEL = 1). Reference inputs are self-biased and must be ac-coupled with 1 µF capacitors. Reference inputs accept differential or single-ended inputs. |  |

| 44          | V3_REF     | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Reference Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                              |  |

| 45          | V3_PFD     | 3.15 V to 3.45 V Positive Power Supply Pin for PFD Circuitry. Short this pin to the other pins in 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                                            |  |

| 46          | V5_CP      | 4.75 V to 5.25 V Positive Power Supply Pin for Charge Pump Circuitry. This pin must be isolated from the V5_VCO supply plane.                                                                                                                                                                                                                                                                                                                                            |  |

| 47          | CP         | Charge Pump Output. This bidirectional current output is normally connected to the external loop filter.                                                                                                                                                                                                                                                                                                                                                                 |  |

| Exposed Pad | EP         | Exposed Pad. Negative power supply (ground). The exposed pad must be soldered directly to the PCB land. The PCB land pattern must have multiple thermal vias to the ground plane for both low ground inductance and low thermal resistance.                                                                                                                                                                                                                              |  |

analog.com Rev. 0 | 11 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{3.3V-1} = V_{3.3V-2} = 3.3 \text{ V}$ ,  $V_{5V} = 5 \text{ V}$ , all voltages are with respect to GND,  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

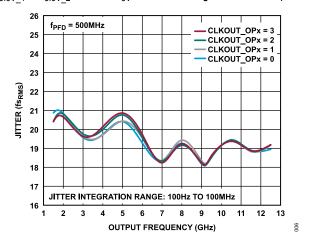

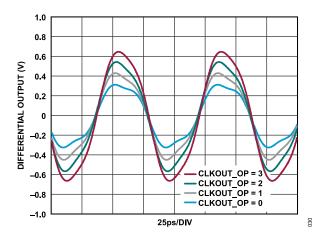

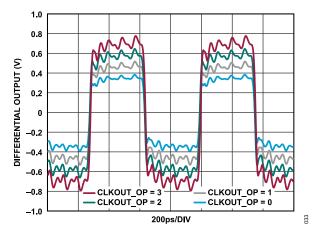

Figure 6. Jitter vs. Output Frequency at Various Output Amplitudes

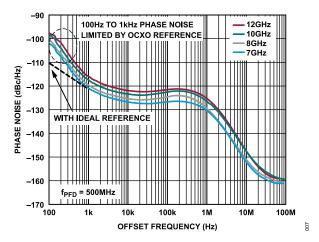

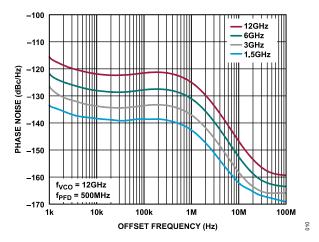

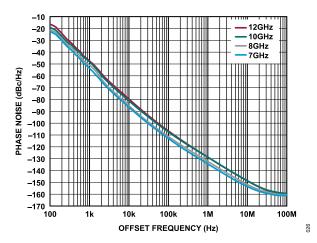

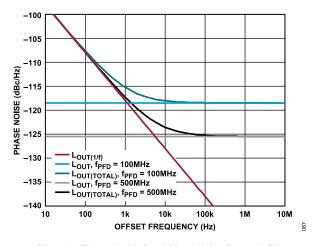

Figure 7. Closed Loop Phase Noise at Various Output Frequencies

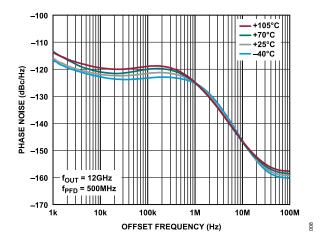

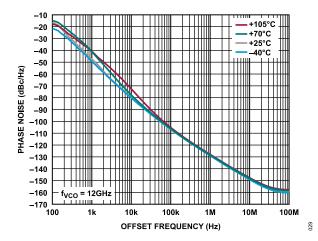

Figure 8. Closed Loop Phase Noise at Various Temperatures

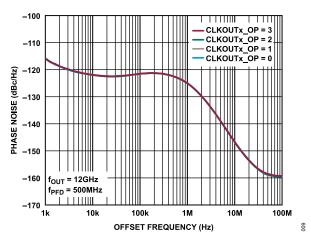

Figure 9. Closed Loop Phase Noise at Various Output Amplitudes

Figure 10. Closed Loop Phase Noise at Various CLKOUT\_DIV Settings

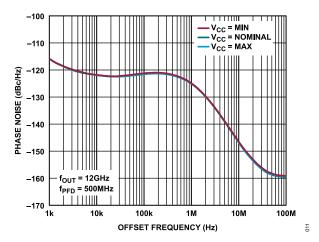

Figure 11. Closed Loop Phase Noise at Various Power Supply Voltages

analog.com Rev. 0 | 12 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

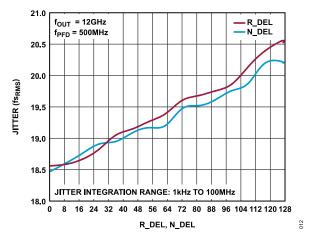

Figure 12. Jitter vs. R\_DEL, N\_DEL

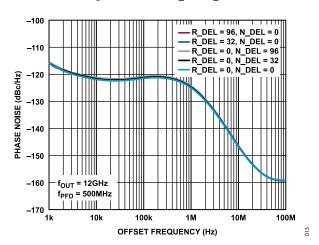

Figure 13. Closed Loop Phase Noise at Various R\_DEL and N\_DEL Settings

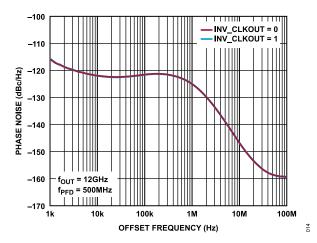

Figure 14. Closed Loop Phase Noise at Various Clock Invert Settings

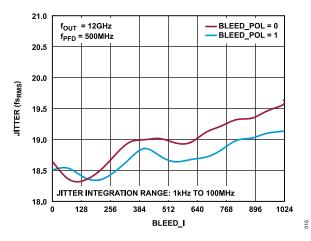

Figure 15. Jitter vs. BLEED\_I

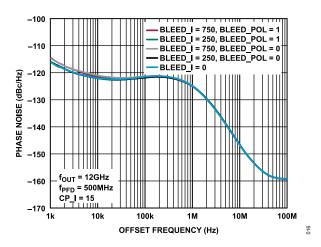

Figure 16. Closed Loop Phase Noise at Various Charge Pump Bleed Delays

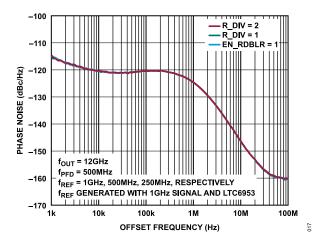

Figure 17. Closed Loop Phase Noise at Various Reference Doubler and Reference Divider Settings

analog.com Rev. 0 | 13 of 79

## TYPICAL PERFORMANCE CHARACTERISTICS

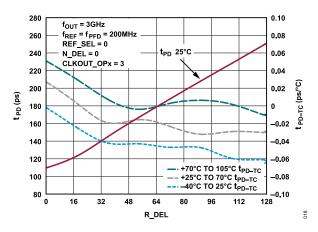

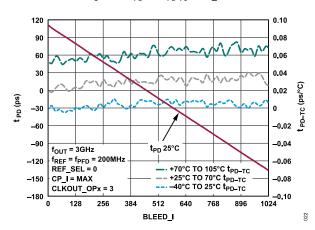

Figure 18. Propagation Delay (t<sub>PD</sub>) and Propagation Delay Temperature Coefficient (t<sub>PD-TC</sub>) vs. R\_DEL

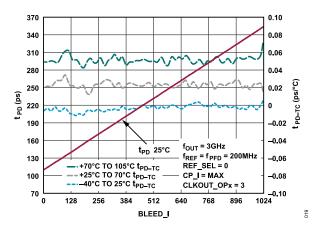

Figure 19.  $t_{PD}$  and  $t_{PD-TC}$  vs. BLEED\_I , BLEED\_POL = 0

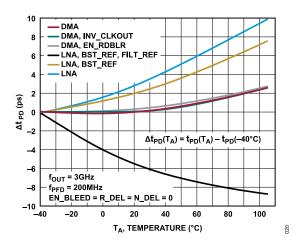

Figure 20. Delta Propagation Delay ( $\Delta t_{PD}$ ) vs.  $T_A$ , Temperature, Device Configuration

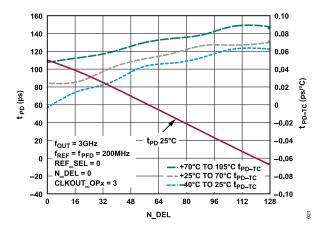

Figure 21. t<sub>PD</sub> and t<sub>PD-TC</sub> vs. N\_DEL

Figure 22.  $t_{PD}$  and  $t_{PD-TC}$  vs. BLEED\_I, BLEED\_POL = 1

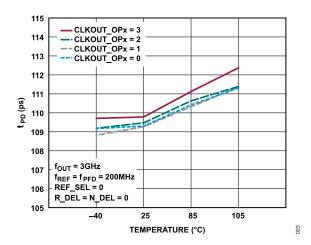

Figure 23. t<sub>PD</sub> vs. Temperature, CLKOUT\_OP Setting

analog.com Rev. 0 | 14 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

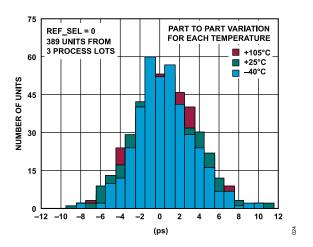

Figure 24. Normalized Propagation Delay (tpD) Histogram

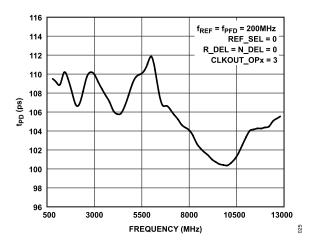

Figure 25. t<sub>PD</sub> vs. Frequency

Figure 26. Open Loop VCO Phase Noise at Various Frequencies

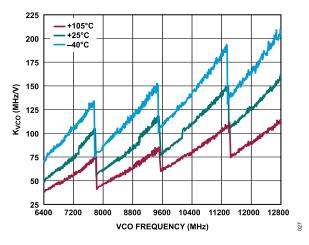

Figure 27. K<sub>VCO</sub> at Various Frequencies and Temperatures

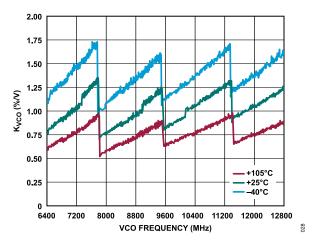

Figure 28. K<sub>VCO</sub> Percentage at Various Frequencies and Temperatures

Figure 29. Open Loop VCO Phase Noise at Various Temperatures

analog.com Rev. 0 | 15 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

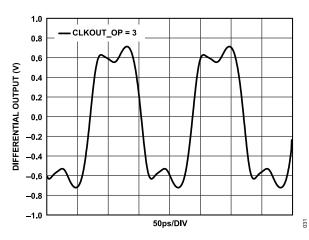

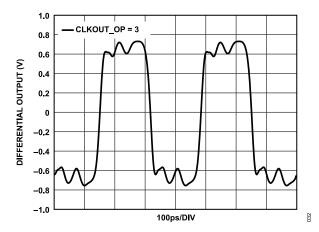

Figure 30. Differential Output at 12 GHz

Figure 31. Differential Output at 6 GHz

Figure 32. Differential Output at 3 GHz

Figure 33. Differential Output at 1.5 GHz

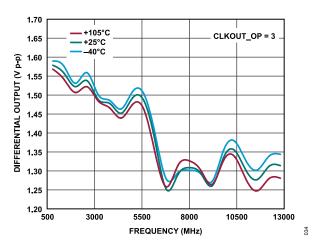

Figure 34. Differential Output vs. Frequency, Temperature

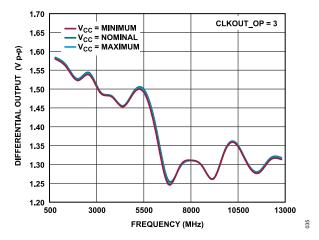

Figure 35. Differential Output vs. Frequency, Power Supply Voltage

analog.com Rev. 0 | 16 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

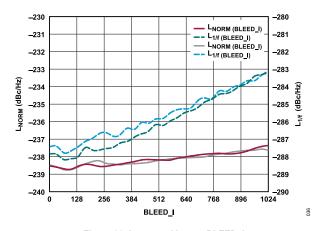

Figure 36. L<sub>NORM</sub> and L<sub>1/f</sub> vs. BLEED\_I

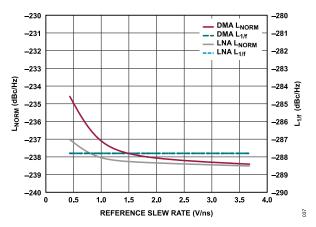

Figure 37. L<sub>NORM</sub> and L<sub>1/f</sub> vs. Reference Slew Rate, Reference Amplifier

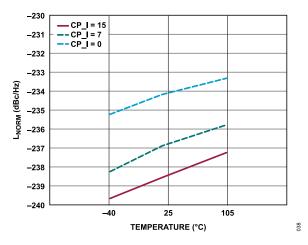

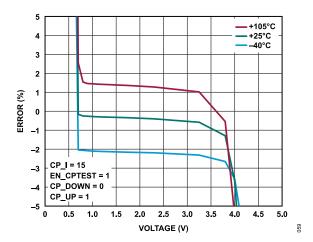

Figure 38. L<sub>NORM</sub> vs. Temperature, Charge Pump Current

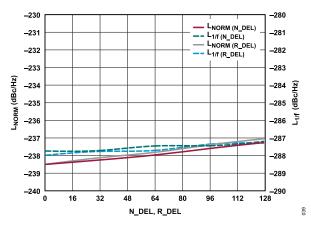

Figure 39. L<sub>NORM</sub> and L<sub>1/f</sub> vs. N\_DEL, R\_DEL

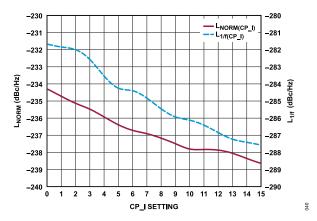

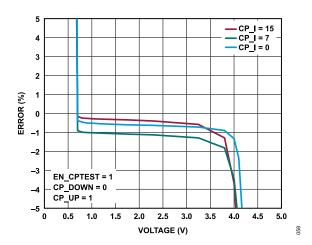

Figure 40.  $L_{NORM}$  and  $L_{1/f}$  vs.  $CP\_I$  Setting

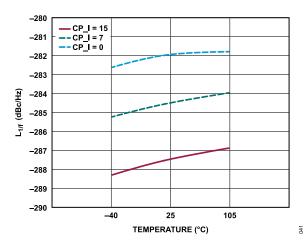

Figure 41. L<sub>1/f</sub> vs. Temperature, Charge Pump Current

analog.com Rev. 0 | 17 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

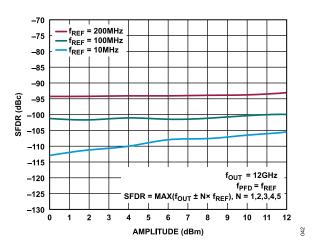

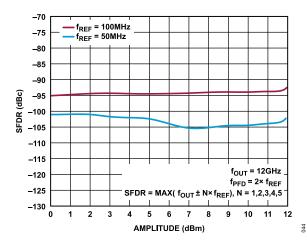

Figure 42. Reference and PFD Spurious Level at Various Reference Frequencies and Reference Amplitudes, EN RDBLR = 0

Figure 43. Reference and PFD Spurious Level at Various Reference Frequencies and Output Frequencies, EN RDBLR = 0

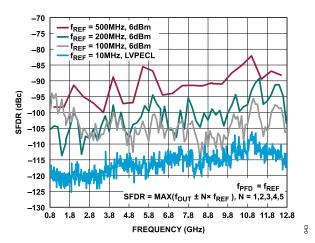

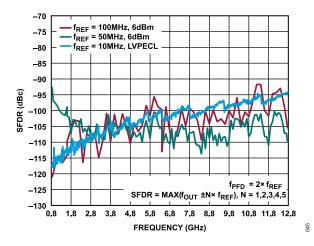

Figure 44. Reference and PFD Spurious Level at Various Reference Frequencies and Reference Amplitudes, EN RDBLR = 1

Figure 45. Reference and PFD Spurious Level at Various Reference Frequencies and Output Frequencies, EN RDBLR = 1

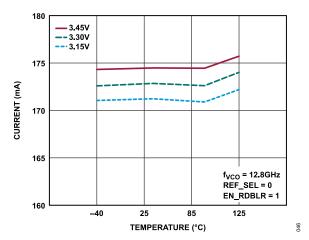

Figure 46. 3.3 V Supply Group 1 Current at Various Junction Temperatures and Power Supply Voltages

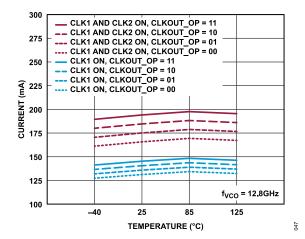

Figure 47. 3.3 V Supply Group 2 Current at Various Junction Temperatures and Output Settings

analog.com Rev. 0 | 18 of 79

# TYPICAL PERFORMANCE CHARACTERISTICS

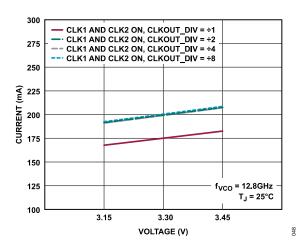

Figure 48. 3.3 V Supply Group 2 Current at Various Power Supply Voltages and CLKOUT DIV Settings

Figure 49. 5 V Supply Current at Various Output Frequencies and Junction Temperatures

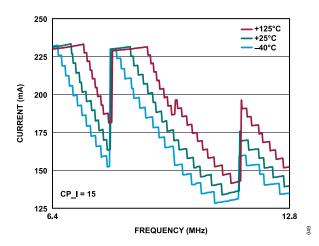

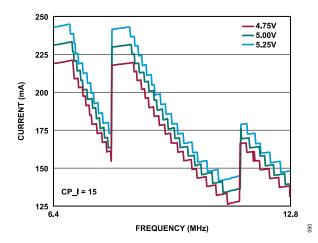

Figure 50. 5 V Supply Current at Various Output Frequencies and Power Supply Voltages

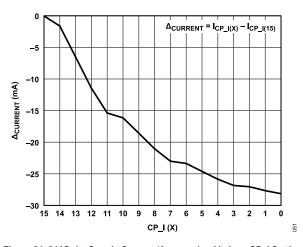

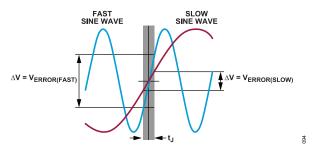

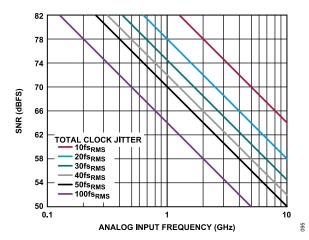

Figure 51. 5 V Delta Supply Current (Δ<sub>CURRENT</sub>) at Various CP\_I Settings