# Dual Channel, 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC

#### **FEATURES**

- ▶ 16-bit resolution

- ▶ 33 MUPS rate in fast mode

- ▶ 22 MUPS rate in precision mode

- ▶ 65 ns small signal settling time to 0.1% accuracy

- ▶ 100 ns large signal settling time to 0.1% accuracy

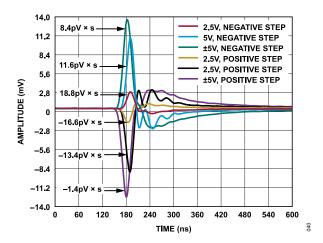

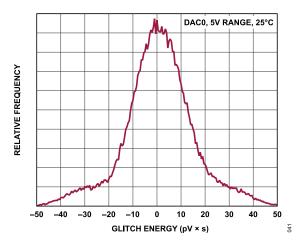

- ▶ Ultra small glitch: < 50 pV×s

- ▶ Ultra low latency: 5 ns

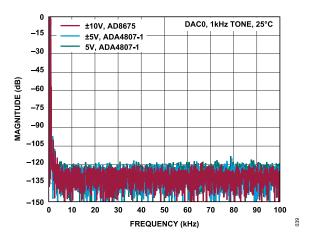

- ▶ THD: -105 dB at 1 kHz

- ▶ Highly configurable output voltage span and offset

- ▶ 1.2 V and 1.8 V logic level compatible

- ▶ Single (classic), dual, and quad SPI modes

- Multiple error detectors, both analog and digital domains

- 2.5 V internal voltage reference, 10 ppm/°C maximum temperature coefficient

- ▶ 5 mm × 5 mm LFCSP

#### **APPLICATIONS**

- Instrumentation

- Hardware in the loop

- Process control equipment

- Medical devices

- Automated test equipment

- Data acquisition system

- Programmable voltage sources

- Optical communications

#### **GENERAL DESCRIPTION**

The AD3552R is a low drift, dual channel, ultra-fast, 16-bit accuracy, current output digital-to-analog converter (DAC) that can be configured in multiple voltage span ranges. The AD3552R operates with a fixed 2.5 V reference.

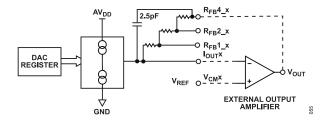

Each DAC incorporates three drift compensating feedback resistors for the required external transimpedance amplifier (TIA) that scales the output voltage. Offset and gain scaling registers allow for generation of multiple output span ranges, such as 0 V to 2.5 V, 0 V to 5 V, 0 V to 10 V, -5 V to +5 V, and -10 V to +10 V, and custom intermediate ranges with full 16-bit resolution.

The DAC can operate in fast mode for maximum speed or precision mode for maximum accuracy.

The serial peripheral interface (SPI) can be configured in quad SPI mode, dual synchronous SPI mode, dual SPI mode, and single SPI (classic SPI) mode with single date rate (SDR) or double data rate (DDR), with logical levels from 1.2 V to 1.8 V.

The AD3552R is specified over the extended industrial temperature range  $(-40^{\circ}\text{C to } + 105^{\circ}\text{C})$ .

Table 1. Related Devices

| Part No.  | Description                                                                   |

|-----------|-------------------------------------------------------------------------------|

| AD8675    | 36 V precision, 2.8 nV/√Hz rail-to-rail output operational amplifier          |

| AD8065    | High performance, 145 MHz <i>Fast</i> FET <sup>™</sup> operational amplifiers |

| ADA4807-1 | 3.1 nV/√Hz, 1 mA, 180 MHz, rail-to-rail input/output amplifier                |

| LTC6655   | 0.25 ppm noise, low drift precision reference                                 |

| ADR4525   | Ultralow noise, high accuracy, 2.5 V voltage reference                        |

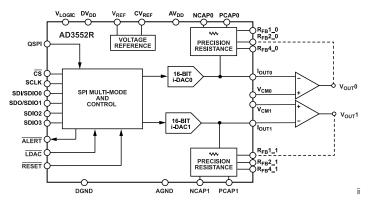

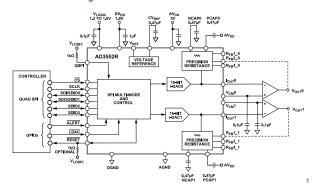

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      | 0: -       4 4                                                                                                                    |                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                    | Serial Interface                                                                                                                  |                                                                                 |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                    | DAC Update Modes                                                                                                                  |                                                                                 |

| Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                    | Power-Down                                                                                                                        | 38                                                                              |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      | Reset                                                                                                                             |                                                                                 |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                    | Error Detection                                                                                                                   | 38                                                                              |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                    | Alert Pin                                                                                                                         | 40                                                                              |

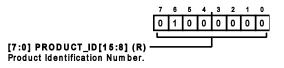

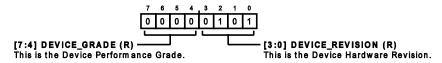

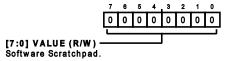

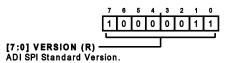

| Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                    | Device ID                                                                                                                         |                                                                                 |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      | Summary of Interface Access Modes                                                                                                 | 40                                                                              |

| Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      | Registers                                                                                                                         |                                                                                 |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      | Register Summary                                                                                                                  |                                                                                 |

| Pin Configuration and Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | Interface Register Details                                                                                                        |                                                                                 |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      | DAC Register Details                                                                                                              |                                                                                 |

| Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      | Applications Information                                                                                                          |                                                                                 |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      | Power Supply Recommendations                                                                                                      |                                                                                 |

| Product Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      | Combining DAC Channels                                                                                                            |                                                                                 |

| DAC Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | Layout Guidelines                                                                                                                 |                                                                                 |

| Predefined Output Voltage Spans                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | Outline Dimensions                                                                                                                |                                                                                 |

| Custom Output Voltage Span                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | Ordering Guide                                                                                                                    |                                                                                 |

| Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      | Evaluation Boards                                                                                                                 |                                                                                 |

| V <sub>RFF</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | Evaluation Boards                                                                                                                 |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | AC to Dual Channel, 16-Bit, 33 MUPS, Multis                                                                                       |                                                                                 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | AC to Dual Channel, 16-Bit, 33 MUPS, Multis<br><br>V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug | <i>'</i>                                                                        |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section                                                                                                                                                                                                                                                                                                       | <sub>C</sub> , VREF to               | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | <br>ghout) ´                                                                    |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section                                                                                                                                                                                                                                                                                                       | <sub>C</sub> , VREF to               | <br>V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                | <br>ghout) ´                                                                    |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a                                                                                                                                                                                                                                                              | <br>C, VREF to<br>and Table 1        | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | jhout) ′                                                                        |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1                                                                                                                                                                                                                                          | C, VREF to                           | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | dhout)                                                                          |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2                                                                                                                                                                                                                       | C, VREF to                           | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)                                                                          |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Change to Table 5                                                                                                                                                                                                     | <sub>C</sub> , VREF to               | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>                                                                      |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Change to Table 5                                                                                                                                                                                                     | <sub>C</sub> , VREF to               | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>                                                                      |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Change to Table 5 Changes to Figure 13 and Table 7                                                                                                                                                                    | <sub>C</sub> , VREF to               | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>                                                                      |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC Changed DVDD to DVDD, IOVDD to VLOGI Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Changes to Table 3 Changes to Table 5 Changes to Figure 13 and Table 7 Change to Figure 32                                                                                                                                                        | <sub>C</sub> , VREF to               | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>                                                                      |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Changes to Table 3 Change to Table 5 Changes to Figure 13 and Table 7 Changes to Figure 32 Changes to Figure 60 and Figure 61 Changes to Figure 62, and Figure 64 to Figure 64                                           | C, VREF to                           | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>2<br>1<br>1<br>1<br>1                                                 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Changes to Table 3 Change to Table 5 Changes to Figure 13 and Table 7 Changes to Figure 32 Changes to Figure 60 and Figure 61 Changes to Figure 62, and Figure 64 to Figure 64                                           | C, VREF to                           | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | ghout)<br>2<br>1<br>1<br>1<br>1                                                 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Changes to Table 3 Change to Table 5 Changes to Figure 13 and Table 7 Changes to Figure 32 Changes to Figure 60 and Figure 61 Changes to Figure 62, and Figure 64 to Figure 67; Renumbered Sequential Added Figure 68 | gure 66                              | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | nhout)                                                                          |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC Changed DVDD to DV <sub>DD</sub> , IOVDD to V <sub>LOGI</sub> Changes to Features Section Changes to General Description Section a Changes to Figure 1 Changes to Table 2 Changes to Table 3 Change to Table 5 Changes to Figure 13 and Table 7 Changes to Figure 32 Changes to Figure 60 and Figure 61 Changes to Figure 62, and Figure 64 to Figure 67; Renumbered Sequential Added Figure 68 | gure 66                              | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | nhout)                                                                          |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66                              | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Throug                                                    | 22<br>22<br>22                                                                  |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66 Nonlinearity Section         | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22<br>22<br>22<br>22<br>24<br>24<br>24<br>25                                    |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Mu Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                 | gure 66 Nonlinearity Section         | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22<br>22<br>22<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>2 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66 Nonlinearity Section Section | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22<br>22<br>22<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>2 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66 Nonlinearity Section Section | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22                                                                              |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66 Nonlinearity Section Section | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>2 |

| 2/2023—Rev. A to Rev. B Changed 16-Bit, 33 MUPS, Multispan, Multi-IO SPI DAC                                                                                                                                                                                                                                                                                                                                                                                                    | gure 66                              | V <sub>REF</sub> , AVDD to AV <sub>DD</sub> , VDD to AVD <sub>DD</sub> (Through                                                   | 22 24 24 24 24 24 24 24 24 24 24 24 24 2                                        |

**Data Sheet**

## **TABLE OF CONTENTS**

| Changes to Product Description Section                          | 26 |

|-----------------------------------------------------------------|----|

| Changes to DAC Architecture Section and Figure 69               | 26 |

| Changes to Predefined Output Voltage Spans and Table 8          |    |

| Changes to Custom Output Voltage Span Section                   |    |

| Added Table 9 and Table 10; Renumbered Sequentially             |    |

| Changes to Transfer Function Section                            |    |

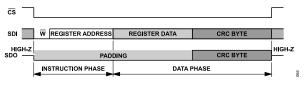

| Change to SPI Frame Synchronization Section                     |    |

| Change to Multibyte Registers Section                           |    |

| Changes to Address Direction Section                            |    |

| Change to Figure 74                                             |    |

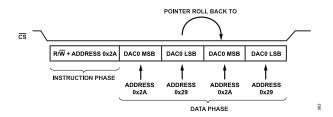

| Changes to Streaming Mode Section                               |    |

| Changes to Figure 76 Caption and Figure 77                      |    |

| Change to Figure 89                                             |    |

| Changes to SDIO Drive Strength Section and Figure 90            |    |

| Changes to DAC Update Modes Section and Figure 91               |    |

| Changes to Table 15                                             |    |

| Changes to Power-Down Section                                   |    |

| Changes to Reset Pin Section                                    |    |

| Changes to SPI Mode Error Section                               |    |

| Changes to SPI Clock Counter Section                            | 39 |

| Changes to Table 19                                             |    |

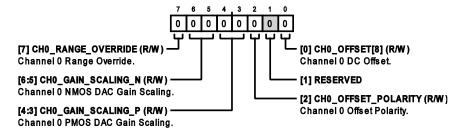

| Changes to Channel 0 Gain Register Figure and Table 42          |    |

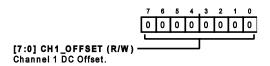

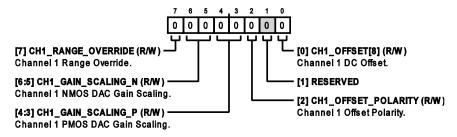

| Changes to Channel 1 Gain Register Figure and Table 43          | 59 |

| Changes to Power Supply Recommendations Section and Figure 9494 |    |

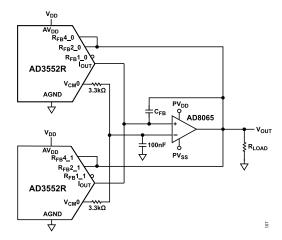

| Changes to Combining DAC Channels Section and Figure 95         |    |

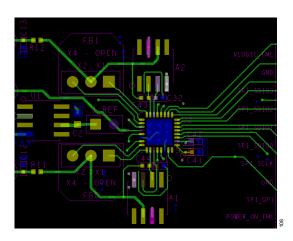

| Changes to Layout Guidelines Section                            |    |

| Updated Outline Dimensions                                      |    |

| 0/0000 B 0 / B 4                                                |    |

| 2/2022—Rev. 0 to Rev. A                                         | 40 |

| Changes to Figure 13 and Table 7<br>Changes to Figure 92        |    |

| UIIAIIYES IU FIYUIE 72                                          | 00 |

1/2022—Revision 0: Initial Version

## **SPECIFICATIONS**

# **ELECTRICAL CHARACTERISTICS**

$AV_{DD}$  = 5.0 V ± 5%,  $DV_{DD}$  = 1.8 V ± 5%, 1.1 V ≤  $V_{LOGIC}$  ≤ 1.9 V,  $V_{REF}$  = 2.5 V,  $-40^{\circ}C$  ≤  $T_{A}$  ≤ +105°C, output amplifier AD8675, unless otherwise noted.

Table 2.

| Parameter <sup>1</sup>                 | Symbol             | Min                | Тур  | Max                | Unit               | Test Conditions/Comments                                   |

|----------------------------------------|--------------------|--------------------|------|--------------------|--------------------|------------------------------------------------------------|

| STATIC PERFORMANCE                     |                    |                    | _    |                    |                    |                                                            |

| Resolution                             |                    | 16                 |      |                    | Bits               |                                                            |

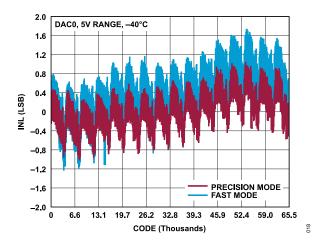

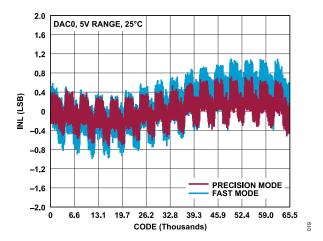

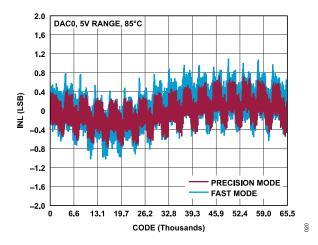

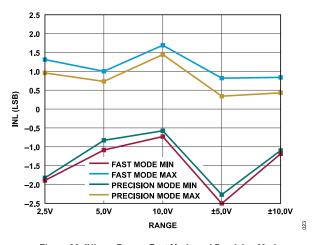

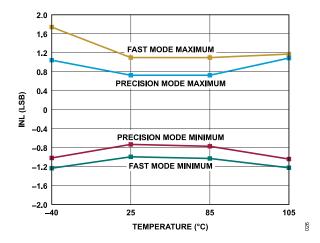

| Relative Accuracy (INL)                |                    | -2                 |      | +2                 | LSB                | 5 V range only                                             |

|                                        |                    | -4                 |      | +4                 | LSB                | All other ranges <sup>2</sup>                              |

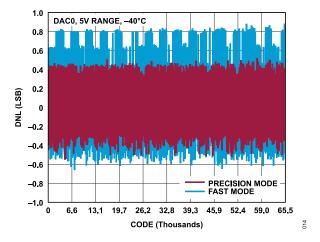

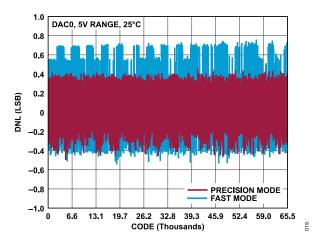

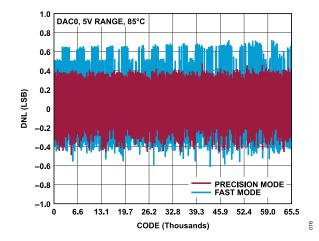

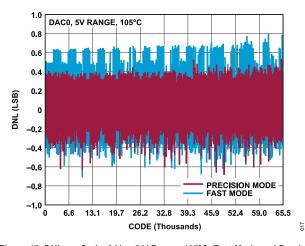

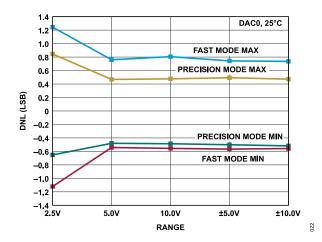

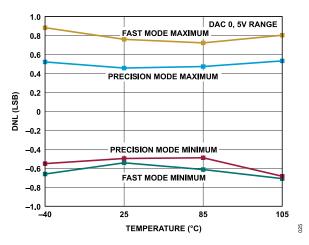

| Differential Nonlinearity (DNL)        |                    | -1                 |      | +1                 | LSB                | Precision mode: -40°C to +105°C,<br>fast mode: 0°C to 85°C |

|                                        |                    | -2                 |      | +2                 | LSB                | Fast mode: -40°C to +105°C                                 |

|                                        |                    | -2                 |      | +2                 | LSB                | 0 V to 2.5 V range, fast or precision modes <sup>2</sup>   |

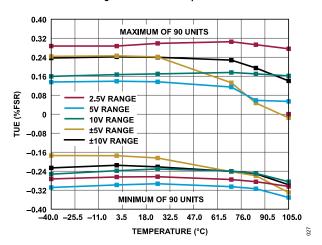

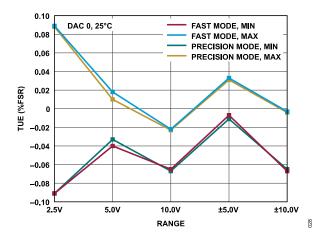

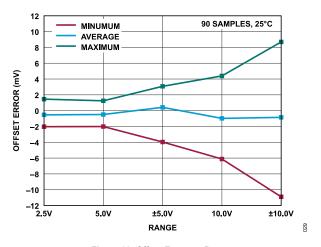

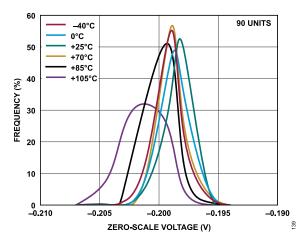

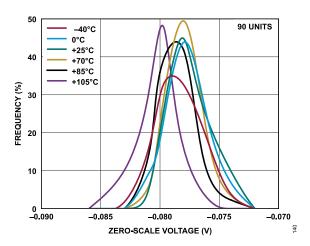

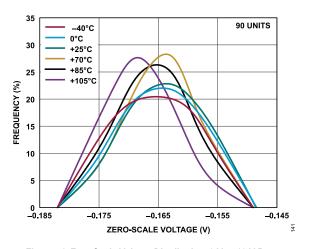

| Offset Error                           |                    |                    | 0.03 |                    | %FSR               | Midscale, 25°C                                             |

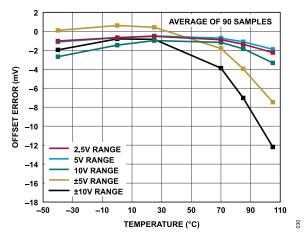

| Offset Error Drift <sup>2</sup>        |                    |                    | 2    | 8                  | ppm FSR/°C         | 0 V to 5 V and 0 V to 10 V ranges                          |

|                                        |                    |                    | 4    | 16                 | ppm FSR/°C         | All other ranges                                           |

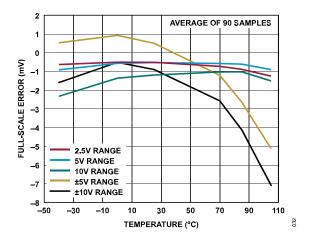

| Full-Scale Error                       |                    |                    | 0.04 |                    | %FSR               | 25°C                                                       |

| Full-Scale Error Drift <sup>2</sup>    |                    |                    | 1    | 5                  | ppm FSR/°C         | 0 V to 5 V and 0 V to 10 V ranges                          |

|                                        |                    |                    | 4    | 12                 | ppm FSR/°C         | All other ranges                                           |

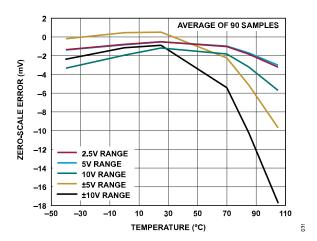

| Zero-Scale Error <sup>3</sup>          |                    |                    | 0.05 |                    | %FSR               | 25°C                                                       |

| Zero-Scale Error Drift <sup>2</sup>    |                    |                    | 3.5  | 8                  | ppm FSR/°C         | 0 V to 5 V and 0 V to 10 V ranges                          |

|                                        |                    |                    | 7    | 16                 | ppm FSR/°C         | All other ranges                                           |

| Total Unadjusted Error (TUE)           |                    | -0.5               |      | +0.5               | %FSR               | j ,                                                        |

| DC Power Supply Rejection Ratio (PSRR) |                    |                    | 0.6  |                    | mV/V               | DAC code = midscale                                        |

| DC Crosstalk                           |                    |                    | 3    |                    | μV/V               | Full-scale step                                            |

| DUTPUT CHARACTERISTICS                 |                    |                    |      |                    |                    | '                                                          |

| Output Current                         | I <sub>OUT</sub> x |                    | 1.6  |                    | mA                 | Absolute value                                             |

| REFERENCE OUTPUT                       | 100111             |                    |      |                    |                    |                                                            |

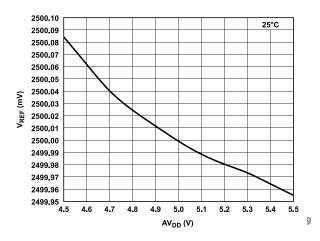

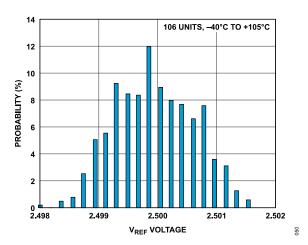

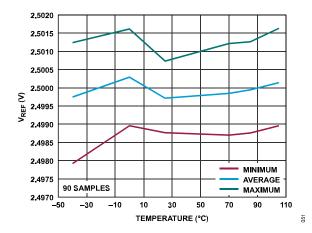

| Output Voltage                         |                    | 2.492              | 2.5  | 2.508              | V                  | At 25°C, over lifetime                                     |

| Voltage Reference Temperature          |                    |                    | 3    | 10                 | ppm/°C             | ,                                                          |

| Coefficient (TC) <sup>4</sup>          |                    |                    | Ū    |                    | PP, 0              |                                                            |

| Output Impedance                       |                    |                    | 50   |                    | mΩ                 |                                                            |

| Output Voltage Noise                   |                    |                    | 2.7  |                    | μV rms             | 0.1 Hz to 10 Hz                                            |

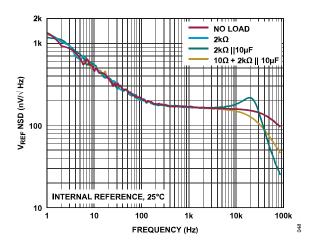

| Output Voltage Noise Density           |                    |                    | 173  |                    | nV/√ <del>Hz</del> | f = 1 kHz, no load on V <sub>REF</sub>                     |

|                                        |                    |                    | 164  |                    | nV/√ <del>Hz</del> | f = 10 kHz, no load on V <sub>RFF</sub>                    |

| Capacitive Load Stability <sup>2</sup> |                    |                    |      | 10                 | μF                 | , KEI                                                      |

| Load Regulation                        |                    |                    | 50   |                    | μV/mA              | At 25°C                                                    |

| Output Current Load Capability         |                    |                    | ±8   |                    | mA                 |                                                            |

| Line Regulation                        |                    |                    | 135  |                    | μV/V               | At 25°C                                                    |

| REFERENCE INPUT                        |                    |                    |      |                    | 1 :                | -                                                          |

| Reference Current                      |                    |                    | 1    |                    | μA                 |                                                            |

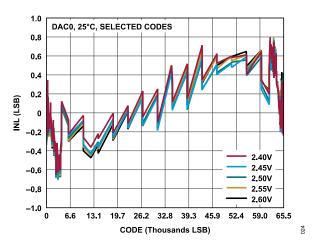

| Reference Input Range <sup>2</sup>     | V <sub>REF</sub>   | 2.4                | 2.5  | 2.6                | Λ,                 |                                                            |

| Reference Input Impedance              | NEF                |                    | 3    | =-*                | MΩ                 |                                                            |

| OGIC INPUTS                            |                    |                    |      |                    |                    |                                                            |

| Input Current                          | l <sub>l</sub>     | -1                 |      | +1                 | μA                 | Per pin                                                    |

| Input Low Voltage                      | V <sub>IL</sub>    | '                  |      | 0.35 ×             | V                  |                                                            |

| inpat Low Voltage                      | ↑IL                |                    |      | V <sub>LOGIC</sub> |                    |                                                            |

| Input High Voltage                     | V <sub>IH</sub>    | 0.65 ×             |      | 20010              | V                  |                                                            |

| . 5 5                                  | ""                 | V <sub>LOGIC</sub> |      |                    |                    |                                                            |

analog.com Rev. B | 4 of 70

## **SPECIFICATIONS**

Table 2. (Continued)

| Parameter <sup>1</sup>              | Symbol                     | Min                       | Тур | Max                          | Unit | Test Conditions/Comments                                                                         |

|-------------------------------------|----------------------------|---------------------------|-----|------------------------------|------|--------------------------------------------------------------------------------------------------|

| Pin Capacitance                     | C <sub>I</sub>             |                           | 4   |                              | pF   |                                                                                                  |

| LOGIC OUTPUTS                       |                            |                           |     |                              |      |                                                                                                  |

| Output Low Voltage                  | V <sub>OL</sub>            |                           |     | 0.20 ×<br>V <sub>LOGIC</sub> | V    | I <sub>SINK</sub> = 100 μA                                                                       |

| Output High Voltage                 | V <sub>OH</sub>            | 0.80 × V <sub>LOGIC</sub> |     |                              | V    | I <sub>SOURCE</sub> = 100 μA                                                                     |

| Pin Capacitance                     | Co                         |                           | 4   |                              | pF   |                                                                                                  |

| POWER REQUIREMENTS                  |                            |                           |     |                              |      |                                                                                                  |

| V <sub>LOGIC</sub> Pin              |                            | 1.1                       | 1.8 | 1.89                         | V    |                                                                                                  |

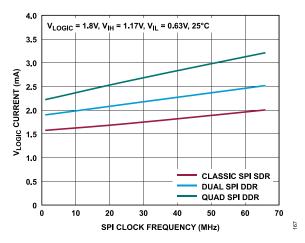

| V <sub>LOGIC</sub> Current          | I <sub>LOGIC</sub>         |                           | 1   | 7.5                          | μA   | $V_{IH} = V_{LOGIC} \times 0.9$ , $V_{IL} = V_{LOGIC} \times 0.1$                                |

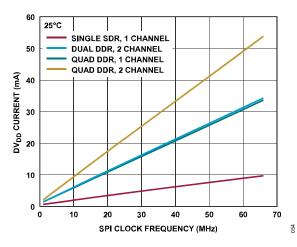

| V <sub>LOGIC</sub> Dynamic Current  | I <sub>LOGIC_DYNAMIC</sub> |                           | 3   | 5                            | mA   | SCLK = 66 MHz, quad SPI DDR, $V_{IH} = V_{LOGIC} \times 0.65$ , $V_{IL} = V_{LOGIC} \times 0.35$ |

| DV <sub>DD</sub> Pin                |                            | 1.71                      | 1.8 | 1.89                         | V    |                                                                                                  |

| DV <sub>DD</sub> Current            | I <sub>DVDD</sub>          |                           | 0.5 | 0.8                          | mA   |                                                                                                  |

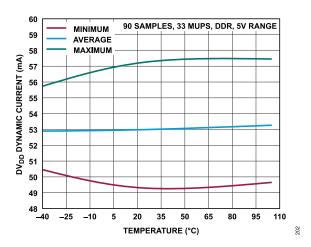

| DV <sub>DD</sub> Dynamic Current    | I <sub>DVDD_DYNAMIC</sub>  |                           | 53  | 60                           | mA   | SCLK = 66 MHz, quad SPI DDR, simultaneous update                                                 |

| AV <sub>DD</sub> Pin                |                            | 4.75                      | 5   | 5.25                         | V    |                                                                                                  |

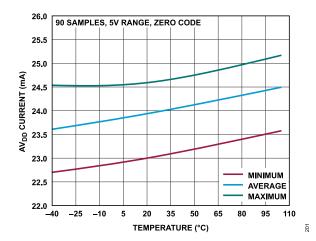

| AV <sub>DD</sub> Current            | I <sub>DD</sub>            |                           | 22  | 28.5                         | mA   | Channel 0 and Channel 1 zero-scale, 0 V to ±5 V range                                            |

| AV <sub>DD</sub> Power-Down Current | I <sub>DD</sub>            |                           | 0.6 |                              | mA   | After reset, DACs powered down                                                                   |

| AV <sub>DD</sub> Reset Current      | I <sub>DD</sub>            |                           | 120 |                              | μA   | RESET asserted                                                                                   |

<sup>&</sup>lt;sup>1</sup> See the Terminology section.

## **AC CHARACTERISTICS**

$AV_{DD}$  = 5.0 V ± 5%,  $DV_{DD}$  = 1.8 V ± 5%, 1.1 V ≤  $V_{LOGIC}$  ≤ 1.9 V,  $-40^{\circ}C$  ≤  $T_{A}$  ≤ +105°C, measured with the ADA4807-1 external amplifier, unless otherwise noted.

Table 3.

| Parameter <sup>1</sup>           | Min | Тур | Max | Unit   | Test Conditions/Comments                                                                                |

|----------------------------------|-----|-----|-----|--------|---------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE              |     |     |     |        |                                                                                                         |

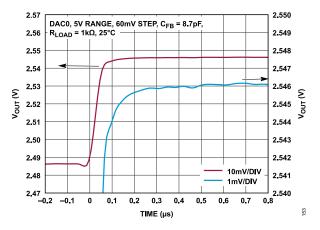

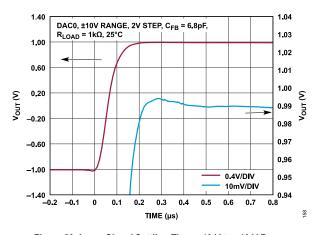

| Output Voltage Settling Time     |     | 100 |     | ns     | 2 V step, 0.1% error, 0 V to 5 V range                                                                  |

|                                  |     | 75  |     | ns     | 2 V step, 1% error, 0 V to 5 V range                                                                    |

|                                  |     | 65  |     | ns     | 60 mV step, 0.1% error, 0 V to 5 V range                                                                |

|                                  |     | 15  |     | ns     | 60 mV step, 1% error, 0 V to 5 V range                                                                  |

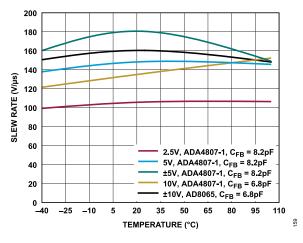

| Slew Rate                        |     | 100 |     | V/µs   | Full-scale step, 0 V to 2.5 V range                                                                     |

| Digital-to-Analog Glitch Impulse |     | 50  |     | pV×s   | 0 V to 5 V range, ±1 LSB change around major carry                                                      |

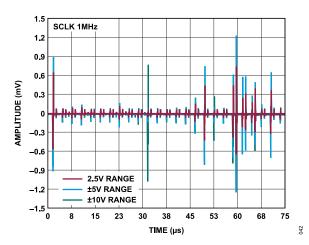

| Digital Feedthrough              |     | 25  |     | pV×s   | 50 MHz clock, R <sub>FB</sub> 2_x                                                                       |

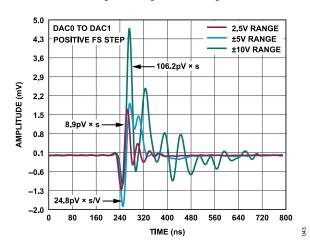

| DAC to DAC Crosstalk             |     | 6.5 |     | pV×s/V | Full-scale step, R <sub>FB</sub> 2_x                                                                    |

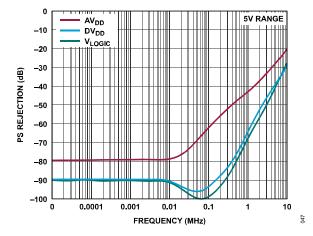

| AC PSRR                          |     | 80  |     | dB     | 1 kHz, R <sub>FB</sub> 1_x                                                                              |

|                                  |     | 43  |     | dB     | 1 MHz, R <sub>FB</sub> 1_x                                                                              |

| Output Noise Spectral Density    |     | 15  |     | nV/√Hz | DAC code = midscale, external reference, 10 kHz, NCAPx = 1.2 $\mu$ F, PCAPx = none, R <sub>FB</sub> 1_x |

|                                  |     | 30  |     | nV/√Hz | R <sub>FB</sub> 2_x                                                                                     |

|                                  |     | 60  |     | nV/√Hz | R <sub>FB</sub> 4_x                                                                                     |

analog.com Rev. B | 5 of 70

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Measured at zero code.

<sup>&</sup>lt;sup>4</sup> Reference temperature coefficient is calculated as per the box method.

#### **SPECIFICATIONS**

Table 3. (Continued)

| Parameter <sup>1</sup>             | Min | Тур  | Max | Unit          | Test Conditions/Comments                                                                                |

|------------------------------------|-----|------|-----|---------------|---------------------------------------------------------------------------------------------------------|

| Output Noise                       |     | 3.8  |     | $\mu V_{RMS}$ | DAC code = midscale, external reference, 1 Hz to 10 kHz, NCAPx = $1.2 \mu$ F, PCAPx = none, $R_{FB}1_x$ |

|                                    |     | 7.6  |     | $\mu V_{RMS}$ | R <sub>FB</sub> 2_x                                                                                     |

|                                    |     | 15.4 |     | $\mu V_{RMS}$ | R <sub>FB</sub> 4_x                                                                                     |

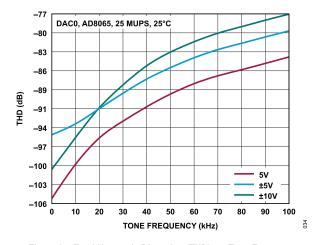

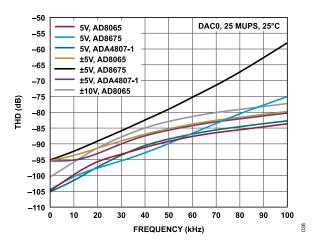

| Total Harmonic Distortion (THD)    |     | -105 |     | dB            | 0 V to 5 V range, f <sub>OUT</sub> = 1 kHz                                                              |

|                                    |     | -101 |     | dB            | f <sub>OUT</sub> = 10 kHz                                                                               |

|                                    |     | -84  |     | dB            | f <sub>OUT</sub> = 100 kHz                                                                              |

| Spurious-Free Dynamic Range (SFDR) |     | -105 |     | dB            | 0 V to 5 V range, f <sub>OUT</sub> = 1 kHz                                                              |

<sup>&</sup>lt;sup>1</sup> See the Terminology section.

## **TIMING CHARACTERISTICS**

$AV_{DD} = 5.0 \text{ V} \pm 5\%$ ,  $DV_{DD} = 1.8 \text{ V} \pm 5\%$ ,  $1.1 \text{ V} \le V_{LOGIC} \le 1.9 \text{ V}$ ,  $-40^{\circ}C \le T_{A} \le +105^{\circ}C$ , unless otherwise noted.

Table 4.

| Parameter <sup>1, 2</sup>    | Description                                                         | Min  | Тур  | Max | Unit              | Test Conditions /<br>Comments                      |

|------------------------------|---------------------------------------------------------------------|------|------|-----|-------------------|----------------------------------------------------|

|                              | SCLK frequency                                                      |      | 1717 | 66  | MHz               | Comments                                           |

| f <sub>SCLK</sub>            | SCLK cycle time                                                     | 15.2 |      | 00  | ns                |                                                    |

| t <sub>1</sub>               | SCLK dydle tilrie SCLK half period                                  | 7.6  |      |     |                   |                                                    |

| t <sub>SCLK/2</sub>          | ·                                                                   | 5    |      |     | ns                |                                                    |

| t <sub>2</sub>               | CS falling edge to first SCLK rising edge                           | -    |      |     | ns                |                                                    |

| t <sub>3</sub>               | Last SCLK sampling edge <sup>3</sup> to $\overline{CS}$ rising edge | 10   |      |     | ns                |                                                    |

| t <sub>4</sub>               | CS falling edge from SCLK sampling edge ignored                     | 5    |      |     | ns                |                                                    |

| t <sub>5</sub>               | CS rising edge to SCLK rising edge ignored                          | 5    |      |     | ns                |                                                    |

| $t_6$                        | Minimum CS high time                                                | 10   |      |     | ns                |                                                    |

| t <sub>7</sub>               | Data setup time                                                     | 2    |      |     | ns                |                                                    |

| $t_8$                        | Data hold time                                                      | 2    |      |     | ns                |                                                    |

| t <sub>9</sub>               | SCLK falling edge to SDO data valid                                 |      |      | 15  | ns                | 1.7 < V <sub>LOGIC</sub> < 1.9                     |

|                              |                                                                     |      |      | 25  | ns                | 1.1 < V <sub>LOGIC</sub> < 1.7                     |

| t <sub>10</sub>              | SCLK sampling edge to LDAC falling edge                             | 7.6  |      |     | ns                |                                                    |

| t <sub>11</sub>              | LDAC pulse width low                                                | 7.6  |      |     | ns                |                                                    |

| t <sub>12</sub>              | CS rising edge to SDO disabled                                      |      | 50   |     | ns                |                                                    |

| t <sub>13</sub>              | LDAC rising edge to CS falling edge                                 | 5    |      |     | ns                |                                                    |

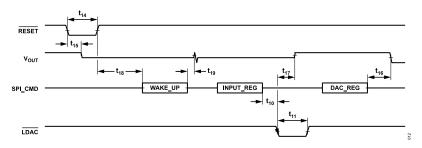

| t <sub>14</sub>              | RESET pulse width low                                               | 10   |      |     | ns                | t <sub>14</sub> to t <sub>19</sub> shown in Figure |

| t <sub>15</sub>              | RESET pulse activation time                                         |      |      | 100 | ns                |                                                    |

| t <sub>16</sub>              | V <sub>OUT</sub> Update from CHx_DAC Register Write                 |      | 12.6 |     | ns                |                                                    |

| t <sub>17</sub>              | V <sub>OUT</sub> update from <del>LDAC</del> falling edge           |      | 5    |     | ns                |                                                    |

| t <sub>18</sub> <sup>4</sup> | Wait time before DAC register access                                | 100  |      |     | ms                |                                                    |

| t <sub>19</sub> <sup>5</sup> | Shutdown exit time                                                  |      | 5    |     | ms                |                                                    |

| Update Rate                  | Quad SPI mode, DDR and streaming enabled, precision mode            |      |      | 22  | MUPS <sup>6</sup> |                                                    |

|                              | Quad SPI mode, DDR and streaming enabled, fast mode                 |      |      | 33  | MUPS <sup>6</sup> |                                                    |

<sup>&</sup>lt;sup>1</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90%) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

analog.com Rev. B | 6 of 70

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> The SCLK sampling edge refers to the SCLK edge where the data is read in (sampled)

$<sup>^4</sup>$  Same timing must be expected at power-up from the instant that AV<sub>DD</sub> = 4 V or DV<sub>DD</sub> = 0.8 V.

## **SPECIFICATIONS**

- <sup>5</sup> Time required to exit power-down to normal mode.

- <sup>6</sup> MUPS is mega updates per second.

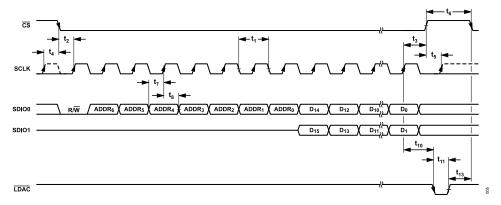

# **Timing Diagrams**

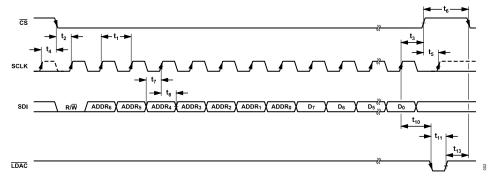

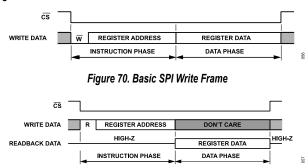

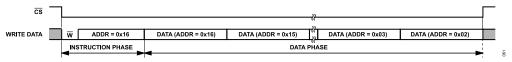

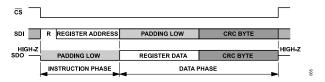

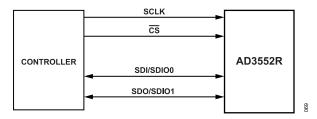

Figure 2. Classic SPI Write Operation with Single Data Rate

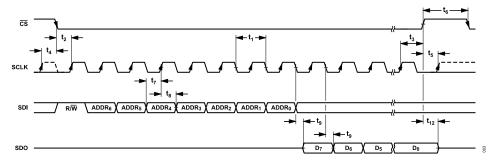

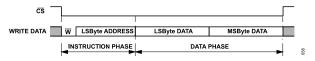

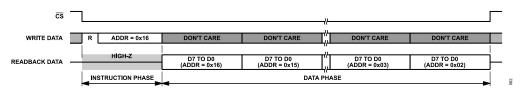

Figure 3. Classic SPI Read Operation with Single Data Rate

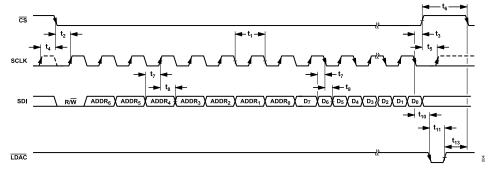

Figure 4. Classic SPI Write Operation with Double Data Rate

analog.com Rev. B | 7 of 70

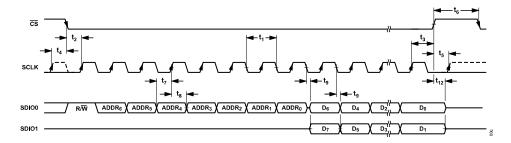

## **SPECIFICATIONS**

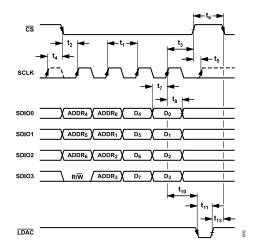

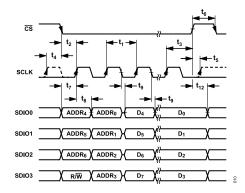

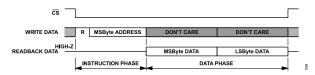

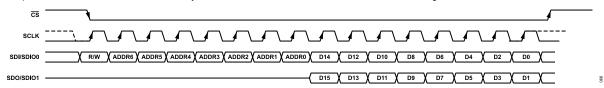

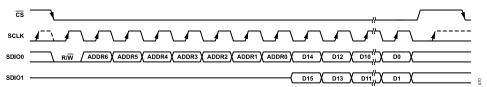

Figure 5. Dual SPI Write Operation with Single Data Rate

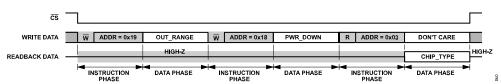

Figure 6. Dual SPI Read Operation with Single Data Rate

Figure 7. Dual SPI Write Operation with Double Data Rate

analog.com Rev. B | 8 of 70

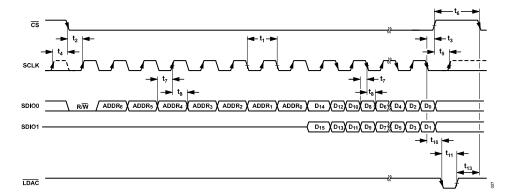

## **SPECIFICATIONS**

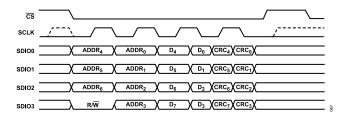

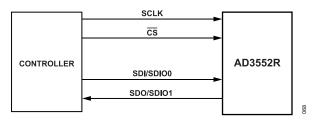

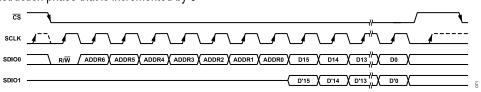

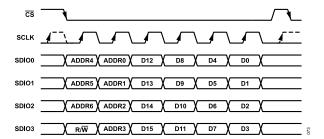

Figure 8. Dual Synchronous SPI Write Operation with Single Data Rate

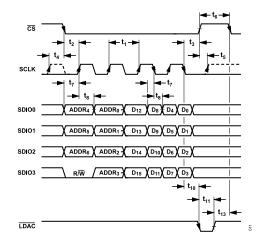

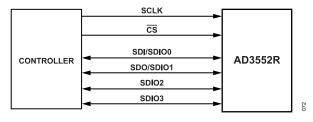

Figure 9. Quad SPI Write Operation with Single Data Rate

Figure 10. Quad SPI Read Operation with Single Data Rate

analog.com Rev. B | 9 of 70

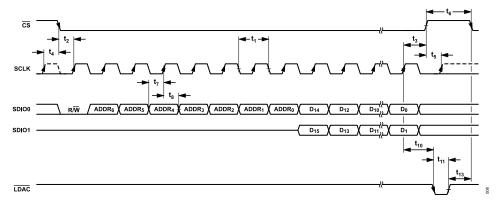

## **SPECIFICATIONS**

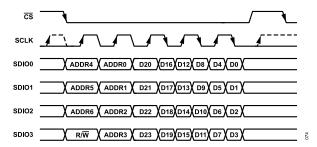

Figure 11. Quad SPI Write Operation with Double Data Rate

Figure 12. Start-Up Sequence Timing

analog.com Rev. B | 10 of 70

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| Parameter                                      | Rating                                                                |  |  |

|------------------------------------------------|-----------------------------------------------------------------------|--|--|

| AV <sub>DD</sub> to AGND                       | -0.3 V to +6 V                                                        |  |  |

| DV <sub>DD</sub> to DGND                       | -0.3 V to +2.1 V                                                      |  |  |

| AGND to DGND                                   | -0.3 V to +0.3 V                                                      |  |  |

| V <sub>LOGIC</sub> to DGND                     | -0.3 V to DV <sub>DD</sub> + 0.3 V or                                 |  |  |

|                                                | +2.1 V (whichever is less)                                            |  |  |

| V <sub>REF</sub> to AGND                       | -0.3 V to +3 V                                                        |  |  |

| R <sub>FB</sub> x_y to AGND                    | -18 V to +18 V                                                        |  |  |

| Digital Input Voltage to DGND                  | -0.3 V to V <sub>LOGIC</sub> + 0.3 V or +2.1 V<br>(whichever is less) |  |  |

| Operating Temperature Range                    |                                                                       |  |  |

| Industrial                                     | -40°C to +105°C                                                       |  |  |

| Storage Temperature Range                      | -65°C to +150°C                                                       |  |  |

| Maximum Junction Temperature (T <sub>J</sub> ) | 125°C                                                                 |  |  |

| Power Dissipation                              | (Maximum T <sub>J</sub> - T <sub>A</sub> )/θ <sub>JA</sub>            |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operation environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance.

$\theta_{JC}$  is the junction to case thermal resistance. Both  $\theta_{JA}$  and  $\theta_{JC}$  are defined by the JEDEC JESD51 standard, and their values are dependent on the test board and test environment.

Table 6. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------------------|---------------|---------------|------|

| CP-32-30                  | 43.5          | 23.6          | °C/W |

Simulation values on JEDEC 2S2P board with 9 thermal vias, still air (0 m/sec airflow).

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 11 of 70

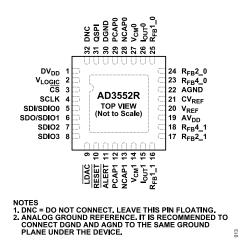

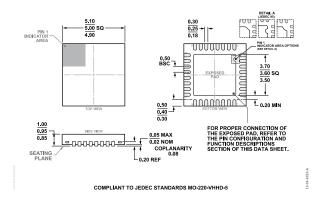

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 13. Pin Configuration

Table 7. Pin Function Descriptions

| Pin No. | Mnemonic             | Type | Description                                                                                                                                                                                                                                                                                                           |

|---------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DV <sub>DD</sub>     | S    | Digital Core Power Supply. 1.8 V ± 5%.                                                                                                                                                                                                                                                                                |

| 2       | $V_{LOGIC}$          | S    | Digital Interface Power Supply. 1.2 V to 1.8 V.                                                                                                                                                                                                                                                                       |

| 3       | CS                   | DI   | Chip Select, Active Low Logic Input. This is the frame synchronization signal for the input data.                                                                                                                                                                                                                     |

| 4       | SCLK                 | DI   | Serial Clock Input.                                                                                                                                                                                                                                                                                                   |

| 5       | SDI/SDIO0            | DI/O | Serial Data Input in Classic SPI Mode.                                                                                                                                                                                                                                                                                |

|         |                      |      | Serial Bidirectional Input/Output Bit 0 in Dual or Quad SPI Modes.                                                                                                                                                                                                                                                    |

| 6       | SDO/SDIO1            | DI/O | Serial Data Output in Classic SPI Mode.                                                                                                                                                                                                                                                                               |

|         |                      |      | Serial Bidirectional Input/Output Bit 1 in Dual or Quad SPI Modes.                                                                                                                                                                                                                                                    |

| 7       | SDIO2                | DI/O | Serial Bidirectional Input/Output Bit 2 in Quad SPI Mode. Pull down if not used.                                                                                                                                                                                                                                      |

| 8       | SDIO3                | DI/O | Serial Bidirectional Input/Output Bit 3 in Quad SPI Mode. Pull down if not used.                                                                                                                                                                                                                                      |

| 9       | LDAC                 | DI   | Load DAC, Active Low Logic Input. LDAC can be operated in synchronous mode or asynchronous mode. Pulsing this pin low causes the DAC register to be updated if the input register has new data. If this pin is tied permanently low, the DAC is automatically updated when new data is written to the input register. |

| 10      | RESET                | DI   | Asynchronous Reset Input. Active low logic input. When RESET is low, all registers are reset to their default values and the activity on the digital interface is ignored. The AD3552R incorporates a power-on reset (POR) circuit. If this pin is not used it must be tied to                                        |

| 11      | ALERT                | DO   | V <sub>LOGIC</sub> .  Alert Pin. Active low logic output. This pin is driven low if an alert condition is detected and it is not masked by the corresponding bit in the mask register. This pin has an internal configurable pull-up resistor.                                                                        |

| 12      | PCAP1                | AI/O | Noise Reduction Capacitor for DAC1, Optional. Capacitor connected to AV <sub>DD</sub> .                                                                                                                                                                                                                               |

| 13      | NCAP1                | AI/O | Noise Reduction Capacitor for DAC1, Optional. Capacitor connected to GND.                                                                                                                                                                                                                                             |

| 14      | V <sub>CM</sub> 1    | AO   | Common Mode Voltage for DAC1. Analog input/output.                                                                                                                                                                                                                                                                    |

| 15      | I <sub>OUT</sub> 1   | AI/O | DAC1 Output Current.                                                                                                                                                                                                                                                                                                  |

| 16      | R <sub>FB</sub> 1_1  | AI/O | Hardware Gain Selection for DAC1, Gain = 1.                                                                                                                                                                                                                                                                           |

| 17      | R <sub>FB</sub> 2 _1 | AI/O | Hardware Gain Selection for DAC1, Gain = 2.                                                                                                                                                                                                                                                                           |

| 18      | R <sub>FB</sub> 4 _1 | AI/O | Hardware Gain Selection for DAC1, Gain = 4.                                                                                                                                                                                                                                                                           |

| 19      | AV <sub>DD</sub>     | S    | Analog Power Supply. 5 V ± 5%.                                                                                                                                                                                                                                                                                        |

| 20      | $V_{REF}$            | AI/O | Voltage Reference, 2.5 V. Input when using external reference, output or floating when using internal reference.                                                                                                                                                                                                      |

| 21      | CV <sub>REF</sub>    | AI/O | Decoupling Capacitor for Internal Reference, Optional.                                                                                                                                                                                                                                                                |

| 22      | AGND                 | S    | Analog Ground Reference. It is recommended to connect DGND and AGND to the same ground plane under the device.                                                                                                                                                                                                        |

| 23      | R <sub>FB</sub> 4 _0 | AI/O | Hardware Gain Selection for DAC0, Gain = 4.                                                                                                                                                                                                                                                                           |

| 24      | R <sub>FB</sub> 2 _0 | AI/O | Hardware Gain Selection for DAC0, Gain = 2.                                                                                                                                                                                                                                                                           |

| 25      | R <sub>FB</sub> 1 _0 | AI/O | Hardware Gain Selection for DAC0, Gain = 1.                                                                                                                                                                                                                                                                           |

| 26      | I <sub>OUT</sub> 0   | AI/O | DAC0 Output Current.                                                                                                                                                                                                                                                                                                  |

| 27      | V <sub>CM</sub> 0    | AO   | Common Mode Voltage for DAC0 External TIA.                                                                                                                                                                                                                                                                            |

analog.com Rev. B | 12 of 70

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

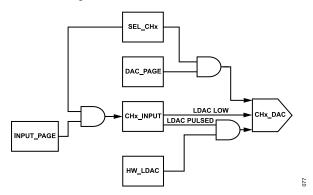

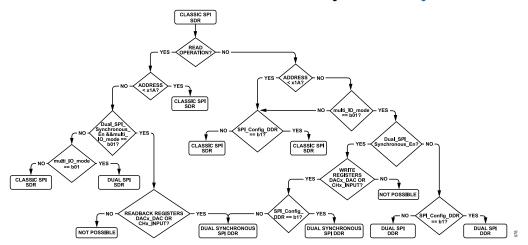

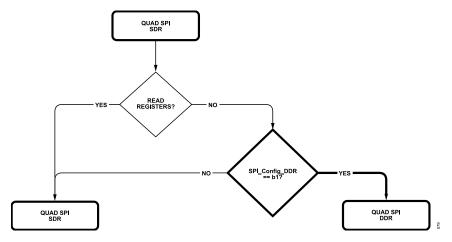

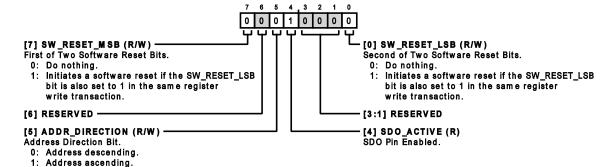

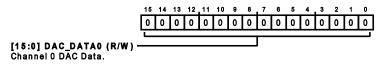

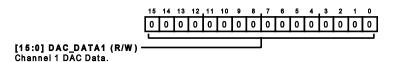

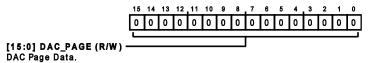

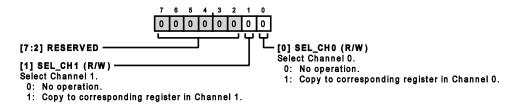

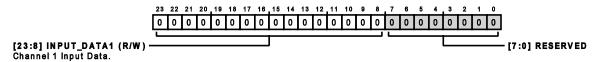

Table 7. Pin Function Descriptions (Continued)