# **Temperature Sensing MOSFET, N-Channel 40-V (D-S)**

#### **FEATURES**

- Temperature-Sense Diodes for Thermal Shutdown

- TrenchFET® Power MOSFET

- 175°C Maximum Junction Temperature

- ESD Protected: 2000 V

- Logic-Level Low On-Resistance

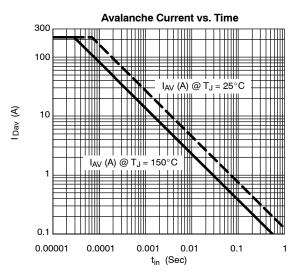

- Avalanche Rated

- Low Gate Charge

- Fast Turn-On Time

- 100% R<sub>g</sub> Tested

- 5-Lead Ď<sup>2</sup>PAK

#### **APPLICATIONS**

- Automotive

- Industrial

| PRODUCT SUMMARY          |                                 |                    |  |  |

|--------------------------|---------------------------------|--------------------|--|--|

| V <sub>(BR)DSS</sub> (V) | $r_{DS(on)}$ ( $\Omega$ )       | I <sub>D</sub> (A) |  |  |

| 40                       | 0.009 @ V <sub>GS</sub> = 10 V  | 60 <sup>a</sup>    |  |  |

|                          | 0.012 @ V <sub>GS</sub> = 4.5 V | 60                 |  |  |

Notes

a. Package Limited

#### **DESCRIPTION**

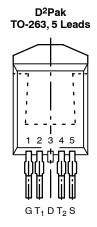

The SUM60N04-12LT is a 40-V n-channel, 15-m $\Omega$  logic level MOSFET in a 5-lead D²PAK package built on the Vishay Siliconix proprietary high-cell density TrenchFET technology.

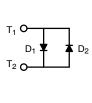

Two anti-parallel electrically isolated poly-silicon diodes are used to sense the temperature changes in the MOSFET.

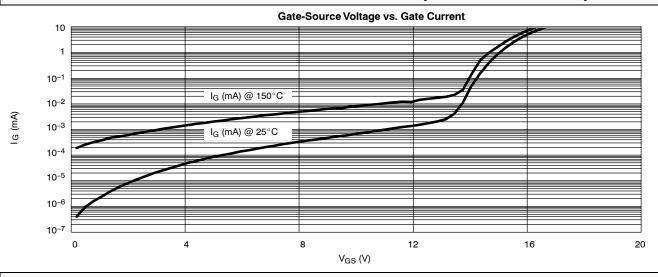

The gate of the MOSFET is protected from high voltage transients by two back-to-back poly-silicon zener diodes.

### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

G

N-Channel MOSFET

Ordering Information: SUM60N04-12LT

SUM60N04-12LT-E3 (Lead Free)

| ABSOLUTE MAXIMUM RATINGS (TA = 25°C UNLESS OTHERWISE NOTED) |                        |                                   |                 |      |  |

|-------------------------------------------------------------|------------------------|-----------------------------------|-----------------|------|--|

| Parameter                                                   |                        | Symbol                            | Limit           | Unit |  |

| Drain-Source Voltage                                        |                        | V <sub>DS</sub>                   | 40              | .,   |  |

| Gate-Source Voltage                                         |                        | V <sub>GS</sub>                   | ±20             | v    |  |

| V <sub>GS</sub> Clamp Current                               |                        | I <sub>G</sub>                    | 50              | mA   |  |

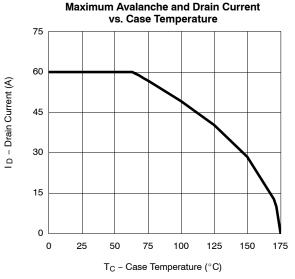

| Continuous Drain Current (T <sub>J</sub> = 175°C)           | T <sub>c</sub> = 25°C  |                                   | 60 <sup>a</sup> |      |  |

|                                                             | T <sub>c</sub> = 100°C | I <sub>D</sub>                    | 50              | А    |  |

| Avalanche Current                                           |                        | I <sub>AR</sub>                   | 50              |      |  |

| Repetitive Avalanche Energy L = 0.1 mH                      |                        | E <sub>AR</sub>                   | 125             | mJ   |  |

| Source-to-Anode Voltage                                     |                        | V <sub>SA</sub>                   | 100             | v    |  |

| Source-to-Cathode Voltage                                   |                        | V <sub>SC</sub>                   | 100             |      |  |

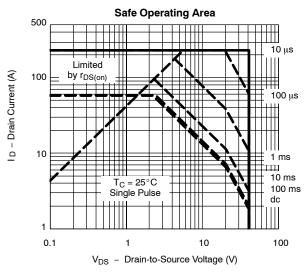

| Maximum Power Dissipation <sup>a</sup>                      | T <sub>C</sub> = 25°C  | _                                 | 110             |      |  |

|                                                             | $T_A = 25^{\circ}C^d$  | P <sub>D</sub>                    | 3.75            | w    |  |

| Operating Junction and Storage Temperature Range            |                        | T <sub>J</sub> , T <sub>stg</sub> | -55 to 175      | °C   |  |

| THERMAL RESISTANCE RATINGS       |                   |       |      |  |

|----------------------------------|-------------------|-------|------|--|

| Parameter                        | Symbol            | Limit | Unit |  |

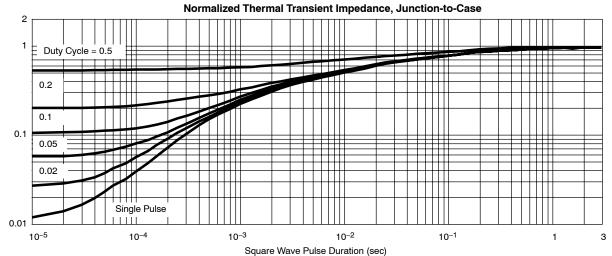

| Junction-to-Ambient <sup>d</sup> | R <sub>thJA</sub> | 40    | °C/W |  |

| Junction-to-Case                 | R <sub>thJC</sub> | 1.35  |      |  |

#### Notes:

- notes:

a. Package limited.

b. Duty Cycle ≤ 1%.

c. See SOA curve for voltage derating.

d. When mounted on 1-inch square PCB FR4.

| Parameter                                     | Symbol               | Test Condition                                                                                        | Min      | Тур    | Max    | Unit |

|-----------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|----------|--------|--------|------|

| Static                                        |                      |                                                                                                       | <b>.</b> |        |        |      |

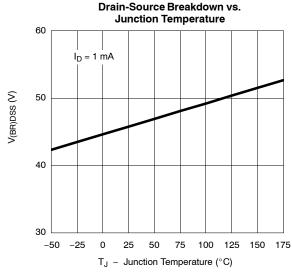

| Drain-Source Breakdown Voltage                | V <sub>(BR)DSS</sub> | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 1 mA                                                          | 40       |        |        |      |

| V <sub>GS</sub> Clamp Voltage                 | V <sub>GS</sub>      | $V_{DS}$ = 0 V, $I_G$ = 20 $\mu A$                                                                    | 10       |        | 20     | V    |

| Gate Threshold Voltage                        | V <sub>GS(th)</sub>  | $V_{DS} = V_{GS}$ , $I_{DS} = 1$ mA                                                                   | 1        |        | 2      |      |

| Gate-Body Leakage                             | I <sub>GSS</sub>     | $V_{DS}$ = 0 V, $V_{GS}$ = ±5 V                                                                       |          |        | ± 250  | nA   |

| Zero Gate Voltage Drain Current               | I <sub>DSS</sub>     | $V_{DS} = 40 \text{ V}, V_{GS} = 0 \text{ V}$                                                         |          |        | 1      |      |

| <del></del>                                   |                      | $V_{DS} = 40 \text{ V}, V_{GS} = 0 \text{ V}, T_{J} = 125^{\circ}\text{C}$                            |          |        | 50     | μΑ   |

| Zero Gate Voltage Drain Current               | I <sub>DSS</sub>     | $V_{DS}$ = 40 V, $V_{GS}$ = 0 V, $T_{J}$ = 175°C                                                      |          |        | 250    |      |

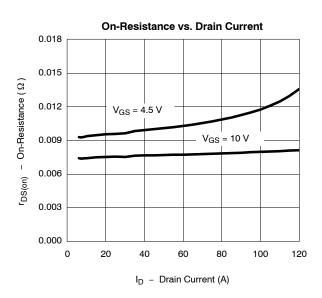

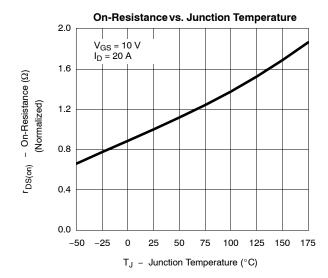

| Drain-Source On-State Resistance <sup>a</sup> |                      | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 20 A                                                         |          | 0.0075 | 0.009  | - Ω  |

|                                               |                      | $V_{GS}$ = 10 V, $I_D$ = 20 A, $T_J$ = 125°C                                                          |          |        | 0.0135 |      |

|                                               | r <sub>DS(on)</sub>  | $V_{GS}$ = 10 V, $I_D$ = 20 A, $T_J$ = 175°C                                                          |          |        | 0.018  |      |

|                                               |                      | $V_{GS} = 4.5 \text{ V}, I_D = 20 \text{ A}$                                                          |          | 0.0095 | 0.012  |      |

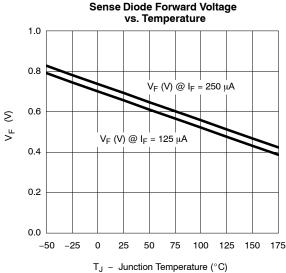

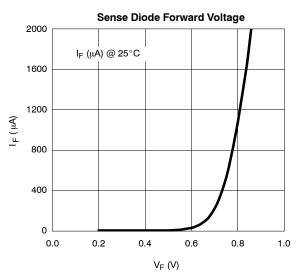

|                                               | V <sub>FD1</sub>     | $I_F = 250 \mu A$                                                                                     | 675      |        | 735    |      |

| Sense Diode Forward Voltage                   | V <sub>FD2</sub>     | I <sub>F</sub> = 250 μA                                                                               | 675      |        | 735    | mV   |

| Sense Diode Forward Voltage Increase          | $\Delta V_{F}$       | From $I_F$ = 125 $\mu A$ to $I_F$ = 250 $\mu A$                                                       | 25       |        | 50     |      |

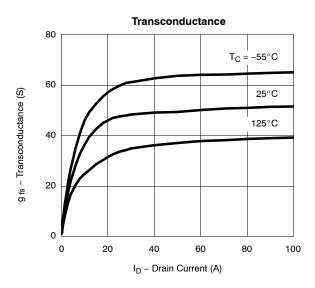

| Forward Transconductancea                     | 9 <sub>fs</sub>      | $V_{DS} = 15 \text{ V}, I_D = 20 \text{ A}$                                                           |          | 35     |        | S    |

| Dynamic <sup>b</sup>                          | <b>1</b>             |                                                                                                       | <b>'</b> |        | l      |      |

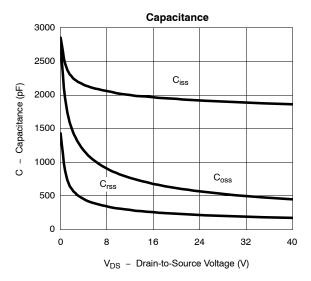

| Input Capacitance                             | C <sub>iss</sub>     |                                                                                                       |          | 1920   |        |      |

| Output Capacitance                            | C <sub>oss</sub>     | $V_{GS} = 0 \text{ V}, V_{DS} = 25 \text{ V}, f = 1 \text{ MHz}$                                      |          | 560    |        | pF   |

| Reverse Transfer Capacitance                  | C <sub>rss</sub>     |                                                                                                       |          | 210    |        |      |

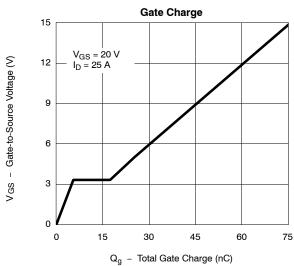

| Total Gate Charge <sup>c</sup>                | Qg                   |                                                                                                       |          | 51     | 70     | nC   |

| Gate-Source Charge <sup>c</sup>               | Q <sub>gs</sub>      | $V_{DS} = 20 \text{ V}, V_{GS} = 10 \text{ V}, I_D = 25 \text{ A}$                                    |          | 5.5    |        |      |

| Gate-Drain Charge <sup>c</sup>                | Q <sub>gd</sub>      |                                                                                                       |          | 12     |        |      |

| Gate Resistance                               | R <sub>g</sub>       |                                                                                                       | 1.2      |        | 4.1    | Ω    |

| Turn-On Delay Time <sup>c</sup>               | t <sub>d(on)</sub>   |                                                                                                       |          | 20     | 40     |      |

| Rise Time <sup>c</sup>                        | t <sub>r</sub>       | $V_{DD}$ = 20 V, $R_L$ = 0.8 $\Omega$<br>$I_D$ $\approx$ 25 A, $V_{GEN}$ = 10 V, $R_g$ = 2.5 $\Omega$ |          | 70     | 120    |      |

| Turn-Off Delay Time <sup>c</sup>              | t <sub>d(off)</sub>  |                                                                                                       | 35       | 70     | - ns   |      |

| Fall Time <sup>c</sup>                        | t <sub>f</sub>       |                                                                                                       |          | 20     | 40     |      |

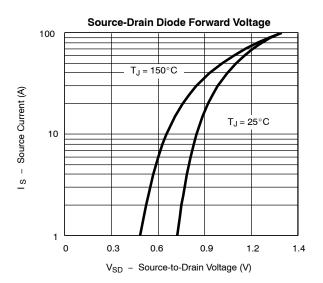

| Source-Drain Diode Ratings and                | d Characteristic     | s (T <sub>C</sub> = 25°C) <sup>b</sup>                                                                |          |        |        |      |

| Continuous Current                            | Is                   |                                                                                                       |          |        | 60     | ^    |

| Pulsed Current                                | I <sub>SM</sub>      |                                                                                                       |          |        | 240    | A .  |

| Forward Voltage <sup>a</sup>                  | V <sub>SD</sub>      | I <sub>F</sub> = 60 A, V <sub>GS</sub> = 0 V                                                          |          |        | 1.4    | V    |

| Reverse Recovery Time                         | t <sub>rr</sub>      | $I_F = 60 \text{ A}, \text{ di/dt} = 100 \text{ A/}\mu\text{s}$                                       |          | 40     | 60     | ns   |

### Notes:

- a Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2%.

b. Guaranteed by design, not subject to production testing.

c Independent of operating temperature.

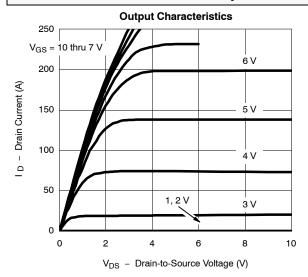

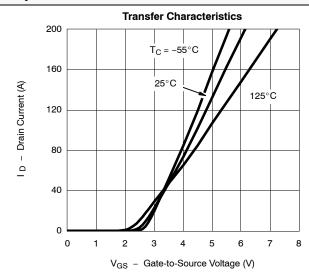

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

### TYPICAL CHARACTERISTICS OF G-S CLAMPING DIODES (25°C UNLESS NOTED)

### THERMAL RATINGS

Normalized Effective Transient Thermal Impedance

### **APPLICATIONS**

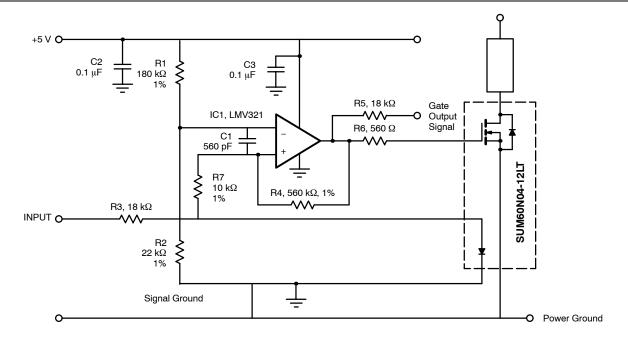

FIGURE 1.

The SUM60N04-12LT provides a non-committed diode to allow temperature sensing of the actual MOSFET chip. The addition of one simple comparator and a few other components is all that is required to implement a temperature protected MOSFET. Since it has a very tight tolerance on forward voltage, the forward voltage of the diode can be used to provide to shutdown signal. The diode forward voltage falls to around 0.4 V with a bias current of 250  $\mu A$  when the MOSFET chip is close to the maximum permitted temperature value. The external comparator used to detect over temperature can also be used as a driver stage for the MOSFET, meaning that the on/off input is logic compatible, and can be driven from a logic gate.

A typical circuit is shown in Figure 1. Here a LMV321 operational amplifier is used to drive the MOSFET, and as a comparator to when the maximum junction temperature is reached. The circuit will turn on once more when the chip has cooled to approximately 110°C, and can cycle on and off until the fault is cleared or the power is removed. This circuit has assumed a 5-V rail is available, but the circuit could easily be adapted for a 12-V rail, for example.

The LMV321 op amp was selected to give reasonable output current to drive the MOSFET at a reasonable price. The SC-70 package means that the protection circuit uses very little board space. However the limited output current means that it can only be used in slow switching applications, where one microsecond switching time and limited dv/dt immunity can be

accepted. For PWM and other faster applications, a buffer should be added to drive the MOSFET, or the schematic in Figure 2 used to give fast switching speed.

The reference voltage for the trip point is derived from the 5-V rail, which should have reasonable voltage accuracy and stability ( $\pm$  0.5 V). A voltage reference could be added if required, but the circuit is only intended to make the MOSFET invulnerable to drastic faults that might otherwise cause it to fail, not to give a precise shutdown point. 1% resistors are used to provide a reference voltage of 0.545 V, giving a nominal rising trip point of around 155°C, allowing for the hysteresis drop over R7.

A 560-pF capacitor across the inputs of the comparator provides some noise immunity and gives a response time of around a micro second, just faster than the switching speed of the MOSFET in this circuit (faster response has diminishing returns as the turn-off time is fixed). This does have a side effect of introducing such a delay at turn-on. If this is an issue (although if this delay is an issue, the switching time should be reviewed also), a separate driver could be added using a comparator for over temperature detection only as shown in Figure 2. The diode is then left biased whenever the power is applied to the load and there is no turn-on delay. In a very noisy environment C1 should be increased and additional capacitors may also be required from each input of the comparator to ground and on the logic input.

The bias current of  $250-\mu A$  nominal is derived from the input signal. In this manner, a simple comparator can be used as a driver for normal on/off operation and a fault detector circuit. The circuit used to provide the input signal must therefore be able to source 0.25 mA with no significant voltage drop.

The LMV321 can provide a output current of 60-mA typical, which provides reasonable switching time for non-PWM applications. A  $560-\Omega$  resistor is added in series to protect the op amp and to prevent instability, but will result in switching times of several micro seconds. A lower value may be possible depending on layout, but may violate conditions recommended by the op amp manufacturer.

Hysteresis is added by means of a resistor network around the comparator. Approximately 40  $^{\circ}$ C hysteresis is added using the components shown. This hysteresis could be reduced if necessary by increasing the value of R4. Another means of implementing hysteresis is to use the output of the comparator to provide some of the bias current for the sensing diode. When the comparator output is low (tripped/off), the bias current is reduced by, say, 150  $\mu$ A, causing the forward voltage to drop by around 50 mV. This concept would also allow a lower sourcing capability in the logic circuit providing the on/off signal

and therefore should be used if input current requirements become a problem.

With the input high, bias current flows and as long as the forward voltage of the diode is higher than 0.465 V, the comparator output is high and the MOSFET is on. If the forward voltage of the diode drops below 0.465 V, the comparator output goes low and the MOSFET is turned off. The gate drive voltage can also be used as an output signal (if required) for logic to interpret and to signify that there is a fault. Note the cathode of the sensing diode should NOT be connected directly to the source of the MOSFET as the noise introduced by high currents in the source loop could affect operation of the sensing circuit. A separate signal ground should be used and connect to power ground at one point only.

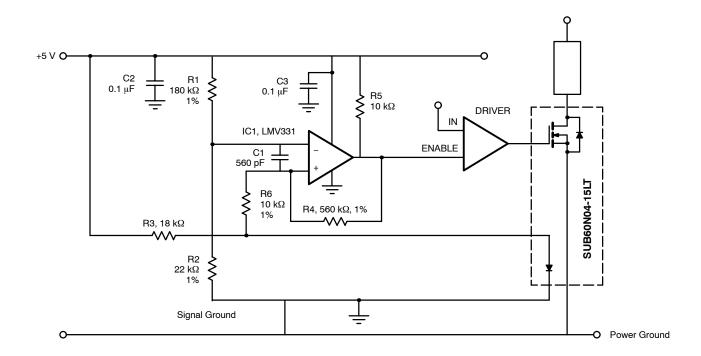

A variation on this schematic is shown in Figure 2. Here a low cost comparator (again in a SOT-23 or SC-70) is used to provide a fault output signal only. The diode bias current is taken from the 5 V. In this manner the diode bias is applied at all times, so the noise filtering capacitor, C1 will not introduce a turn-on delay. The fault output signal could be used to enable the gate driver as shown, or fed to larger monitoring circuit to shutdown the MOSFET.

FIGURE 2.