# PXI-5421 Specifications

### Contents

| PXI-5421 Specifications | 7 |

|-------------------------|---|

| NI JTZI JDECINCALIONS   | _ |

### PXI-5421 Specifications

#### **Definitions**

Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.

**Characteristics** describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- Typical specifications describe the performance met by a majority of models.

- **Nominal** specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

Specifications are **Nominal** unless otherwise noted.

#### **Conditions**

Specifications are valid under the following conditions unless otherwise noted:

- Ambient temperature range of 0 °C to 55 °C

- Analog filter enabled

- Interpolation set to maximum allowed factor for a given sample rate

- Signals terminated with 50 Ω

- Direct path set to 1 Vpk-pk

- Low-gain amplifier path set to 2 Vpk-pk

- High-gain amplifier path set to 12 Vpk-pk

- Sample Clock set to 100 MS/s

Typical specifications are valid under the following conditions unless otherwise noted:

Ambient temperature range of 23 ±5 °C

### **CH 0 Analog Output**

| Number of channels | 1        |

|--------------------|----------|

| Connector type     | SMB jack |

### **Output Voltage**

| Full-scale voltage |                                                        |

|--------------------|--------------------------------------------------------|

| Main output path   | 12.00 V pk-pk to 5.64 mV pk-pk into a 50 $\Omega$ load |

| Direct output path | 1.000 V pk-pk to 0.707 V pk-pk                         |

| DAC resolution     | 16 bits                                                |

### **Amplitude and Offset**

Table 1. Amplitude Range

| Path Load           | Amplitude (V pk-pk) |         |      |

|---------------------|---------------------|---------|------|

|                     | Minimum             | Maximum |      |

| Direct              | 50 Ω                | 0.707   | 1.00 |

|                     | 1 kΩ                | 1.35    | 1.91 |

|                     | Open                | 1.41    | 2.00 |

| Low-gain amplifier  | 50 Ω                | 0.00564 | 2.00 |

|                     | 1 kΩ                | 0.0107  | 3.81 |

|                     | Open                | 0.0113  | 4.00 |

| High-gain amplifier | 50 Ω                | 0.0338  | 12.0 |

|                     | 1 kΩ                | 0.0644  | 22.9 |

|                     | Open                | 0.0676  | 24.0 |

| Amplitude resolution | <0.06% (0.004 dB) of <b>Amplitude Range</b>                                               |

|----------------------|-------------------------------------------------------------------------------------------|

| Offset range         | Span of ±25% of <b>Amplitude Range</b> with increments <0.0014% of <b>Amplitude Range</b> |

#### Accuracy

#### Table 2. DC Accuracy

| Path                | DC Accuracy                      | DC Accuracy |                                                                                |  |

|---------------------|----------------------------------|-------------|--------------------------------------------------------------------------------|--|

|                     | ±10 °C of Self-Ca<br>Temperature | alibration  | 0 °C to 55 °C                                                                  |  |

| Low-gain amplifier  | ±0.2% of Ampli                   |             | $\pm 0.4\%$ of <b>Amplitude Range</b> $\pm 0.05\%$ of <b>Offset</b> $\pm 1$ mV |  |

| High-gain amplifier | 0.05% of <b>Offset</b>           | ± 500 μV    |                                                                                |  |

| Direct              | ±0.2% Amplitud                   | de Range    | ±0.4% Amplitude Range                                                          |  |

| DC offset error     |                                  | ±30 mV      |                                                                                |  |

## (+2.0% + 1 mV), (-1.0% - 1 mV) AC amplitude accuracy (+0.8% + 0.5 mV), (-0.2% - 0.5 mV), typical

### Output

| Output impedance            | Software-selectable: 50 $\Omega$ or 75 $\Omega$ , nominal              |

|-----------------------------|------------------------------------------------------------------------|

| Load impedance compensation | Output amplitude is compensated for user-<br>specified load impedances |

| Output coupling             | DC                                                                     |

| Output enable               | Software-selectable                                                    |

| Maximum output overload | CH 0 can be connected to a 50 $\Omega$ , ±12 V (±8 V for the direct path) source without sustaining any damage. |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|

| Waveform summing        | Supported                                                                                                       |

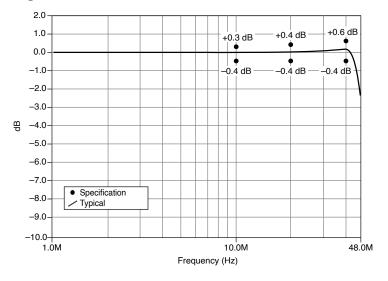

### **Frequency and Transient Response**

| Bandwidth                    | 43 MHz                                                                                                     |

|------------------------------|------------------------------------------------------------------------------------------------------------|

| Digital interpolation filter | Software-selectable: Finite impulse response (FIR) filter. Available interpolation factors are 2, 4, or 8. |

| Analog filter                | Software-selectable: 7-pole elliptical filter                                                              |

| Passband flatness            |                                                                                                            |

| Direct path                  | -0.4 dB to +0.6 dB, 100 Hz to 40 MHz                                                                       |

| Low-gain amplifier path      | -1.0 dB to +0.5 dB, 100 Hz to 20 MHz                                                                       |

| High-gain amplifier path     | -1.2 dB to +0.5 dB, 100 Hz to 20 MHz                                                                       |

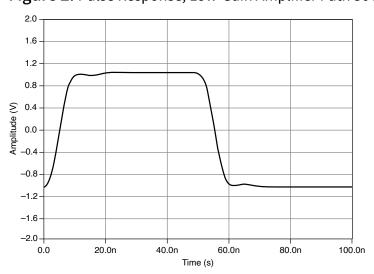

| Pulse response               |                                                                                                            |

| Direct path                  |                                                                                                            |

| Rise/fall time               | <5 ns                                                                                                      |

|                              | <4.5 ns, typical                                                                                           |

| Aberration                   | <10%, typical                                                                                              |

| Low-gain amplifier path      |                                                                                                            |

| Rise/fall time           | <8 ns            |  |

|--------------------------|------------------|--|

|                          | <7 ns            |  |

|                          | <5.5 ns, typical |  |

| Aberration               | <5%, typical     |  |

| High-gain amplifier path |                  |  |

| Rise/fall time           | <10 ns           |  |

| Aberration               | <5%, typical     |  |

Figure 1. Normalized Passband Flatness, Direct Path

Figure 2. Pulse Response, Low-Gain Amplifier Path 50  $\Omega$  Load

### **Suggested Maximum Frequencies for Common Functions**

| Suggested maximum frequencies |  |  |

|-------------------------------|--|--|

| Direct path                   |  |  |

| 43 MHz                        |  |  |

| Not recommended               |  |  |

| Not recommended               |  |  |

| Not recommended               |  |  |

| Low-gain amplifier path       |  |  |

| 43 MHz                        |  |  |

| 25 MHz                        |  |  |

| 5 MHz                         |  |  |

| 5 MHz                         |  |  |

|                               |  |  |

| High-gain amplifier path |          |  |

|--------------------------|----------|--|

| Sine                     | 43 MHz   |  |

| Square                   | 12.5 MHz |  |

| Ramp                     | 5 MHz    |  |

| Triangle                 | 5 MHz    |  |

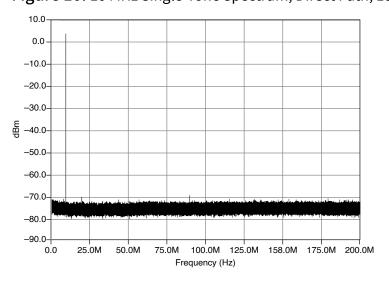

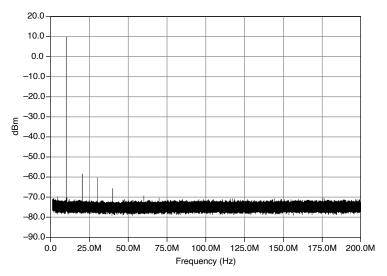

### **Spectral Characteristics**

Table 3. Spurious-Free Dynamic Range (SFDR) with Harmonics

| Frequency | SFDR with Harmonics (dB), Typical |                            |                             |  |

|-----------|-----------------------------------|----------------------------|-----------------------------|--|

|           | Direct Path                       | Low-Gain Amplifier<br>Path | High-Gain Amplifier<br>Path |  |

| 1 MHz     | 70                                | 65                         | 66                          |  |

| 5 MHz     |                                   |                            | 58                          |  |

| 10 MHz    |                                   |                            | 52                          |  |

| 20 MHz    | 63                                | 64                         | 49                          |  |

| 30 MHz    | 57                                | 60                         | 43                          |  |

| 40 MHz    | 48                                | 53                         | 39                          |  |

| 50 MHz    |                                   |                            |                             |  |

| 60 MHz    | 47                                | 52                         |                             |  |

| 70 MHz    |                                   |                            |                             |  |

| 80 MHz    | 41                                |                            |                             |  |

Table 4. Spurious-Free Dynamic Range (SFDR) without Harmonics

| Frequency | SFDR without Harmonics (dB), Typical |                            |                             |  |

|-----------|--------------------------------------|----------------------------|-----------------------------|--|

|           | Direct Path                          | Low-Gain Amplifier<br>Path | High-Gain Amplifier<br>Path |  |

| 1 MHz     | 84                                   | 79                         | 76                          |  |

| 5 MHz     |                                      |                            |                             |  |

| Frequency | SFDR without Harmonics (dB), Typical |                            |                             |

|-----------|--------------------------------------|----------------------------|-----------------------------|

|           | Direct Path                          | Low-Gain Amplifier<br>Path | High-Gain Amplifier<br>Path |

| 10 MHz    | 79                                   |                            |                             |

| 20 MHz    |                                      |                            |                             |

| 30 MHz    | 72                                   | 70                         | 67                          |

| 40 MHz    | 47                                   | 57                         | 54                          |

| 50 MHz    |                                      | 52                         | _                           |

| 60 MHz    | 46                                   | 51                         |                             |

| 70 MHz    |                                      |                            |                             |

| 80 MHz    | 40                                   |                            |                             |

#### Table 5. Average Noise Density, Direct Path

| Amplitude Range |         | Average Noise Density, Typical |        |         |

|-----------------|---------|--------------------------------|--------|---------|

|                 |         | nV<br>√Hz                      | dBm/Hz | dBFS/Hz |

| 1.00 V pk-pk    | 4.0 dBm | 19.9                           | -141   | -145    |

#### Table 6. Average Noise Density, Low-Gain Amplifier Path

| Amplitude Range |           | Average Noise Density, Typical |        |         |

|-----------------|-----------|--------------------------------|--------|---------|

|                 |           | nV<br>√Hz                      | dBm/Hz | dBFS/Hz |

| 0.06 V pk-pk    | -20.5 dBm | 1.3                            | -148   | -144    |

| 0.10 V pk-pk    | -16.0 dBm | 2.2                            |        |         |

| 0.40 V pk-pk    | -4.0 dBm  | 8.9                            |        |         |

| 1.00 V pk-pk    | 4.0 dBm   | 22.3                           | -140   |         |

| 2.00 V pk-pk    | 10.0 dBm  | 44.6                           | -134   |         |

Table 7. Average Noise Density, High-Gain Amplifier Path

| Amplitude Range |          | Average Noise Density, Typical |        |         |

|-----------------|----------|--------------------------------|--------|---------|

|                 |          | nV<br>√Hz                      | dBm/Hz | dBFS/Hz |

| 4.00 V pk-pk    | 16.0 dBm | 93.8                           | -128   | -144    |

| 12.00 V pk-pk   | 25.6 dBm | 281.5                          | -118   |         |

Figure 3. 10 MHz Single-Tone Spectrum, Direct Path, 200 MS/s, Typical

Figure 4. 10.00001 MHz Single-Tone Spectrum, Low-Gain Amplifier Path, 200 MS/s, Typical

Figure 5. Total Harmonic Distortion, Direct Path, Typical

Figure 6. Total Harmonic Distortion, Low-Gain Amplifier Path, Typical

Figure 7. Total Harmonic Distortion, High-Gain Amplifier Path, Typical

Figure 8. Intermodulation Distortion, 200 kHz Separation, Typical

Figure 9. Direct Path, Two-Tone Spectrum, Typical

Signal to Noise and Distortion (SINAD)

All values are typical.

| Direct path             |                                       |

|-------------------------|---------------------------------------|

| 1 MHz                   | 64 dB                                 |

| 10 MHz                  | 61 dB                                 |

| 20 MHz                  | 57 dB                                 |

| 30 MHz                  | 60 dB                                 |

| 40 MHz                  | 60 dB                                 |

| 43 MHz                  | 58 dB                                 |

| Low-gain amplifier path | <u> </u>                              |

| 1 MHz                   | 66 dB                                 |

| 10 MHz                  | 60 dB                                 |

|                         | T T T T T T T T T T T T T T T T T T T |

| 20 MHz                   | 56 dB |

|--------------------------|-------|

| 30 MHz                   | 62 dB |

| 40 MHz                   | 62 dB |

| 43 MHz                   | 60 dB |

| High-gain amplifier path |       |

| 1 MHz                    | 63 dB |

| 10 MHz                   | 47 dB |

| 20 MHz                   | 42 dB |

| 30 MHz                   | 62 dB |

| 40 MHz                   | 62 dB |

| 43 MHz                   | 55 dB |

#### Spurious-Free Dynamic Range (SFDR)

All values are typical and include aliased harmonics. Dynamic range is defined as the difference between the carrier level and the largest spur.

| SFDR with harmonics |       |  |

|---------------------|-------|--|

| Direct path         |       |  |

| 1 MHz               | 76 dB |  |

| 10 MHz              | 68 dB |  |

| 20 MHz              | 60 dB |  |

| Direct path              |       |  |

|--------------------------|-------|--|

| SFDR without harmonics   |       |  |

| 43 MHz                   | 59 dB |  |

| 40 MHz                   | 74 dB |  |

| 30 MHz                   | 74 dB |  |

| 20 MHz                   | 42 dB |  |

| 10 MHz                   | 47 dB |  |

| 1 MHz                    | 58 dB |  |

| High-gain amplifier path |       |  |

| 43 MHz                   | 75 dB |  |

| 40 MHz                   | 73 dB |  |

| 30 MHz                   | 73 dB |  |

| 20 MHz                   | 57 dB |  |

| 10 MHz                   | 64 dB |  |

| 1 MHz                    | 71 dB |  |

| Low-gain amplifier path  |       |  |

| 43 MHz                   | 78 dB |  |

| 40 MHz                   | 76 dB |  |

| 30 MHz                   | 73 dB |  |

| 1 MHz                    | 87 dB    |

|--------------------------|----------|

| 10 MHz                   | 86 dB    |

| 20 MHz                   | 79 dB    |

| 30 MHz                   | 72 dB    |

| 40 MHz                   | 75 dB    |

| 43 MHz                   | 77 dB    |

| Low-gain amplifier path  | <u>'</u> |

| 1 MHz                    | 90 dB    |

| 10 MHz                   | 88 dB    |

| 20 MHz                   | 88 dB    |

| 30 MHz                   | 72 dB    |

| 40 MHz                   | 72 dB    |

| 43 MHz                   | 74 dB    |

| High-gain amplifier path |          |

| 1 MHz                    | 90 dB    |

| 10 MHz                   | 90 dB    |

| 20 MHz                   | 88 dB    |

| 30 MHz                   | 73 dB    |

| 40 MHz | 73 dB |

|--------|-------|

| 43 MHz | 59 dB |

#### Total Harmonic Distortion (THD)

| THD (0 °C to 40 °C)     |                  |

|-------------------------|------------------|

| Direct path             |                  |

| 20 kHz                  | -77 dBc, typical |

| 1 MHz                   | -75 dBc, typical |

| 5 MHz                   | -68 dBc          |

| 10 MHz                  | -65 dBc          |

|                         | -66 dBc, typical |

| 20 MHz                  | -55 dBc          |

|                         | -61 dBc, typical |

| 30 MHz                  | -50 dBc          |

|                         | -57 dBc, typical |

| 40 MHz                  | -47 dBc          |

|                         | -54 dBc, typical |

| 43 MHz                  | -46 dBc          |

|                         | -53 dBc, typical |

| Low-gain amplifier path |                  |

| 20 kHz                   | -77 dBc, typical |  |

|--------------------------|------------------|--|

| 1 MHz                    | -70 dBc, typical |  |

| 5 MHz                    | -68 dBc          |  |

| 10 MHz                   | -61 dBc          |  |

|                          | -66 dBc, typical |  |

| 20 MHz                   | -53 dBc          |  |

|                          | -61 dBc, typical |  |

| 30 MHz                   | -48 dBc          |  |

|                          | -57 dBc, typical |  |

| 40 MHz                   | -46 dBc          |  |

|                          | -54 dBc, typical |  |

| 43 MHz                   | -45 dBc          |  |

|                          | -53 dBc, typical |  |

| High-gain amplifier path |                  |  |

| 20 kHz                   | -77 dBc, typical |  |

| 1 MHz                    | -62 dBc, typical |  |

| 5 MHz                    | -55 dBc          |  |

| 10 MHz                   | -46 dBc          |  |

| -76 dBc, typical -74 dBc, typical -67 dBc -63 dBc |

|---------------------------------------------------|

| -74 dBc, typical<br>-67 dBc                       |

| -67 dBc                                           |

|                                                   |

| -63 dBc                                           |

|                                                   |

| -54 dBc                                           |

| -57 dBc                                           |

| -48 dBc                                           |

| -52 dBc                                           |

| -45 dBc                                           |

| -50 dBc                                           |

| -44 dBc                                           |

| -49 dBc                                           |

|                                                   |

| -76 dBc, typical                                  |

| -69 dBc, typical                                  |

| -67 dBc                                           |

| -60 dBc                                           |

|                                                   |

| 20 MHz                   | -52 dBc          |  |

|--------------------------|------------------|--|

|                          | -55 dBc          |  |

| 30 MHz                   | -46 dBc          |  |

|                          | -50 dBc          |  |

| 40 MHz                   | -41 dBc          |  |

|                          | -47 dBc          |  |

| 43 MHz                   | -41 dBc          |  |

|                          | -46 dBc          |  |

| High-gain amplifier path |                  |  |

| 20 kHz                   | -76 dBc, typical |  |

| 1 MHz                    | -61 dBc, typical |  |

| 5 MHz                    | -54 dBc          |  |

| 10 MHz                   | -45 dBc          |  |

#### Average Noise Density

| Direct path                       |                                                                      |

|-----------------------------------|----------------------------------------------------------------------|

| 1 Vpk-pk, 4.0 dBm amplitude range | $ \frac{\text{nV}}{\sqrt{\text{Hz}}} $ , -142 dBm/Hz, -146.0 dBFS/Hz |

| Low-gain amplifier path           |                                                                      |

| 0.06 Vpk-pk, -20.4 dBm amplitude range | 9                                                                     |

|----------------------------------------|-----------------------------------------------------------------------|

| 0.1 Vpk-pk, -16.0 dBm amplitude range  | 9                                                                     |

| 0.4 Vpk-pk, -4.0 dBm amplitude range   | 13<br><u>nV</u><br>√Hz<br>, -145 dBm/Hz, -141.0 dBFS/Hz               |

| 1 Vpk-pk, 4.0 dBm amplitude range      | 18<br>nV<br>√Hz<br>, -142 dBm/Hz, -146.0 dBFS/Hz                      |

| 2 Vpk-pk, 10.0 dBm amplitude range     | 35<br>nV<br>√Hz<br>, -136 dBm/Hz, -146.0 dBFS/Hz                      |

| High-gain amplifier path               |                                                                       |

| 4 Vpk-pk, 16.0 dBm amplitude range     | 71 $\frac{\text{nV}}{\sqrt{\text{Hz}}}$ , -130 dBm/Hz, -146.0 dBFS/Hz |

| 12 Vpk-pk, 25.6 dBm amplitude range    | 213<br>nV<br>√Hz<br>, -120 dBm/Hz, -145.6 dBFS/Hz                     |

Intermodulation Distortion (IMD)

All values are typical.

#### Direct path

| 19.9 MHz and 20.1 MHz   | -78 dBc |  |

|-------------------------|---------|--|

| 34.0 MHz and 35.0 MHz   | -75 dBc |  |

| 34.8 MHz and 35.0 MHz   | -75 dBc |  |

| 42.0 MHz and 43.0 MHz   | -75 dBc |  |

| 42.8 MHz and 43.0 MHz   | -75 dBc |  |

| Low-gain amplifier path |         |  |

| 10.2 MHz and 11.2 MHz   | -80 dBc |  |

| 10.6 MHz and 10.8 MHz   | -79 dBc |  |

| 19.5 MHz and 20.5 MHz   | -66 dBc |  |

| 19.9 MHz and 20.1 MHz   | -65 dBc |  |

| 34.0 MHz and 35.0 MHz   | -58 dBc |  |

| 34.8 MHz and 35.0 MHz   | -58 dBc |  |

| 42.0 MHz and 43.0 MHz   | -55 dBc |  |

| 42.8 MHz and 43.0 MHz   | -55 dBc |  |

| 10.2 MHz and 11.2 MHz | -62 dBc |

|-----------------------|---------|

| 10.6 MHz and 10.8 MHz | -61 dBc |

| 19.5 MHz and 20.5 MHz | -54 dBc |

| 19.9 MHz and 20.1 MHz | -50 dBc |

| 34.0 MHz and 35.0 MHz | -51 dBc |

| 34.8 MHz and 35.0 MHz | -51 dBc |

| 42.0 MHz and 43.0 MHz | -51 dBc |

| 42.8 MHz and 43.0 MHz | -50 dBc |

#### **Spectrum Performance**

The noise floor in the following figures is limited by the measurement device. Refer to Average Noise Density for more information about this limit.

Figure 10. 10 MHz Single-Tone Spectrum, Direct Path, 100 MS/s, Interpolation Factor Set to 4

**Figure 11.** 10 MHz Single-Tone Spectrum, Low-Gain Amplifier Path, 100 MS/s, Interpolation Factor Set to 4

Figure 12. Direct Path, Two-Tone Spectrum, Typical

### Sample Clock

| Sources  |                            |

|----------|----------------------------|

| Internal | Divide-by-N (N ≥ 1)        |

|          | DDS-based, High-Resolution |

|          |                            |

| External | CLK IN (SMB front panel connector)                        |

|----------|-----------------------------------------------------------|

|          | DDC CLK IN (DIGITAL DATA & CONTROL front panel connector) |

|          | PXI Star Trigger (backplane connector)                    |

|          | PXI_Trig <07> (backplane connector)                       |

|          |                                                           |

### Sample Rate Range and Resolution

#### Table 8. Sample Rate Range

| Sample Clock Source | Sample Rate Range     |

|---------------------|-----------------------|

| Divide-by-N         | 23.84 S/s to 100 MS/s |

| High-Resolution     | 10 S/s to 100 MS/s    |

| CLKIN               | 200 kS/s to 105 MS/s  |

| DDC CLK IN          | 10 S/s to 105 MS/s    |

| PXI Star Trigger    | 10 S/s to 105 MS/s    |

| PXI_Trig<07>        | 10 S/s to 20 MS/s     |

#### Table 9. Sample Rate Resolution

| Sample Clock Source | Sample Rate Resolution                                        |

|---------------------|---------------------------------------------------------------|

| Divide-by-N         | Configurable to $(100 \text{ MS/s})/N(1 \le N \le 4,194,304)$ |

| High-Resolution     | 1.06 μHz                                                      |

| CLKIN               | Resolution determined by external clock source.               |

| DDC CLK IN          | External Sample Clock duty cycle tolerance 40% to 60%.        |

| PXI Star Trigger    | 10 0070.                                                      |

| PXI_Trig<07>        |                                                               |

#### **Effective Sample Rate**

| (Interpolation factor) * (Sample rate) = Effective sample rate |                       |                       |

|----------------------------------------------------------------|-----------------------|-----------------------|

| Interpolation factor                                           | Sample rate           | Effective sample rate |

| 1 (Off)                                                        | 10 S/s to 105 MS/s    | 10 S/s to 105 MS/s    |

| 2                                                              | 12.5 MS/s to 105 MS/s | 25 MS/s to 210 MS/s   |

| 4                                                              | 10 MS/s to 100 MS/s   | 40 MS/s to 400 MS/s   |

| 8                                                              | 10 MS/s to 50 MS/s    | 80 MS/s to 400 MS/s   |

### Sample Clock Delay Range and Resolution

Table 10. Delay Adjustment Range

| Sample Clock Source | Delay Adjustment Range |

|---------------------|------------------------|

| Divide-by-N         | ±1 Sample Clock period |

| High-Resolution     |                        |

| CLKIN               | 0 ns to 7.6 ns         |

| DDC CLK IN          |                        |

| PXI Star Trigger    |                        |

| PXI_Trig <07>       |                        |

#### Table 11. Delay Adjustment Resolution

| Sample Clock Source | Delay Adjustment Resolution |

|---------------------|-----------------------------|

| Divide-by-N         | <10 ps                      |

| High-Resolution     | Sample Clock period/16,384  |

| CLKIN               | <15 ps                      |

| DDC CLK IN          |                             |

| PXI Star Trigger    |                             |

| PXI_Trig <07>       |                             |

### System Phase Noise and Jitter (10 MHz Carrier)

| System phase noise density offset |  |

|-----------------------------------|--|

|                                   |  |

| Divide-by-N                                              |             |  |

|----------------------------------------------------------|-------------|--|

| 100 Hz                                                   | -107 dBc/Hz |  |

| 1 kHz                                                    | -121 dBc/Hz |  |

| 10 kHz                                                   | -137 dBc/Hz |  |

| High-Resolution                                          | '           |  |

| 100 Hz                                                   | -109 dBc/Hz |  |

| 1 kHz                                                    | -121 dBc/Hz |  |

| 10 kHz                                                   | -123 dBc/Hz |  |

| CLK IN                                                   | <u>'</u>    |  |

| 100 Hz                                                   | -111 dBc/Hz |  |

| 1 kHz                                                    | -122 dBc/Hz |  |

| 10 kHz                                                   | -135 dBc/Hz |  |

| PXI Star Trigger                                         |             |  |

| 100 Hz                                                   | -115 dBc/Hz |  |

| 1 kHz                                                    | -118 dBc/Hz |  |

| 10 kHz                                                   | -130 dBc/Hz |  |

| System output jitter (integrated from 100 Hz to 100 kHz) |             |  |

| Divide-by-N                                              | <1.2 ps rms |  |

| High-Resolution                                          | <4.2 ps rms |  |

|                                                          |             |  |

| CLK IN                                       | <1.2 ps rms |  |

|----------------------------------------------|-------------|--|

| PXI Star Trigger                             | <3.0 ps rms |  |

| External Sample Clock input jitter tolerance |             |  |

| Cycle-cycle jitter                           | ±300 ps     |  |

| Period jitter                                | ±1 ns       |  |

### Sample Clock Exporting

| Destinations      | PFI <01> (SMB front panel connectors)                      |

|-------------------|------------------------------------------------------------|

|                   | DDC CLK OUT (DIGITAL DATA & CONTROL front panel connector) |

|                   | PXI_Trig <06> (backplane connector)                        |

| Maximum frequency |                                                            |

| PFI <01>          | 105 MHz                                                    |

| DDC CLK OUT       | 105 MHz                                                    |

| PXI_Trig <06>     | 20 MHz                                                     |

| Jitter            |                                                            |

| PFI 0             | 6 ps rms, typical                                          |

| PFI 1             | 12 ps rms, typical                                         |

| DDC CLK OUT       | 40 ps rms, typical                                         |

| Duty cycle        |                                                            |

|                   |                                                            |

| PFI <01>    | 25% to 65% |

|-------------|------------|

| DDC CLK OUT | 40% to 60% |

### Onboard Clock (Internal VCXO)

| Source             | Internal Sample Clocks can either be locked to a Reference Clock using a phase-locked loop or derived from the onboard VCXO frequency reference. |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency accuracy | ±25 ppm                                                                                                                                          |

### Phase-Locked Loop (PLL) Reference Clock

| Sources            | PXI_CLK10 (backplane connector)  CLK IN (SMB front panel connector)                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency accuracy | When using the PLL, the frequency accuracy of the PXI-5421 is solely dependent on the frequency accuracy of the PLL Reference Clock source. |

| Lock time          | 200 ms, maximum 70 ms, typical                                                                                                              |

| Frequency range    | 5 MHz to 20 MHz in increments of 1 MHz                                                                                                      |

| Duty cycle range   | 40% to 60%                                                                                                                                  |

| Destinations       | PFI <01> (SMB front panel connectors)                                                                                                       |

| PXI_Trig <06> (backplane connector) |  |

|-------------------------------------|--|

|                                     |  |

#### **CLK IN**

| Connector type                            | SMB jack                                       |

|-------------------------------------------|------------------------------------------------|

| Direction                                 | Input                                          |

| Destinations                              | Sample Clock                                   |

|                                           | PLL Reference Clock                            |

| Frequency range                           |                                                |

| Sample Clock destination and sine waves   | 1 MHz to 105 MHz                               |

| Sample Clock destination and square waves | 200 kHz to 105 MHz                             |

| PLL Reference Clock destination           | 5 MHz to 20 MHz                                |

| Input voltage range into 50 $\Omega$      |                                                |

| Sine wave                                 | 0.65 V pk-pk to 2.8 V pk-pk (0 dBm to +13 dBm) |

| Square wave                               | 0.2 V pk-pk to 2.8 V pk-pk                     |

| Maximum input overload                    | ±10 V                                          |

| Input impedance                           | 50 Ω                                           |

| Input coupling                            | AC                                             |

#### PFI 0 and PFI 1

| Connector type         | SMB jack (x2)                                                                                                                                                                                            |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Direction              | Bidirectional                                                                                                                                                                                            |

| Frequency range        | DC to 105 MHz                                                                                                                                                                                            |

| As an input (trigger)  |                                                                                                                                                                                                          |

| Destinations           | Start Trigger                                                                                                                                                                                            |

| Maximum input overload | -2 V to +7 V                                                                                                                                                                                             |

| VIH                    | 2.0 V                                                                                                                                                                                                    |

| VIL                    | 0.8 V                                                                                                                                                                                                    |

| Input impedance        | 1 kΩ                                                                                                                                                                                                     |

| As an output (event)   |                                                                                                                                                                                                          |

| Sources                | Sample Clock divided by integer K (1 ≤ K ≤ 4,194,304)  Sample Clock Timebase (100 MHz) divided by integer M (2 ≤ M ≤ 4,194,304)  PLL Reference Clock  Marker  Exported Start Trigger (Out Start Trigger) |

| Output impedance       | 50 Ω                                                                                                                                                                                                     |

|                        |                                                                                                                                                                                                          |

| Maximum output overload     | -2 V to +7 V |  |

|-----------------------------|--------------|--|

| Minimum V OH                |              |  |

| Open load                   | 2.9 V        |  |

| 50 Ω load                   | 1.4 V        |  |

| Maximum V OL                |              |  |

| Open load                   | 0.2 V        |  |

| 50 Ω load                   | 0.2 V        |  |

| Rise/fall time (20% to 80%) | ≤2.0 ns      |  |

#### TClk Synchronization

# Intermodule SMC Synchronization Using NI-TClk for Identical Modules

National Instruments TClk synchronization method and the NI-TClk instrument driver are used to align the Sample Clocks on any number of SMC-based modules in a chassis.

- Specifications are valid for any number of PXI modules installed in one PXI-1042 chassis

- All parameters are set to identical values for each SMC-based module

- Sample Clock is set to 100 MS/s, Divide-by-N, and all filters are disabled

- For other configurations, including multichassis systems, contact NI Technical Support at <u>ni.com/support</u>

| Skew | 500 ps, typical |

|------|-----------------|

|      |                 |

| Average skew after manual adjustment     | <10 ps, typical |

|------------------------------------------|-----------------|

| Sample Clock delay/adjustment resolution | ≤10 ps, typical |

**Note** Although you can use NI-TClk to synchronize nonidentical modules, these specifications apply only to synchronizing identical modules.

### DIGITAL DATA & CONTROL (DDC)

| Connector type                | 68-pin VHDCI female receptacle |

|-------------------------------|--------------------------------|

| Number of data output signals | 16                             |

| Control signals               | DDC CLK OUT (clock output)     |

|                               | DDC CLK IN (clock input)       |

|                               | PFI 2 (input)                  |

|                               | PFI 3 (input)                  |

|                               | PFI 4 (output)                 |

|                               | PFI 5 (output)                 |

| Ground                        | 23 pins                        |

#### Output Signals (Data Outputs, DDC CLK OUT, and PFI <4..5>)

| Low-voltage differential signal (LVDS) |                |

|----------------------------------------|----------------|

| V OH                                   | 1.3 V, typical |

|                                        |                |

|                             | 1.7 V, maximum                                                                                                                                               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V OL                        | 0.8 V, minimum                                                                                                                                               |

|                             | 1.0 V, typical                                                                                                                                               |

| Differential output voltage | 0.25 V, minimum                                                                                                                                              |

|                             | 0.45 V, maximum                                                                                                                                              |

| Output common-mode voltage  | 1.125 V, minimum                                                                                                                                             |

|                             | 1.375 V, maximum                                                                                                                                             |

| Rise/fall time (20% to 80%) | 0.8 ns, typical                                                                                                                                              |

|                             | 1.6 ns, maximum                                                                                                                                              |

| Output skew                 | 1 ns, typical                                                                                                                                                |

|                             | 2 ns, maximum                                                                                                                                                |

| Output enable/disable       | Controlled through the software on all data output signals and control signals collectively. When disabled, the output signals go to a high-impedance state. |

| Maximum output overload     | -0.3 V to +3.9 V                                                                                                                                             |

### Input Signals (DDC CLK IN and PFI <2..3>)

| Signal type                  | Low-voltage differential signal (LVDS) |

|------------------------------|----------------------------------------|

| Input differential impedance | 100 Ω                                  |

| Maximum output overload    | -0.3 V to +3.9 V |

|----------------------------|------------------|

| Differential input voltage | 0.1 V, minimum   |

|                            | 0.5 V, maximum   |

| Input common mode voltage  | 0.2 V, minimum   |

|                            | 2.2 V, maximum   |

#### DDC CLK OUT

| Clocking format | Data outputs and markers change on the falling edge of DDC CLK OUT. |

|-----------------|---------------------------------------------------------------------|

| Frequency range | Refer to the <u>Sample Clock</u> section for more information.      |

| Duty cycle      | 40% to 60%                                                          |

| Jitter          | 40 ps rms                                                           |

#### **DDC CLK IN**

| Clocking format            | DDC data output signals change on the rising edge of DDC CLK IN. |

|----------------------------|------------------------------------------------------------------|

| Frequency range            | 10 Hz to 105 MHz                                                 |

| Input duty cycle tolerance | 40% to 60%                                                       |

| Input jitter tolerances    | 300 ps pk-pk of cycle-cycle jitter                               |

| 1 ns rms of period jitter |

|---------------------------|

|                           |

### **Start Trigger**

| PFI<01> (SMB front panel connectors)                               |

|--------------------------------------------------------------------|

| PFI<23> (DIGITAL DATA & CONTROL front panel connector)             |

| PXI_Trig<07> (backplane connector)                                 |

| PXI Star Trigger (backplane connector)                             |

| Software (use node or function call)                               |

| Immediate (does not wait for a trigger). The default is Immediate. |

| Single                                                             |

| Continuous                                                         |

| Stepped                                                            |

| Burst                                                              |

| Rising                                                             |

| 25 ns                                                              |

| t                                                                  |

| 43 Sample Clock periods + 110 ns, typical                          |

| 57 Sample Clock periods + 110 ns, typical                          |

|                                                                    |

| Interpolation factor of 4              | 63 Sample Clock periods + 110 ns, typical                                                                                                     |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Interpolation factor of 8              | 64 Sample Clock periods + 110 ns, typical                                                                                                     |

| Delay from Start Trigger to DDC output | 40 Sample Clock periods + 110 ns                                                                                                              |

| Exported trigger destinations          | A signal used as a trigger can be routed out to any destination listed in the <b>Destinations</b> specification of the <u>Markers</u> section |

| Exported trigger delay                 | 65 ns, typical                                                                                                                                |

| Exported trigger pulse width           | >150 ns                                                                                                                                       |

### Markers

| Destinations                       | PFI <01> (SMB front panel connectors)  PFI <45> (DIGITAL DATA & CONTROL front panel connector)  PXI_Trig <06> (backpane connector) |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Quantity                           | One marker per segment                                                                                                             |

| Quantum                            | Marker position must be placed at an integer multiple of four samples.                                                             |

| Width                              | >150 ns                                                                                                                            |

| Skew with respect to analog output |                                                                                                                                    |

| PFI <01>                           | ±2 Sample Clock periods                                                                                                            |

|                                    |                                                                                                                                    |

| PXI_Trig <06>                            | ±2 Sample Clock periods |

|------------------------------------------|-------------------------|

| Skew with respect to digital data output |                         |

| PFI <45>                                 | <2 ns                   |

| Jitter                                   | 20 ps rms               |

### **Arbitrary Waveform Generation Mode**

| Memory usage        | The PXI-5421 uses the Synchronization and Memory Core (SMC) technology in which waveforms and instructions share onboard memory. Parameters—such as number of segments in sequence list, maximum number of waveforms in memory, and number of samples available for waveform storage—are flexible and user-defined. |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Onboard memory size |                                                                                                                                                                                                                                                                                                                     |

| 8 MB standard       | 8,388,608 bytes                                                                                                                                                                                                                                                                                                     |

| 32 MB option        | 33,554,432 bytes                                                                                                                                                                                                                                                                                                    |

| 256 MB option       | 268,435,456 bytes                                                                                                                                                                                                                                                                                                   |

| 512 MB option       | 536,870,912 bytes                                                                                                                                                                                                                                                                                                   |

| Output modes        | Arbitrary waveform  Arbitrary sequence                                                                                                                                                                                                                                                                              |

Table 12. Minimum Waveform Size

| Trigger Mode | Minimum Waveform S | Minimum Waveform Size (Samples)     |                        |

|--------------|--------------------|-------------------------------------|------------------------|

|              | Arbitrary Waveform | Arbitrary Sequence Mod              | de                     |

|              | Mode               | At >50 MS/s                         | At ≤50 MS/s            |

| Single       | 16                 |                                     |                        |

| Continuous   | 16 samples         | 96 samples at >50 MS/s              | 32 samples at ≤50 MS/s |

| Stepped      |                    |                                     |                        |

| Burst        |                    |                                     |                        |

| Loop count   |                    | 1 to 16,777,215                     |                        |

|              |                    | Burst trigger: Unlimited            |                        |

| Quantum      |                    | Waveform size must be four samples. | an integer multiple of |

### **Memory Limits**

Table 13. Maximum Waveform Memory

| Onboard Memory | Maximum Waveform Memory (Samples) |                         |

|----------------|-----------------------------------|-------------------------|

|                | Arbitrary Waveform Mode           | Arbitrary Sequence Mode |

| 8 MB standard  | 4,194,176                         | 4,194,120               |

| 32 MB option   | 16,777,088                        | 16,777,008              |

| 256 MB option  | 134,217,600                       | 134,217,520             |

| 512 MB option  | 268,435,328                       | 268,435,200             |

**Table 14.** Maximum Waveforms in Arbitrary Sequence Mode

| Onboard Memory | Maximum Waveforms     |

|----------------|-----------------------|

|                | 65,000                |

|                | Burst trigger: 8,000  |

| 32 MB option   | 262,000               |

|                | Burst trigger: 32,000 |

| Onboard Memory | Maximum Waveforms      |

|----------------|------------------------|

| ·              | 2,097,000              |

|                | Burst trigger: 262,000 |

| 512 MB option  | 4,194,000              |

|                | Burst trigger: 524,000 |

Table 15. Maximum Segments in a Sequence in Arbitrary Sequence Mode

| Onboard Memory | Maximum Segments in a Sequence |

|----------------|--------------------------------|

| 8 MB standard  | 104,000                        |

|                | Burst trigger: 65,000          |

| 32 MB option   | 418,000                        |

|                | Burst trigger: 262,000         |

| 256 MB option  | 3,354,000                      |

|                | Burst trigger: 2,090,000       |

| 512 MB option  | 6,708,000                      |

|                | Burst trigger: 4,180,000       |

### Calibration

| Self-calibration     | An onboard, 24-bit ADC and precision voltage reference are used to calibrate the DC gain and offset. The self-calibration is initiated by the user through the software and takes approximately 75 seconds to complete. |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External calibration | External calibration calibrates the VCXO, voltage reference, DC gain, and offset. Appropriate constants are stored in nonvolatile memory.                                                                               |

| Calibration interval | Specifications valid within two years of external calibration.                                                                                                                                                          |

| Warm-up time         | 15 minutes                                                                                                                                                                                                              |

#### **Power**

All values are typical. Overload operation occurs when CH 0 is shorted to ground.

| +3.3 VDC           |        |  |

|--------------------|--------|--|

| Typical operation  | 1.9 A  |  |

| Overload operation | 2.7 A  |  |

| +5 VDC             |        |  |

| Typical operation  | 2.0 A  |  |

| Overload operation | 2.2 A  |  |

| +12 VDC            | 1      |  |

| Typical operation  | 0.46 A |  |

| Overload operation | 0.5 A  |  |

| -12 VDC            |        |  |

| Typical operation  | 0.01 A |  |

| Overload operation | 0.01 A |  |

| Total power        |        |  |

| Typical operation  | 21.9 W |  |

| Overload operation | 26.0 W |  |

#### **Environment**

| Maximum altitude | 2,000 m (at 25 °C ambient temperature) |

|------------------|----------------------------------------|

|                  |                                        |

| Pollution Degree | 2 |

|------------------|---|

|                  |   |

Indoor use only.

### **Operating Environment**

| Ambient temperature range | 0 °C to 55 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.)                                                   |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                           | 0 °C to 45 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.) when installed in a PXI-101x or PXI-1000B chassis |

| Relative humidity range   | 10% to 90%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                                        |

### **Storage Environment**

| Ambient temperature range | -25 °C to 85 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.) |

|---------------------------|------------------------------------------------------------------------------|

| Relative humidity range   | 5% to 95%, noncondensing (Tested in accordance with IEC 60068-2-56.)         |

### **Shock and Vibration**

| Shock     |                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Operating | 30 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Test profile developed in accordance with MIL-PRF-28800F.) |

|           |                                                                                                                                         |

| Storage          | 50 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Test profile developed in accordance with MIL-PRF-28800F.)             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Random vibration |                                                                                                                                                     |

| Operating        | 5 Hz to 500 Hz, 0.31 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64.)                                                                   |

| Nonoperating     | 5 Hz to 500 Hz, 2.46 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64. Test profile exceeds the requirements of MIL-PRF-28800F, Class 3.) |

#### **Physical**

| Dimensions | 3U, one-slot, PXI/cPCI module                            |

|------------|----------------------------------------------------------|

|            | 21.6 cm × 2.0 cm × 13.0 cm (8.5 in. × 0.8 in. × 5.1 in.) |

| Weight     | 345 g (12.1 oz)                                          |

# **Compliance and Certifications**

#### **Safety Compliance Standards**

This product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:

- IEC 61010-1, EN 61010-1

- UL 61010-1, CSA C22.2 No. 61010-1

**Note** For safety certifications, refer to the product label or the <u>Product</u> Certifications and Declarations section.

#### **Electromagnetic Compatibility**

This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:

- EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity

- EN 55011 (CISPR 11): Group 1, Class A emissions

- EN 55022 (CISPR 22): Class A emissions

- EN 55024 (CISPR 24): Immunity

- AS/NZS CISPR 11: Group 1, Class A emissions

- AS/NZS CISPR 22: Class A emissions

- FCC 47 CFR Part 15B: Class A emissions

- ICES-001: Class A emissions

**Note** In the United States (per FCC 47 CFR), Class A equipment is intended for use in commercial, light-industrial, and heavy-industrial locations. In Europe, Canada, Australia, and New Zealand (per CISPR 11), Class A equipment is intended for use only in heavy-industrial locations.

**Note** Group 1 equipment (per CISPR 11) is any industrial, scientific, or medical equipment that does not intentionally generate radio frequency energy for the treatment of material or inspection/analysis purposes.

**Note** For EMC declarations, certifications, and additional information, refer to the <u>Product Certifications and Declarations</u> section.

#### **Product Certifications and Declarations**

Refer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for NI products, visit <a href="mailto:ni.com/product-certifications">ni.com/product-certifications</a>, search by model number, and click the appropriate link.

#### **Environmental Management**

NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.

For additional environmental information, refer to the **Engineering a Healthy Planet** web page at <u>ni.com/environment</u>. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.

#### **EU and UK Customers**

• 🕱 Waste Electrical and Electronic Equipment (WEEE)—At the end of the product life cycle, all NI products must be disposed of according to local laws and regulations. For more information about how to recycle NI products in your region, visit <u>ni.com/environment/weee</u>.

电子信息产品污染控制管理办法(中国 RoHS)

• ◎ ◎ ● 中国 RoHS— NI 符合中国电子信息产品中限制使用某些有害物质 指令(RoHS)。关于 NI 中国 RoHS 合规性信息,请登录 ni.com/environment/ rohs\_china。 (For information about China RoHS compliance, go to ni.com/ environment/rohs china.)