## Kria K24 SOM Data Sheet

DS985 (v1.0) September 19, 2023

**Preliminary Product Specification**

### **Overview**

## **Module Description**

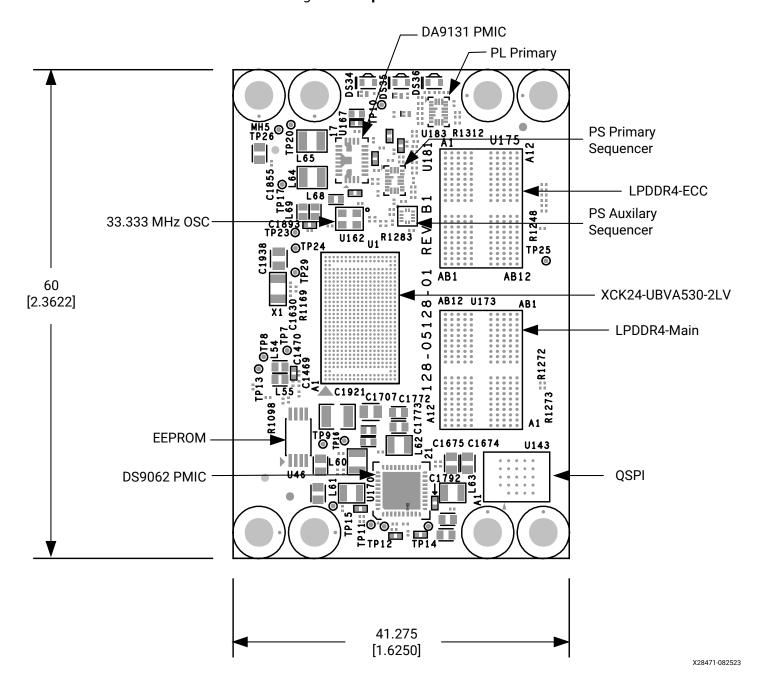

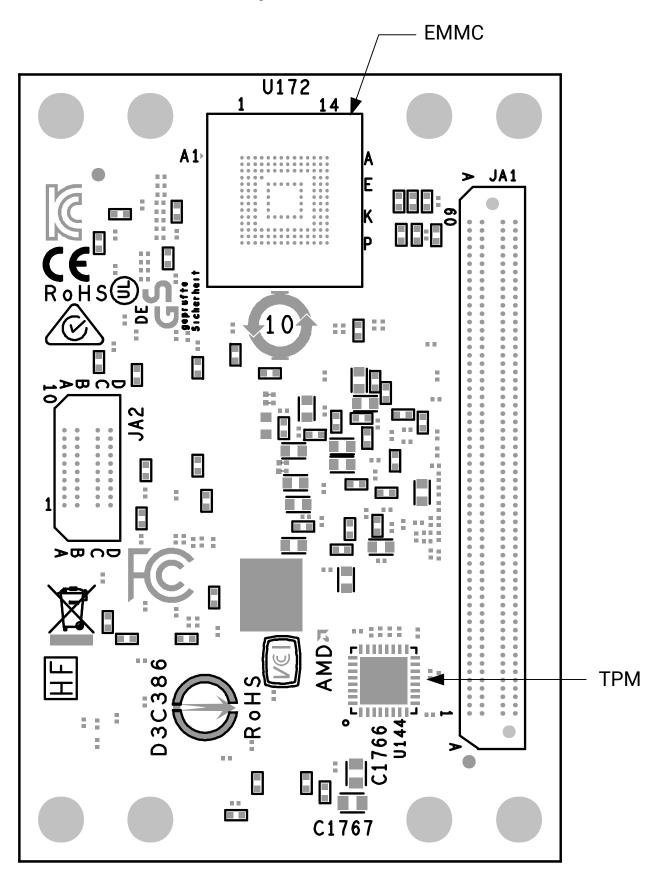

The AMD Kria™ K24 system-on-module (SOM) is a compact embedded platform that integrates a custom-built AMD Zynq™ UltraScale+™ MPSoC that runs optimally (and exclusively) on the K24 SOM with LPDDR4 memory, nonvolatile storage devices, a security module, and an aluminum thermal heat enclosure. The SOM is designed to be plugged into a carrier card with solution-specific peripherals. Key target applications include motor control, industrial communications and robotics, among many others. The following figure shows the top-side and bottom-side connector view.

Figure 1: K24 SOM

X27912-032223

## **Ordering Information**

**Table 1: Ordering Information**

| Part Number   | Device  | Temperature Grade | ECC for LPDDR4 | Description |

|---------------|---------|-------------------|----------------|-------------|

| SM-K24-XCL2GC | XCK24-C | Commercial        | No ECC         | K24C SOM    |

| SM-K24-XCL2GI | XCK24-I | Industrial        | With ECC       | K24I SOM    |

AMD Adaptive Computing is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this link for more information.

# **Functional Overview and Block Diagram**

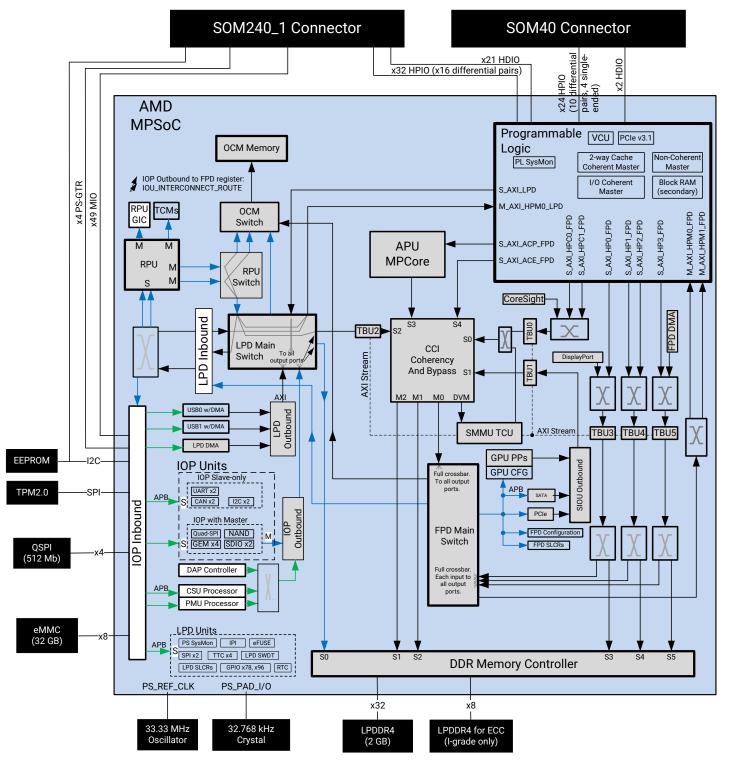

The K24 SOM leverages the XCK24-UBVA530-2LV-C/XCK24-UBVA530-2LV-I, a custom-built Zynq UltraScale+MPSoC that runs optimally (and exclusively) on the SOM. It provides an embedded processing system (PS) with tightly integrated programmable logic and a rich set of configurable I/O capabilities. The SOM hardware features include:

- Zynq UltraScale+ MPSoC (XCK24 in commercial (C) grade or industrial (I) grade)

- 2 GB 32-bit wide, 1066 Mb/s LPDDR4 memory, ECC support for I grade, no ECC support for C grade

- Integrated non-volatile memory devices

- 。 512 Mb QSPI

- 。 32 GB eMMC

- 64 Kb EEPROM

- TPM2.0 security module

- One 240-pin connector and one 40-pin connector with access to user-configurable I/O. The 240-pin connector is backward compatible to the K26 SOM 240\_1 connector:

- 。 PS MIO

- PS-GTR transceivers

- PS I2C platform control bus

- PL HPIO

- PL HDIO

- Sideband platform signals

- Power and power sequencing signals

- Integrated and flexible power design

- SOC power supplies derived from a single +5V input

- PL I/O supplies customized through carrier card defined power rails

- Compact mechanical size with integrated thermal interface plate

The following sections provide a more detailed description of:

- Functional interfaces and input/output

- MPSoC processing system (PS)

- MPSoC programmable logic (PL)

- Boot sources and storage devices

- Security features and module

Figure 2: K24 SOM Block Diagram

X27906-050823

### **Functional Interfaces**

The K24 SOM provides a combination of fixed and user-defined functional interfaces. Each interface is implemented with one of the major systems within the MPSoC. The following table is a summary of the interfaces, and system association (PS or PL), with a description of their use.

**Table 2: Interfaces Summary**

| Interface                | Physical Location                      | Linked<br>Subsystem | Functional Description                                                                                     |  |

|--------------------------|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|--|

| QSPI                     | MIO bank 500<br>MIO[5:0]               | PS                  | SOM QSPI memory                                                                                            |  |

| SD                       | MIO bank 500<br>MIO[23:13]             | PS                  | SOM eMMC memory, MIO[22:13] = eMMC, MIO[23] = eMMC reset                                                   |  |

| I2C                      | MIO bank 500<br>MIO[25:24]             | PS                  | SOM power management, EEPROM, and carrier card extensible I2C bus                                          |  |

| SPI                      | MIO bank 500<br>MIO[11:9], MIO[6]      | PS                  | Isolated SPI interface for TPM 2.0 security module                                                         |  |

| Power management         | MIO bank 501<br>MIO[34:32]             | PS                  | Fixed PMU SOM based power management                                                                       |  |

| Power management         | MIO bank 501<br>MIO[31], MIO[35]       | PS                  | MIO35_PMU_GPO and MIO31_PMU_GPI: Optional PMU I/O signals for use by a carrier card designer               |  |

| MIO – user defined I/O   | MIO bank 501<br>MIO[30:26], MIO[51:38] | PS                  | 19 user-defined multiplexed CPU connected I/O pins                                                         |  |

| MIO – user defined I/O   | MIO Bank 502<br>MIO[77:52]             | PS                  | 26 user-defined multiplexed CPU connected I/O pins                                                         |  |

| LPDDR4 memory controller | MIO bank 504                           | PS                  | SOM LPDDR4 memory                                                                                          |  |

| HDA                      | HDIO bank 26                           | PL                  | 24 pins total, 23 available user-defined high-density input/output pins                                    |  |

| НРА                      | HPIO bank 66                           | PL                  | User-defined high-performance input/output pins, 18 differential pin pairs and one single-ended pin        |  |

| НРА                      | HPIO bank 65                           | PL                  | User-defined high-performance input/output pins, eight differential pin pairs, and three single-ended pins |  |

| PS-GTR transceivers      | PS GTR 505                             | PS                  | Four lanes of user-defined high-speed serial transceivers                                                  |  |

The K24 SOM provides a large number of flexible user-defined I/O that can be configured for various I/O standards and voltage levels. Voltage levels for each HDIO and HPIO bank can be customized by the SOM carrier card design to provide the application-required voltage rails to the corresponding I/O banks. See the Supported I/O Standards section for the I/O voltage rail pin definitions and corresponding decoupling requirements.

The K24 SOM provides PS-GTR transceivers to implement various high-speed protocols. The supported protocols are listed in the protocol tables of the Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925), and are described in the Zynq UltraScale+ Device Technical Reference Manual (UG1085) and Zynq UltraScale+ MPSoC: Software Developers Guide (UG1137). The transceivers are configured via the AMD Vivado™ Design Suite.

## **Processing System**

This section outlines the processing system (PS) resources. It includes:

- APU: Arm® Cortex®-A53 based application processing unit (APU) consisting of quad-core Cortex-A53 processors with an  $F_{MAX}$  = 1333 MHz, L2 cache, SIMD, VFP4 floating point, and cryptography extensions.

- **RPU:** Arm Cortex-R5F based real-time processing unit (RPU) consisting of dual-core Cortex-R5F processors with floating point unit support with an  $F_{MAX}$  = 533 MHz, able to operate in stand-alone and lock-step functions.

- PMU: Platform management unit for dedicated SOM power and subsystem management functions.

- **Dynamic memory controller (DDRC):** DDR memory controller with configurable quality-of-service configuration capabilities.

- GPU: Arm Mali<sup>™</sup>-400 MP2 based graphics processing unit with an F<sub>MAX</sub> = 600 MHz.

- **System Monitor:** Built-in analog-digital-converter (ADC) with threshold checks for monitoring and reporting power supply and temperature conditions.

- RTC: Real-time clock for maintaining an accurate time base with optional battery backup through a carrier card pin.

The PS provides access to a number of integrated peripherals through multiplexed input/output (MIO) banks. The MPSoC has a total of three MIO banks. The SOM uses the first bank for the on-board peripherals, while the other two MIO banks are customizable and available through the SOM connector interface. All three MIO banks are powered by the SOM with a 1.8V power rail.

Refer to the MIO Interfaces table in the Zynq UltraScale+ Device Technical Reference Manual (UG1085) for more information on MIO usage for Zynq UltraScale+ MPSoCs. MIO mapping must comply with the Zynq UltraScale+ MPSoC design constraints and requirements.

## **MIO Banks**

For MIO assignment, refer to the MIO Table at a Glance in Zynq UltraScale+ Device Technical Reference Manual (UG1085) for complete constraints.

Table 3: MIO Banks

|          | MIO Banks |          |              |         |          |                        |                       |                      |                      |                        |                  |                   |                      |

|----------|-----------|----------|--------------|---------|----------|------------------------|-----------------------|----------------------|----------------------|------------------------|------------------|-------------------|----------------------|

| Bank 500 | 0         | 1        | 2            | 3       | 4        | 5                      | 6                     | 7                    | 8                    | 9                      | 10               | 11                | 12                   |

|          |           |          | C            | QSPI    | -        |                        | SPI1                  | GF                   | PIO0                 |                        | SPI1             |                   | GPIO0 <sup>1.a</sup> |

|          | sclk_out  | miso_mo1 | mo2          | mo3     | mosi_mi0 | n_ss_out               | sclk_out              | LED_DS35             | LED_DS36             | n_ss_out               | miso             | mosi              | FW_UEn               |

|          | 13        | 14       | 15           | 16      | 17       | 18                     | 19                    | 20                   | 21                   | 22                     | 23               | 24                | 25                   |

|          |           |          |              |         | eN       | MMC (SD0)              |                       |                      | -                    | -                      | GPIO0            | ]                 | 2C1                  |

|          | data[0]   | data[1]  | data[2]      | data[3] | data[4]  | data[5]                | data[6]               | data[7]              | cmd_out              | clk_out                | eMMC_Rst         | scl               | sda                  |

| Bank 501 | 26        | 27       | 28           | 29      | 30       | 31                     | 32                    | 33                   | 34                   | 35                     | 36               | 37                | 38                   |

|          |           |          | User Defined | d       |          | PMU_GPI <sup>1.b</sup> | Reserved <sup>2</sup> | PMU_GPO <sup>2</sup> | PMU_GPO <sup>2</sup> | PMU_GPO <sup>1.c</sup> | UAR <sup>*</sup> | Γ1 <sup>1.d</sup> | User Defined         |

|          |           |          |              |         |          | MIO31_PMU<br>_GPI      |                       | PL_Pwr_EN            | PS_Pwr_En            | MIO35_PMU<br>_GPO      | txd              | rxd               |                      |

|          | 39        | 40       | 41           | 42      | 43       | 44                     | 45                    | 46                   | 47                   | 48                     | 49               | 50                | 51                   |

|          |           |          |              |         |          |                        | User Defir            | ied                  |                      |                        |                  |                   |                      |

|          |           |          |              |         |          |                        |                       |                      |                      |                        |                  |                   |                      |

### Table 3: MIO Banks (cont'd)

|          | MIO Banks                              |    |    |    |    |    |    |    |    |    |    |    |    |

|----------|----------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|

| Bank 502 | 52 53 54 55 56 57 58 59 60 61 62 63 64 |    |    |    |    |    |    |    |    | 64 |    |    |    |

|          | User Defined                           |    |    |    |    |    |    |    |    |    |    |    |    |

|          |                                        |    |    |    |    |    |    |    |    |    |    |    |    |

|          | 65                                     | 66 | 67 | 68 | 69 | 70 | 71 | 72 | 73 | 74 | 75 | 76 | 77 |

|          | User Defined                           |    |    |    |    |    |    |    |    |    |    |    |    |

|          |                                        |    |    |    |    |    |    |    |    |    |    |    |    |

#### Notes:

- 1. AMD carrier cards, their reference designs and software stacks use some MIO pins for special purposes as listed by pin. They are used in the released Linux image, image selector, image recovery, PMU firmware, and other firmware applications. Custom designs can choose to align the MIO pins to these optional default assignments to adopt these software features with minimal customization.

- a. MIO12 is the firmware update enable pin

- b. MIO31 is the hardware driven pin that is used as an input to the PMU, it can be mapped to PMU functionality (e.g., shutdown)

- c. MIO35 is the PMU driven pin that can be mapped to PMU functionality (e.g., watchdog or reset)

- d. MIO36 and MIO37 are the default Linux console interface pins

- 2. MIO32, MIO33, and MIO34 are reserved for the PMU. These pins are fixed in the SOM hardware design. The K24 SOM only implements MIO33 and MIO34.

## **MIO Peripherals**

A number of peripherals are available within the MIO. The following is a summary of the interfaces that can be configured for your applications.

- **PS-GTR transceivers (x4):** Four dedicated PS-GTR receivers and transmitters with up to 6.0 Gb/s data rates supporting SGMII, tri-speed Ethernet, PCI Express® Gen2, serial ATA (SATA), USB3.0, and DisplayPort

- **Gigabit Ethernet MAC (GEM):** Four 10/100/1000 tri-speed GEM peripherals with IEEE Std 802.3 and IEEE Std 1588 revision 2.0 support

- **DisplayPort controller:** Provides a flexible display output with direct memory access (DMA), centralized buffer manager, rendering block, and audio mixer block.

- CAN controller: Two full CAN 2.0B, CAN 2.0A, and ISO 118981-1 standards compliant CAN bus interfaces.

- USB controller: Two USB 3.0/2.0 device, host, or OTG peripherals, each supporting up to 12 endpoints.

- PCI Express controller: Compliant with the PCI Express base specification 2.1 with support for x1, x2, or x4 line width at Gen1 (2.5 GT/s) or Gen2 (5 GT/s) rates.

- **SD/SDIO/eMMC controller:** One SD 3.00, SDIO 3.0, and eMMC4.51 compliant controller can be used as a carrier card peripheral from MIO[22:13], the other eMMC controller is reserved for the eMMC on the SOM.

- UART controller: Zyng UltraScale+ MPSoC provides two high-speed UART controllers (up to 1 Mb/s).

- **SPI controller:** One SPI port is reserved for the trusted platform module on the SOM and one full-duplex SPI port (with three peripheral chip selects) is available for the carrier card peripheral.

- **SATA Host controller:** Supports up to two channels at 1.5, 3.0, and 6.0 Gb/s data rates as defined by the SATA specification, revision 3.1

- I2C controller: Master and slave I2C interface with support for multi-master designs and clock rates up to 400 Kb/s.

### **I2C Bus Interface**

The PS hosts the SOM I2C platform management bus for interfacing with supporting SOM peripherals. These devices are summarized in the following table. The PS I2C bus interface can be extended on a carrier card, but must not introduce address conflicts. The following table defines the K24 SOM I2C device addresses in 7-bit format.

Table 4: SOM I2C Interface Addresses

| I2C 7-bit Address | Description                                             |

|-------------------|---------------------------------------------------------|

| 0x50, 0x58        | SOM EEPROM                                              |

| 0x51, 0x59        | SOM240_1 connector, intended for EEPROM on carrier card |

| 0x30, 0x31        | DA9062 PMIC                                             |

| 0x33              | DA9131 PMIC                                             |

| 0x68              | PL power domain monitor                                 |

| 0×70              | PS power domain monitor                                 |

## **Programmable Logic**

The K24 SOM includes a custom-built Zynq UltraScale+ MPSoC (XCK24), that runs optimally (and exclusively) on the K24 SOM and includes a flexible and extensible programmable logic system (PL). The PL resources are summarized in the following table.

Table 5: PL Resources

| Resource             | K24 SOM | Description                                                         |

|----------------------|---------|---------------------------------------------------------------------|

| System logic cells   | 154,350 | Programmable logic cells for available                              |

| CLB flip-flops       | 141,120 | Configurable logic block (CLB): Total number of flip-flops          |

| CLB LUTs             | 70,560  | Configurable logic block: Total number of look-up tables            |

| Distributed RAM (Mb) | 1.8     | Distributed memory                                                  |

| Block RAM            | 216     | Number of 36 Kb block RAMs                                          |

| Block RAM (Mb)       | 7.6     | Total block RAM memory footprint                                    |

| UltraRAM blocks      | 0       | 288 Kb dual-port, 72-bit-wide memory with error correction          |

| DSP slices           | 360     | 27 x 18 signed multiplier with 48-bit adder/accumulator             |

| Video Codec          | 0       | H.264 and H.265 supported simultaneous encode/decode                |

| HDIO                 | 23      | High-density I/O supports 1.2V to 3.3V rails                        |

| HPIO                 | 56      | High-performance I/O differential pairs supports 1.0V to 1.8V rails |

### **Boot Sources and Storage Devices**

The K24 SOM includes two nonvolatile storage boot devices, a QSPI flash memory, and an eMMC flash memory. The primary boot device is selected by tying the MODE[3:0] pins to the desired value on your carrier card. The boot-mode pins are made available at the SOM connector to allow flexibility in defining the boot device. The boot-mode configurations for using QSPI or eMMC are shown in the following table. Other boot-mode options can be introduced based on your carrier card design. See the Zynq UltraScale+ Device Technical Reference Manual (UG1085) for the full set of boot-mode definitions. Reference the Kria SOM Carrier Card Design Guide (UG1091) for details on strapping the boot-mode resistors.

Table 6: Boot Mode Pins and Location

| Boot Mode         | PS_Mode Pins[3:0] | Physical Pin Location |  |

|-------------------|-------------------|-----------------------|--|

| Quad-SPI (32 bit) | 0010              | MIO[5:0]              |  |

| еММС              | 0110              | MIO[22:13]            |  |

The K24 SOM provides two storage devices to enable a primary/secondary boot process with isolation between boot firmware and operating system (OS) storage, or similar device firmware segmentation. As an example of a supported hierarchical boot process, the SOM boot mode can be set to QSPI as the primary boot device, which contains the power-on boot firmware, and then the power-on boot loader (e.g., U-Boot) loads the OS from the eMMC secondary boot device.

## **Security Features**

The K24 SOM provides two levels of security with dedicated hardware built into the MPSoC and an on-board trusted platform module (TPM) device. Together they enable implementation of tamper monitoring, secure boot, measured boot, and hardware accelerated cryptographic functions.

The K24 SOM includes the following security features:

- Encryption and authentication of configuration files

- Hardened crypto-accelerators available for user applications

- Secure methods for storing cryptographic keys via eFUSEs

- Methods for detecting and responding to device tamper events

MPSoCs have a dedicated configuration security unit (CSU), which is used for supporting secure boot, tamper monitoring, secure key storage, and cryptographic hardware acceleration. See the *Security* chapter in the *Zynq UltraScale+ Device Technical Reference Manual* (UG1085) for implementation details. The cryptographic accelerators available on the MPSoC are as follows:

- SHA-3/384

- AES-GCM-256

- RSA exponential multiplier

The CSU, an internal on-chip memory (OCM), and flexible key storage provide hardware root of trust mechanisms for implementing secure boot within the MPSoC. The hardware capabilities support authenticated and encrypted protections for boot and associated configuration files.

After ensuring the initial boot integrity of the device, the CSU then acts as a centralized tamper monitoring and response controller using the MPSoC integrated system monitor (SYSMON) for measuring and implementing voltage and temperature alarms and configurations. Various alarms and set points can be configured as defined in the Zynq UltraScale+ Device Technical Reference Manual (UG1085).

The MPSoC includes a key management infrastructure supporting battery-backed RAM (BBRAM), eFUSE, embedded boot keys, and device family keys. When BBRAM is required, battery backup must be provided on the carrier card. Additional details on the key management functions of the MPSoC are outlined in the *Zynq UltraScale+ Device Technical Reference Manual* (UG1085).

The MPSoC contains a 96-bit unique, nonvolatile device identifier called the device DNA that is permanently programmed in the MPSoC. The SOM EEPROM also contains a unique identifier (UID), programmed at the time of SOM manufacturing. These unique identifiers support the implementation over-the-air (OTA) device enrollment and attestation functionality.

The MPSoC eFUSEs allow permanent enable or disable of specific features to protect deployed systems. A complete list of these capabilities is outlined in the *Zynq UltraScale+ Device Technical Reference Manual* (UG1085). Two commonly used features are:

- RSA\_EN: Forces every device boot to be authenticated via RSA

- JTAG\_DIS: Disables JTAG

In addition to the MPSoC security features, the SOM has an Infineon OPTIGA TPM device that is compliant with the trusted computing group (TCG) TPM 2.0 standard. This TPM 2.0 device enables hardware-based security for remote attestation, measured boot, and other secure cryptographic functions. The TPM reset is connected to the PS\_POR\_L pin. AMD does not preload the TPM, it only contains the Infineon factory-programmed endorsement key.

# **Electrical Specifications**

This section describes the electrical interfaces and connections available on the SOM to use with your carrier card design.

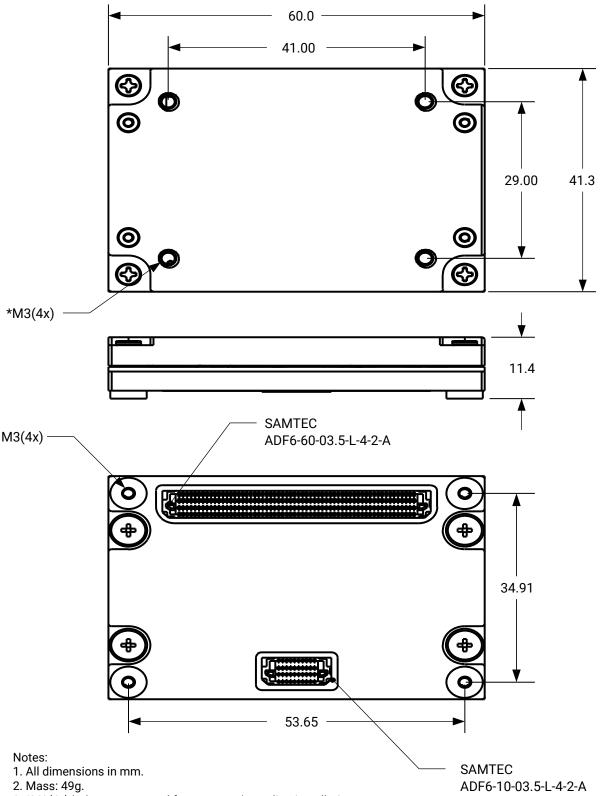

### **SOM Connector Overview**

The K24 SOM uses one 240-pin connectors and one 40-pin connector to provide electrical connectivity between the SOM and the carrier card. These two connectors are referred to as SOM240\_1 and SOM40. The SOM240\_1 connector is backward compatible with SOM240\_1 connector on the K26 SOM.

The SOM240\_1 connector uses the Samtec 0.635 mm AcceleRate HD high-density 4-row, 60 position connector set. The part number for the socket (ADF6-60-03.5-L-4-2-A) is used on the bottom side of the SOM. The part number for the terminal (ADM6-60-01.5-L-4-2-A) is for use on the carrier card.

The SOM40 connector uses the Samtec 0.635 mm AcceleRate (R) HD high-density 4-row, 10 position connector set. The part number for the socket (ADF6-10-03.5-L-4-2-A) is used on the bottom side of the SOM. The part number for the terminal (ADM6-10-01.5-L-4-2-A) is for use on the carrier card.

Note: Contact your Samtec distributor for more information.

The SOM240 1 and SOM40 connectors provide support for following interfaces.

- Control and status signals

- Multiplexed I/O (MIO) bank

- PS-GTR high-speed serial transceiver signals

- High-performance I/O (HPIO) bank signals

- High-density I/O (HDIO) bank signals

- Power system

# **Supported I/O Standards**

The K24 SOM supports all I/O standards supported by the respective bank that a signal is connected to with the exception of I/O standards that require a reference voltage ( $V_{REF}$ ). For more information, refer to the *UltraScale Architecture SelectIO Resources User Guide* (UG571).

During power-up and configuration, internal pull-up resistors are disabled and each SelectIO™ pin is set to tristate.

The K24 SOM is built with the XCK24-UBVA530-2LV device; which has a -2 speed grade and is an LV device (operates at  $V_{CCINT}$  = 0.72V). Consult the corresponding I/O speed tables in *Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics* (DS925) for the definition of maximum data rates.

### DCI—VRP Termination

The Kria SOM design leverages the AMD Zynq™ UltraScale+™ MPSoCs with InFO package (XCK24-UBVA530-2LV) for a physically smaller packaging and SOM size. This allows product development to reduce PCB size through internally controlling the impedance of I/O pins, removing the need for external termination resistors. DCI configuration is only used on HP I/O banks within the MPSoCs.

For more information on DCI, see the *UltraScale Architecture SelectIO Resources User Guide* (UG571), with specific attention to the *DCI—Only Available in the HP I/O Banks* and *VRP External Resistance Design Migration Guidelines* topics. The has two HP I/O banks. The following table defines the VRP configuration for each bank. The value of  $240\Omega$  was chosen based upon the previous references.

Table 7: VRP Resistor Selection

| Pin | Name              | Value |

|-----|-------------------|-------|

| M4  | IO_T0U_N12_VRP_65 | 240Ω  |

| E4  | IO_T0U_N12_VRP_66 | 240Ω  |

## **Signal Naming Conventions**

For signal to connector mapping in text format, see the relevant XDC and trace delay files. These files provide the AMD Zynq™ UltraScale+™ MPSoC constraints and package pin name to SOM240\_1 and SOM40 mapping. The SOM240 and SOM40 connectors adopt the naming conventions outlined in the following table.

**Table 8: Signal Naming Conventions**

| Signal           | Description                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module (M)       | The SOM, in this case the K24 SOM.                                                                                                                                                                 |

| Carrier card (C) | The board that the SOM is plugged into is called the carrier card.                                                                                                                                 |

| C2M              | Signal names with C2M indicate that the signal is driven by the carrier card and received by the SOM.                                                                                              |

| M2C              | Signal names with M2C indicate that the signal is driven by the SOM and received by the carrier card.                                                                                              |

| _P               | The postfix _P on differential signal pairs indicates the positive component of a differential signal. Used on SOM240.                                                                             |

| _N               | The postfix $_{-\mathbb{N}}$ on differential signal pairs indicates the negative component of a differential signal. Used on SOM240.                                                               |

| Р                | The postfix P on differential signal pairs indicates the positive component of a differential signal. Used on SOM40.                                                                               |

| N                | The postfix ${\tt N}$ on differential signal pairs indicates the negative component of a differential signal. Used on SOM40.                                                                       |

| _L or _B         | The postfix _L on a single-ended signal indicates an active-Low signal. This is used for the connector pinouts only. The postfix _B is also used to indicate an active-Low signal. Used on SOM240. |

**Table 9: Legend for Connector Pinouts**

| Example           | SOM240 Connector        | Function                       |

|-------------------|-------------------------|--------------------------------|

| GND               | Both SOM240_1 and SOM40 | Ground pins                    |

| VCC_SOM           | Both SOM240_1 and SOM40 | Power connection pins          |

| MIO35             | SOM240_1                | MIO 501 bank pins              |

| MIO58             | SOM240_1                | MIO 502 bank pins              |

| JTAG_TMS_C2M      | SOM240_1                | Configuration and control pins |

| GTR_DP1_M2C_P     | SOM240_1                | PS-GTR transceiver pins        |

| HPA06_P or HPA22P | SOM240_1 or SOM40       | HPA pins                       |

| HDA00_CC          | SOM240_1 and SOM40      | HDA pins                       |

Refer to the Zynq UltraScale+ Device Packaging and Pinouts Product Specification User Guide (UG1075) for more information on pin types.

**Table 10: Legend for Pin Types**

| Example  | Definition                                   |

|----------|----------------------------------------------|

| GC       | Global clock                                 |

| HDGC     | Global clock                                 |

| VRP      | DCI voltage reference resistor               |

| QBC      | Byte lane clock                              |

| DBC      | Byte lane clock                              |

| SMBA     | SMBAlert output                              |

| PU18_10  | 10.0 KΩ pull-up resistor to VCC_PS_1V80      |

| PU18_2p2 | 2.21 KΩ pull-up resistor to VCC_PS_1V80      |

| PU18_4p7 | 4.7 KΩ pull-up resistor to VCC_PS_1V80       |

| PU50     | 10.0 KΩ pull-up resistor to VCC_5V0          |

| PD50     | 49.9 KΩ pull-down resistor from VCC_5V0      |

| AC01UF   | AC coupled with 0.01 μF capacitor on the SOM |

## **SOM240\_1 Connector Pinout**

The SOM240\_1 connector provides access to two MIO banks (MIO501, MIO502), HPIO bank 65 (HPA), HDIO bank 26 (HDA), and the PS-GTR transceivers (MIO505). It also provides sideband signals for configuration and operation of the board. For additional pin definitions see the K24 SOM XDC file.

Table 11: SOM240\_1 Connector Pinout

| Connector<br>Row/Pin<br>Number | А        | В          | С          | D        |

|--------------------------------|----------|------------|------------|----------|

| 1                              | VCC_BATT | HPA05_CC_P | GND        | VCCO_HPA |

| 2                              | GND      | HPA05_CC_N | GND        | VCCO_HPA |

| 3                              | HPA06_P  | GND        | HPA00_CC_P | GND      |

| 4                              | HPA06_N  | HPA04_P    | HPA00_CC_N | HPA02_P  |

Table 11: SOM240\_1 Connector Pinout (cont'd)

| Connector<br>Row/Pin<br>Number | Α             | В                   | С                 | D             |

|--------------------------------|---------------|---------------------|-------------------|---------------|

| 5                              | GND           | HPA04_N             | GND               | HPA02_N       |

| 6                              | HPA_CLK0_P    | GND                 | HPA03_P           | GND           |

| 7                              | HPA_CLK0_N    | HPA07_P             | HPA03_N           | HPA01_P       |

| 8                              | GND           | HPA07_N             | GND               | HPA01_N       |

| 9                              | HPA12_P       | GND                 | HPA08_P           | GND           |

| 10                             | HPA12_N       | HPA11_P             | HPA08_N           | HPA09_P       |

| 11                             | GND           | HPA11_N             | GND               | HPA09_N       |

| 12                             | HPA13_P       | GND                 | HPA10_CC_P        | GND           |

| 13                             | HPA13_N       | VCCO_HDA            | HPA10_CC_N        | HPA14_P       |

| 14                             | GND           | VCCO_HDA            | GND               | HPA14_N       |

| 15                             | HDA09         | GND                 | PS_POR_L          | GND           |

| 16                             | HDA10         | HDA03               | PS_SRST_C2M_L     | HDA00_CC      |

| 17                             | HDA11         | HDA04               | GND               | HDA01         |

| 18                             | GND           | HDA05               | HDA06             | HDA02         |

| 19                             | VCCOEN_PS_M2C | GND                 | HDA07             | GND           |

| 20                             | VCCOEN_PL_M2C | HDA15               | HDA08_CC          | HDA12         |

| 21                             | GND           | HDA16_CC            | GND               | HDA13         |

| 22                             | JTAG_TMS_C2M  | HDA17               | HDA18             | HDA14         |

| 23                             | JTAG_TDO_M2C  | GND                 | HDA19             | GND           |

| 24                             | JTAG_TDI_C2M  | PS_ERROR_OUT_M2C    | HDA20             | PWRGD_FPD_M2C |

| 25                             | JTAG_TCK_C2M  | PS_ERROR_STATUS_M2C | GND               | PWRGD_LPD_M2C |

| 26                             | GND           | PWROFF_C2M_L        | MIO24_I2C_SCK     | PWRGD_PL_M2C  |

| 27                             | MODE0_C2M     | GND                 | MIO25_I2C_SDA     | GND           |

| 28                             | MODE1_C2M     | MIO35               | MIO12_FWUEN_C2M_L | MIO26         |

| 29                             | MODE2_C2M     | MIO36               | GND               | MIO27         |

| 30                             | MODE3_C2M     | MIO37               | MIO29             | MIO28         |

| 31                             | Reserved      | GND                 | MIO30             | GND           |

| 32                             | Reserved      | MIO38               | MIO31             | MIO44         |

| 33                             | GND           | MIO39               | GND               | MIO45         |

| 34                             | MIO41         | MIO40               | MIO47             | MIO46         |

| 35                             | MIO42         | GND                 | MIO48             | GND           |

| 36                             | MIO43         | MIO50               | MIO49             | MIO52         |

| 37                             | GND           | MIO51               | GND               | MIO53         |

| 38                             | MIO61         | Reserved            | MIO55             | MIO54         |

| 39                             | MIO62         | GND                 | MIO56             | GND           |

| 40                             | MIO63         | MIO58               | MIO57             | MIO64         |

| 41                             | GND           | MIO59               | GND               | MIO65         |

| 42                             | MIO73         | MIO60               | MIO67             | MIO66         |

| 43                             | MIO74         | GND                 | MIO68             | GND           |

| 44                             | MIO75         | MIO70               | MIO69             | MIO76         |

Table 11: SOM240\_1 Connector Pinout (cont'd)

| Connector<br>Row/Pin<br>Number | А                 | В                 | С                 | D                 |

|--------------------------------|-------------------|-------------------|-------------------|-------------------|

| 45                             | GND               | MIO71             | Reserved          | MIO77             |

| 46                             | GND               | MIO72             | GND               | Reserved          |

| 47                             | GTR_DP1_M2C_P     | GND               | GTR_REFCLK0_C2M_P | GND               |

| 48                             | GTR_DP1_M2C_N     | GND               | GTR_REFCLK0_C2M_N | GND               |

| 49                             | GND               | GTR_REFCLK1_C2M_P | GND               | GTR_DP3_C2M_P     |

| 50                             | GND               | GTR_REFCLK1_C2M_N | GND               | GTR_DP3_C2M_N     |

| 51                             | GTR_REFCLK3_C2M_P | GND               | GTR_DP3_M2C_P     | GND               |

| 52                             | GTR_REFCLK3_C2M_N | GND               | GTR_DP3_M2C_N     | GND               |

| 53                             | GND               | GTR_DP2_C2M_P     | GND               | GTR_REFCLK2_C2M_P |

| 54                             | GND               | GTR_DP2_C2M_N     | GND               | GTR_REFCLK2_C2M_N |

| 55                             | GTR_DP0_C2M_P     | GND               | GTR_DP1_C2M_P     | GND               |

| 56                             | GTR_DP0_C2M_N     | GND               | GTR_DP1_C2M_N     | GND               |

| 57                             | GND               | GTR_DP0_M2C_P     | GND               | GTR_DP2_M2C_P     |

| 58                             | GND               | GTR_DP0_M2C_N     | GND               | GTR_DP2_M2C_N     |

| 59                             | VCC_SOM           | GND               | VCC_SOM           | GND               |

| 60                             | VCC_SOM           | VCC_SOM           | VCC_SOM           | VCC_SOM           |

# **SOM240\_1 Signal Names and Descriptions**

See the Zynq UltraScale+ Device Packaging and Pinouts Product Specification User Guide (UG1075) for further pin descriptions.

Table 12: SOM240\_1 Signal Pins

| Pin Number | Pin Type        | Signal Name | Signal Description                                                                                                     |  |  |  |

|------------|-----------------|-------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

|            | Connector Row A |             |                                                                                                                        |  |  |  |

| A1         |                 | VCC_BATT    | PS BBRAM and real-time clock (RTC) supply voltage, requires external battery. Connect to GND when battery is not used. |  |  |  |

| A2         |                 | GND         | Ground, connect to carrier card ground plane                                                                           |  |  |  |

| A3         |                 | HPA06_P     | HPIO on bank 65                                                                                                        |  |  |  |

| A4         |                 | HPA06_N     | HPIO on bank 65                                                                                                        |  |  |  |

| A5         |                 | GND         | Ground, connect to carrier card ground plane                                                                           |  |  |  |

| A6         | GC              | HPA_CLK0_P  | HPIO global clock pin on bank 65                                                                                       |  |  |  |

| A7         | GC              | HPA_CLK0_N  | HPIO global clock pin on bank 65                                                                                       |  |  |  |

| A8         |                 | GND         | Ground, connect to carrier card ground plane                                                                           |  |  |  |

| A9         |                 | HPA12_P     | HPIO on bank 65                                                                                                        |  |  |  |

| A10        |                 | HPA12_N     | HPIO on bank 65                                                                                                        |  |  |  |

| A11        |                 | GND         | Ground, connect to carrier card ground plane                                                                           |  |  |  |

| A12        | QBC             | HPA13_P     | HPIO on bank 65                                                                                                        |  |  |  |

| A13        | QBC             | HPA13_N     | HPIO on bank 65                                                                                                        |  |  |  |

| A14        |                 | GND         | Ground, connect to carrier card ground plane                                                                           |  |  |  |

Table 12: SOM240\_1 Signal Pins (cont'd)

| lane<br>ripherals on the carrier card<br>ripherals on the carrier card<br>lane |

|--------------------------------------------------------------------------------|

| ripherals on the carrier card                                                  |

| ripherals on the carrier card                                                  |

| ripherals on the carrier card                                                  |

| ipherals on the carrier card                                                   |

| •                                                                              |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

|                                                                                |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

| lane                                                                           |

| lane                                                                           |

|                                                                                |

|                                                                                |

| lane                                                                           |

| lane                                                                           |

|                                                                                |

|                                                                                |

| lane                                                                           |

| lane                                                                           |

|                                                                                |

|                                                                                |

|                                                                                |

Table 12: SOM240\_1 Signal Pins (cont'd)

| Pin Number | Pin Type | Signal Name         | Signal Description                                                                                                  |

|------------|----------|---------------------|---------------------------------------------------------------------------------------------------------------------|

| A57        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| A58        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| A59        |          | VCC_SOM             | SOM main supply voltage, +5V                                                                                        |

| A60        |          | VCC_SOM             | SOM main supply voltage, +5V                                                                                        |

|            |          |                     | Connector Row B                                                                                                     |

| B1         | QBC      | HPA05_CC_P          | HPIO clock-capable pin on bank 65                                                                                   |

| B2         | QBC      | HPA05_CC_N          | HPIO clock-capable pin on bank 65                                                                                   |

| B3         |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B4         |          | HPA04_P             | HPIO on bank 65                                                                                                     |

| B5         |          | HPA04_N             | HPIO on bank 65                                                                                                     |

| В6         |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| В7         |          | HPA07_P             | HPIO on bank 65                                                                                                     |

| B8         |          | HPA07_N             | HPIO on bank 65                                                                                                     |

| В9         |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B10        | GC       | HPA11_P             | HPIO on bank 65                                                                                                     |

| B11        | GC       | HPA11_N             | HPIO on bank 65                                                                                                     |

| B12        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B13        |          | VCCO_HDA            | HDA I/O voltage rail, 1.2V to 3.3V                                                                                  |

| B14        |          | VCCO_HDA            | HDA I/O voltage rail, 1.2V to 3.3V                                                                                  |

| B15        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B16        |          | HDA03               | HDIO on bank 26                                                                                                     |

| B17        |          | HDA04               | HDIO on bank 26                                                                                                     |

| B18        |          | HDA05               | HDIO on bank 26                                                                                                     |

| B19        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B20        |          | HDA15               | HDIO on bank 26                                                                                                     |

| B21        | HDGC     | HDA16_CC            | HDIO clock-capable pin on bank 26                                                                                   |

| B22        | HDGC     | HDA17               | HDIO on bank 26                                                                                                     |

| B23        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B24        |          | PS_ERROR_OUT_M2C    | PS error indication from SOM                                                                                        |

| B25        |          | PS_ERROR_STATUS_M2C | PS error status from SOM                                                                                            |

| B26        | PU50     | PWROFF_C2M_L        | Control signal to turn off all power rails on the SOM                                                               |

| B27        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B28        |          | MIO35               | PS MIO signal on bank 501. Optional use as PMU output.                                                              |

| B29        |          | MIO36               | PS MIO signal on bank 501. Optional use as PMU output. Default use as UART TXD in the released Kria PetaLinux BSPs. |

| B30        |          | MIO37               | PS MIO signal on bank 501. Optional use as PMU output. Default use as UART RXD in the released Kria PetaLinux BSPs. |

| B31        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

| B32        |          | MIO38               | PS MIO signal on bank 501                                                                                           |

| B33        |          | MIO39               | PS MIO signal on bank 501                                                                                           |

| B34        |          | MIO40               | PS MIO signal on bank 501                                                                                           |

| B35        |          | GND                 | Ground, connect to carrier card ground plane                                                                        |

Table 12: SOM240\_1 Signal Pins (cont'd)

| Pin Number | Pin Type | Signal Name       | Signal Description                                                                             |

|------------|----------|-------------------|------------------------------------------------------------------------------------------------|

| B36        |          | MIO50             | PS MIO signal on bank 501                                                                      |

| B37        |          | MIO51             | PS MIO signal on bank 501                                                                      |

| B38        |          | Reserved          | Not connected to SOM connector                                                                 |

| B39        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B40        |          | MIO58             | PS MIO signal on bank 502                                                                      |

| B41        |          | MIO59             | PS MIO signal on bank 502                                                                      |

| B42        |          | MIO60             | PS MIO signal on bank 502                                                                      |

| B43        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B44        |          | MIO70             | PS MIO signal on bank 502                                                                      |

| B45        |          | MIO71             | PS MIO signal on bank 502                                                                      |

| B46        |          | MIO72             | PS MIO signal on bank 502                                                                      |

| B47        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B48        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B49        | AC01UF   | GTR_REFCLK1_C2M_P | PS-GTR REFCLK1 input, bank 505                                                                 |

| B50        | AC01UF   | GTR_REFCLK1_C2M_N | PS-GTR REFCLK1 input, bank 505                                                                 |

| B51        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B52        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B53        |          | GTR_DP2_C2M_P     | PS-GTR lane 2 RX, bank 505                                                                     |

| B54        |          | GTR_DP2_C2M_N     | PS-GTR lane 2 RX, bank 505                                                                     |

| B55        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B56        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B57        |          | GTR_DP0_M2C_P     | PS-GTR lane 0 TX, bank 505                                                                     |

| B58        |          | GTR_DP0_M2C_N     | PS-GTR lane 0 TX, bank 505                                                                     |

| B59        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| B60        |          | VCC_SOM           | SOM main supply voltage, +5V                                                                   |

| •          |          | •                 | Connector Row C                                                                                |

| C1         |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C2         |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C3         | DBC      | HPA00_CC_P        | HPIO clock-capable pin on bank 65                                                              |

| C4         | DBC      | HPA00_CC_N        | HPIO clock-capable pin on bank 65                                                              |

| C5         |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C6         | DBC      | HPA03_P           | HPIO on bank 65                                                                                |

| C7         | DBC      | HPA03_N           | HPIO on bank 65                                                                                |

| C8         |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C9         | QBC      | HPA08_P           | HPIO on bank 65                                                                                |

| C10        | QBC      | HPA08_N           | HPIO on bank 65                                                                                |

| C11        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C12        | GC, QBC  | HPA10_CC_P        | HPIO clock-capable pin on bank 65                                                              |

| C13        | GC, QBC  | HPA10_CC_N        | HPIO clock-capable pin on bank 65                                                              |

| C14        |          | GND               | Ground, connect to carrier card ground plane                                                   |

| C15        | PU18_4p7 | PS_POR_L          | PS power-on reset driven by the carrier card. When deasserted, the PS begins the boot process. |

Table 12: SOM240\_1 Signal Pins (cont'd)

| Pin Number | Pin Type | Signal Name       | Signal Description                                                                                                        |

|------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| C16        | PU18_4p7 | PS_SRST_C2M_L     | PS system reset driven by the carrier card. When asserted, forces the PS to enter the system reset sequence.              |

| C17        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C18        |          | HDA06             | HDIO on bank 26                                                                                                           |

| C19        |          | HDA07             | HDIO on bank 26                                                                                                           |

| C20        | HDGC     | HDA08_CC          | HDIO clock-capable pin on bank 26                                                                                         |

| C21        |          | GND               | Ground                                                                                                                    |

| C22        |          | HDA18             | HDIO on bank 26                                                                                                           |

| C23        |          | HDA19             | HDIO on bank 26                                                                                                           |

| C24        |          | HDA20             | HDIO on bank 26                                                                                                           |

| C25        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C26        | PU18_2p2 | MIO24_I2C_SCK     | PS I2C clock output, bank 500                                                                                             |

| C27        | PU18_2p2 | MIO25_I2C_SDA     | PS I2C serial data, bank 500                                                                                              |

| C28        | PU18_10  | MIO12_FWUEN_C2M_L | PS MIO signal on bank 500. Optional default use as firmware update enable indication in the released Kria PetaLinux BSPs. |

| C29        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C30        |          | MIO29             | PS MIO signal on bank 501. Optional use as PMU input.                                                                     |

| C31        |          | MIO30             | PS MIO signal on bank 501. Optional use as PMU input.                                                                     |

| C32        |          | MIO31             | PS MIO signal on bank 501. Optional use as PMU input.                                                                     |

| C33        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C34        |          | MIO47             | PS MIO signal on bank 501                                                                                                 |

| C35        |          | MIO48             | PS MIO signal on bank 501                                                                                                 |

| C36        |          | MIO49             | PS MIO signal on bank 501                                                                                                 |

| C37        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C38        |          | MIO55             | PS MIO signal on bank 502                                                                                                 |

| C39        |          | MIO56             | PS MIO signal on bank 502                                                                                                 |

| C40        |          | MIO57             | PS MIO signal on bank 502                                                                                                 |

| C41        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C42        |          | MIO67             | PS MIO signal on bank 502                                                                                                 |

| C43        |          | MIO68             | PS MIO signal on bank 502                                                                                                 |

| C44        |          | MIO69             | PS MIO signal on bank 502                                                                                                 |

| C45        |          | Reserved          | No connect on the SOM                                                                                                     |

| C46        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C47        | AC01UF   | GTR_REFCLK0_C2M_P | PS-GTR REFCLK0 input, bank 505                                                                                            |

| C48        | AC01UF   | GTR_REFCLK0_C2M_N | PS-GTR REFCLK0 input, bank 505                                                                                            |

| C49        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C50        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C51        |          | GTR_DP3_M2C_P     | PS-GTR lane 3 TX, bank 505                                                                                                |

| C52        |          | GTR_DP3_M2C_N     | PS-GTR lane 3 TX, bank 505                                                                                                |

| C53        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C54        |          | GND               | Ground, connect to carrier card ground plane                                                                              |

| C55        |          | GTR_DP1_C2M_P     | PS-GTR lane 1 RX, bank 505                                                                                                |

Table 12: SOM240\_1 Signal Pins (cont'd)

| Pin Number | Pin Type | Signal Name   | Signal Description                                    |  |

|------------|----------|---------------|-------------------------------------------------------|--|

| C56        |          | GTR_DP1_C2M_N | PS-GTR lane 1 RX, bank 505                            |  |

| C57        |          | GND           | Ground, connect to carrier card ground plane          |  |

| C58        |          | GND           | Ground, connect to carrier card ground plane          |  |

| C59        |          | VCC_SOM       | SOM main supply voltage, +5V                          |  |

| C60        |          | VCC_SOM       | SOM main supply voltage, +5V                          |  |

| ,          |          |               | Connector Row D                                       |  |

| D1         |          | VCCO_HPA      | HPA I/O voltage rail, 1.0V to 1.8V                    |  |

| D2         |          | VCCO_HPA      | HPA I/O voltage rail, 1.0V to 1.8V                    |  |

| D3         |          | GND           | Ground, connect to carrier card ground plane          |  |

| D4         |          | HPA02_P       | HPIO on bank 65                                       |  |

| D5         |          | HPA02_N       | HPIO on bank 65                                       |  |

| D6         |          | GND           | Ground, connect to carrier card ground plane          |  |

| D7         |          | HPA01_P       | HPIO on bank 65                                       |  |

| D8         |          | HPA01_N       | HPIO on bank 65                                       |  |

| D9         |          | GND           | Ground, connect to carrier card ground plane          |  |

| D10        | GC       | HPA09_P       | HPIO on bank 65                                       |  |

| D11        | GC       | HPA09_N       | HPIO on bank 65                                       |  |

| D12        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D13        |          | HPA14_P       | HPIO on bank 65                                       |  |

| D14        |          | HPA14_N       | HPIO on bank 65                                       |  |

| D15        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D16        | HDGC     | HDA00_CC      | HDIO clock-capable pin on bank 26                     |  |

| D17        | HDGC     | HDA01         | HDIO on bank 26                                       |  |

| D18        |          | HDA02         | HDIO on bank 26                                       |  |

| D19        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D20        | HDGC     | HDA12         | HDIO on bank 26                                       |  |

| D21        | HDGC     | HDA13         | HDIO on bank 26                                       |  |

| D22        |          | HDA14         | HDIO on bank 26                                       |  |

| D23        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D24        | PD50     | PWRGD_FPD_M2C | Power good indication for PS FPD power rails          |  |

| D25        | PD50     | PWRGD_LPD_M2C | Power good indication for PS LPD power rails          |  |

| D26        | PD50     | PWRGD_PL_M2C  | Power good indication for all PL power rails          |  |

| D27        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D28        |          | MIO26         | PS MIO signal on bank 501. Optional use as PMU input. |  |

| D29        |          | MIO27         | PS MIO signal on bank 501. Optional use as PMU input. |  |

| D30        |          | MIO28         | PS MIO signal on bank 501. Optional use as PMU input. |  |

| D31        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D32        |          | MIO44         | PS MIO signal on bank 501                             |  |

| D33        |          | MIO45         | PS MIO signal on bank 501                             |  |

| D34        |          | MIO46         | PS MIO signal on bank 501                             |  |

| D35        |          | GND           | Ground, connect to carrier card ground plane          |  |

| D36        |          | MIO52         | PS MIO signal on bank 502                             |  |

Table 12: SOM240\_1 Signal Pins (cont'd)

| Pin Number | Pin Type | Signal Name       | Signal Description                           |

|------------|----------|-------------------|----------------------------------------------|

| D37        |          | MIO53             | PS MIO signal on bank 502                    |

| D38        |          | MIO54             | PS MIO signal on bank 502                    |

| D39        |          | GND               | Ground, connect to carrier card ground plane |

| D40        |          | MIO64             | PS MIO signal on bank 502                    |

| D41        |          | MIO65             | PS MIO signal on bank 502                    |

| D42        |          | MIO66             | PS MIO signal on bank 502                    |

| D43        |          | GND               | Ground, connect to carrier card ground plane |

| D44        |          | MIO76             | PS MIO signal on bank 502                    |

| D45        |          | MIO77             | PS MIO signal on bank 502                    |

| D46        |          | Reserved          | No connect on the SOM                        |

| D47        |          | GND               | Ground, connect to carrier card ground plane |

| D48        |          | GND               | Ground, connect to carrier card ground plane |

| D49        |          | GTR_DP3_C2M_P     | PS-GTR lane 3 RX, bank 505                   |

| D50        |          | GTR_DP3_C2M_N     | PS-GTR lane 3 RX, bank 505                   |

| D51        |          | GND               | Ground, connect to carrier card ground plane |

| D52        |          | GND               | Ground, connect to carrier card ground plane |

| D53        | AC01UF   | GTR_REFCLK2_C2M_P | PS-GTR REFCLK2 input, bank 505               |

| D54        | AC01UF   | GTR_REFCLK2_C2M_N | PS-GTR REFCLK2 input, bank 505               |

| D55        |          | GND               | Ground, connect to carrier card ground plane |

| D56        |          | GND               | Ground, connect to carrier card ground plane |

| D57        |          | GTR_DP2_M2C_P     | PS-GTR lane 2 TX, bank 505                   |

| D58        |          | GTR_DP2_M2C_N     | PS-GTR lane 2 TX, bank 505                   |

| D59        |          | GND               | Ground, connect to carrier card ground plane |

| D60        |          | VCC_SOM           | SOM main supply voltage, +5V                 |

## **SOM40 Connector Pinout**

The SOM40 connector provides access to two HPIO bank 65 (HPA), HPIO bank 66 (HPA), and HDIO bank 26 (HDA). For additional pin definitions see the K24 SOM XDC file.

**Table 13: SOM40 Connector Pinout**

| Connector<br>Row/Pin<br>Number | А             | В      | С         | D      |

|--------------------------------|---------------|--------|-----------|--------|

| 1                              | HPA16P        | GND    | HPA15_CCP | GND    |

| 2                              | HPA16N        | HPA18P | HPA15_CCN | HPA17P |

| 3                              | GND           | HPA18N | GND       | HPA17N |

| 4                              | HPA20_CCP_CLK | GND    | HPA19P    | GND    |

| 5                              | HPA20_CCN     | HPA22P | HPA19N    | HPA21P |

| 6                              | GND           | HPA22N | GND       | HPA21N |

| 7                              | HPA24P        | GND    | HPA23P    | GND    |

| 8                              | HPA24N        | HPA27  | HPA23N    | HPA25  |

Table 13: SOM40 Connector Pinout (cont'd)

| Connector<br>Row/Pin<br>Number | А     | В     | С     | D     |

|--------------------------------|-------|-------|-------|-------|

| 9                              | GND   | HPA28 | GND   | HPA26 |

| 10                             | HDA22 | GND   | HDA21 | GND   |

# **SOM40 Signal Names and Descriptions**

See the Zynq UltraScale+ Device Packaging and Pinouts Product Specification User Guide (UG1075) for further pin descriptions.

Table 14: SOM40 Signal Pins

| Pin Number | Pin Type        | Signal Name   | Signal Description                           |  |  |  |

|------------|-----------------|---------------|----------------------------------------------|--|--|--|

|            | Connector Row A |               |                                              |  |  |  |

| A1         |                 | HPA16P        | HPIO on bank 65                              |  |  |  |

| A2         |                 | HPA16N        | HPIO on bank 65                              |  |  |  |

| A3         |                 | GND           | Ground, connect to carrier card ground plane |  |  |  |

| A4         | GC              | HPA20_CCP_CLK | HPIO on bank 66                              |  |  |  |

| A5         | GC              | HPA20_CCN     | HPIO on bank 66                              |  |  |  |

| A6         |                 | GND           | Ground, connect to carrier card ground plane |  |  |  |

| A7         |                 | HPA24P        | HPIO on bank 65                              |  |  |  |

| A8         |                 | HPA24N        | HPIO on bank 65                              |  |  |  |