# ADA4099-2BCHIPS

# 50 V, 8 MHz, 1.65 mA per Channel, Robust, Over-The-Top, Precision Op Amp

#### **FEATURES**

- ▶ Ultrawide common-mode input range: -15.1 V to +55 V

- ▶ Wide power supply voltage operating range: 3.15 V to 50 V

- ▶ Low supply current: 1.65 mA per channel

- Low input offset voltage: ±12 μV

- ► Low offset voltage drift: ±0.1 µV/°C

- Low voltage noise

- ▶ 1/f noise corner: 6 Hz

- ▶ 150 nV p-p at 0.1 Hz to 10 Hz

- 7 nV/√Hz at 100 Hz (e<sub>n</sub>)

- ▶ High speed

- ▶ GBP: 8 MHz

- Slew rate: 5.5 V/μs at ΔV<sub>OUT</sub> = 25 V

- Low power supply shutdown current: 17 μA per channel

- ▶ Low input bias current: ±4 nA

- Large signal voltage gain: 154 dB at ΔV<sub>OUT</sub> = 25 V

- ▶ CMRR: 130 dB at  $V_{CM}$  = -14.75 to +13.25 V

- ▶ PSRR: 136 dB

- ▶ Input overdrive tolerant with no phase reversal

#### **APPLICATIONS**

- Industrial sensor conditioning

- Supply current sensing

- Battery and power supply monitoring

- ▶ Front-end amplifiers in abusive environments

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

#### **GENERAL DESCRIPTION**

The ADA4099-2BCHIPS is a robust, precision, rail-to-rail input and output dual-channel operational amplifier with inputs that operate from  $-V_S$  to  $+V_S$  and beyond, which is referred to in this data sheet as Over-The-Top<sup>TM</sup>. The device features an offset voltage of  $\pm 12~\mu V$ , an input bias current (I<sub>B</sub>) of  $\pm 4$  nA, and can operate on supplies that range from 3.15 V to 50 V. The ADA4099-2BCHIPS draws 1.65 mA of supply current per channel.

The ADA4099-2BCHIPS Over-The-Top input stage has robust input protection features for abusive environments. The inputs can tolerate up to 80 V of differential voltage without damage or degradation to dc accuracy. The operating input common-mode range extends from rail-to-rail and beyond, up to 70 V > –V $_{\rm S}$ , independent of the +V $_{\rm S}$  supply.

The ADA4099-2BCHIPS is unity-gain stable and can drive loads requiring up to 20 mA per channel. The device can also drive capacitive loads as large as 100 pF. The amplifier is available with low power shutdown per channel.

The ADA4099-2BCHIPS is specified at +25°C but is functional over the extended industrial temperature range (-40°C to +125°C). Additional application and technical information can be found in the ADA4099-2 data sheet.

### **TABLE OF CONTENTS**

| Features 1                               | ESD Caution                                 | 5   |

|------------------------------------------|---------------------------------------------|-----|

| Applications1                            | Pin Configuration and Function Descriptions | . 6 |

| Functional Block Diagram1                | Outline Dimensions                          | . 7 |

| General Description1                     |                                             |     |

| Specifications3                          | Recommendations                             | . 7 |

| Electrical Characteristics—±15 V Supply3 | Ordering Guide                              | 8   |

| Absolute Maximum Ratings5                | -                                           |     |

## **REVISION HISTORY**

7/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 8

### **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS—±15 V SUPPLY**

$Common-mode\ voltage\ (V_{CM})=0\ V,\ SHDNx\ pins\ are\ open,\ load\ resistance\ (R_L)=499\ k\Omega\ to\ ground,\ and\ T_A=25^{\circ}C,\ unless\ otherwise\ noted.$

Table 1.

| Parameter                                            | Test Conditions/Comments                                                                                 | Min                   | Тур        | Max          | Unit      |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------|------------|--------------|-----------|

| DC PERFORMANCE                                       |                                                                                                          |                       |            |              |           |

| Input Offset Voltage (V <sub>OS</sub> ) <sup>1</sup> |                                                                                                          | :                     | ±12        |              | μV        |

|                                                      | Power supply voltage (V <sub>SY</sub> ) = ±25 V                                                          | :                     | ±15        |              | μV        |

| Input Voltage Offset Drift <sup>2</sup>              | $T_{MIN} < T_A < T_{MAX}$                                                                                | :                     | ±0.1       |              | μV/°C     |

| Input Bias Current (I <sub>B</sub> )                 |                                                                                                          | :                     | <u>+</u> 4 |              | nA        |

| . (5)                                                | V <sub>SY</sub> = ±25 V                                                                                  | :                     | <u>+</u> 4 |              | nA        |

| Input Offset Current (I <sub>OS</sub> )              |                                                                                                          | :                     | ±2         |              | nA        |

| . (33)                                               | V <sub>SY</sub> = ±25 V                                                                                  | :                     | <u>+</u> 4 |              | nA        |

| Common-Mode Rejection Ratio (CMRR)                   | V <sub>CM</sub> = −14.75 V to +13.25 V                                                                   |                       | 130        |              | dB        |

| , , ,                                                | V <sub>CM</sub> = -15.1 V to +13.25 V                                                                    |                       | 126        |              | dB        |

|                                                      | V <sub>CM</sub> = -15.1 V to +55 V                                                                       | 126                   |            | dB           |           |

| Common-Mode Input Range                              | Guaranteed by CMRR tests                                                                                 | -15.1                 |            | +55          | V         |

| Large Signal Voltage Gain (A <sub>OL</sub> )         | Delta output voltage ( $\Delta V_{OUT}$ ) = 25 V                                                         |                       | 154        |              | dB        |

| ( , OL)                                              | $\Delta V_{OUT} = 25 \text{ V, } R_L = 10 \text{ k}\Omega$                                               |                       | 134        |              | dB        |

| NOISE PERFORMANCE                                    | 001 1,12 1- 1-1                                                                                          |                       |            |              |           |

| Input Voltage Noise                                  | Frequency = 0.1 Hz to 10 Hz                                                                              |                       | 150        |              | nV p-p    |

| mpat voltage Holos                                   | 1/f noise corner                                                                                         |                       | 6          |              | Hz        |

|                                                      | Frequency = 100 Hz                                                                                       |                       | 7          |              | nV/√Hz    |

| Over-The-Top                                         | Frequency = 100 Hz, $V_{CM}$ > positive supply voltage (+ $V_S$ )                                        |                       | 8          |              | nV/√Hz    |

| Input Current Noise                                  | Frequency = 100 Hz                                                                                       |                       | 0.5        |              | pA/√Hz    |

| Over-The-Top                                         | Frequency = 100 Hz, V <sub>CM</sub> > +V <sub>S</sub>                                                    |                       | 5.5        |              | pA/√Hz    |

| DYNAMIC PERFORMANCE                                  | Trequency = 100 Hz, V <sub>CM</sub> > 1V <sub>S</sub>                                                    |                       |            |              | prv vi iz |

| Slew Rate                                            | ΔV <sub>OUT</sub> = 25 V                                                                                 |                       | 5.5        |              | V/µs      |

|                                                      | 1                                                                                                        |                       |            |              | MHz       |

| Gain Bandwidth Product (GBP)                         | Test frequency (f <sub>TEST</sub> ) = 25 kHz                                                             |                       | 8<br>57    |              |           |

| Phase Margin                                         | AV - 12 V                                                                                                |                       |            |              | deg       |

| 1% Settling Time                                     | $\Delta V_{OUT} = \pm 2 V$                                                                               |                       | 1.15       |              | μs        |

| 0.1% Settling Time                                   | $\Delta V_{OUT} = \pm 2 V$                                                                               |                       | 1.5        |              | μs        |

| Total Harmonic Distortion plus Noise (THD + N)       | Frequency = 10 kHz, output voltage ( $V_{OUT}$ ) = 5.6 V p-p, $R_L$ = 10 k $\Omega$ , bandwidth = 80 kHz |                       | 0.001      |              | %         |

| NPUT CHARACTERISTICS                                 | - 10 K2, Bandwidth - 00 KH2                                                                              |                       |            |              |           |

| Input Resistance                                     | Differential mode                                                                                        |                       | 100        |              | kΩ        |

| Iliput Nesistance                                    | Common mode                                                                                              |                       | >1         |              | GΩ        |

| Input Canasitanes                                    |                                                                                                          |                       |            |              |           |

| Input Capacitance                                    | Differential mode Common mode                                                                            | 9                     |            | pF           |           |

| NUDALA AND QUIDAIG DIAIG                             | Common mode                                                                                              |                       | 3          |              | p⊦        |

| SHDN1 AND SHDN2 PINS                                 | A 15 6 OUDM 16 A/ )                                                                                      |                       |            | \/ . 0.5     |           |

| Input Logic Low                                      | Amplifier active, SHDNx voltage (V <sub>SHDN</sub> ) < negative                                          |                       |            | $-V_S + 0.5$ | V         |

| Innut Logic Lligh                                    | supply voltage (-V <sub>S</sub> ) + 0.5 V                                                                | V . 1 E               |            |              | V         |

| Input Logic High                                     | Amplifier shutdown, V <sub>SHDN</sub> > -V <sub>S</sub> + 1.5 V                                          | -V <sub>S</sub> + 1.5 | 0 F        |              | V         |

| Response Time                                        | Amplifier active to shutdown                                                                             |                       | 2.5        |              | μs        |

| Dull Davin Commant                                   | Amplifier shutdown to active                                                                             |                       | 10         |              | μs        |

| Pull-Down Current                                    | $V_{SHDN} = -V_S + 0.5 V$                                                                                | -0.6                  |            | μA           |           |

|                                                      | $V_{SHDN} = -V_S + 1.5 V$                                                                                |                       | 0.3        |              | μA        |

| OUTPUT CHARACTERISTICS                               |                                                                                                          |                       |            |              |           |

| Output Voltage Swing Low                             | $V_{OD}^3 = 30 \text{ mV}, \text{ no load}$                                                              |                       | 45         |              | mV        |

|                                                      | $V_{OD}^3$ = 30 mV, sink current ( $I_{SINK}$ ) = 10 mA                                                  | ]                     | 260        |              | mV        |

analog.com Rev. 0 | 3 of 8

#### **SPECIFICATIONS**

Table 1.

| Parameter Test Conditions/Comments     |                                                                   | Min  | Min Typ Max |      | Unit |  |

|----------------------------------------|-------------------------------------------------------------------|------|-------------|------|------|--|

| Output Voltage Swing High              | $V_{OD}^3$ = 30 mV, no load                                       |      | 45          |      | mV   |  |

|                                        | $V_{OD}^3$ = 30 mV, source current (I <sub>SOURCE</sub> ) = 10 mA |      | 900         |      | mV   |  |

| Short-Circuit Current                  | I <sub>SOURCE</sub>                                               |      | 34          |      | mA   |  |

|                                        | I <sub>SINK</sub>                                                 |      | 50          |      | mA   |  |

| POWER SUPPLY                           |                                                                   |      |             |      |      |  |

| Maximum Operating Voltage <sup>4</sup> |                                                                   |      |             | 50   | V    |  |

| Operating Range                        | Guaranteed by power supply rejection ratio (PSRR)                 | 3.15 |             | 50   | V    |  |

| Supply Current per Channel             | Amplifier active                                                  |      | 1.65        |      | mA   |  |

|                                        | $V_{SY} = \pm 25 V$                                               | 1.75 |             |      | mA   |  |

|                                        | Amplifier shutdown, V <sub>SHDN</sub> = −V <sub>S</sub> + 1.5 V   |      | 17          |      | μA   |  |

| PSRR                                   | V <sub>SY</sub> = 3.15 V to 50 V                                  | 136  |             | dB   |      |  |

| THERMAL SHUTDOWN <sup>5</sup>          |                                                                   |      |             |      |      |  |

| Temperature                            | T <sub>J</sub>                                                    |      | 175         |      | °C   |  |

| Hysteresis                             |                                                                   | 20   |             | °C   |      |  |

| Functional Temperature                 | T <sub>A</sub>                                                    | -40  |             | +125 | °C   |  |

<sup>1</sup> Thermoelectric voltages present in the high speed production test limit the measurement accuracy of this parameter. The limits listed in Table 1 represent an upper limit imposed by the test capability and are not necessarily indicative of actual performance of the devices.

analog.com Rev. 0 | 4 of 8

$<sup>^{2}\,</sup>$  Offset voltage drift is guaranteed through lab characterization and is not production tested.

$<sup>^3~\</sup>rm V_{OD}$  is +30 mV for  $\rm V_{OUT}$  high and –30 mV for  $\rm V_{OUT}$  low.

<sup>&</sup>lt;sup>4</sup> Maximum operating voltage is limited by the time-dependent dielectric breakdown (TDDB) of on-chip capacitor oxides. The amplifier tolerates temporary transient overshoot up to the specified absolute maximum rating and the dc supply voltage must be limited to the maximum operating voltage.

<sup>&</sup>lt;sup>5</sup> Thermal shutdown is lab characterized only and is not tested in production.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                              | Rating          |  |

|----------------------------------------|-----------------|--|

| Supply Voltage <sup>1</sup>            |                 |  |

| Transient                              | 60 V            |  |

| Continuous                             | 50 V            |  |

| Differential Input Voltage             | ±80 V           |  |

| ±INx Pin Voltage                       |                 |  |

| Continuous                             | -5 V to +80 V   |  |

| Survival                               | -10 V to +80 V  |  |

| ±INx Pin Current                       | 20 mA           |  |

| SHDNx Pin Voltage                      | -0.3 V to +60 V |  |

| Storage Temperature Range              | -65°C to +150°C |  |

| Functional Temperature Range           | -55°C to +150°C |  |

| Junction Temperature (T <sub>J</sub> ) | 175°C           |  |

Maximum supply voltage is limited by the TDDB of on-chip capacitor oxides. The amplifier tolerates temporary transient overshoot up to the specified transient maximum rating. The continuous operating supply voltage must be limited to no more than 50 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 5 of 8

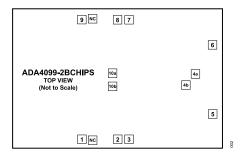

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pad Configuration

Table 3. Pad Function Descriptions<sup>1</sup>

| Pad Number | Mnemonic          | X Coordinate | Y Coordinate | Description                                      |

|------------|-------------------|--------------|--------------|--------------------------------------------------|

| 1          | V <sub>OUT1</sub> | -386         | -643         | Output, Channel 1                                |

| 2          | -IN1              | -001         | -643         | Inverting Input, Channel 1                       |

| 3          | +IN1              | -122         | -643         | Noninverting Input, Channel 1                    |

| 4a         | -V <sub>S</sub>   | +837         | +059         | Negative Supply Voltage (Both Must Be Connected) |

| 4b         | -V <sub>S</sub>   | +735         | -059         | Negative Supply Voltage (Both Must Be Connected) |

| 5          | SHDN1             | +1022        | -373         | Shutdown Channel 1                               |

| 6          | SHDN2             | +1022        | +373         | Shutdown Channel 2                               |

| 7          | +IN2              | -001         | +643         | Noninverting Input, Channel 2                    |

| 8          | -IN2              | +122         | +643         | Inverting Input, Channel 2                       |

| 9          | V <sub>OUT2</sub> | -386         | +643         | Output, Channel 2                                |

| 10a        | +V <sub>S</sub>   | -056         | +070         | Positive Supply Voltage (Both Must Be Connected) |

| 10b        | +V <sub>S</sub>   | -056         | -070         | Positive Supply Voltage (Both Must Be Connected) |

<sup>&</sup>lt;sup>1</sup> All dimensions are referenced from the center of the die to the center of each bond pad.

analog.com Rev. 0 | 6 of 8

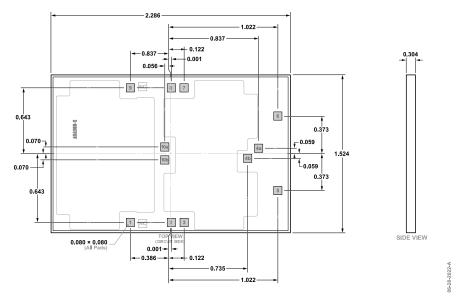

## **OUTLINE DIMENSIONS**

Figure 3. 12-Pad Bare Die [CHIP] (C-12-5) Dimensions shown in millimeters

## **DIE SPECIFICATIONS AND ASSEMBLY RECOMMENDATIONS**

# **Die Specifications**

Table 4. Die Specifications

| Parameter            | Value                                          | Unit |

|----------------------|------------------------------------------------|------|

| Chip Size            | 1424 × 2186                                    | μm   |

| Scribe Line Width    | 100 × 100                                      | μm   |

| Die Size Maximum     | 1524 × 2286                                    | μm   |

| Thickness            | 304                                            | μm   |

| Backside             | V-                                             | V    |

| Passivation          | 1.1 (doped silicon and polymer)                | μm   |

| Top Coat Thickness   | 32                                             | μm   |

| Bond Pads (Minimum)  | 80 × 80                                        | μm   |

| Bond Pad Composition | 1.0% aluminum silicon (AlSi), 0.5% copper (Cu) | %    |

## **Assembly Recommendations**

Table 5. Assembly Recommendations

| Assembly Component | Recommendation |

|--------------------|----------------|

| Die Attach         | ABLESTIK 8200T |

| Bonding Method     | 1 mil gold     |

| Bonding Sequence   | Unspecified    |

analog.com Rev. 0 | 7 of 8

### **OUTLINE DIMENSIONS**

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                 | Package Quantity    | Package Option |

|--------------------|-------------------|-------------------------------------|---------------------|----------------|

| ADA4099-2BCHIPS-WP | -40°C to +125°C   | 12-Pad Bare Die [CHIP], Waffle Pack |                     | C-12-5         |

| ADA4099-2BCHIPS-PT | -40°C to +125°C   | 12-Pad Bare Die [CHIP]              | Tape and Reel, 3000 | C-12-5         |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.