110 V High Voltage, 1 A High Current,

# Arbitrary Waveform Generator with Integrated 14-Bit High Speed DAC

# **FEATURES**

- Wide high voltage supply range: ±12 V to ±55 V

- High Output Capability

- Output voltage range: Up to ±40 V

- ► High output current drive: 1 A continuous

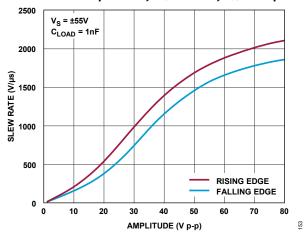

- ► High slew rate: ≥1800 V/μs into 1000 pF load

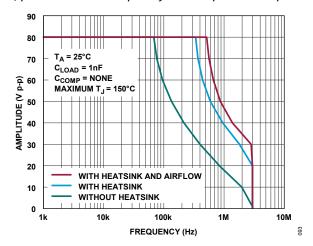

- ► Large signal bandwidth: 1 MHz

- ► Extensive Programming and Diagnostics

- ► 14-bit resolution arbitrary waveform generation (AWG) mode

- ► 16 level analog pattern generation (APG) mode

- ▶ Digitally programmable current, voltage and thermal fault monitoring and protection

- Programmable supply current with shutdown mode

- Design-in Friendly

- ► Unlimited capacitive load drive with external compensation and slew control

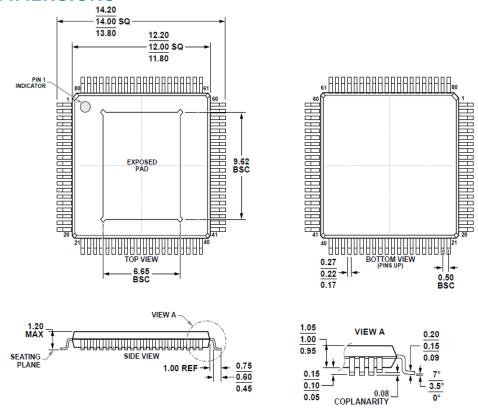

- ► Package: 80-pin, 12mm x 12mm TQFP

- ► EPAD-up package for mountable heatsink

- ► Operating temperature range: -40 °C to +85 °C

# **APPLICATIONS**

- Automatic test equipment (ATE)

- Display panel formation and testing

- Piezo drivers

- Programmable power supplies

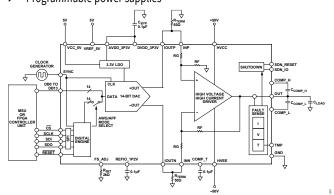

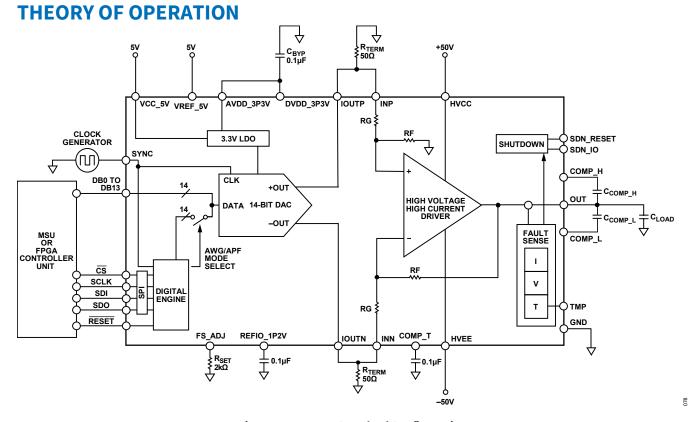

Figure 1. Simplified Functional Block Diagram

## GENERAL DESCRIPTION

The AD8460 is a "bits in, power out" high voltage, high-power, highspeed driver optimized for large output current (up to ±1 A) and high slew rate (up to  $\pm 1800 \text{ V/}\mu\text{s}$ ) at high voltage (up to  $\pm 40 \text{ V}$ ) into capacitive loads. Combining a 14-bit high-speed DAC, a high voltage, high output current (HV-HI) analog driver, and fault monitoring and protection circuits, the AD8460 is ideally suited for high power applications such as arbitrary waveform generation (AWG), programmable power supplies, and high voltage automated test equipment (ATE).

A proprietary high-voltage BCDMOS process, novel high voltage architecture, and thermally enhanced package from Analog Devices Inc. enable this high-performance driver. A digital engine implements userconfigurable features: modes for digital input, programmable supply current, and fault monitoring and programmable protection settings for output current, output voltage, and junction temperature. Analog features extend functionality: external compensation enables unlimited capacitive load drive, programmable shutdown delay, and full-scale adjustment. The AD8460 operates on high voltage dual supplies up to ±55 V and a single low voltage supply of 5 V.

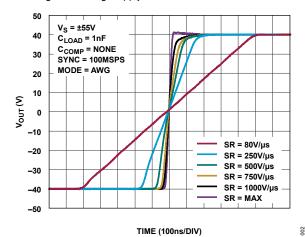

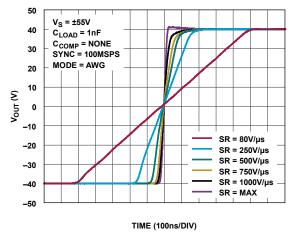

Figure 2. Large Signal Pulse Response vs. Edge Speed with External Slew Control

003

110 V High Voltage, 1 A High Current,

Arbitrary Waveform Generator with Integrated 14-Bit High Speed DAC

#### **FUNCTIONAL BLOCK DIAGRAM** VCC\_5V VREF\_5V AVDD\_3P3V CLOCK GENERATOR RF 3.3V LDO SHUTDOWN SDN\_IO (M) COMP\_H CLK +OUT C<sub>COMP H</sub> HIGH VOLTAGE HIGH CURRENT DRIVER DATA 14-BIT DAC MSU OR FPGA CONTROLLER UNIT COMP L AWG/APF MODE SELECT cs RF SCLK ν DIGITAL ENGINE SDI т SDC RG RESET IOUTN R<sub>TERM</sub> 50Ω

Figure 3. Functional Block Diagram

# **TABLE OF CONTENTS**

| Features1                                     |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Functional Block Diagram2                     |

| Revision History4                             |

| Specifications5                               |

| Timing Diagrams11                             |

| ABSOLUTE MAXIMUM RATINGS12                    |

| Thermal Resistance13                          |

| Electrostatic Discharge (ESD)13               |

| PIN CONFIGURATION AND FUNCTION DESCRIPTIONS14 |

| INTERPRETING TYPICAL PERFORMANCE CURVES17     |

| Typical Performance Characteristics17         |

| Terminology26                                 |

| Alarm26                                       |

| Analog Pattern Generation (APG) Mode26        |

| Arbitrary Waveform Generation (AWG) Mode26    |

| Arm26                                         |

| Disarm26                                      |

| Fault26                                       |

| Protection System26                           |

| Reserved26                                    |

| Safe Operating Area (SOA)26                   |

| Shutdown and Sleep26                          |

| Slew Boost27                                  |

| Span27                                        |

| Theory of Operation28                         |

| Overview28                                    |

| INITIAL POWER-UP29                            |

| POWER SUPPLIES AND DECOUPLING29               |

| VREF_5V29                                     |

| POWER SUPPLY SEQUENCING30                     |

| REFERENCE OPERATION30                         |

| INPUT AND MODE OF OPERATION31                 |

| ANALOG PATTERN GENERATION (APG)                   | 32       |

|---------------------------------------------------|----------|

| ARBITRARY WAVEFORM GENERATION (AWG)               | 33       |

| PREDISTORTION AND ADJUSTABLE INPUT EDGE SE        |          |

| OUTPUT CURRENT DRIVE                              | 34       |

| FAULT MONITORING AND PROTECTION                   | 34       |

| FAULT-INITIATED SHUTDOWN PROTECTION FEATU         |          |

| SHUTDOWN PROTECTION SETTINGS                      | 36       |

| PROGRAMMING OVERCURRENT PROTECTION                | 36       |

| PROGRAMMING OVERVOLTAGE PROTECTION                | 37       |

| PROGRAMMING OVERTEMPERATURE PROTECTION            | 38. NC   |

| PROGRAMMING SHUTDOWN THRESHOLD SETTING            | S38      |

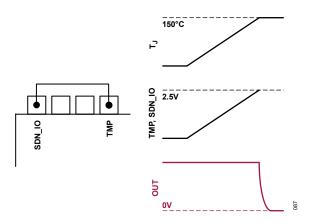

| SHUTDOWN CONTROL (SDN_IO)                         | 39       |

| DELAYED SHUTDOWN                                  | 39       |

| MANUAL THERMAL SHUTDOWN                           | 40       |

| POWER ON RESET (POR) AND <b>RESET</b>             | 41       |

| SLEEP CONTROL AND OTHER REGISTER RELATED FEATURES | 41       |

| SLEEP CONTROL                                     | 41       |

| OTHER FEATURES                                    | 42       |

| SLEW BOOST                                        | 42       |

| THERMAL MONITORING (TMP)                          | 42       |

| OUTPUT COMPENSATION (COMP_H AND COMP_             | _L) . 42 |

| THERMAL COMPENSATION (COMP_T)                     | 43       |

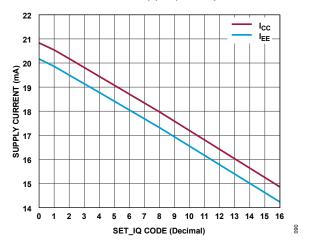

| PROGRAMMABLE QUIESCENT CURRENT                    | 43       |

| pplications Information                           | 45       |

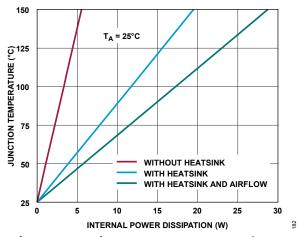

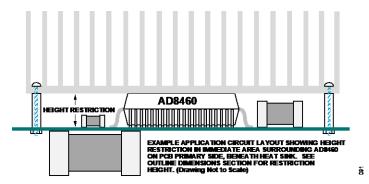

| Thermal Management                                | 45       |

| PCB Thermal Design                                | 45       |

| POWER DISSIPATION                                 | 45       |

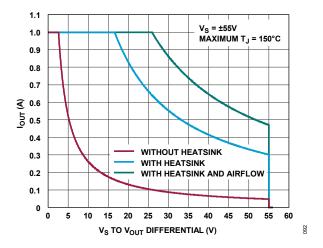

| SAFE OPERATING AREA                               | 46       |

| DC SOA                                            | 47       |

| Dynamic SOA                                       | 47       |

| Limiting Dynamic Peak Current for >1nF Loads      | 48       |

| FULL-SCALF ADJUSTMENT                             | 48       |

| FULL-SCALE REDUCTION49                    | HVDAC DATA REGISTER (PATTERN MEMORY) SUMMARY 63   |

|-------------------------------------------|---------------------------------------------------|

| LAYOUT50                                  | HVDAC DATA REGISTER (PATTERN MEMORY) DETAILS . 67 |

| TOP LEVEL DIGITAL REGISTER ASSIGNMENT51   | Outline Dimensions74                              |

| Device control Register Summary and map52 | Ordering Guide74                                  |

| CONTROL REGISTER DETAILS55                | Evaluation Board74                                |

# **REVISION HISTORY**

10/2023 - Rev. 0

analog.com Rev.0 4 of 75

# **SPECIFICATIONS**

# **Table 1. Electrical Characteristics**

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \ \Omega, R_{SET} \text{ to FS}\_ADJ = 2 \ k\Omega, COMP\_L, COMP\_H = 0 \ pF, C_{LOAD} = 1 \ nF, T_C = 30^{\circ}C, unless otherwise noted.)$

| PARAMETER                           | SYMBOL                     | CONDITIONS/COMMENTS                                                             | MIN | TYP           | MAX  | UNITS       |

|-------------------------------------|----------------------------|---------------------------------------------------------------------------------|-----|---------------|------|-------------|

| DYNAMIC PERFORMANCE                 |                            |                                                                                 |     |               |      |             |

| Small Signal Bandwidth              | f <sub>3db</sub>           | $V_{OUT} = 0.1 \text{ V p-p}, T_J = 85^{\circ}\text{C}.$<br>See Figure 27.      |     | 4.3           |      | MHz         |

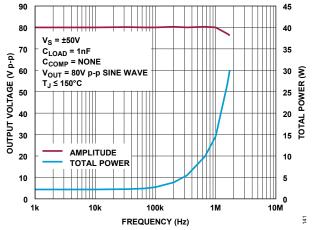

| Large Signal Bandwidth <sup>1</sup> |                            | V <sub>OUT</sub> = 80 V p-p. See <i>Figure</i> 26.                              |     | 1             |      | MHz         |

| Claw Pata 200/, to 200/             | SR <sub>RISE</sub>         | V <sub>OUT</sub> = 80 V p-p. See <i>Figure 8</i> .                              |     | 2100          |      | V/µs        |

| Slew Rate, 20% to 80%               | SR <sub>FALL</sub>         | V <sub>OUT</sub> = 80 V p-p. See <i>Figure</i> 9.                               |     | 1800          |      | V/µs        |

| Output 1% Settling Time             | t <sub>st</sub>            | V <sub>OUT</sub> = 40 V p-p. See <i>Figure 4</i> .                              |     | 13.5          |      | μs          |

| Output 0.1% Settling Time           | t <sub>st</sub>            | V <sub>OUT</sub> = 40 V p-p. See <i>Figure 4</i> .                              |     | 39.5          |      | μs          |

| NOISE/DISTORTION PERFORM            | IANCE                      |                                                                                 |     |               |      |             |

| Output Noise Spectral<br>Density    | $V_N$                      | $C_{LOAD} = 0 \text{ nF, } T_J = 85^{\circ}C, f = 100$ kHz                      |     | 0.6           |      | μV/√Hz      |

| Harmonic Distortion,                |                            | V <sub>OUT</sub> = 80 V p-p, 1 kHz                                              |     | -66           |      | dBc         |

| HD2/HD3                             |                            | V <sub>OUT</sub> = 80 V p-p, 100 kHz                                            |     | -70           |      | dBc         |

| OUTPUT DC ACCURACY <sup>2</sup>     |                            |                                                                                 |     |               |      |             |

| Output Offset Error                 | Vos                        |                                                                                 |     | 4             | 25   | mV          |

| Output Onset Error                  | $V_{OS\_TC}$               | $T_C = 30^{\circ}C$ to $85^{\circ}C$                                            |     | 0.16          |      | mV/°C       |

|                                     | V <sub>GAIN_ERROR</sub>    | V <sub>OUT</sub> = 80 V p-p                                                     |     | 0.24          | 0.45 | % FSR       |

| Gain Error <sup>3</sup>             | V <sub>GAIN_ERROR_TC</sub> | T <sub>c</sub> = 30°C to 85°C                                                   |     | 0.002         |      | %<br>FSR/°C |

| Integral Nonlinearity               | INL                        |                                                                                 | -17 | +3/-8         | 12   | LSB         |

| Differential Nonlinearity           | DNL                        |                                                                                 | -10 | +0.3/-4       | 4    | LSB         |

| OUTPUT CHARACTERISTICS              |                            |                                                                                 |     |               |      |             |

| Output Voltage Range⁴               | V <sub>OUT</sub>           |                                                                                 |     | ±40           |      | V           |

| 0.1.1111                            | .,,                        | $I_{OUT} = 0.25 \text{ A}, T_J = 85^{\circ}\text{C}. \text{ See}$<br>Figure 43. |     | HVCC -<br>2.2 |      | V           |

| Output Headroom                     | V <sub>OUT_H</sub>         | I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 85°C. See<br><i>Figure 43</i> .        |     | HVCC -<br>5   |      | V           |

| Outrot Factor                       | V                          | $I_{OUT} = -0.25 \text{ A}, T_{J} = 85^{\circ}\text{C}. \text{ See}$ Figure 43. |     | HVEE + 3.3    |      | V           |

| Output Footroom                     | V <sub>OUT_L</sub>         | I <sub>ОUТ</sub> = -1 A, T <sub>J</sub> = 85°C. See<br><i>Figure 43</i> .       |     | HVEE + 11.1   |      | V           |

analog.com Rev.0 5 of 75

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \ \Omega, R_{SET} = 0 \text{ EV}, R_{SET} =$

| PARAMETER                                               | SYMBOL                    | CONDITIONS/COMMENTS                                                        | MIN   | TYP      | MAX                 | UNITS |

|---------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|-------|----------|---------------------|-------|

| Continuous Output<br>Current Drive⁵                     | Гоит                      |                                                                            |       | 1        |                     | Α     |

| Peak Instantaneous<br>Output Current Drive <sup>6</sup> | I <sub>оит</sub>          |                                                                            |       | 2.6/-2.2 |                     | Α     |

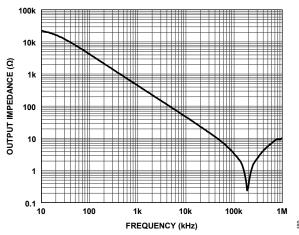

| Output Resistance During<br>Shutdown                    | Z <sub>OUT_SDN</sub>      | See Figure 47.                                                             |       | 27       |                     | kΩ    |

| IOUTP, IOUTN                                            |                           |                                                                            |       |          |                     |       |

| Compliance Range                                        | $V_{IOUTP_{N}}$           |                                                                            | -1    |          | 1.25                | >     |

| REFERENCE INPUT                                         |                           |                                                                            |       |          |                     |       |

| Input Range                                             | VREF_5V <sup>7</sup>      |                                                                            |       | 5        |                     | V     |

| Input Range                                             | REFIO_1P2V                |                                                                            | 0.12  | 1.2      | 1.25                | V     |

|                                                         | VREF_5V                   |                                                                            |       | 34       |                     | kΩ    |

| Input Resistance                                        | REFIO_1P2V                | Average input resistance over REFIO_1P2V input range.                      |       | 15       |                     | kΩ    |

| REFERENCE OUTPUT                                        |                           |                                                                            |       |          |                     |       |

| O. da. da Valla                                         | DEELO 1DOV                |                                                                            | 1.195 | 1.22     | 1.245               | V     |

| Output Voltage                                          | REFIO_1P2V                | T <sub>C</sub> = 30°C to 85°C                                              |       | 17       |                     | μV/°C |

| Output Current Drive                                    |                           |                                                                            |       | 100      |                     | μΑ    |

| SDN_IO SPECIFICATIONS                                   |                           |                                                                            |       |          |                     |       |

| Output Voltage Range                                    | SDN_IO                    | SDN_IO Floating                                                            | 0     |          | V <sub>cc</sub> _5V | V     |

| Chart day on Thomas hadd                                | SDN_IO <sub>RISING</sub>  |                                                                            | 2.54  | 2.56     | 2.57                | V     |

| Shutdown Threshold                                      | SDN_IO <sub>FALLING</sub> |                                                                            | 2.45  | 2.47     | 2.48                | V     |

| Output Current Drive Sink                               | SDN_IO <sub>SNK</sub>     |                                                                            |       | -180     |                     | μΑ    |

| Output Current Drive<br>Source                          | SDN_IO <sub>SRC</sub>     |                                                                            |       | 180      |                     | μΑ    |

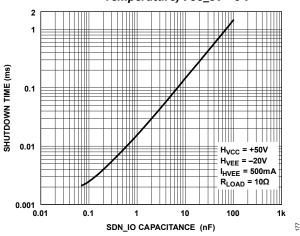

| Turn Off Time                                           | SDN_IO <sub>TOFF</sub>    | SDN_IO > SDN_IO <sub>RISING</sub> to shutdown. See <i>DELAYED</i> SHUTDOWN |       | 400      |                     | ns    |

| DC OVERCURRENT PROTECTI                                 | ON                        |                                                                            |       |          |                     |       |

| Sourcing Setpoint Range<br>Max                          |                           |                                                                            |       | 1        |                     | Α     |

| Sourcing Code Range                                     |                           |                                                                            | 0x06  |          | 0x40                |       |

| Sinking Setpoint Range<br>Max                           |                           |                                                                            |       | -1       |                     | Α     |

analog.com Rev.0 6 of 75

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \ \Omega, R_{SET} = 0 \text{ EV}, R_{SET} =$

| PARAMETER                              | SYMBOL                                 | CONDITIONS/COMMENTS                 | MIN  | TYP    | MAX  | UNITS  |

|----------------------------------------|----------------------------------------|-------------------------------------|------|--------|------|--------|

| Sinking Code Range                     |                                        |                                     | 0x40 |        | 0x06 |        |

| Setpoint Resolution                    |                                        |                                     |      | 15.625 |      | mA/lsb |

| Setpoint Accuracy                      |                                        | Code = 0x06, 93.75 mA               |      | 3.6    |      | %      |

| DC OVERVOLTAGE PROTECTION              | ON                                     |                                     |      |        |      |        |

| Positive Voltage Setpoint<br>Range Max |                                        |                                     |      | 55     |      | V      |

| Positive Code Range                    |                                        |                                     | 0x01 |        | 0x1C |        |

| Negative Voltage Setpoint<br>Range Max |                                        |                                     |      | -55    |      | V      |

| Negative Code Range                    |                                        |                                     | 0x1C |        | 0x01 |        |

| Setpoint Resolution                    |                                        |                                     |      | 1.953  |      | V/lsb  |

| Setpoint Accuracy                      |                                        | Code = 0x10, 31.25 V                |      | 1.4    |      | %      |

| DC OVERTEMPERATURE PROT                | ECTION                                 |                                     |      |        |      |        |

| Setpoint Range <sup>8</sup>            |                                        | Max                                 |      | 150    |      | °C     |

| Setpoint Range                         |                                        | Min                                 |      | 20     |      | °C     |

| Code Range                             |                                        |                                     | 0x2C |        | 0x40 |        |

| Setpoint Resolution                    |                                        |                                     |      | 6.51   |      | °C/lsb |

| Setpoint Accuracy                      |                                        | Code = 0x40, T <sub>J</sub> = 150°C |      | 2.3    |      | %      |

| TEMPERATURE MONITOR SPE                | CIFICATIONS                            |                                     |      |        |      |        |

| Initial Voltage                        | TMP_V <sub>INITIAL</sub>               | T <sub>J</sub> = 30°C               | 1.75 | 1.78   | 1.81 | V      |

| Scaling                                | TMP_TC                                 |                                     |      | 6      |      | mV/°C  |

| SYNC INPUT <sup>9,10</sup>             |                                        |                                     |      |        |      |        |

| Input High Voltage                     | VIH <sub>SYNC</sub>                    |                                     | 2    |        | 3.47 | V      |

| Input Low Voltage                      | VIL <sub>SYNC</sub>                    |                                     | 0    |        | 0.8  | V      |

| Input Current                          | I <sub>L_SYNC</sub>                    |                                     | -1   |        | 1    | μΑ     |

| Input Capacitance                      | C <sub>SYNC</sub>                      |                                     |      | 12     |      | pF     |

| PARALLEL INTERFACE INPUTS              | (DB0 to DB13)                          | 9,10                                |      |        |      |        |

| Input High Voltage                     | VIHPARALLEL                            |                                     | 2    |        | 3.47 | V      |

| Input Low Voltage                      | VILPARALLEL                            |                                     | 0    |        | 0.8  | V      |

| Input Current                          | I <sub>L_PARALLEL</sub>                |                                     | -1   |        | 1    | μΑ     |

| Input Capacitance                      | C <sub>PARALLEL</sub>                  |                                     |      | 8      |      | pF     |

| SPI INTERFACE INPUTS (SCLK             | , SDI, <del>CS</del> ) <sup>9,10</sup> |                                     |      |        |      |        |

| Input High Voltage                     | VIH <sub>SPI</sub>                     |                                     | 2.4  |        | 3.47 | V      |

analog.com Rev.0 7 of 75

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} = 0 \text{ EV}, R_{TERM} = 0 \text{ pF}, C_{LOAD} = 1 \text{ nF}, T_{C} = 30^{\circ}\text{C}, unless otherwise noted.})$

| PARAMETER                              | SYMBOL                   | CONDITIONS/COMMENTS                    | MIN   | TYP   | MAX  | UNITS |

|----------------------------------------|--------------------------|----------------------------------------|-------|-------|------|-------|

| Input Low Voltage                      | VIL <sub>SPI</sub>       |                                        | 0     |       | 0.8  | V     |

| Input Current                          | I <sub>L_SPI</sub>       |                                        | -1    |       | 1    | μΑ    |

| Input Capacitance                      | C <sub>SPI</sub>         |                                        |       | 5     |      | pF    |

| SPI INTERFACE OUTPUT (SD               | OO) <sup>9,10</sup>      |                                        |       |       |      |       |

| Output High Voltage                    | VOH <sub>SDO</sub>       |                                        | 2.4   |       | 3.31 | V     |

| Output Low Voltage                     | VOL <sub>SDO</sub>       |                                        | 0     |       | 0.4  | V     |

| High Impedance Input<br>Current        | I <sub>L_SDO</sub>       |                                        | -60   |       | 60   | μΑ    |

| Output Capacitance                     | C <sub>SDO</sub>         |                                        |       | 5     |      | pF    |

| RESET DIGITAL INPUT <sup>9,10</sup>    |                          |                                        |       |       | •    |       |

| Input High Voltage                     | VIH <sub>RESET</sub>     |                                        | 2.4   |       | 3.47 | V     |

| Input Low Voltage                      | VILRESET                 |                                        | 0     |       | 0.8  | V     |

| Input Current                          | I <sub>L_RESET</sub>     |                                        | -1    |       | 1    | μΑ    |

| Input Capacitance                      | C <sub>RESET</sub>       |                                        |       | 5     |      | pF    |

| Minimum Duration                       |                          |                                        |       | 10    |      | ns    |

| SDN_RESET Specifications <sup>9,</sup> | 10                       |                                        |       |       |      |       |

| Input High Voltage                     | VIH <sub>SDN_RESET</sub> |                                        | 2.4   |       | 3.47 | V     |

| Input Low Voltage                      | VIL <sub>SDN_RESET</sub> |                                        | 0     |       | 0.8  | V     |

| Input Current                          | I <sub>L_SDN_RESET</sub> |                                        | -10   |       | 10   | μΑ    |

| Input Capacitance                      | C <sub>SDN_RESET</sub>   |                                        |       | 5     |      | pF    |

| POWER SUPPLIES                         |                          |                                        |       |       |      |       |

|                                        | HVCC                     |                                        | 12    |       | 55   | V     |

| Operation Range                        | HVEE                     |                                        | -55   |       | -12  | V     |

|                                        | VCC_5V                   |                                        | 4.9   | 5     | 5.5  | V     |

|                                        | Інусс                    | See PROGRAMMABLE<br>QUIESCENT CURRENT. |       | 22.5  | 26.5 | mA    |

| Quiescent Current<br>(Enabled)         | I <sub>HVEE</sub>        | See PROGRAMMABLE<br>QUIESCENT CURRENT. | -26.5 | -22.5 |      | mA    |

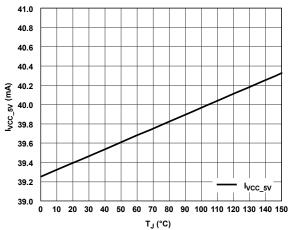

|                                        | I <sub>VCC_5V</sub>      |                                        |       | 39    | 41.5 | mA    |

analog.com Rev.0 8 of 75

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{SET} + 5 \text{ V}, R_{TERM} = 50 \Omega, R_{TERM} = 50$

| PARAMETER                       | SYMBOL                 | CONDITIONS/COMMENTS                     | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|------------------------|-----------------------------------------|------|------|------|-------|

|                                 | ,                      |                                         |      | 120  | 160  | μΑ    |

|                                 | I <sub>HVCC</sub>      | HVCC = + 12 V                           |      | 80   |      | μΑ    |

| Quiescent Current<br>(Shutdown) | 1                      |                                         | -160 | -120 |      | μΑ    |

| (Silucdowil)                    | I <sub>HVEE</sub>      | HVEE = −12 V                            |      | -80  |      | μΑ    |

|                                 | I <sub>VCC_5V</sub>    |                                         |      | 10.5 | 13.5 | mA    |

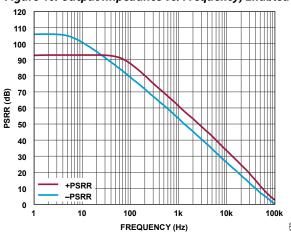

|                                 | PSRR <sub>HVCC</sub>   | HVCC = + 12 V to + 55 V, HVEE<br>= -50V |      | 93   |      | dB    |

| Power Supply Rejection<br>Ratio | PSRR <sub>HVEE</sub>   | HVCC = + 50 V, HVEE = -12 V<br>to -55 V |      | 106  |      | dB    |

|                                 | PSRR <sub>VCC_5V</sub> | VCC_5V = 4.9 V to + 5.5 V               |      | 86   |      | dB    |

- <sup>1</sup> Large signal bandwidth may be limited by thermal design. Refer to *Thermal Management* section.

- <sup>2</sup> These specifications are referred to the output of the AD8460.

- <sup>3</sup> FSR = Full scale range

- <sup>4</sup> This output voltage swing is set by the device's default configuration.

- <sup>5</sup> See *Thermal Management* section for more details.

- <sup>6</sup> The AD8460 has been lifetime tested with a 1 nF load, driven with an 80 Vp-p square wave at 1 kHz.

- <sup>7</sup> See the VREF\_5V section for details on the effects of supply variations on this pin.

- <sup>8</sup> The absolute maximum junction temperature is 150°C.

- <sup>9</sup> Guaranteed by design and characterization, not production tested.

- $^{10}$  T<sub>J</sub> = 30 °C to 105 °C

analog.com Rev.0 9 of 75

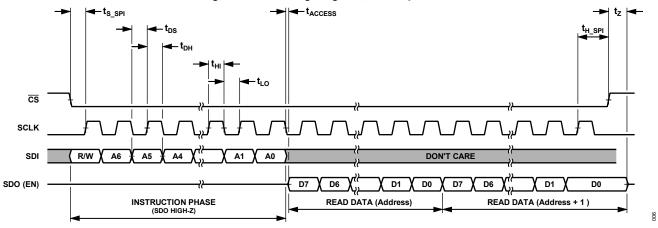

## **Table 2. TIMING CHARACTERISTICS**

$(HVCC = +50 \text{ V}, HVEE = -50 \text{ V}, SET\_IQ = 0x00, VCC\_5V = +5 \text{ V}, VREF\_5V = +5 \text{ V}, REFIO\_1P2V = +1.2 \text{ V}, R_{TERM} = 50 \ \Omega, R_{SET} = 0 \text{ EV}, R_{SET} =$

| PARAMETER                    | SYMBOL              | CONDITIONS/COMMENTS                          | MIN | TYP | MAX | UNITS |

|------------------------------|---------------------|----------------------------------------------|-----|-----|-----|-------|

| SYNC CLOCK RATE <sup>1</sup> |                     |                                              |     |     |     |       |

| Maximum Clock Rate           | SYNC <sub>AWG</sub> | AWG Mode (Parallel Data Inputs) <sup>2</sup> |     | 100 |     | MHz   |

| Maximum Clock Rate           | SYNC <sub>APG</sub> | APG Mode (Serial Data Inputs)                |     | 20  |     | MHz   |

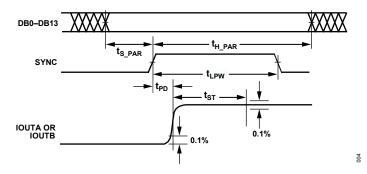

| PARALLEL TIMING <sup>1</sup> |                     |                                              |     |     |     |       |

| Input Setup Time             | t <sub>S_PAR</sub>  |                                              | 4   |     |     | ns    |

| Input Hold Time              | t <sub>H_PAR</sub>  |                                              | 4   |     |     | ns    |

| Latch Pulse Width            | t <sub>LPW</sub>    |                                              | 4   |     |     | ns    |

| Output Propagation Delay     | t <sub>PD</sub>     |                                              |     | 45  |     | ns    |

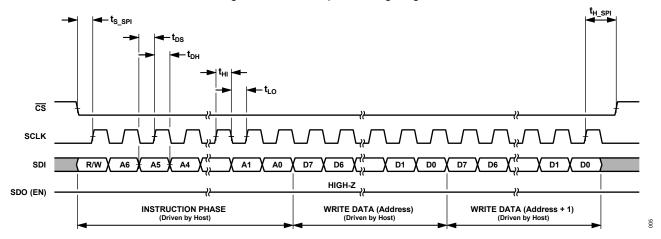

| SPI TIMING <sup>1</sup>      |                     |                                              |     |     |     |       |

| SCLK Frequency               | f <sub>SCLK</sub>   |                                              |     |     | 20  | MHz   |

| Pulse Width High             | t <sub>HI</sub>     |                                              | 24  |     |     | ns    |

| Pulse Width Low              | t <sub>LO</sub>     |                                              | 20  |     |     | ns    |

| Setup CS to SCLK Edge        | t <sub>S_SPI</sub>  |                                              | 5   |     |     | ns    |

| Hold SCLK to CS High         | t <sub>H_SPI</sub>  |                                              | 5   |     |     | ns    |

| Setup Time SDI to SCLK High  | t <sub>DS</sub>     |                                              | 5   |     |     | ns    |

| Hold Time SDI to SCLK Low    | t <sub>DH</sub>     |                                              | 5   |     |     | ns    |

| Data Valid SCLK to SDO       | t <sub>ACCESS</sub> |                                              |     |     | 10  | ns    |

| SDO Data Release             | tz                  |                                              |     |     | 10  | ns    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not production tested.

analog.com Rev.0 | 10 of 75

<sup>&</sup>lt;sup>2</sup> For details on the maximum achievable output frequency, see *Figure 26* and *Thermal Management* section.

# **Timing Diagrams**

Figure 4. Parallel Inputs Timing Diagram

Figure 5. SPI Timing Diagram (Write Operation)

Figure 6. SPI Timing Diagram (Read Operation)

analog.com Rev.0 11 of 75

**AD8460**

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$  °C, unless otherwise specified.

**Table 3. Absolute Maximum Ratings**

| PARAMETER                                           | RATING                                                   |

|-----------------------------------------------------|----------------------------------------------------------|

| HVCC to HVEE                                        | 115V                                                     |

| OUT                                                 | HVEE - 0.3V to HVCC + 0.3V                               |

| COMP_H                                              | HVCC - 5V to HVCC + 0.3V                                 |

| COMP_L                                              | HVEE - 0.3V to HVEE + 5V                                 |

| COMP_T to GND                                       | -0.3V to VCC_5V + 0.3V                                   |

| VCC_5V to GND                                       | -0.3V to +6V                                             |

| SYNC, DB0 – DB13 to GND                             | -0.3V to DVDD_3P3V + 0.3V                                |

| VREF_5V to GND                                      | -0.3V to VCC_5V + 0.3V or +5.85 V<br>(whichever is less) |

| DVDD_3P3V to GND                                    | -0.3V to 3.6V                                            |

| AVDD_3P3V to GND                                    | -0.3V to 3.6V                                            |

| SCLK, /CS, SDIO, SDO to GND                         | -0.3V to VCC_5V + 0.3V                                   |

| REFIO_1P2V to GND                                   | -0.3V to AVDD_3P3V + 0.3V                                |

| FS_ADJ to GND                                       | -0.3V to AVDD_3P3V + 0.3V                                |

| IOUTP, IOUTN to GND                                 | -1V to AVDD_3P3V + 0.3V                                  |

| SYNC Clock to GND                                   | -0.3V to DVDD_3P3V +0.3V                                 |

| RESET to GND                                        | -0.3V to VCC_5V + 0.3V                                   |

| SDN_IO, SDN_RESET to GND                            | -0.3V to VCC_5V + 0.3V                                   |

| TMP to GND                                          | -0.3V to VCC_5V + 0.3V                                   |

| Storage Temperature Range                           | −65°C to +150°C                                          |

| Operating Temperature Range <sup>1</sup>            | −40°C to +85°C                                           |

| Junction Temperature (T <sub>J</sub> ) <sup>2</sup> | +150°C                                                   |

| Peak Solder Reflow Temperature <sup>3</sup>         | IPC/JEDEC J-STD-020                                      |

<sup>&</sup>lt;sup>1</sup> Subject to T<sub>J</sub> <=150 °C

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

analog.com Rev.0 | 12 of 75

Extended operation of Tj at or near the absolute maximum junction temperature rating accelerates device aging. Ensure proper thermal management.

<sup>&</sup>lt;sup>3</sup> RoHS-compliant assemblies (20 sec to 40 sec)

## **Thermal Resistance**

Thermal performance is directly linked to PCB design and operating environment. Close attention to PCB thermal design is required. To keep the junction temperature (T<sub>J</sub>) below the absolute maximum rating, it is typically required to incorporate thermal management techniques. See the *Thermal Management* section for more details.

$\theta_{JA}$  is the natural convection, junction-to-ambient thermal resistance.  $\theta_{JC}$  is the junction-to-case thermal resistance.

#### **Table 4. Thermal Resistance**

| Package Type <sup>1</sup> | $\theta_{JA}^2$ | $\theta_{JC}^3$ | $\theta_{JC}^2$ | Unit |

|---------------------------|-----------------|-----------------|-----------------|------|

| 80-Lead TQFP (SV-80-7)    | 39.5            | 1.1             | 2.3             | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values based on JEDEC JESD-51. For  $\theta_{JA}$  with heatsink and airflow. See the *Thermal Management* section.

# **Electrostatic Discharge (ESD)**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only. Human body model (HBM) per ANSI/ESDA/JEDEC JS-001. Field induced charged device model (FICDM) per ANSI/ESDA/JEDEC JS-002.

Table 5. AD8460 80-Lead TQFP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | ± 1000                  | 1C    |

| FICDM     | ± 1000                  | C3    |

## **ESD Caution**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev.0 | 13 of 75

<sup>&</sup>lt;sup>2</sup> Includes derating across the die.

<sup>&</sup>lt;sup>3</sup> Equal power dissipation across the die.

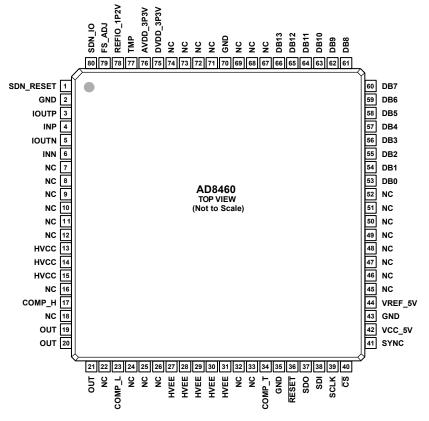

**AD8460**

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. NC = NO CONNECT. DO NOT CONNECT. THIS PIN SHOULD BE SOLDERED DOWN ONTO A FLOATING PAD.

2. EXPOSED THERMAL PAD. ELECTRICALLY CONNECTED TO GND INTERNALLY. CONNECT TO EXTERNAL HEAT SINK (GROUNDED OR FLOATING) FOR THERMAL MANAGEMENT.

200

Figure 7. Top View with Pin 1 in Upper Left and Pin Numbers Ascending Anticlockwise

## **Table 6. Pin Function Descriptions**

| PIN     | NAME      | DESCRIPTION                                                                                                                                              |  |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | SDN_RESET | Shutdown reset input (active high).                                                                                                                      |  |

| 2       | GND       | Ground (analog and digital).                                                                                                                             |  |

| 3       | IOUTP     | DAC current output. Connect to INP. Requires an external, precision, low drift 50 $\Omega$ with 0.1% tolerance resistor from IOUTP to GND.               |  |

| 4       | INP       | High voltage driver noninverting input. Connect to IOUTP.                                                                                                |  |

| 5       | IOUTN     | DAC complementary current output. Connect to INN. Requires an external, precision, low drift 50 $\Omega$ with 0.1% tolerance resistor from IOUTN to GND. |  |

| 6       | INN       | High voltage driver inverting input. Connect to IOUTN.                                                                                                   |  |

| 7 to 12 | NC        | Do not connect. This pin should be soldered down onto a floating pad.                                                                                    |  |

Rev.0 14 of 75 analog.com

| 13 to 15 | HVCC        | High voltage positive power supply.                                                                                                                                                                                          |  |  |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16       | NC          | Do not connect. This pin should be soldered down onto a floating pad.                                                                                                                                                        |  |  |

| 17       | COMP_H      | High side compensation. Depending on capacitive load drive requirements, this may be left floating or connected to OUT through a capacitor. See the <i>OUTPUT COMPENSATION (COMP_H AND COMP_L)</i> section for more details. |  |  |

| 18       | NC          | Do not connect. This pin should be soldered down onto a floating pad.                                                                                                                                                        |  |  |

| 19 to 21 | OUT         | High voltage analog output.                                                                                                                                                                                                  |  |  |

| 22       | NC          | Do not connect. This pin should be soldered down onto a floating pad.                                                                                                                                                        |  |  |

| 23       | COMP_L      | Low side compensation. Depending on capacitive load drive requirements, this may left floating or connected to OUT through a capacitor. See the <i>OUTPUT COMPENSATIO</i> (COMP_H AND COMP_L) section for more details.      |  |  |

| 24 to 26 | NC          | Do not connect. These pins should be soldered down onto a floating pad.                                                                                                                                                      |  |  |

| 27 to 31 | HVEE        | High voltage negative power supply.                                                                                                                                                                                          |  |  |

| 32 to 33 | NC          | Do not connect. These pins should be soldered down onto a floating pad.                                                                                                                                                      |  |  |

| 34       | COMP_T      | Thermal monitor compensation. Connect a 0.1 μF capacitor to GND.                                                                                                                                                             |  |  |

| 35       | GND         | Ground (analog and digital).                                                                                                                                                                                                 |  |  |

| 36       | RESET       | Digital reset (active low, 3.3 V logic).                                                                                                                                                                                     |  |  |

| 37       | SDO         | SPI serial data output (3.3 V logic).                                                                                                                                                                                        |  |  |

| 38       | SDI         | SPI serial data input (3.3 V logic)                                                                                                                                                                                          |  |  |

| 39       | SCLK        | SPI serial clock input (3.3 V logic).                                                                                                                                                                                        |  |  |

| 40       | cs          | SPI chip select input (active low, 3.3 V logic).                                                                                                                                                                             |  |  |

| 41       | SYNC        | Sync clock input for internal DAC data (3.3 V logic).                                                                                                                                                                        |  |  |

| 42       | VCC_5V      | Low voltage power supply (5 V).                                                                                                                                                                                              |  |  |

| 43       | GND         | Ground (analog and digital).                                                                                                                                                                                                 |  |  |

| 44       | VREF_5V     | Reference voltage for analog low voltage and protection threshold DACs. Connect VREF_5V to an external 5 V reference or VCC_5V (reduced accuracy). See the <i>VREF_5V</i> section for more details on power sequencing.      |  |  |

| 45 to 52 | NC          | Do not connect. This pin should be soldered down onto a floating pad.                                                                                                                                                        |  |  |

| 53       | DB0         | DAC LSB (3.3 V logic). AWG mode data input. DB0 must be NC or floated in APG mode.                                                                                                                                           |  |  |

| 54 to 65 | DB1 to DB12 | DAC data bits [1:12] (3.3 V logic). AWG mode data inputs. DB1 to DB12 must be NC or floated in APG mode.                                                                                                                     |  |  |

| 66       | DB13        | DAC MSB (3.3 V logic). AWG mode data input. DB13 must be NC or floated in APG mode                                                                                                                                           |  |  |

| 67 to 69 | NC          | Do not connect. These pins should be soldered down onto a floating pad.                                                                                                                                                      |  |  |

| 70       | GND         | Ground (analog and digital).                                                                                                                                                                                                 |  |  |

| 71 to 74 | NC          | Do not connect. This pin should be soldered down onto a floating pad.                                                                                                                                                        |  |  |

| 75       | DVDD_3P3V   | Digital supply bypass. Connect directly to AVDD_3P3V. Requires 0.1 μF capacitor to GND.                                                                                                                                      |  |  |

analog.com Rev.0 | 15 of 75

| 76 | AVDD_3P3V  | Analog supply bypass. Output of internal 3.3 V LDO. Requires 0.1 μF capacitor to GND.                                                                                               |  |

|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 77 | TMP        | Junction temperature monitor output voltage.                                                                                                                                        |  |

| 78 | REFIO_1P2V | Reference input/output for internal DAC. Connect to external 1.2 V reference or output of 1.2 V reference output (reduced accuracy). Requires 0.1 $\mu$ F capacitor to GND.         |  |

| 79 | FS_ADJ     | DAC full-scale current output adjust. Requires $2 \text{ k}\Omega$ resistor to GND. For more information about full-scale adjustment, see the <i>FULL-SCALE ADJUSTMENT</i> section. |  |

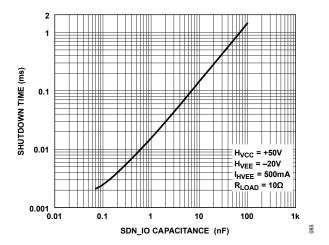

| 80 | SDN_IO     | Shutdown input/output (Shutdown active high). Connect capacitor to GND for shutdown delay.                                                                                          |  |

|    | EPAD       | Exposed thermal pad. Electrically connected to GND internally. Connect to external heat sink (grounded or floating) for thermal management.                                         |  |

analog.com Rev.0 | 16 of 75

**AD8460**

## INTERPRETING TYPICAL PERFORMANCE CURVES

The AD8460's performance parameters are fundamentally dependent on junction temperature  $(T_J)$ , which may be significantly higher than ambient temperature  $(T_A)$ . For this reason, all AD8460 typical performance curves (TPCs) relating to temperature are represented as a function of  $T_J$  (axis at bottom of plot), which can be measured through the TMP pin. See the TMP section for information on direct die temperature measurement.

To present a complete picture,  $T_A$  is shown as an alternative scale at the top of the plot. Refer to  $T_A$  scale for estimation of junction temperature when the TMP pin is not monitored. The relation between TJ and TA is valid for the default thermal management configuration and the specified test conditions indicated for each plot. See the *Thermal Management* section for the relationship among  $T_J$ ,  $T_A$ , and power dissipation.

Finally, note that each curve on a temperature—based TPC has both a solid and a dashed section. The solid portion represents typical performance that is exhibited when using the recommended passive heat sinking configuration. The dashed portion represents typical performance that is achievable when using active thermal management, such as with forced air or liquid cooling. See the *Thermal Management* section for more information.

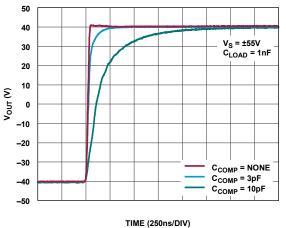

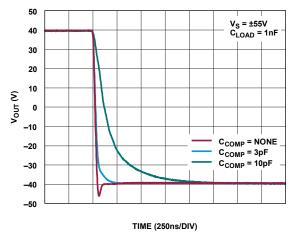

# TYPICAL PERFORMANCE CHARACTERISTICS

HVCC = +50 V, HVEE = -50 V, SET\_IQ = 0x00, VCC\_5V = +5 V, VREF\_5V = +5 V, REFIO\_1P2V = +1.2 V, R<sub>TERM</sub> = 50  $\Omega$ , R<sub>SET</sub> to FS\_ADJ = 2 k $\Omega$ , COMP\_L, COMP\_H = 0 pF, C<sub>LOAD</sub> = 1 nF, T<sub>C</sub> = 30°C, unless otherwise noted.

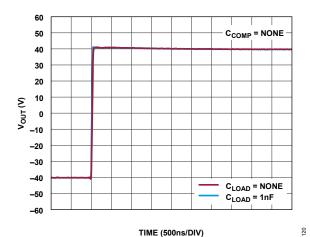

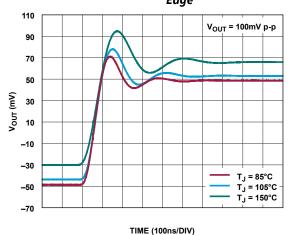

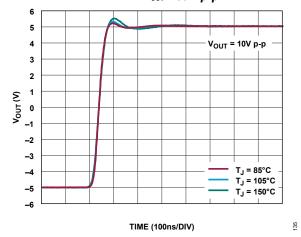

Figure 8. Large Signal Pulse Response vs.  $C_{COMP}$ , Rising Edge,  $C_{LOAD} = 1 \text{ nF}$

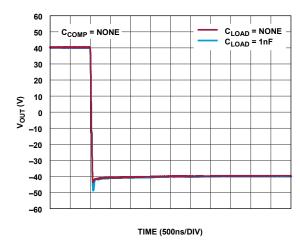

Figure 9. Falling Edge - Large Signal Pulse Response vs.

CCOMP, Falling Edge, CLOAD = 1 nF

analog.com Rev.0 | 17 of 75

Figure 10. Large Signal Pulse Response vs. CLOAD, Rising Edge

Figure 12. Large Signal Pulse Response vs. Edge Speed,  $C_{LOAD} = 1 \text{ nF}, C_{COMP} = \text{None}$

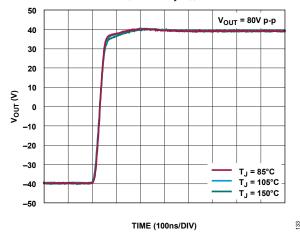

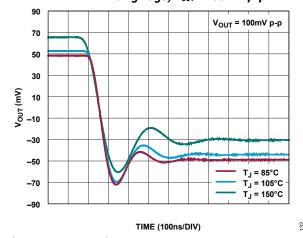

Figure 14. Large Signal Pulse Response vs. Temperature, Rising Edge

Figure 11. Large Signal Pulse Response vs. CLOAD, Falling Edge

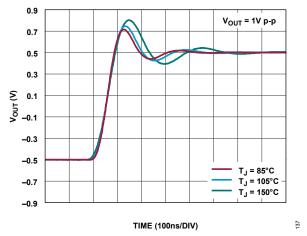

Figure 13. Small Signal Pulse Response vs. Temperature, Rising Edge,  $V_{OUT}$  = 100 mV p-p

Figure 15. Small Signal Pulse Response vs. Temperature, Falling Edge,  $V_{OUT} = 100 \text{ mV p-p}$

analog.com Rev.0 | 18 of 75

Figure 16. Large Signal Pulse Response vs. Temperature, Falling Edge

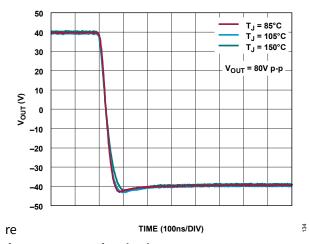

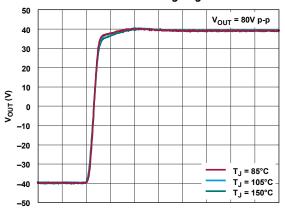

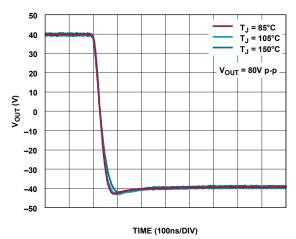

Figure 18. Pulse Response vs. Temperature, Rising Edge,  $V_{OUT}$  = 80 V p-p

TIME (100ns/DIV)

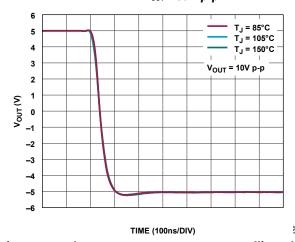

Figure 20. Pulse Response vs. Temperature, Rising Edge,  $V_{OUT} = 10 \text{ V p-p}$

Figure 17. Pulse Response vs. Temperature, Falling Edge,  $V_{OUT} = 80 \text{ V p-p}$

Figure 19. Pulse Response vs. Temperature, Falling Edge,  $V_{OUT}$  = 10 V p-p

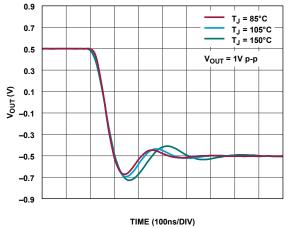

Figure 21. Pulse Response vs. Temperature, Falling Edge,  $V_{\text{OUT}} = 1 \text{ V } p\text{-}p$

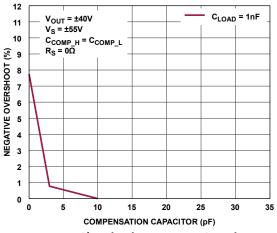

analog.com Rev.0 | 19 of 75

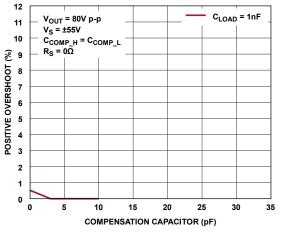

Figure 22. Pulse Response vs. Temperature, Rising Edge,  $V_{OUT} = 1 \text{ V } p\text{-}p$

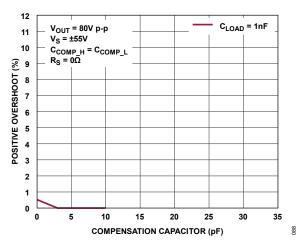

Figure 24. Large Signal Pulse Response Overshoot vs.  $C_{LOAD}$  and  $C_{COMP}$ , Positive Overshoot

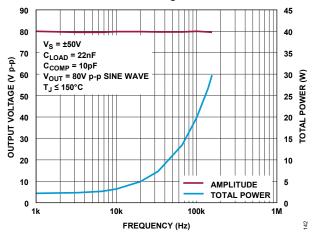

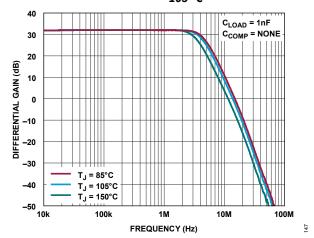

Figure 26. Large Signal Bandwidth, CLOAD = 1 nF, CCOMP = None

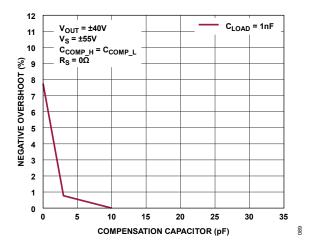

Figure 23. Large Signal Pulse Response Overshoot vs. CLOAD and CCOMP, Negative Overshoot

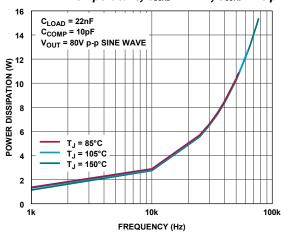

Figure 25. Large Signal Bandwidth,  $C_{LOAD}$  = 22 nF,  $C_{COMP}$  = 10 pF

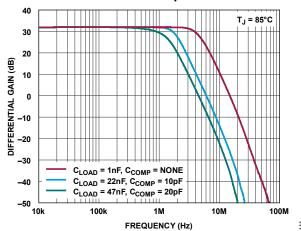

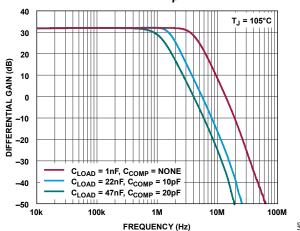

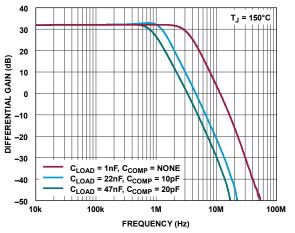

Figure 27. Small Signal Frequency Response vs. C<sub>LOAD</sub>, T<sub>J</sub> = 85 °C

analog.com Rev.0 | 20 of 75

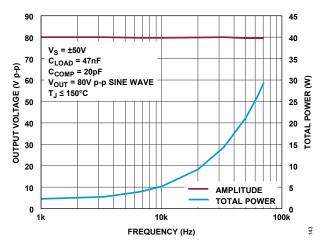

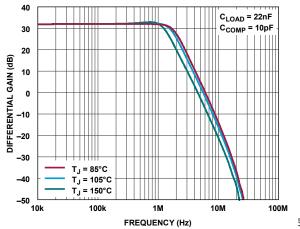

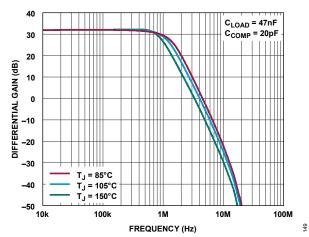

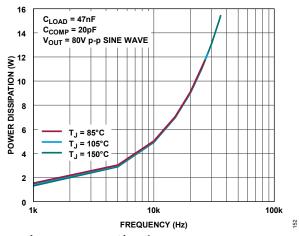

Figure 28. Large Signal Bandwidth,  $C_{LOAD}$  = 47 nF,  $C_{COMP}$  = 20 pF

Figure 30. Small Signal Frequency Response vs.  $C_{LOAD}$ ,  $T_J = 105 \, ^{\circ}\text{C}$

Figure 32. Small Signal Frequency Response vs. Temperature,  $C_{LOAD} = 1$  nF,  $C_{COMP} = None$

Figure 29. Small Signal Frequency Response vs.  $C_{LOAD}$ ,  $T_J = 150 \, ^{\circ}\text{C}$

Figure 31. Small Signal Frequency Response vs. Temperature,  $C_{LOAD} = 22 \text{ nF}$ ,  $C_{COMP} = 10 \text{ pF}$

Figure 33. Large Signal Frequency Response vs. Temperature,  $C_{LOAD} = 1$  nF,  $C_{COMP} = N$ one

analog.com Rev.0 | 21 of 75

**AD8460**

Figure 34. Small Signal Frequency Response vs. Temperature,  $C_{LOAD} = 47 \text{ nF}$ ,  $C_{COMP} = 20 \text{ pF}$

Figure 36. Large Signal Frequency Response vs. Temperature,  $C_{LOAD} = 22 \text{ nF}$ ,  $C_{COMP} = 10 \text{ pF}$

Figure 38. Slew Rate vs. Output Amplitude

Figure 35. Large Signal Frequency Response vs. Temperature, CLOAD = 47 nF, CCOMP = 20pF

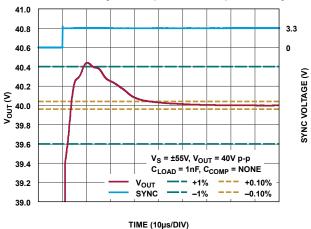

Figure 37. Settling Time to 0.1% and 1%,  $V_{OUT}$  = 40 Vp-p,  $V_S$  =  $\pm 55 V$ ,  $C_{LOAD}$  = 1 nF,  $C_{COMP}$  = None

Figure 39. Settling Time to 0.1% and 1%,  $V_{OUT}$  = 10 Vp-p,  $V_S$  =  $\pm 55 V$ ,  $C_{LOAD}$  = 1 nF,  $C_{COMP}$  = None

analog.com Rev.0 22 of 75

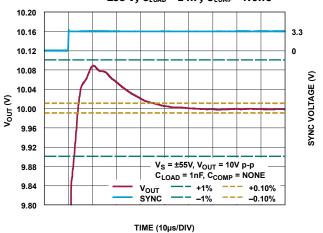

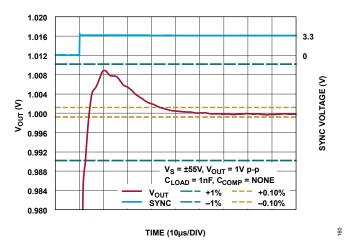

Figure 40. Settling Time to 0.1% and 1%,  $V_{OUT} = 1 \text{ Vp-p}$ ,  $V_S = \pm 55 \text{ V}$ ,  $C_{LOAD} = 1 \text{ nF}$ ,  $C_{COMP} = None$

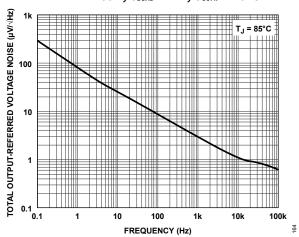

Figure 42. Total Output Noise vs. Frequency

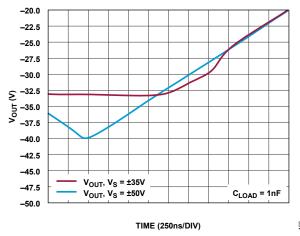

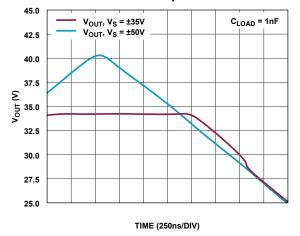

Figure 44. Output Overdrive Recovery vs. Time, Rising

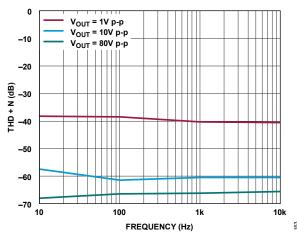

Figure 41. Total Harmonic Distortion and Noise vs.

Frequency at Various Large Output Swings

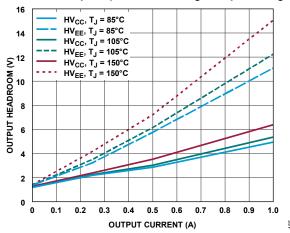

Figure 43. Output Headroom vs. Output Current and Temperature

Figure 45. Output Overdrive Recovery vs. Time, Falling

analog.com Rev.0 | 23 of 75

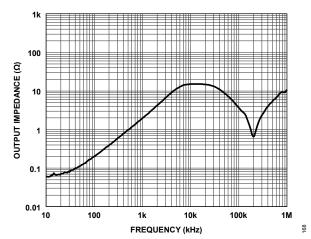

Figure 46. Output Impedance vs. Frequency, Enabled

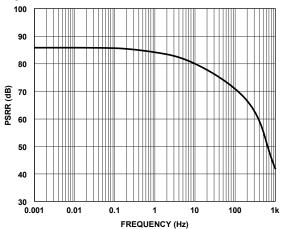

Figure 48. PSRR vs. Frequency, HVCC and HVEE,  $V_s = \pm 50 \text{ V}$

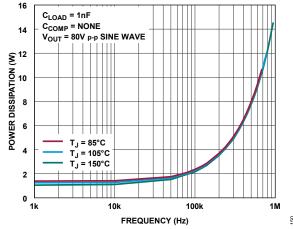

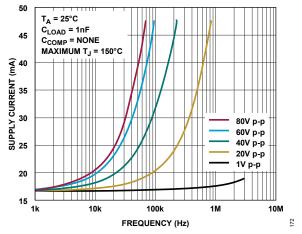

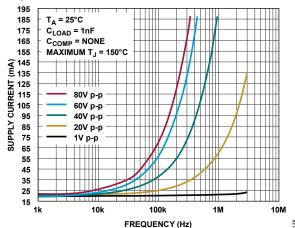

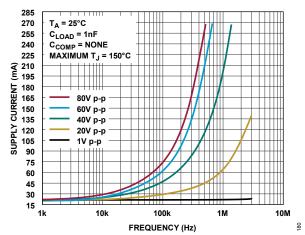

Figure 50. Supply Current and Amplitude vs. Frequency, Square Wave, No Heatsink, C<sub>LOAD</sub> = 1 nF, C<sub>COMP</sub> = None

Figure 47. Output Impedance vs. Frequency, Disabled

Figure 49. PSRR vs. Frequency, VCC\_5V, VCC\_5V = 5 V

Figure 51. Supply Current and Amplitude vs. Frequency Square Wave, with Heatsink,  $C_{LOAD} = 1$  nF,  $C_{COMP} = None$

analog.com Rev.0 24 of 75

**AD8460**

Figure 52. Supply Current and Amplitude vs. Frequency Square Wave, with Heatsink and Airflow,  $C_{LOAD} = 1$  nF,  $C_{COMP} = None$

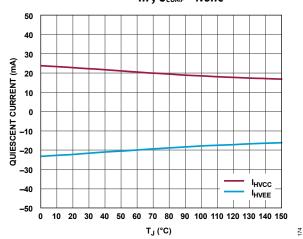

Figure 54. High Voltage Quiescent Supply Current vs. Temperature,  $V_s = \pm 50 \text{ V}$

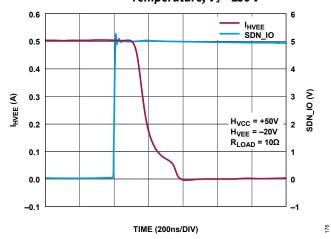

Figure 56. Shutdown Response vs. Time

Figure 53. Junction Temperature vs. Internal Power Dissipation

Figure 55. VCC\_5V Quiescent Supply Current vs. Temperature, VCC\_5V = 5 V

Figure 57. Shutdown Response vs. SDNIO Capacitance

analog.com Rev.0 | 25 of 75

# **TERMINOLOGY**

#### **Alarm**

Alarm refers to the detection of any of the five fault conditions monitored by the protection system: overcurrent (sourcing or sinking), overvoltage (positive or negative), or overtemperature. The alarm flag is customizable to either self-clear upon fault clear, or latch the alarm state as evidence of fault occurrence. When any alarm is latched, it must be cleared.

# **Analog Pattern Generation (APG) Mode**

The APG mode is analogous to the operation of a digital pattern generator. In the AD8460, an analog pattern of up to 16 sequential elements may be created, with each element containing an analog voltage rather than a digital voltage (logic state). Each analog voltage value is represented by 14-bit data. Voltage data is loaded serially through serial peripheral interface (SPI) into pattern memory prior to updating driver output. The APG mode is recommended for simple, repetitive waveforms consisting of sequential voltage levels.

# **Arbitrary Waveform Generation (AWG) Mode**

The AWG mode is analogous to the operation of an arbitrary waveform generator. Digital data is presented in parallel fashion to the DAC and the driver output is updated synchronously with the data transfer, allowing waveforms to be created in real time. The AWG mode is recommended for complex or non-repetitive waveforms.

#### Arm

To arm the protection system is to put the driver into a mode where it detects an alarm condition and shuts down the device.

#### Disarm

To disarm the driver is to put it into a state where it ignores an alarm condition and does not shut down the device. Use extreme caution when the driver is disarmed as it is unprotected from faults and possible damage.

#### **Fault**

A fault is any of the five overload conditions detectable by the protection system. Any fault triggers an alarm, though an alarm must exist for some minimum (user-adjustable) duration to force a shutdown.

# **Protection System**

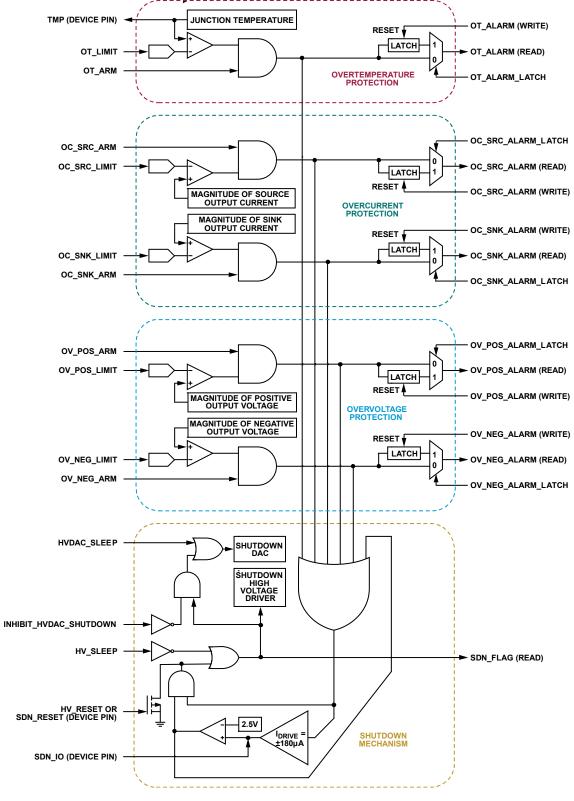

The protection system comprises limit-setting DACs, comparators, and logic gates that detect faults according to user-specified limits. See *Figure 64* for a block diagram showing basic functionality.

#### Reserved

Reserved refers to internal registers not for user access.

# **Safe Operating Area (SOA)**

The safe operating area is a two-dimensional envelope bounded by parameters the user must manage to prevent damage from overheating.

#### **Shutdown and Sleep**

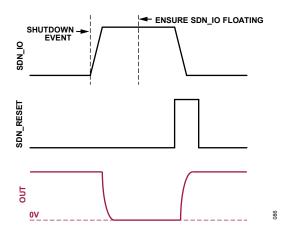

Both shutdown and sleep refer to a state of inactivity characterized by floating (high impedance) output and greatly reduced power consumption. Shutdown may be initiated by the user, by pulsing SDN\_IO high, or may be initiated by the protection system in response to an alarm of sufficient duration. If there is any parasitic or added capacitance to SDN\_IO, wait until the SDN\_IO voltage goes below its threshold voltage before trying to exit shutdown. To exit shutdown, use any of the following three ways:

Pulse SDN\_RESET high, then leave low.

analog.com Rev.0 26 of 75

- ▶ Pulse the HV\_RESET bit high through two SPI commands (drive high, then drive low).

- ▶ Pulse SDN\_IO low, then float.

Sleep refers to a non-latching state of inactivity like shutdown, but which is initiated (HV\_SLEEP = 0) and terminated (HV\_SLEEP = 1) through SPI commands. Sleep supersedes all commands that use the SDN\_IO shutdown mechanism, both fault-initiated and user-initiated. See *Figure 64* for a logic diagram of the protection system and shutdown mechanism.

# **Slew Boost**

Slew boost refers to a design feature of the AD8460 that increases supply current during fast input signal transitions, permitting faster output slew without the continuous power-dissipation penalty of conventional high-speed amplifiers.

# Span

Span refers to the difference between the highest and lowest output values. The AD8460 has a nominal span of 80 V (+40 V - (-40 V)).

analog.com Rev.0 27 of 75

Figure 58. AD8460 Standard Configuration

## **Overview**

The AD8460 is a "bits in, power out" high voltage, high-power, high-speed driver optimized for large output current (up to  $\pm 1$  A) and high slew rate (up to  $\pm 1800$  V/ $\mu$ s) at high voltage (up to  $\pm 40$  V) into capacitive loads. Combining a 14-bit high-speed DAC, a high voltage, high output current (HV-HI) analog driver, and fault monitoring and protection circuits, the AD8460 is ideally suited for high power applications such as arbitrary waveform generation (AWG), programmable power supplies, and high voltage automated test equipment (ATE).

The input to the system is provided as a 14 bit digital DAC code. The part can either operate in the analog pattern generation (APG) or arbitrary waveform generation (AWG) mode. In the APG mode, SPI communication is used to write up to 16 levels into digital registers, and clocking SYNC updates the output, serially proceeding to each next level in the table. In the AWG mode, the DAC uses 14 parallel digital inputs DB0 to DB13, and clocking SYNC updates the output. See *INPUT AND MODE OF OPERATION*.

With configurable DAC parameters  $R_{SET}$ ,  $V_{REFIO\_1P2V}$ , and  $R_{TERM} = 50 \Omega$ , the driver output transfer function is equal to:

$$V_{OUT} = \left(80 \text{ V} \times \left(\frac{DAC \text{ CODE}}{2^{14}}\right) - 40 \text{ V}\right) \times \left(\frac{2 \text{ k}\Omega}{R_{SET}}\right) \times \left(\frac{V_{REFIO_{1P2V}}}{1.2 \text{ V}}\right)$$

Under conventional  $V_{REFIO\ 1P2V} = 1.2 \text{ V}$ ,  $R_{SET} = 2 \text{ k}\Omega$ , and  $R_{TERM} = 50 \Omega$ , the driver output transfer function simplifies to:

$$V_{OUT} = \left(80 \text{ V} \times \left(\frac{DAC \text{ CODE}}{2^{14}}\right) - 40 \text{ V}\right)$$

analog.com Rev.0 28 of 75

The maximum output swing is established by the internal DAC configuration. See *FULL-SCALE ADJUSTMENT*.

The AD8460 requires dual high voltage (up to ±55 V) power supplies at HVCC and HVEE, and a single low voltage (5 V) power supply at VCC\_5V. The part generates 3.3 V internally from a LDO output at AVDD\_3P3V, and DVDD\_3P3V is an internal digital supply bypass point that should be connected to AVDD\_3P3V. See POWER SUPPLIES AND DECOUPLING.

A reference of 5 V is required at VREF\_5V to provide the reference voltage for analog low voltage and protection threshold DACs. Connect VREF\_5V to an external 5 V reference or to VCC\_5V (reduced accuracy). The AD8460 utilizes a reference of 1.2 V at REFIO\_1P2V to provide the reference voltage for the high-speed DAC. Connect REFIO\_1P2V to an external 1.2 V reference or float to use the internal 1.2 V reference, which can give rise to reduced accuracy. See *REFERENCE OPERATION*. An external resistor  $R_{SET}$  connected to FS\_ADJ establishes the internal DAC's reference current  $I_{REF}$ . When  $R_{SET} = 2 \text{ k}\Omega$ , as in *Figure 58*, the DAC's full scale complementary output currents are set to the nominal value of 20 mA. See *FULL-SCALE ADJUSTMENT*.

The DAC and the high-voltage, high-current (HV-HI) output driver can be connected externally through pin IOUTP and INP on the high side, and pin IOUTN and INN on the low side. The termination resistors (R\_{TERM}) set the inputs to the HV-HI driver. The R\_{TERM} resistors are recommended to be high precision 50  $\Omega$ . The % tolerance on the R\_{TERM} corresponds to possible error at the output. Typically, a tolerance of 0.1% is recommended in systems that balance precision and cost. 0.01% resistors are recommended for higher precision systems.

In addition to drive capability, the AD8460 provides a suite of features relating to fault monitoring and load protection. The part features a junction temperature monitor providing voltage at output indicating junction temperature up to 2.5 V at maximum junction temperature of 150 °C. The digital engine allows for programmable output current limit (source current and/or sink current), programmable output voltage limit (positive voltage and/or negative voltage), and programmable temperature limit (maximum junction temperature). See SHUTDOWN PROTECTION SETTINGS.

# INITIAL POWER-UP POWER SUPPLIES AND DECOUPLING

The AD8460 requires dual high voltage supplies in the range of  $\pm 12$  V to  $\pm 50$  V at HVCC and HVEE, as well as a single 5 V low voltage supply at VCC\_5V. Bypass all supply pins to ground using high quality, low ESR 0.1  $\mu$ F capacitors.

Place bypass capacitors as close to the supply pins as possible, with a short, direct connection to the PCB's analog ground plane. Additionally, place four 1.2  $\mu$ F ceramic capacitors from each high voltage supply to ground to provide good low frequency bypassing, and to provide the needed current to support large, fast-slewing signals. Low-inductance planes are recommended for high voltage supply routing.

AVDD\_3P3V is the analog supply bypass point for the internal 3.3 V LDO. AVDD\_3P3V requires a 0.1  $\mu$ F bypass capacitor from AVDD\_3P3V to GND. Connect AVDD\_3P3V to DVDD\_3P3V.

#### VREF 5V

VREF\_5V sets the reference voltage for internal alarm threshold DACs and needs to be biased. A precise 5 V reference IC is recommended. Alternatively, VREF\_5V can be connected to VCC\_5V (reduced accuracy).

analog.com Rev.0 29 of 75

A reduced accuracy VREF\_5V reference shifts the internal LDO reference voltage and causes the SDN\_IO shutdown voltage, overvoltage, and overtemperature thresholds to vary from table specified values. For example, if a 5 V reference with 1% tolerance at VREF\_5V is utilized, these levels may vary 1% from typical values.

The order of VCC\_5V and VREF\_5V power-on affects the initial state of the HV-HI driver. See *POWER SUPPLY SEQUENCING*.

## **POWER SUPPLY SEQUENCING**

DVDD\_3P3V must be tied to AVDD\_3P3V before power-up. The high voltage power supplies (HVCC and HVEE) and VCC\_5V may be brought up individually, in any order.

AD8460 can be powered up in shutdown or active mode. Powering the AD8460 in shutdown mode is recommended and this can be accomplished by powering on VCC\_5V before VREF\_5V. After initial power-up in shutdown mode, the SDN\_IO pin must be pulled low to ensure the AD8460 is turned on. Subsequently, floating the SDN\_IO pin enables the fault monitoring and protection feature while the AD8460 remains on. When powering down, bring VREF\_5V down first, then bring down VCC\_5V.

If VCC\_5V is powered on connected to VREF\_5V, the part powers on with the driver enabled and DAC disabled. Use extreme caution when powering up in active mode as the output voltage can power on at high voltage. This may result in high output current.

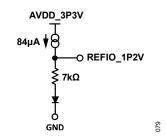

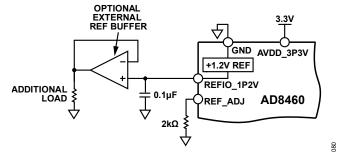

## REFERENCE OPERATION

The AD8460 internal DAC contains an internal 1.2 V band gap reference. The internal reference cannot be disabled, but can be easily overridden by an external reference for greater output accuracy. *Figure 59* shows a representative circuit of the band gap reference. Pin REFIO\_1P2V serves as either an output or an input depending on whether the internal or an external reference is used. To use the internal reference, simply decouple the REFIO\_1P2V pin to GND with a  $0.1~\mu F$  capacitor. The internal reference voltage is present at REFIO\_1P2V. If the voltage at REFIO\_1P2V is to be used anywhere else in the circuit, an external buffer amplifier with an input bias current of less than 100 nA should be used. *Figure 60* shows an example of buffered internal reference configuration.

Figure 59. Representative Circuit of Internal Reference

Figure 60. Buffered Internal Reference Configuration

analog.com Rev.0 30 of 75

**AD8460**

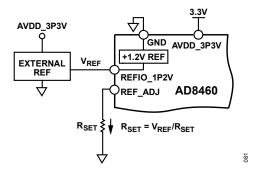

An external reference can be applied to REFIO\_1P2V, as shown in *Figure 61*. The external reference may provide either a fixed reference voltage to enhance accuracy and drift performance or a varying reference voltage for gain control. Note that the  $0.1\,\mu\text{F}$  compensation capacitor may not be required since the internal reference is overridden, and the relatively high input impedance of REFIO\_1P2V minimizes loading of the external reference.

Figure 61. External Reference Configuration

# INPUT AND MODE OF OPERATION

The AD8460 can generate waveforms in either the analog pattern generation (APG) or arbitrary waveform generation (AWG) mode.

The APG mode is used when the desired waveform is a series of sequential DC voltage levels, and edge speed control is not a requirement. In the APG mode, a pattern of up to 16 discrete DC voltage levels is loaded serially into pattern memory through the SPI. After a pattern is loaded, SYNC is used to clock pattern data to the output. 14-bit data is latched into the DAC on the rising edge of SYNC, and the data pointer advances to the next register on the subsequent falling edge. After the final value in pattern memory is sent to the DAC, the data pointer returns to the first data register and the pattern loops as long as SYNC is clocked. In the APG mode, the parallel data port (pins DB13:DB0) must be floated, as these pins are driven internally by the digital engine.

In the AWG mode, 14-bit digital input data representing the desired waveform is loaded through the parallel interface (pins DB13:DB0) and clocked in on the rising edge of SYNC, corresponding to conventional parallel mode high-speed DAC usage to update the output. The AWG mode is used when complex waveforms, specific edge speeds, or digital predistortion are required. *Table 7* briefly compares the APG and AWG input modes.

Table 7. Comparing the APG and AWG Input Modes

| Mode | Input Type         | Output Waveform   | Adjustable<br>Edge<br>Speed | Pre-<br>distortion      |

|------|--------------------|-------------------|-----------------------------|-------------------------|

| APG  | Serial through SPI | Pulses            | Limited to<br>16 levels     | Limited to<br>16 levels |

| AWG  | Parallel           | Complex waveforms | Yes                         | Yes                     |

analog.com Rev.0 | 31 of 75

# **ANALOG PATTERN GENERATION (APG)**

To enable the APG mode, set the APG\_MODE\_ENABLE bit to (1) in the CTRL\_REG\_02 register and then set WAVE\_GEN\_MODE bit to (1) in the CTRL\_REG\_00 register.

The pattern is generated in non-real time and data is loaded serially through SPI into pattern memory prior to updating the driver output. The SYNC signal loads the DAC input on its rising edge based on the values in the pattern memory in the HVDAC\_DATA\_REGMAP and updates the driver output on its falling edge. The pattern loops if SYNC is pulsed. The maximum SYNC rate for APG mode is 20 MHz.

In HVDAC\_DATA\_REGMAP, each 14 bit level is stored in a combination of two 8 bit registers, containing the low order byte and high order byte. For example, the first level in the pattern is stored in HVDAC\_DATA\_BYTE\_00 and HVDAC\_DATA\_BYTE\_01, If the first level is 14 bit binary sequence  $b_{13}b_{12}b_{11}b_{10}b_9b_8b_7b_6b_5b_4b_3b_2b_1b_0$ , HVDAC\_DATA\_BYTE\_00 contains the 8 low order bits (binary  $b_7b_6b_5b_4b_3b_2b_1b_0$ ), and HVDAC\_DATA\_BYTE\_01 contains the 8 high order bits (binary  $b_9b_9b_1a_1b_1a_1b_2a_1b_1a_1b_2a_1b_1a_1b_2a_1b_1a_1b_2a_1b_1a_1b_1a_1b_2a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1a_1b_1$

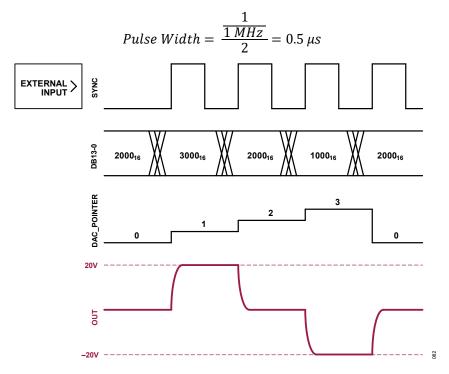

The default pattern memory value produces a 4-level, ±20 V up-down sequential staircase waveform at a frequency defined by the SYNC clock rate, as shown in *Figure 62*. These default values may be overwritten through SPI. The APG mode generates analog pattern of up to 16 sequential voltage levels. The pulse width for each voltage level is defined by the SYNC clock rate and can be calculated by:

$$Pulse\ Width = \frac{\frac{1}{SYNC\ Clock\ Rate}}{\#\ of\ Sequential\ Voltage\ Levels}$$

Assume the SYNC clock rate is 1 MHz and the output is a 2-level sequential pulse, the pulse width is:

Figure 62. APG Mode Reference Example

analog.com Rev.0 32 of 75

# **ARBITRARY WAVEFORM GENERATION (AWG)**

The AD8460 powers on by default in the AWG mode.

Clear the APG\_MODE\_ENABLE bit to 0 in the CTRL\_REG\_02 register and clear the WAVE\_GEN\_MODE bit to 0 in the CTRL\_REG\_00 register to select the AWG mode. The waveform is generated in real-time and data is loaded into registers through the parallel data port. The SYNC signal loads the HVDAC on its rising edge and updates the driver output on its falling edge. The maximum SYNC rate for the AWG mode is 100 MHz.

In the AWG mode, operation is essentially that of a high-speed DAC. The user provides 14-bit parallel data to pins DB0 to DB13 and provides a SYNC clock. Data is usually provided through the user field-programmable gate array (FPGA).

Figure 63. AWG Mode Reference Example

## PREDISTORTION AND ADJUSTABLE INPUT EDGE SPEED

Capacitive loading, cable length, and edge speed may produce distortion in the AD8460's transient settling characteristic, such as overshoot and ringing. The AWG mode allows the users to modify the waveform data to minimize this distortion. The modifications include adding an inverse characteristic to improve the shape of the response or adjusting the input edge to a slower speed.

The predistortion feature creates an input waveshape with undershoot, which can be used to compensate the overshoot for a given load. While this can be done in both the AWG and APG modes, the AWG mode provides higher resolution and therefore better distortion cancellation in all but the simplest waveforms.