## Evaluating the LTC9101-3/LTC9103 16-Port, IEEE 802.3at PSE Controller with Power Management and LED Control

## **FEATURES**

- ▶ 16 Port IEEE 802.3at-compliant PSE

- ▶ Autonomous Power Management with flash configuration

- ▶ Serial LED driver for Port LEDs

## **EVALUATION KIT CONTENTS**

- ▶ EVAL-LTC9101-3-AZ Daughter Card

- ► EVAL-LTC9101-3-MB-AZ Motherboard

## **DOCUMENTS NEEDED**

LTC9101-3/LTC9103 Datasheet

#### **ADDITIONAL HARDWARE NEEDED**

- ▶ DC Power Supply

- ▶ IEEE 802.3af/at Powered Device(s)

#### **SOFTWARE NEEDED**

Contact Analog Devices Applications for information regarding Custom Configurations.

#### **GENERAL DESCRIPTION**

The EVAL-LTC9101-3 is a 16-channel IEEE 802.3at compliant power sourcing equipment (PSE) with autonomous power management and serial LED driver for port LEDs. The EVAL-LTC9101-3 includes the EVAL-LTC9101-3-AZ daughter card, the EVAL-LTC9101-3-MB-AZ motherboard, and features the LTC9101-3 and LTC9103 PSE platform chipset.

In the EVAL-LTC9101-3, a single LTC9101-3 digital controller interfaces with up to two LTC9103, 8-channel, analog controllers for 16 power channels total. Up to sixteen IEEE 802.3af/at/bt powered devices (PDs) can be connected to the EVAL-LTC9101-3 and powered from this system using a single power supply.

The LTC9101-3 and LTC9103 use a proprietary isolated data interface allowing the LTC9101-3 to share the same logic supply as the host controller and eliminate the need for an additional isolated 3.3 V supply. The EVAL-LTC9101-3 operates completely autonomously without a host controller, including flash configuration for power management and port LEDs. Port Status and Fault LEDs quickly show PoE status for up to sixteen ports, including fault codes, driven by the LTC9101-3 using a serial LED driver. A Supply Overload LED warns if system power usage is near the power budget and indicates if port power is denied or revoked.

Robust surge protection is provided by design and on-board surge protection devices. An optional on-board buck regulator provides 3.3 V from the VEE supply for the digital circuits. This demonstration manual provides a quick start procedure and an EVAL-LTC9101-3 overview.

Design files for this circuit board are available at https://www.ana-log.com/EVAL-LTC9101-3

All registered trademarks and trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| -eatures 1                             | Main VEE PoE Supply   |   |

|----------------------------------------|-----------------------|---|

| Evaluation Kit Contents1               |                       |   |

| Documents Needed1                      | LED Indicators        | 7 |

| Additional Hardware Needed1            | Device Configuration  | 8 |

| Software Needed1                       | Custom Configurations | 8 |

| General Description1                   | Digital Connections   | 8 |

| EVAL-LTC9101-3 Evaluation Board Photo3 |                       |   |

| Quick Start Procedure4                 | Onboard 3.3 V Supply  | 8 |

| LTC9101-3 Evaluation Kit6              | Surge Testing         | 8 |

| Port Output6                           | Legacy Mode           | 8 |

| Daughter Card Insertion Precautions7   | Power Management      | g |

# **REVISION HISTORY**

7/2023—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 10

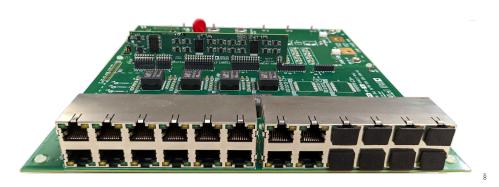

# **EVAL-LTC9101-3 EVALUATION BOARD PHOTO**

Figure 1. EVAL-LTC9101-3 Evaluation Board Photo

analog.com Rev. 0 | 3 of 10

## **QUICK START PROCEDURE**

# **EVAL-LTC9101-3 Operation**

The EVAL-LTC9101-3 includes the EVAL-LTC9101-3-AZ daughter card and EVAL-LTC9101-3-MB-AZ motherboard. This kit allows for evaluating the LTC9101-3/LTC9103 chipset configured as either an 8-port or 16-port, 802.3at PSE endpoint.

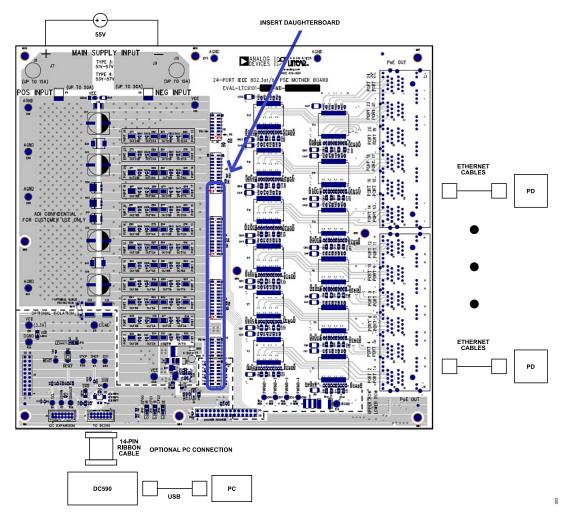

Follow the procedure below and refer to Figure 2 through Figure 4, and Table 1 for proper equipment setup and default configuration. This default setup automatically powers all valid PDs.

- 1. On the EVAL-LTC9101-3-MB-AZ motherboard, set LEGACY jumper JP14 to HI to only power IEEE 802.3 compliant PDs that present a valid detection signature.

- On the EVAL-LTC9101-3-MB-AZ motherboard, set the CFG1 (JP21) jumper to HI to enable all ports. For CFG1 options see Table 1.

Table 1. EVAL-LTC9101-3 CFG1 Jumper Settings

| Jumper      | _             |                |

|-------------|---------------|----------------|

| CFG1 (JP21) | # of LTC9103s | Max # of Ports |

| LO          | 1             | 8              |

| HI          | 2             | 16             |

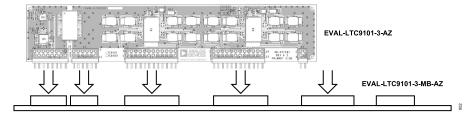

- 3. Align pin 1 of the 16-pin male connector P1 on the EVAL-LTC9101-3-AZ daughter card with pin 1 of the 16-pin female connector J11 on the EVAL-LTC9101-3-MB-AZ motherboard as shown in Figure 2. The five male connectors and five female sockets should match. Keyed pins in J12 assist with the alignment shown in Figure 3. Carefully push the daughter card straight down until the male and female connectors are flush with each other.

- 4. Connect a supply to the EVAL-LTC9101-3-MB-AZ motherboard with the positive rail to POS INPUT (+) and negative rail to NEG INPUT (-) as shown in Figure 3. Use a power supply capable of sourcing the system power budget, refer to Table 1. Ramp the supply up to within 51 V and 57 V.

**NOTE:** At start up, the Supply Overload LED ( $\overline{\text{OVR}}$ ), Status LEDs (Green LEDs on J3 and J4), and Fault LEDs (Yellow LEDs on J3 and J4) go through a default self test pattern. The power on self test pattern will be repeated on a LTC9101-3 reset. This does not affect PoE operation and the LEDs will be valid once the test pattern is complete.

**5.** Connect up to sixteen IEEE 802.3af/at/bt PDs to the mother-board's RJ45 connectors J3 and J4, as shown in Figure 4.

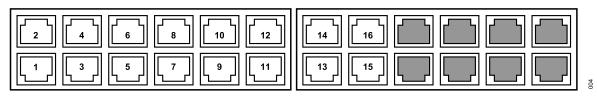

**NOTE:** RJ45 ports 17, 18, 19, 20, 21, 22, 23 and 24 on J3 are blocked on the EVAL-LTC9101-3-MB-AZ motherboard in the EVAL-LTC9101-3. See the section on Port Output for more information.

Figure 2. Inserting the EVAL-LTC9101-3-AZ Daughter Card into J1 through J5 of the EVAL-LTC9101-3-MB-AZ Motherboard

analog.com Rev. 0 | 4 of 10

# **QUICK START PROCEDURE**

Figure 3. EVAL-LTC9101-3 Connections

analog.com Rev. 0 | 5 of 10

EVAL-LTC9101-3 includes the EVAL-LTC9101-3-MB-AZ, 16-Port, 2-pair IEEE 802.3at PoE PSE motherboard for a PSE endpoint. This motherboard accepts an EVAL-LTC9101-3-AZ daughter card with sixteen power channels. It contains two, 2×6, RJ45 connectors and sixteen 1000BASE-T Ethernet transformers rated for PoE operation. The EVAL-LTC9101-3-MB-AZ motherboard also has switches, jumpers, and pushbuttons for configuring the PSE, with port LEDs and test points.

## **PORT OUTPUT**

The PDs are connected using an Ethernet cable (Cat5, Cat5e or better cabling as specified by IEEE 802.3) to any of the valid ports at the two, 2×6, RJ45 connectors J3 and J4 on the EVAL-LTC9101-3-MB-AZ motherboard. The LTC9101-3/LTC9103 delivers

power over one power channel. The term "channel" refers to the PSE circuitry assigned to a corresponding pairset. Each port is connected as a 2-pair port driven by a single power channel connected to Alternative A (pairs 1, 2 and 3, 6). Alternative B (pairs 4, 5 and 7, 8) is unpowered. Each port has a test point OUTnA which connects to Alternative A, pair 1, 2 for port n.

An IEEE 802.3at PSE uses a single power channel per port, connected to either Alternative A or Alternative B. EVAL-LTC9101-3-MB-AZ layout supports up to twenty four 4-pair ports with options for connecting Alternative A and Alternative B.

The EVAL-LTC9101-3 supports sixteen, 2-pair ports. Refer to See-Figure 4 for the port output map of the EVAL-LTC9101-3.

Figure 4. EVAL-LTC9101-3 Port Output Map

analog.com Rev. 0 | 6 of 10

#### DAUGHTER CARD INSERTION PRECAUTIONS

When inserting or removing the daughter card into the EVAL-LTC9101-3-MB-AZ motherboard, verify all supplies and LEDs are off. Push the card straight down for insertion or pull straight up for removal to avoid bending the connector pins. Follow the instructions in the Quick Start Procedure for alignment and see Figure 2.

# MAIN VEE POE SUPPLY

The VEE supply is the main PoE supply connected to the EVAL-LTC9101-3-MB-AZ motherboard. For proper connection and appropriate supply voltage ranges see Quick Start Procedure.

Choose a power supply with a limit set higher than the maximum system power budget. The banana jacks (J8 and J10) are sufficient for up to 15 A.

## **ISOLATION**

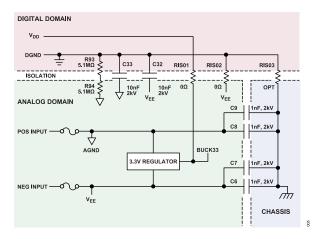

The IEEE 802.3 Ethernet specifications require network segments (including the analog PoE circuitry) to be electrically isolated from the chassis ground. The EVAL-LTC9101-3-MB-AZ motherboard and EVAL-LTC9101-3-AZ daughter card layouts and high voltage capacitors provide an isolation barrier between Analog and Digital domains. Transformers provide a galvanic barrier between DGND and AGND on the EVAL-LTC9101-3-AZ daughter card. By default, this isolation barrier is bridged by resistors on the motherboard to allow for evaluation using a single power supply. Remove RISO1 and RISO2, then provide an external 3.3 V supply between V<sub>DD</sub> and DGND to evaluate this board as an isolated system.

All RJ45 shields and terminations are connected to the chassis ground. AGND and  $V_{EE}$  each connect to the chassis ground with two pairs of 1 nF, 2 kV capacitors (C6-C9). AGND and  $V_{EE}$  also connect to DGND each with 10 nF, 2 kV capacitors (C32-C33). An optional 0  $\Omega$  resistor can be installed at RISO3 to tie the chassis ground to DGND. Two series 1206, 5.1  $M\Omega$  resistors connect between AGND and DGND for high voltage capacitance discharge. See Figure 5 for diagram of connections between Analog and Digital domains, as well as chassis ground on the EVAL-LTC9101-3-MB-AZ motherboard.

The EVAL-LTC9101-3-AZ daughter card is laid out with isolation.

Figure 5. Motherboard Power Supply Connections and Isolation Barriers

#### LED INDICATORS

The  $V_{EE}$  LED (D29) and  $V_{DD}$  LED (LED13) indicate if a voltage is present at the respective supplies. Verify these LEDs are off before inserting or removing the daughter card.

Each port has respective Status and Fault LEDs to indicate different states. Status is connected to a green LED while Fault is connected to a yellow LED. For default Port LED behavior see Table 2. The Supply Overload LED (OVR, LED14) indicates if power has been denied, revoked, or if the system is near the power budget. Status, Fault, and Supply Overload LED functions can be modified with a custom configuration package.

analog.com Rev. 0 | 7 of 10

Table 2. Default PoE Operation vs. port LEDs

|                                     | LED         |            |  |

|-------------------------------------|-------------|------------|--|

| Condition                           | Port Status | Port Fault |  |

| Detect Open                         | Off         | Off        |  |

| Port Powered                        | On          | Off        |  |

| Detect Invalid                      | Off         | Blink      |  |

| Class Invalid                       | Off         | Blink      |  |

| Inrush Fault                        | Off         | Blink      |  |

| $P_{CUT}$ , $I_{CUT}$ and $I_{LIM}$ | Off         | Blink      |  |

| DC Disconnect                       | Off         | Blink      |  |

| Power Denied                        | Blink       | Off        |  |

| Power Revoked                       | Blink       | Off        |  |

NOTE: Blink rate is 800ms on and 800ms off.

#### **DEVICE CONFIGURATION**

The CFG1 pin state during reset configures the number of analog controllers in the system. The CFG1 pin connects to a jumper that pulls either HI for a logical 1, or LO for logical 0. See Table 1 for the numbers of ports and LTC9103s set by CFG1 pin. CFG1 pin also sets the default system power budget and near-limit warning thresholds. See Power Management section for more information. The CFG0 and CFG2 jumpers must be set LO, to set the CFG0 and CFG2 pins to a logical 0.

## **CUSTOM CONFIGURATIONS**

An LTC9101-3/LTC9103 system may be configured in a variety of ways by storing a custom configuration package in a dedicated flash partition. If a stored configuration is utilized, CFG1 is still required to inform the LTC9101-3 how many analog controllers are in the system. Refer to the data sheet for more information and contact ADI Applications for assistance with generating custom configuration packages.

## **DIGITAL CONNECTIONS**

The DC590 USB to I $^2$ C controller board is connected to the EVAL-LTC9101-3-MB-AZ motherboard at J1 through a 14-pin ribbon cable. The LTC9101-3's I $^2$ C base address is 0x20. SDAOUT and SDAIN can be tied together through a shunt resistor, R73. Turrets on the EVAL-LTC9101-3-MB-AZ motherboard provide test points for SCL, SDAIN, SDAOUT, V<sub>DD</sub>, DGND, and  $\overline{\text{RESET}}$ .

## **RESET PUSHBUTTON**

Pushbutton switch SW1, when pressed, pulls the RESET pin of the daughter card logic low. The PSE controller is then held inactive with all ports off. When SW1 is released, RESET is pulled high, and the PSE returns to autonomous operation while OVR, Status, and Fault LEDs run through the LED power on self test.

#### **ONBOARD 3.3 V SUPPLY**

The EVAL-LTC9101-3-MB-AZ motherboard has an onboard (non-isolated) 3.3 V/1 A buck regulator that provides a local 3.3 V, with the net named BUCK33. This onboard logic supply is for demonstration purposes only and allows for use of a single supply while evaluating the EVAL-LTC9101-3.

## **SURGE TESTING**

The EVAL-LTC9101-3 can be configured with either the Digital domain connected to reference ground plane, or with the Digital domain floating with the Analog domain for different surge test setups. The default EVAL-LTC9101-3 configuration has DGND connected to  $V_{\text{FF}}$  and floating from chassis ground.

# **LEGACY MODE**

Legacy Mode operation is enabled with the  $\overline{\text{LEGACY}}$  pin, which is controlled by the  $\overline{\text{LEGACY}}$  jumper (JP15). If the  $\overline{\text{LEGACY}}$  jumper is LO, Legacy mode is enabled and legacy PDs with large common-mode capacitance (>10  $\mu$ F) will be powered. If the  $\overline{\text{LEGACY}}$  jumper is HI or floating, legacy mode is disabled and only valid IEEE 802.3 PDs will be powered. The  $\overline{\text{LEGACY}}$  pin state is continuously monitored.

analog.com Rev. 0 | 8 of 10

## **POWER MANAGEMENT**

The LTC9101-3 manages a user-defined system-level power budget across all ports. Port power is automatically assigned based on system power availability, initial physical classification and after power-up, port dynamic power consumption. The default system power budget is based off the maximum number of ports in the system, which is set by the CFG1 pin. See Table 3 for the default

Table 3. Default System Power Budget and Near-Limit Warning Thresholds

power management settings. The Supply Overload ( $\overline{\text{OVR}}$ ) LED turns on if it is near the power budget and blink if power is denied or revoked. The LTC9101-3 prioritizes port power by port number, sequentially (port 1 is highest priority). Refer to the data sheet for more information on the Power Management algorithm. The system power budget, warning levels, and port priority can be modified with a custom configuration package.

| CFG1 | Total Number of Ports | System Power Budget | Set Power Warning (OVR LED Turns On) | Power Warning Reset (OVR LED Turns Off) |

|------|-----------------------|---------------------|--------------------------------------|-----------------------------------------|

| LO   | 8                     | 64 W                | 49 W                                 | 45 W                                    |

| HI   | 16                    | 128 W               | 113 W                                | 109 W                                   |

analog.com Rev. 0 | 9 of 10

## **NOTES**

#### ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.