## **AM27LS00, AM27LS01**

## 256-Bit Low-Power Schottky Bipolar RAM

The AM27LS00/01 Family is comprised of fully decoded bipolar random-access memories for use in high-speed buffer memories. The memories are organized 256-words by 1-bit with an 8-bit binary address field and separate data in and data output lines. The memories have three active LOW chip select inputs and a three-state output (AM27LS00 devices) or open-collector output (AM27LS01 devices). All inputs are buffered to present an input load of only 0.5 TTL unit loads.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## Am27LS00/01 Series

256-Bit Low-Power Schottky Bipolar RAM

#### DISTINCTIVE CHARACTERISTICS

- High speed

- Internal ECL circuitry for optimum speed/power performance over voltage and temperature

- Output preconditioned during write to eliminate the write recovery glitch

- Available with three-state outputs or with open-collector outputs

#### GENERAL DESCRIPTION

The Am27LS00/01 Family is comprised of fully decoded bipolar random-access memories for use in high-speed buffer memories. The memories are organized 256-words by 1-bit with an 8-bit binary address field and separate data in and data output lines. The memories have three active LOW chip select inputs and a three-state output (Am27LS00 devices) or open-collector output (Am27LS01 devices). All inputs are buffered to present an input load of only 0.5 TTL unit loads.

Read/write operation is controlled by an active LOW write enable input. When the write enable is LOW and the chip is selected the data on the data input is written into the location specified by the address inputs. During this operation the output of the -1 device is active and inverts the value of DI (Write Transparent Operation). The other devices disable the output during the period  $\overline{\rm WE}$  is low. Reading is accomplished by having the chip selected and the write enable input HIGH. Data stored in the location specified by the address inputs is read out and appears on the data output inverted.

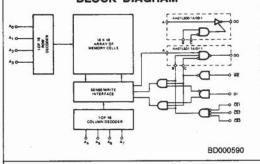

#### **BLOCK DIAGRAM**

#### MODE SELECT TABLE

| Input |    |    | Data Output                |              |  |  |

|-------|----|----|----------------------------|--------------|--|--|

| CS    | WE | DI | Status DO (tn+1)           | Mode         |  |  |

| н     | Х  | X  | Output Disabled            | No Selection |  |  |

| L     | L  | L  | Inverted/Disabled*         | Write '0'    |  |  |

| L     | L  | Н  | Inverted/Disabled*         | Write '1'    |  |  |

| L     | н  | Х  | Selected Bit<br>(Inverted) | Read         |  |  |

H = HIGH L = LOW X = Don't Care \*Inverted = -1 Devices Disabled = All Other Devices

#### PRODUCT SELECTOR GUIDE

| Temperature Range       |                   | C         | С          | М         | М          |

|-------------------------|-------------------|-----------|------------|-----------|------------|

| Access Time             |                   | 35 ns     | 1 4        | 5 ns      | 55 ns      |

| Part Number             | Write Transparent |           | Am27LS00-1 |           | Am27LS00-1 |

| Part Number Three-State | STD               | Am27LS00A | Am27LS00   | Am27LS00A | Am27LS00   |

|                         | Write Transparent |           | Am27LS01-1 |           | Am27LS01-1 |

| Open Collector          | STD               | Am27LS01A | Am27LS01   | Am27LS01A | Am27LS01   |

Publication # Rev. Amendment 03233 D /0

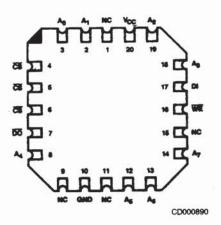

#### CONNECTION DIAGRAM Top View

\*Same pinouts apply to both Ceramic DIP and Flatpack.

Note: Pin 1 is marked for orientation.

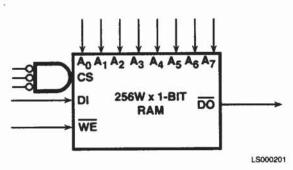

#### LOGIC SYMBOL

V<sub>CC</sub> = Power Supply GND = Ground

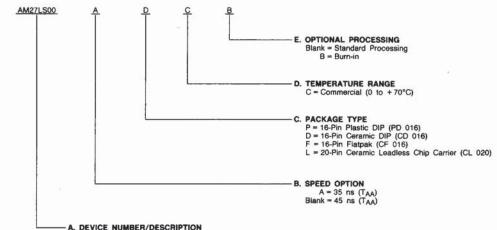

#### ORDERING INFORMATION (Cont'd.)

#### Standard Products

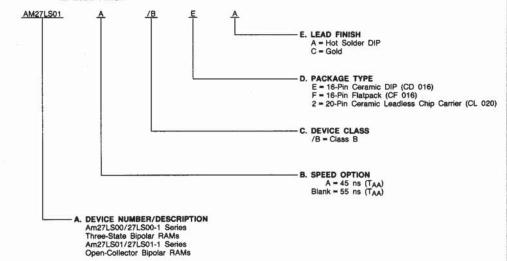

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

D. Temperature Range

- E. Optional Processing

A. DEVICE NUMBER/DESCRIPTION Am27LS00/27LS00-1 Series Three-State Bipolar RAMs Am27LS01/27LS01-1 Series Open-Collector Bipolar RAMs

| Va         | Valid Combinations   |  |  |  |  |  |  |

|------------|----------------------|--|--|--|--|--|--|

| AM27LS00   |                      |  |  |  |  |  |  |

| AM27LS00A  | 199 0000             |  |  |  |  |  |  |

| AM27LS00-1 | PC, PCB,<br>DC, DCB. |  |  |  |  |  |  |

| AM27LS01   | FC, FCB,             |  |  |  |  |  |  |

| AM27LS01A  | LC, LCB              |  |  |  |  |  |  |

| AM27LS01-1 |                      |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |               |   |  |  |  |

|--------------------|---------------|---|--|--|--|

| AM27LS00           |               |   |  |  |  |

| AM27LS00A          |               | - |  |  |  |

| AM27LS00-1         | /BEA,         |   |  |  |  |

| AM27LS01           | /BFA,<br>/B2C |   |  |  |  |

| AM27LS01A          | 7,520         |   |  |  |  |

| AM27LS01-1         |               |   |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65 to +            | 15000  |

|---------------------------------------|--------|

| Ambient Temperature with              | 150 0  |

| Power Applied55 to +                  | 10500  |

| Supply voltage to ground potential    |        |

| (Pin16 to Pin8) continuous0.5 \/ to + | 70 V   |

| DC Voltage Applied to Outputs         |        |

| for High Output State0.5 V to+ Vo-    | o may  |

| DC Input Voltage0.5 V to -            | Ciliax |

| Output Current, into Outputs          | - vcc  |

| DC Input Current30 mA to +            | U MA   |

| -30 mA to +                           | 5 mA   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

| Commercial (C) Devices |                |

|------------------------|----------------|

| Temperature            | 0 to +75°C     |

| Military (M) Devices   |                |

| Temperature            | 55 to +125°C   |

| Supply Voltage         | +4.5 to +5.5 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

See Note 4

## DC CHARACTERISTICS over operating range unless otherwise specified\*

| Parameter<br>Symbol                                                                                                | raidileter             |                                                                                 |                                                      |             |        | Тур.    |       |       |

|--------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-------------|--------|---------|-------|-------|

| VOH                                                                                                                |                        |                                                                                 | Min.                                                 | (Note 1)    | Max.   | Units   |       |       |

| (Note 2)                                                                                                           | Output HIGH Voltage    | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | IOH = -5.2 mA                                        | COM, L      | 2.4    | 3.2     |       |       |

| VOL                                                                                                                |                        |                                                                                 | IOH = -2.0 mA                                        | MIL         | 2.7    | 3.2     |       | Volts |

| VOL                                                                                                                | Output LOW Voltage     | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | IOL = 16 mA                                          |             |        | 0.3     | 0.45  | Volt  |

| ViH                                                                                                                | Input HIGH Level       | Guaranteed input to<br>(Note 3)                                                 | Guaranteed input logical HIGH voltage for all inputs |             |        |         |       | Volt  |

| VIL                                                                                                                | Input LOW Level        | Guaranteed input logical LOW voltage for all inputs (Note 3)                    |                                                      |             |        |         | 0.8   |       |

| ΙΙL                                                                                                                | input LOW Current      | V <sub>CC</sub> = Máx., V <sub>IN</sub> = 0.40 V                                |                                                      |             |        |         | 0.8   | Voit  |

| JIH .                                                                                                              | Input HIGH Current     | VCC = Max., VIN = 2.7 V                                                         |                                                      |             |        | - 0.030 | -0.25 | mA    |

| Isc                                                                                                                | Output Short Circuit   | 7.00                                                                            |                                                      |             |        | < 1     | 20    | μΑ    |

| (Note 2)                                                                                                           | Current                | V <sub>CC</sub> = Max., V <sub>OUT</sub> =                                      | 0.0 V                                                |             | -20    | -30     | -60   | mA    |

| lcc                                                                                                                | Power Supply Current   | All inputs = GND                                                                |                                                      | "A" version |        | 80      | 115   | -     |

| VCL                                                                                                                | land Ot.               | V <sub>CC</sub> = Max.                                                          |                                                      | Standard    |        | 55      | 70    | mA    |

| ·CL                                                                                                                | Input Clamp Voltage    | VCC = Min., I <sub>IN</sub> = -18 mA                                            |                                                      |             | -      | -0.850  |       |       |

|                                                                                                                    |                        | VES = VIH OF VWE = VII                                                          |                                                      |             | -0.650 | -1.2    | Volts |       |

| CEX                                                                                                                | Output Leakage Current | V <sub>OUT</sub> = 2.4 V                                                        |                                                      |             |        | 0       | 30    | μΑ    |

| VCS = V <sub>IH</sub> or V <sub>WE</sub> = V <sub>IL</sub><br>V <sub>OUT</sub> = 0.4 V, V <sub>CC</sub> = Max. (No |                        |                                                                                 |                                                      | (Note 2)    | -30    | 0       | -     | μА    |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V and T<sub>A</sub> = 25°C.

2. This applies to three-state devices only.

3. These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

4. Operating Specification with adequate time for temperatur e stabilization and transverse air flow exceeding 400 linear feet per minute. Conformance testing performed instantaneously where T<sub>A</sub> = T<sub>C</sub>=T<sub>J</sub> 0<sub>J</sub>A = 44 - 59° c/w (with moving air) for ceramic DIPs.0<sub>J</sub>C = 10 - 17° c/w for flatpack or leadless chip carriers.

<sup>\*</sup> See the last page of this spec for Group A Subgroup Testing information.

#### SWITCHING TEST\* SWITCHING TEST KEY TO SWITCHING WAVEFORMS CIRCUIT WAVEFORM WAVEFORM INPUTS OUTPUTS MUST BE WILL BE STEADY TEST POINT MAY CHANGE FROM H TO L FROM OUTPUT <10ns 600Ω CHANGING STATE UNKNOWN TW000030 TC000210 CENTER LINE IS HIGH IMPEDANCE "OFF" STATE DOES NOT KS000010

\* See notes 3, 4, and 5 following Switching Characteristics table.

## SWITCHING CHARACTERISTICS over operating range unless otherwise specified\*

|     |                       |                                                       | Am2  | Am27LS00A/01A Family |      | Am27S00/01 Family |           |      |              | $\Box$                                           |             |

|-----|-----------------------|-------------------------------------------------------|------|----------------------|------|-------------------|-----------|------|--------------|--------------------------------------------------|-------------|

|     |                       |                                                       | C De | C Devices M Devic    |      | vices             | C Devices |      | M Devices    |                                                  | 1 .         |

| No. | Parameter<br>Symbol   | Parameter<br>Description                              | Min. | Max.                 | Min. | Max.              | Min.      | Max. | Min.         | Max.                                             | Units       |

| 1   | t <sub>PLH</sub> (A)  | Delay from Address to Output                          |      | 35                   |      | 45                | _         |      | -            | <del>                                     </del> | <del></del> |

| 2   | t <sub>PHL</sub> (A)  |                                                       |      | 33                   | 1    | 45                |           | 45   |              | 55                                               | ns          |

| 3   | t <sub>PZH</sub> (CS) | Delay from Chip Select (LOW) to                       |      | 25                   |      |                   |           | _    | <del> </del> | <del>                                     </del> |             |

| 4   | t <sub>PZL</sub> (CS) | to Active Output and Correct Data                     |      | 25                   |      | 25                | Í         | 25   |              | 30                                               | ns          |

| 5   | t <sub>PZH</sub> (WE) | Delay from Write Enable (HIGH)                        |      |                      |      |                   |           | -    | -            | _                                                |             |

| 6   | tpZL(WE)              | to Active Output and Correct Data                     |      | 35                   |      | 45                |           | 45   | 1            | 55                                               | ns          |

| 7   | t <sub>S</sub> (A)    | Setup Time Address (Prior to Initiation of Write)     | 0    |                      | 5    |                   | 0         |      | 5            |                                                  | ns          |

| 8   | t <sub>h</sub> (A)    | Hold Time Address (After<br>Termination of Write)     | 0    |                      | 5    |                   | 0         |      | 5            |                                                  | ns          |

| 9   | t <sub>s</sub> (DI)   | Setup Time Data Input (Prior to Termination of Write) | 25   |                      | 30   |                   | 30        |      | 35           |                                                  | ns          |

| 10  | t <sub>h</sub> (DI)   | Hold Time Data Input (After Termination of Write)     | 0    |                      | 5    |                   | 0         |      | 5            |                                                  | ns          |

| 11  | t <sub>pw</sub> (WE)  | Min Write Enable Pulse Width to Insure Write          | 25   |                      | 30   |                   | 30        |      | 35           |                                                  | ns          |

| 12  | t <sub>PHZ</sub> (CS) | Delay from Chip Select (HIGH)                         |      | 25                   |      |                   | -         |      |              |                                                  |             |

| 13  | tpLZ(CS)              | to Inactive Output (HI-Z)                             |      | 25                   |      | 25                | İ         | 25   |              | 30                                               | ns          |

| 14  | t <sub>PLZ</sub> (WE) | Delay from Write Enable (LOW)                         | 1    |                      | -    |                   |           |      |              |                                                  |             |

| 15  | t <sub>PHZ</sub> (WE) | to Inactive Output (HI-Z) (Note 6)                    |      | 30                   |      | 40                | - 1       | 30   |              | 40                                               | ns          |

Notes: 1. Typical limits are at  $V_{CC} = 5.0 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

- Output is preconditioned to data in (inverted) during write to insure correct data is present on all outputs when write is terminated. (No write recovery glitch.)

- (No write recovery glitch.)

3. tpLH(A) and tpHL(A) are tested with S closed an d C<sub>L</sub> = 50 pF with both input and output timing referenced to 1.5 V.

4. For open collector, all delays from write Enable(WE) or Chip Select(CS) inputs to the Data Output(D<sub>OUT</sub>), tpLZ(WE), tpLZ(CS), tpZL(WE) and tpZL(CS) are measured with S closed and C<sub>L</sub> = 50 pF and with both the input and output timing referenced to 1.5 V.

5. For 3-state output, tpZH(WE) and tpZH(CS) are measured with S open, C<sub>L</sub> = 50 pF and with both the input and output timing referenced to 1.5 V. tpZL(WE) and tpZL(CS) are measured with S closed, C<sub>L</sub> = 50 pF and with both the input and output timing referenced to 1.5 V. tpZL(WE) and tpHZ(CS) are measured with S open and C<sub>L</sub> ≤ 5 pF and are measured between the 1.5 V level on the input and the V<sub>OH</sub> 500 mV level on the output. TpLZ(WE) and TpLZ(CS) are measured with S closed and C<sub>L</sub> ≤ 5 pF and are measured between the 1.5 V level on the input and the V<sub>OL</sub> + 500 mV level on the output.

6. Does not apply to -1 devices.

<sup>\*</sup>See the last page of the spec for Group A Subgroup Testing information.

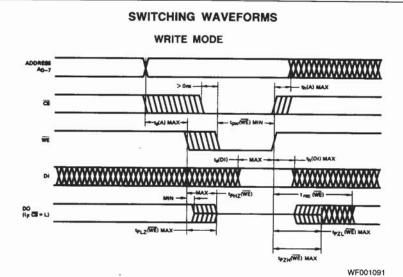

Write Cycle Timing. The cycle is initiated by an address change. After  $t_s(A)$  max, the write enable may begin. The chip select must also be LOW for writing. Following the write pulse,  $t_h(A)$  max must be allowed before the address may be changed again. The output will be inactive (floating for the Am27LS00A/00) while the write enable is LOW. Ordinarily, the chip select should be LOW during the entire write pulse.

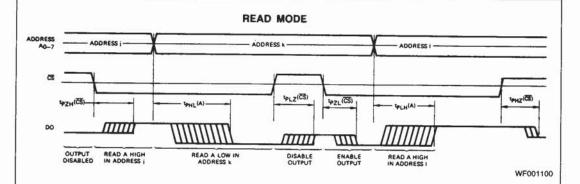

Switching delays from address and chip select inputs to the data output. For the Am27LS00A/00, Am27LS00-1A/00-1 disabled output is "OFF," represented by a single center line. For the Am27LS01A/01, Am27LS01-1A/01-1, a disabled output is HIGH.

#### GROUP A SUBGROUP TESTING

#### DC CHARACTERISTICS

| Parameter<br>Symbol | Subgroups |

|---------------------|-----------|

| V <sub>OH</sub>     | 1, 2, 3   |

| V <sub>OL</sub>     | 1, 2, 3   |

| VIH                 | 1, 2, 3   |

| VIL                 | 1, 2, 3   |

| ŊĹ                  | 1, 2, 3   |

| Ιн                  | 1, 2, 3   |

| Isc                 | 1, 2, 3   |

| lcc                 | 1, 2, 3   |

| V <sub>CL</sub>     | 1, 2, 3   |

| ICEX                | 1, 2, 3   |

#### SWITCHING CHARACTERISTICS

| Parameter<br>Symbol   | Subgroups | Parameter<br>Symbol   | Subgroups |  |  |

|-----------------------|-----------|-----------------------|-----------|--|--|

| t <sub>PLH</sub> (A)  | 9, 10, 11 | t <sub>s</sub> (DI)   | 9, 10, 11 |  |  |

| t <sub>PHL</sub> (A)  | 9, 10, 11 | t <sub>h</sub> (DI)   | 9, 10, 11 |  |  |

| t <sub>PZH</sub> (CS) | 9, 10, 11 | t <sub>pw</sub> (WE)  | 9, 10, 11 |  |  |

| tpZL (CS)             | 9, 10, 11 | t <sub>PHZ</sub> (CS) | 9, 10, 11 |  |  |

| t <sub>PZH</sub> (WE) | 9, 10, 11 | t <sub>PLZ</sub> (ĈŜ) | 9, 10, 11 |  |  |

| t <sub>PZL</sub> (WE) | 9, 10, 11 | t <sub>PLZ</sub> (WE) | 9, 10, 11 |  |  |

| t <sub>s</sub> (A)    | 9, 10, 11 | t <sub>PHZ</sub> (WE) | 9, 10, 11 |  |  |

| t <sub>h</sub> (A)    | 9, 10, 11 |                       |           |  |  |

#### MILITARY BURN-IN

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.