# High-Efficiency, 45V, 3A, Digitally Calibrated, Synchronous Step-Down Module

#### **DESCRIPTION**

The MPM3593 is a high-frequency, synchronous, rectified, step-down module with an  $I^2C$  control interface and a multi-page one-time programmable (OTP) memory. It can achieve up to 3A of continuous output current ( $I_{OUT}$ ), with excellent load and line regulation across a wide input voltage ( $V_{IN}$ ) range.

The MPM3593 integrates an internal high-side MOSFET (HS-FET) and low-side MOSFET (LS-FET) to achieve high efficiency without requiring an external Schottky diode. With internal compensation and a feedback divider, the device provides a very compact solution that requires a minimal number of readily available, standard external components.

The MPM3593 is flexibly designed to support a 0.8V to 12V output voltage ( $V_{OUT}$ ) that can be adjusted on the fly via an I<sup>2</sup>C serial interface. The voltage slew rate, switching frequency ( $f_{SW}$ ), enable, and power-save mode are also configurable via the I<sup>2</sup>C interface. This allows the user to optimize each output for different specifications.

During bench evaluations, different configurations can be easily obtained via the I<sup>2</sup>C interface instead of reworking external the desired components. Once optimal configuration is achieved, a multi-page OTP memory can permanently store the settings.

Current mode operation provides fast transient response and eases loop stabilization. Full protection features include under-voltage lockout (UVLO), over-voltage protection (OVP), over-current protection (OCP), and over-temperature protection.

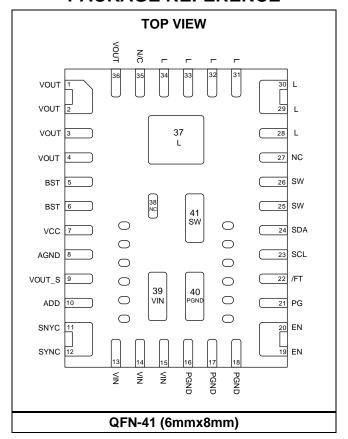

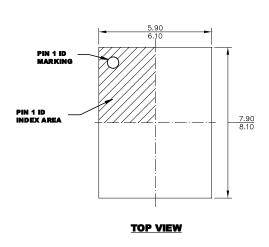

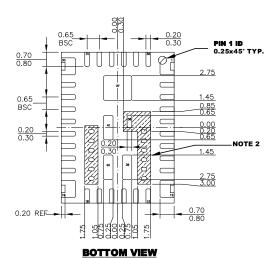

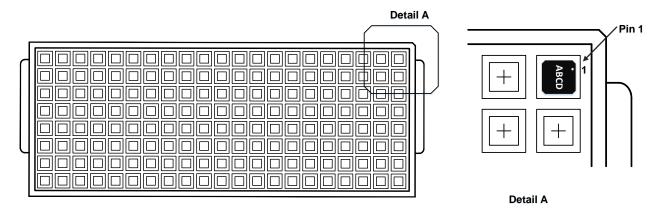

The MPM3593 is available in a QFN-41 (6mmx8mm) package.

#### **FEATURES**

- Wide 3.5V to 45V Operating V<sub>IN</sub> Range

- 3A Continuous Output Current (I<sub>OUT</sub>) at V<sub>OUT</sub>

≤ 5V and 2A Continuous I<sub>OUT</sub> at V<sub>OUT</sub> > 5V

- 12V  $V_{OUT}$  at  $V_{IN} \le 24V$  and 8V  $V_{OUT}$  at  $V_{IN} > 24V$

- High-Efficiency, Synchronous Mode Module

- Power Good (PG) and Fault Indications

- OVP, OCP, and Over-Temperature Protection

- Internal Soft Start (SS)

- Configurable Address via Resistor

- Configurable Parameters via I<sup>2</sup>C Interface Include:

- 0.8V to 12V V<sub>OUT</sub> Range

- Switching Frequency (f<sub>SW</sub>)

- Compensation Network

- Slope Compensation

- Enable (EN) Threshold

- Input UVLO Threshold

- PG Threshold

- AAM Mode and CCM Selection

- o Light-Load Mode Threshold

- SCP Mode Selection

- Current Limit Threshold

- OVP Mode Selection

- Input and Output OVP Threshold

- Over-Temperature Protection Threshold

- Switching Slew Rate

- Output Slew Rate (SS Time, t<sub>SS</sub>)

- SYNC Input and Output Selection

- Phase Shift

- Frequency Dithering for Low-EMI Operation

- Multi-Page One-Time Programmable (OTP)

Memory for Permanent Storage

- Available in a QFN-41 (6mmx8mm) Package

#### **APPLICATIONS**

- Industrial Power Systems

- Automotive Power Systems

- Telecommunication Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

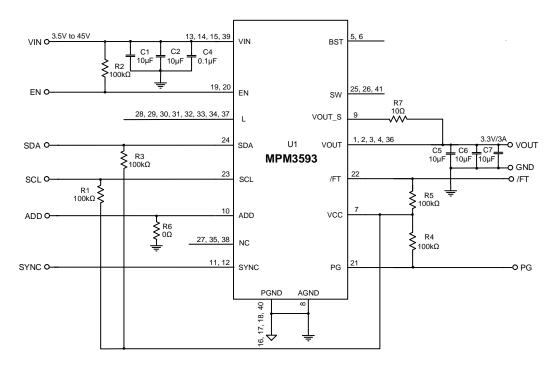

# **TYPICAL APPLICATION**

#### BST O VOUT VOU-10Ω --**W**--O GND PG O C2 VOUT\_S O VCC MPM3593 VCC SDA O SDA SCL O-SCL AGND /FT O /FT O EN ΕN ADD ADD O SYNC

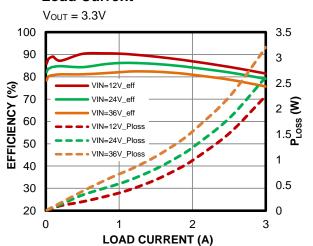

## Efficiency and Power Loss vs. **Load Current**

#### ORDERING INFORMATION

| Part Number*      | Package          | Top Marking | MSL Rating |

|-------------------|------------------|-------------|------------|

| MPM3593GQY-xxxx** | QFN-41 (6mmx8mm) | See Below   | 3          |

| MPM3593GQY-0001   | QFN-41 (6mmx8mm) | See Below   | 3          |

| EVKT-M3593        | -                | -           | -          |

<sup>\*</sup> For tray, add suffix -T (e.g. MPM3593GQY-0001-T).

# TOP MARKING MPSYYWW MP3593 LLLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP3593: Part number LLLLLLLL: Lot number

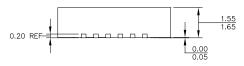

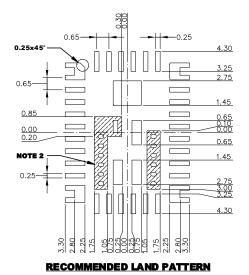

### **PACKAGE REFERENCE**

<sup>\*\* &</sup>quot;xxxx" is the configuration identifier for the register settings stored in the OTP memory. Each "x" can be a hexadecimal value between 0 and F. "0001" is the default configuration code. For more details on the configuration information, see Table 2 and Table 3 on page 29 based on the suffix code "0001".

# **PIN FUNCTIONS**

| Pin#                                    | Name   | Description                                                                                                                                                                                                                       |

|-----------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3,<br>4, 36                       | VOUT   | Module output.                                                                                                                                                                                                                    |

| 5,6                                     | BST    | <b>Bootstrap.</b> A 0.1µF capacitor connected internally between the SW and BST pins forms a floating supply across the high-side MOSFET (HS-FET) switch driver. BST can also be floated.                                         |

| 7                                       | VCC    | Internal 5V low-dropout (LDO) regulator output. A 1µF capacitor connected internally decouples the VCC pin. VCC can also be floated.                                                                                              |

| 8                                       | AGND   | <b>Signal ground.</b> The AGND pin is the internal logic and signal circuit's ground. AGND is not internally connected to the power ground. Ensure AGND is connected to the power ground in the PCB layout.                       |

| 9                                       | VOUT_S | Output voltage (Vоит) sense.                                                                                                                                                                                                      |

| 10                                      | ADD    | Address setting for the I <sup>2</sup> C.                                                                                                                                                                                         |

| 11,12                                   | SYNC   | <b>Synchronized to external clock signal.</b> The SYNC pin can be configured via the I <sup>2</sup> C to the sync input (SYNCIN) or sync output (SYNCO).                                                                          |

| 13, 14,<br>15, 39                       | VIN    | <b>Supply voltage.</b> The VIN pin supplies power to the entire module. To reduce switching spikes, connect a decoupling capacitor from VIN to ground, placed as close as possible to the IC. Connect VIN using a wide PCB trace. |

| 16, 17,<br>18, 40                       | PGND   | <b>Power ground.</b> The PGND pin is the regulated V <sub>OUT</sub> 's reference ground. For the best thermal results, connect PGND to larger copper areas.                                                                       |

| 19, 20                                  | EN     | <b>Enable.</b> Pull the EN pin high to turn on the MPM3593; pull EN low to turn off the MPM3593. EN cannot be floated.                                                                                                            |

| 21                                      | PG     | <b>Power good indicator.</b> The PG pin's output is an open drain. If used, connect a resistor to a pull-up power source.                                                                                                         |

| 22                                      | /FT    | Fault indicator. If any fault or warning occurs, the /FT pin is pulled down.                                                                                                                                                      |

| 23                                      | SCL    | I <sup>2</sup> C serial clock.                                                                                                                                                                                                    |

| 24                                      | SDA    | I <sup>2</sup> C serial data.                                                                                                                                                                                                     |

| 25, 26,<br>41                           | SW     | Module switch output. Internally connect to the internal inductor.                                                                                                                                                                |

| 27, 35,<br>38                           | NC     | Not connected. Float the NC pin. Do not connect the NC pins together in the PCB layout.                                                                                                                                           |

| 28, 29,<br>30, 31,<br>32, 33,<br>34, 37 | L      | N/A.                                                                                                                                                                                                                              |

# **ABSOLUTE MAXIMUM RATINGS (1)** Supply voltage (V<sub>IN</sub>) .....-0.3V to +48V SW voltage (V<sub>SW</sub>) .....-0.3V (-10V for <3ns) .....to $V_{IN}$ + 0.3V (+50V for <3ns) EN voltage (V<sub>EN</sub>) .....-0.3V to +48V BST voltage (V<sub>BST</sub>).....V<sub>SW</sub> + 5.5V VCC voltage (V<sub>CC</sub>).....-0.3V to +5.5V Output voltage (V<sub>OUT</sub>).....-0.3V to +15V All other pins .....-0.3V to +5V Continuous power dissipation ( $T_A = 25$ °C) (2) (5) Junction temperature ......150°C Lead temperature ......260°C Storage temperature.....-65°C to +150°C ESD Ratings (3) Human body model (HBM) .....±2KV Charged device model (CDM) ..... ±750V Recommended Operating Conditions (4) Operating junction temp (T<sub>J</sub>).... -40°C to +150°C

| Thermal Resistance      | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |      |

|-------------------------|-------------------------|--------------------------|------|

| EVM3593-QY-00B (5)      | 26                      | 12.6                     | °C/W |

| JESD51-7 <sup>(6)</sup> | 33.6                    | . 26.2                   | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which may cause the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) HBM, per JEDEC specification JESD22-A114; CDM, per JEDEC specification JESD22-C101, AEC specification AEC-Q100-011. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

- The device is not guaranteed to function outside of its operating conditions. See the Typical Application Circuits section on page 28.

- 5) Measured on EVM3593-QY-00B, 4-layer PCB, 64mmx64mm.

- 6) Measured on JESD51-7, 4-layer PCB. The θ<sub>JA</sub> value given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

5

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C, typical values refer to  $T_J$  = 25°C (8), unless otherwise noted.

| Parameter                                                     | Symbol                                | Condition                                                                 | Min   | Тур | Max   | Units |

|---------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------|-------|-----|-------|-------|

| V <sub>IN</sub> under-voltage lockout (UVLO) rising threshold | V <sub>IN_UVLO_VTH</sub>              | 05h, bits[3:1] = 0b000                                                    | 2.9   | 3.2 | 3.4   | V     |

| V <sub>IN</sub> UVLO threshold hysteresis                     | VIN_UVLO_HYS                          | 05h, bit[0] = 0b1                                                         |       | 4   |       | %     |

| V <sub>IN</sub> UVLO threshold DAC range                      | VIN_UVLO_DAC                          |                                                                           | 3.2   |     | 7.4   | V     |

| V <sub>IN</sub> quiescent current                             | lα                                    | 00h, bits[7:0] = 0x64;<br>01h, bits[1:0] = 0b01;<br>Vout = 5V             |       | 600 | 1000  | μA    |

| V <sub>IN</sub> shutdown current                              | I <sub>SD</sub>                       | $V_{EN} = 0V$ , $T_J = 25$ °C                                             |       |     | 1     | μΑ    |

| Default output voltage                                        | V <sub>OUT_DEFAULT</sub>              | 00h, bits[7:0] = 0x64;<br>01h, bits[1:0] = 0b01;<br>T <sub>J</sub> = 25°C | 4.95  | 5   | 5.05  | V     |

|                                                               |                                       | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$                            | 4.925 | 5   | 5.075 | V     |

|                                                               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | V <sub>IN</sub> ≤ 24V                                                     | 0.8   |     | 12    | V     |

| Operating V <sub>OUT</sub> range                              | V <sub>OUT</sub>                      | V <sub>IN</sub> > 24V                                                     | 0.8   |     | 8     | V     |

| Default switching frequency                                   | fsw_default                           | 02h, bits[5:0] = 0b001010,<br>T <sub>J</sub> = 25°C                       | 450   | 500 | 550   | kHz   |

| Configurable frequency range                                  | f <sub>SW</sub>                       |                                                                           | 250   |     | 2500  | kHz   |

| Sync frequency range                                          | fsync                                 |                                                                           | 250   |     | 2500  | kHz   |

| Sync high threshold                                           | Vsync_high                            |                                                                           | 2     |     |       | V     |

| Sync low threshold                                            | V <sub>SYNC_LOW</sub>                 |                                                                           |       |     | 0.4   | V     |

| Minimum on time (7)                                           | t <sub>ON_MIN</sub>                   | Peak current mode                                                         |       | 80  |       | ns    |

| Minimum off time (7)                                          | toff_min                              |                                                                           |       | 380 |       | ns    |

| High-side MOSFET (HS-FET) on resistance                       | Rds(ON)_H                             | V <sub>BST</sub> - V <sub>SW</sub> = 5V                                   |       | 95  | 180   | mΩ    |

| Low-side MOSFET (LS-FET) on resistance                        | Rds(on)_L                             |                                                                           |       | 50  | 100   | mΩ    |

| Default rising switching slew rate (7)                        | SR <sub>R_DEFAULT</sub>               | 09h, bits[2:1] = 0b00                                                     |       | 1   |       | V/ns  |

| Rising switching slew rate range <sup>(7)</sup>               | SR <sub>R</sub>                       |                                                                           | 1     |     | 4     | V/ns  |

| Default falling switching slew rate (7)                       | SR <sub>F_DEFAULT</sub>               | 09h, bits[4:3] = 0b00                                                     |       | 1   |       | V/ns  |

| Falling switching slew rate range (7)                         | SR <sub>F</sub>                       |                                                                           | 1     |     | 4     | V/ns  |

| BST to SW refresh UVLO                                        | V <sub>BST_UVLO</sub>                 |                                                                           |       | 2.4 | 2.8   | V     |

| BST to SW refresh UVLO hysteresis                             | V <sub>BST_UVLO_HYS</sub>             |                                                                           |       | 0.2 |       | V     |

| Default soft-start time                                       | tss_default                           | 04h, bits[7:6] = 0b01                                                     |       | 1   |       | ms    |

| tss range                                                     | tss                                   |                                                                           | 0.5   |     | 4     | ms    |

| Default EN voltage threshold                                  | VEN_DEFAULT                           | 05h, bits[6:5] = 0b01                                                     | 1.2   | 1.4 | 1.6   | V     |

| EN voltage threshold range                                    | V <sub>EN</sub>                       |                                                                           | 1.2   |     | 2     | V     |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C, typical values refer to  $T_J$  = 25°C (8), unless otherwise noted.

| Parameter                                              | Symbol                      | Condition               | Min | Тур | Max | Units        |

|--------------------------------------------------------|-----------------------------|-------------------------|-----|-----|-----|--------------|

| Default EN voltage hysteresis                          | V <sub>EN_HYS_DEFAULT</sub> | 05h, bit[4] = 0b0       |     | 220 |     | mV           |

| EN voltage hysteresis range                            | V <sub>EN_HYS</sub>         |                         | 220 |     | 420 | mV           |

| Default PG upper trip rising threshold                 | V <sub>PG_U_DEFAULT</sub>   |                         | 108 | 110 | 112 | % of<br>Vouт |

| PG upper trip rising threshold range                   | V <sub>PG_U_RANGE</sub>     |                         | 110 |     | 115 | %            |

| Default PG lower trip rising threshold                 | V <sub>PG_L_</sub> DEFAULT  |                         | 86  | 89  | 92  | % of<br>Vouт |

| PG lower trip threshold range                          | V <sub>PG_L_RANGE</sub>     |                         | 84  |     | 89  | %            |

| Default PG trip threshold hysteresis                   | Vpg_hys_default             |                         |     | 5.5 |     | %            |

| PG trip threshold hysteresis range                     | V <sub>PG-HYS</sub>         |                         | 3   |     | 5.5 | %            |

| PG low output voltage                                  | V <sub>PG_</sub> SINK       | I <sub>SINK</sub> = 1mA |     | 0.1 | 0.3 | V            |

| PG rising deglitch time                                | tpg_delay_rising            |                         |     | 30  |     | μs           |

| PG falling deglitch time                               | tpg_delay_falling           |                         |     | 30  |     | μs           |

| VCC regulator                                          | Vcc                         | Icc = 0mA               | 4.7 | 5   | 5.3 | V            |

| Default peak current limit (7)                         | IPEAK_LIMIT_DEFAULT         | 06h, bits[5:3] = 0b000  | 4.2 | 5   | 5.8 | Α            |

| Peak current limit range                               | I <sub>PEAK_LIMIT</sub>     |                         | 2   |     | 8   | Α            |

| Default valley current limit (7)                       | IVALLEY-LIMIT_DEFAULT       | 06h, bits[2:1] = 0b10   | 3   | 4   | 5.2 | Α            |

| Valley current limit range                             | IVALEY_LIMIT                |                         | 2   |     | 4   | Α            |

| Default output over-voltage protection (OVP) threshold | Vovp_default                | 07h, bits[2:1] = 0b01   | 115 | 120 | 125 | % of<br>Vout |

| Output OVP threshold range                             | Vovp_range                  |                         | 110 |     | 130 | %            |

| Default output OVP hysteresis                          | VOVP_HYS_DEFAULT            | 07h, bit[0] = 0b0       |     | 5.7 |     | % of<br>Vouт |

| Output OVP hysteresis range                            | Vovp_hys_range              |                         | 3.2 |     | 5.7 | %            |

| Input OVP threshold range                              | VIN_OVP_RANGE               |                         | 28  |     | 40  | V            |

| Input OVP threshold accuracy                           | V <sub>IN_OVP_ACC</sub>     | 01h, bits[3:2] = 0b10   | 32  | 34  | 36  | V            |

| Default input OVP hysteresis                           | VIN_OVP_HYS_DEFAULT         | 01h, bit[4] = 0b1       |     | 3.5 |     | % of VIN_OVP |

| Input OVP hysteresis range                             | VIN_OVP_HYS_RANGE           |                         | 3.5 |     | 5.5 | %            |

| Default thermal shutdown (7)                           | T <sub>SD_DEFAULT</sub>     | 07h, bits[7:6] = 0b10   |     | 175 |     | °C           |

| Thermal shutdown range (7)                             | T <sub>SD</sub>             |                         | 125 |     | 175 | °C           |

| Default thermal shutdown hysteresis (7)                | Tsd_sys_default             | 07h, bit[5] = 0b0       |     | 25  |     | °C           |

| Thermal shutdown hysteresis range <sup>(7)</sup>       | T <sub>SD_SYS</sub>         |                         | 25  |     | 50  | °C           |

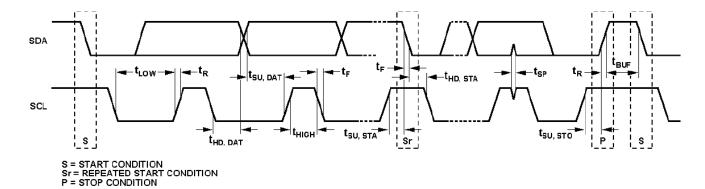

# I<sup>2</sup>C PORT SIGNAL CHARACTERISTICS

$V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C, typical values refer to  $T_J$  = 25°C  $^{(8)}$ , unless otherwise noted.

| Parameters                                       | Symbol              | Condition               | Min                          | Тур | Max | Units |

|--------------------------------------------------|---------------------|-------------------------|------------------------------|-----|-----|-------|

| I <sup>2</sup> C Interface Specifications        |                     |                         |                              |     |     |       |

| Input logic low                                  | VIL                 |                         | 0                            |     | 0.4 | V     |

| Input logic high                                 | $V_{IH}$            |                         | 1.3                          |     |     | V     |

| Output logic low                                 | $V_{OL}$            | I <sub>LOAD</sub> = 3mA |                              |     | 0.4 | V     |

| SCL clock frequency                              | fscL                |                         |                              |     | 400 | kHz   |

| SCL high time                                    | t <sub>HIGH</sub>   |                         | 0.6                          |     |     | μs    |

| SCL low time                                     | tLOW                |                         | 1.3                          |     |     | μs    |

| Data set-up time                                 | tsu_dat             |                         | 100                          |     |     | ns    |

| Data hold time                                   | t <sub>HD_DAT</sub> |                         | 0                            |     | 0.9 | μs    |

| Set-up time for a repeated start condition       | <b>t</b> su_sta     |                         | 0.6                          |     |     | μs    |

| Hold time for a start condition                  | <b>t</b> HD_STA     |                         | 0.6                          |     |     | μs    |

| Bus free time between a start and stop condition | t <sub>BUF</sub>    |                         | 1.3                          |     |     | μs    |

| Set-up time for a stop condition                 | tsu_sto             |                         | 0.6                          |     |     | μs    |

| Rise time of SCL and SDA                         | t <sub>R</sub>      |                         | 20 + 0.1<br>x C <sub>B</sub> |     | 120 | ns    |

| Fall time of SCL and SDA                         | t <sub>F</sub>      |                         | 20 + 0.1<br>x C <sub>B</sub> |     | 120 | ns    |

| Pulse width of suppressed spike                  | tsp                 |                         | 0                            |     | 50  | ns    |

| Capacitance bus for each bus line                | Св                  |                         |                              |     | 400 | pF    |

Figure 1: I<sup>2</sup>C-Compatible Interface Timing Diagram

#### Notes:

- 7) Derived from characterization test. Not tested in production.

- 8) Derived from engineering sample test. Not tested in production.

8

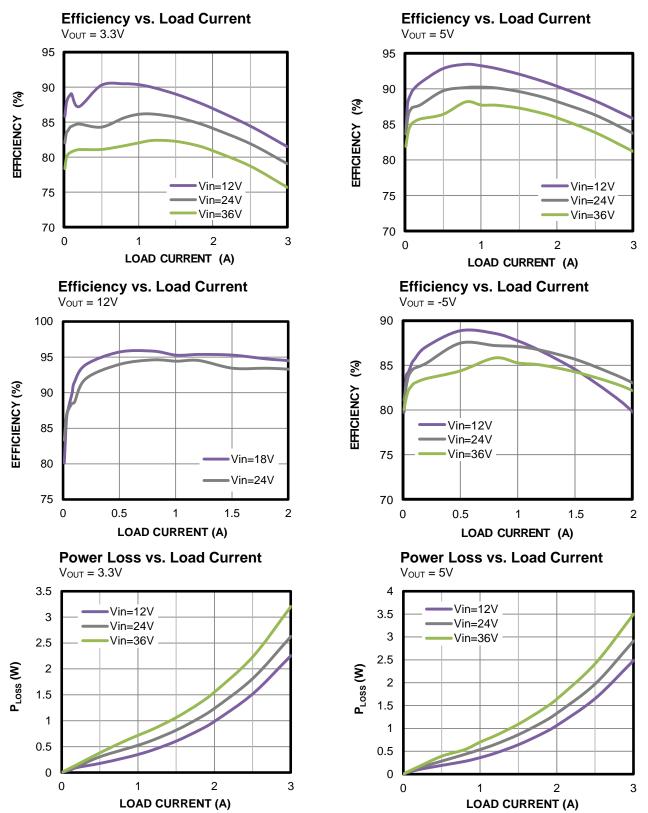

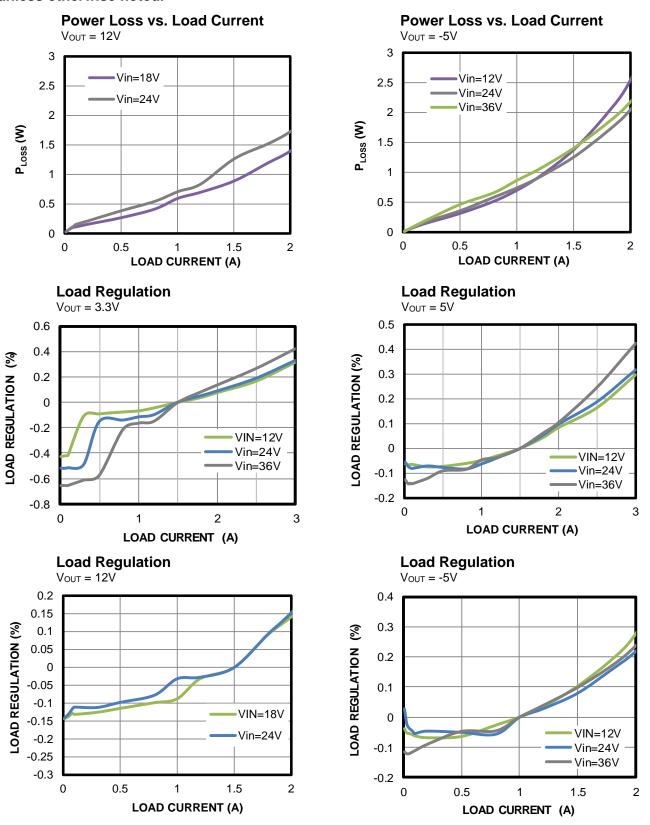

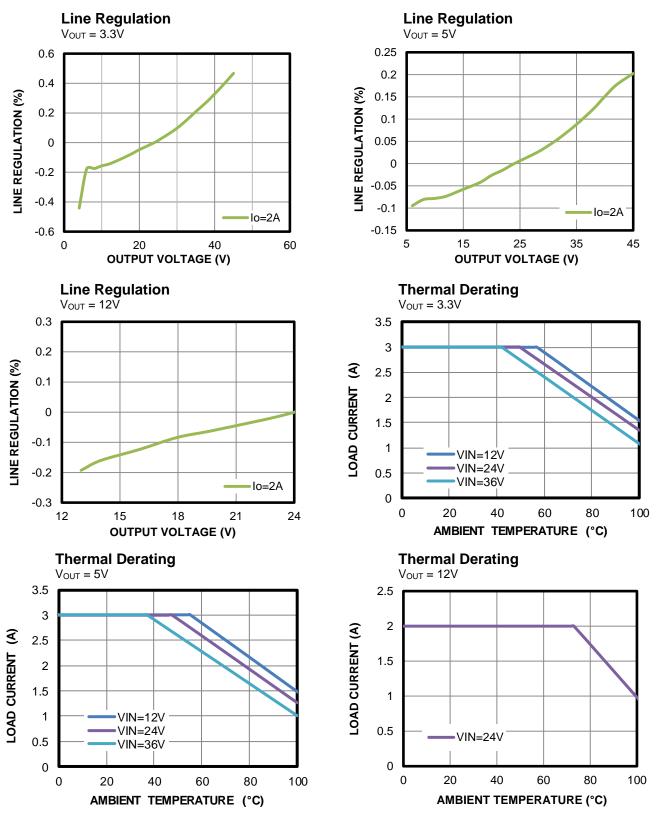

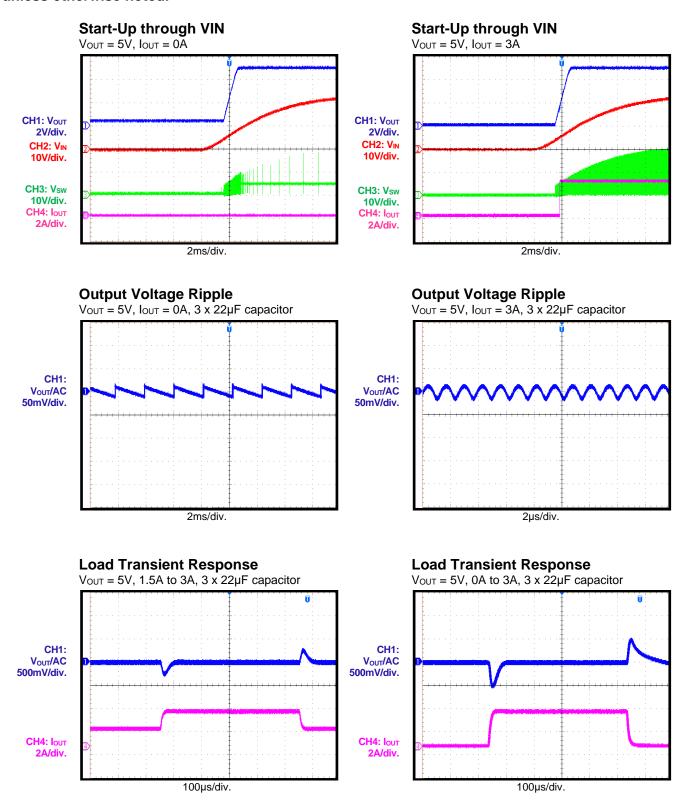

#### TYPICAL PERFORMANCE CHARACTERISTICS

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 24V, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 24V, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

Performance waveforms are tested on the evaluation board.  $V_{IN}$  = 24V, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

Performance waveforms are tested on the evaluation board.  $V_{IN}$  = 24V, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

Performance waveforms are tested on the evaluation board.  $V_{IN}$  = 24V, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

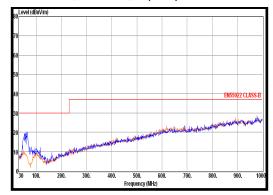

#### Conducted Emissions, EV55022 Class B

$V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ , input Pi filter:  $10\mu F$ ,  $4.7\mu H$ , or  $10\mu F$

#### Radiated Emissions, EV55022 Class B

V<sub>OUT</sub> = 3.3V, I<sub>OUT</sub> = 3A, 10μF input Pi filter

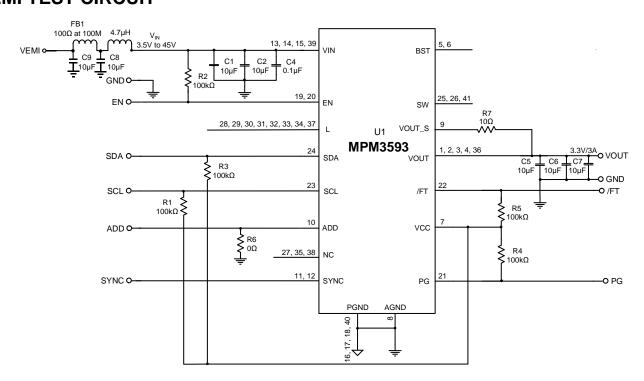

# **EMI TEST CIRCUIT**

Figure 2: EMI Test Circuit

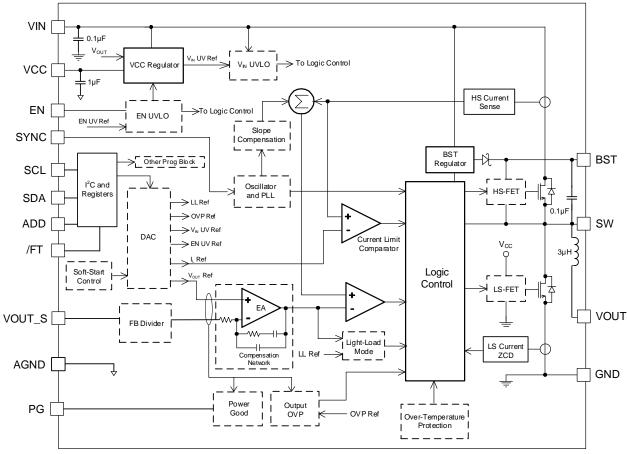

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 3: Functional Block Diagram (9)

#### Note:

9) The blocks with dashed lines are configurable.

#### **OPERATION**

The MPM3593 is a high-frequency, synchronous step-down module with built-in power MOSFETs. The device can achieve up to 3A of continuous output current ( $I_{OUT}$ ) across a wide 3.5V to 45V input voltage ( $V_{IN}$ ) range, with excellent load and line regulation.

#### **Pulse-Width Modulation (PWM) Control**

At moderate-to-high output currents, the MPM3593 operates in fixed-frequency, peak current control mode to regulate the output voltage ( $V_{\text{OUT}}$ ). A pulse-width modulation (PWM) cycle is initiated by the internal clock. At the clock's rising edge, the high side MOSFET (HSFET) turns on and the inductor current ( $I_{\text{L}}$ ) increases linearly to provide energy to the load. The HS-FET remains on until its current reaches the COMP voltage ( $V_{\text{COMP}}$ ), which is the internal error amplifier (EA)'s output.

The EA compares the feedback (FB) voltage ( $V_{FB}$ ) to the internal, high-precision reference voltage ( $V_{REF}$ ) and generates an output voltage ( $V_{EA}$ ) that is proportional to the difference between the two voltages.  $V_{EA}$  is then used to determine the amount of energy that should be transferred to the load.  $V_{COMP}$  is proportional to the load current, where a higher load current results in a higher  $V_{COMP}$ . The FB divider ratio and FB reference voltage can be adjusted via the  $I^2C$ , which makes it easy to adjust different  $V_{OUT}$  values.

When the HS-FET is off, the low-side MOSFET (LS-FET) turns on immediately and remains on until the next clock begins. During this time,  $I_L$  flows through the LS-FET. To avoid shoot-through, a dead time (DT) is inserted to prevent the HS-FET and LS-FET from turning on at the same time.

If the current in the HS-FET does not reach the value set by COMP within one PWM period, then the HS-FET remains on and saves a turn-off operation.

#### Mode Selection (AAM Mode and FCCM)

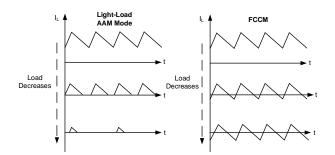

The MPM3593 provides two modes that can be selected via the I<sup>2</sup>C: advanced asynchronous modulation (AAM) mode or forced continuous conduction mode (FCCM) (see Figure 4).

Figure 4: AAM Mode and FCCM

AAM mode optimizes efficiency under light-load or no-load conditions, meanwhile FCCM maintains a constant switching frequency (f<sub>SW</sub>) and smaller output ripple, with the disadvantage of lower efficiency under light loads.

When the load decreases with AAM mode enabled, the MPM3593 first enters discontinuous conduction mode (DCM) with a fixed frequency until  $I_L$  approaches 0A. If the load decreases further, or there is no load that makes the peak  $I_L$  ( $I_{L\_PEAK}$ ) lower than the AAM mode threshold set via the  $I^2C$ , then the MPM3593 enters sleep mode and consumes a very low quiescent current ( $I_Q$ ) to further improve lightload efficiency.

In sleep mode, the internal clock is blocked and  $V_{FB}$  is below  $V_{REF}$ . As a result, the MPM3593 skips some pulses and  $V_{COMP}$  ramps up until  $I_{L\_PEAK}$  exceeds the AAM mode threshold. The internal clock is then reset and the crossover time becomes the benchmark for the next clock. This control scheme helps achieve high efficiency by scaling down the frequency, which reduces the switching and gate driver losses.

As the output current ( $I_{OUT}$ ) increases under lightload conditions,  $V_{COMP}$  and  $f_{SW}$  increase. If  $I_{OUT}$  exceeds the critical level set by  $V_{COMP}$ , then the MPM3593 resumes fixed-frequency PWM control.

When FCCM is enabled, the MPM3593 operates in fixed-frequency, peak current control mode to regulate  $V_{\text{OUT}}$ , regardless of  $I_{\text{OUT}}$ .

#### Internal Regulator (VCC)

Most of the internal circuitry is powered by the internal 5V regulator. This regulator uses  $V_{\text{IN}}$  as its input and operates across the full  $V_{\text{IN}}$  range. When  $V_{\text{IN}}$  exceeds 5V, the regulator's output is in full regulation. A lower  $V_{\text{IN}}$  results in a lower output voltages.

Once  $V_{\text{IN}}$  exceeds its under-voltage lockout (UVLO) threshold and the EN pin is pulled high, the regulator is enabled. During EN shutdown, the VCC regulator is disabled to reduce power dissipation.

For improved thermal performance,  $V_{OUT}$  bias function can be enabled via the  $I^2C$ . When  $V_{OUT}$  exceeds 5V, VCC and the internal circuit are powered by  $V_{OUT}$ . The bias function only works when the MPM3593 is set to AAM mode; the bias function does not work in continuous conduction mode (CCM) even when  $V_{OUT}$  bias is enabled. If an external FB divider is used, do not enable the bias function. For improved output regulation, do not enable the bias function when  $V_{OUT}$  exceeds 9V.

#### **Enable (EN) Control**

EN is a digital control pin that turns the regulator, including the  $I^2C$  block, on and off. Pull EN high to turn on the regulator; pull EN low to turn off the regulator. The EN threshold can be configured via the  $I^2C$ . Do not float EN. To adjust the parameters via the  $I^2C$ , the EN voltage ( $V_{EN}$ ) must exceed 2V. When  $V_{EN}$  is low, the  $I^2C$  interface is blocked to achieve lower current consumption, and the RAM registers are reset to the default value.

#### Switching Frequency (f<sub>SW</sub>)

The MPM3593's frequency is set to 500kHz by default and can be configured between 250kHz and 2.5MHz via the I<sup>2</sup>C.

#### SYNCIN and SYNCO

The SYNC pin can be configured via the I<sup>2</sup>C to the sync input or sync output (SYINC and SYNCO, respectively). SYNCO outputs the sync signal in phase with the internal switching clock. SYNCIN synchronizes the internal f<sub>SW</sub> via an external clock using the SYNC pin, where the phase shift can be set between 0 and 180 degrees according to register 02h, bit[6] in the I<sup>2</sup>C register.

At start-up, the MPM3593 operates at the internally set frequency, then synchronizes quickly to the external clock once soft start (SS) is ready. To drive the internal logic, ensure the SYNC clock's high amplitude exceeds 2V, and the low amplitude is below 0.4V. The external SYNC frequency is recommended to be between 250kHz and 2.5MHz.

#### **Under-Voltage Lockout (UVLO)**

The MPM3593 provides  $V_{\text{IN}}$  under-voltage lockout (UVLO) protection to ensure reliable output power. If EN is active and  $V_{\text{IN}}$  exceeds the UVLO rising threshold, then the MPM3593 starts up. If  $V_{\text{IN}}$  drops below the UVLO falling threshold, then the MPM3593 shuts down. The UVLO threshold can be set between 3.2V and 7.4V via the I<sup>2</sup>C. UVLO is a non-latch protection that prevents the device from operating at an insufficient voltage.

#### Soft Start (SS)

When EN is pulled high, the MPM3593 implements built-in SS to ramp up  $V_{\text{OUT}}$  in a controlled slew rate, avoiding overshoot during start-up. When the MPM3593 starts up, the internal circuitry generates a SS voltage ( $V_{\text{SS}}$ ) that ramps up slowly. If  $V_{\text{SS}}$  is below  $V_{\text{REF}}$ ,  $V_{\text{SS}}$  overrides  $V_{\text{REF}}$  as the EA reference; if  $V_{\text{SS}}$  exceeds  $V_{\text{REF}}$ ,  $V_{\text{REF}}$  acts as the EA reference. Once  $V_{\text{REF}}$  acts as the EA reference, SS completes and the MPM3593 enters steady state.

The SS time ( $t_{SS}$ ) is set internally by default to 1ms.  $t_{SS}$  can also be configured to 0.5ms, 2ms, or 4ms via the I<sup>2</sup>C. When  $V_{OUT}$  is shorted to GND,  $V_{FB}$  decreases and  $V_{SS}$  is discharged. The MPM3593 resumes soft start and begins normal operation.

#### Pre-Biased Start-Up

If  $V_{FB}$  exceeds  $V_{SS}$  at start-up, meaning the output has a pre-biased voltage, neither the HS-FET or LS-FET turn on until  $V_{SS}$  exceeds  $V_{FB}$ .

#### Power Good (PG) Indicator

The MPM3593 includes an open-drain power good (PG) output. Pull PG up to a voltage source via a resistor (e.g.  $100k\Omega$ ). If  $V_{IN}$  is present, PG is pulled to GND before SS is ready. If  $V_{OUT}$  is within the default  $\pm 10\%$  rated voltage window, PG is pulled high after a delay (typically  $30\mu$ s).

If  $V_{\text{OUT}}$  moves outside the default  $\pm 10\%$  range with a hysteresis, PG is pulled low to indicate a failure output status. The PG threshold and hysteresis can be configured via the  $I^2C$ .

#### **FAULT Indicator**

The /FT pin is open-drain output. Pull /FT up to a voltage source via a resistor (e.g.  $100k\Omega$ ). During normal operation, /FT is pulled high. If any fault or warning occurs, /FT is pulled low to indicate a fault status, including input and output over-voltage protection (OVP), short-circuit protection (SCP), and thermal shutdown.

#### **Over-Current Protection (OCP)**

The MPM3593 supports cycle-by-cycle over-current protection (OCP).  $I_L$  is monitored when HS-FET is turned on. Once  $I_{L\_PEAK}$  exceeds the set current limit threshold, the HS-FET immediately turns off. Then the LS-FET turns on to discharge the energy and  $I_L$  decreases. The HS-FET remains off until  $I_L$  drops below the valley current limit. OCP helps prevent  $I_L$  runaway and potential damage to the components.  $I_{L\_PEAK}$  and the valley current threshold can be configured via the  $I^2C$ .

When  $I_L$  triggers the peak current limit, the OCP timer starts immediately. During the OCP timer, if  $I_L$  reaches the current limit in each cycle, then SCP operation is triggered and is set to hiccup mode by default.

#### **Short-Circuit Protection (SCP)**

If a short circuit occurs, the MPM3593 immediately hits its current limit, while  $V_{\text{OUT}}$  quickly drops to the UVLO threshold (default 50% of the set  $V_{\text{OUT}}$ ,  $V_{\text{OUT\_SET}}$ ), which is recognized as an output dead short. This directly triggers SCP. There are three SCP modes that are selectable via the  $I^2C$ : hiccup mode (default), switching with non-hiccup mode, and latch-off mode.

In hiccup mode, the MPM3593 disables its output power stage and resets  $V_{SS}$ , then initiates a SS procedure.  $t_{SS}$  and hiccup duty determine the hiccup off time, which can be set via the  $I^2C$ . If the short-circuit condition still holds after SS completes, the device repeats this operation until the short circuit is removed and the output returns to regulation. SCP significantly reduces the average short-circuit current by periodically restarting the device, which alleviates thermal issues and protects the regulator. In switching

with non-hiccup mode, the MPM3593 continues switching with  $I_L$ , where  $I_L$  is limited by the peak and valley current limit. In latch-off mode, the MPM3593 stops operating once SCP occurs until the device is re-enabled or powered up again.

#### **Output Over-Voltage Protection (OVP)**

The MPM3593 monitors  $V_{\text{OUT}}$  using the VOUT\_S pin to detect  $V_{\text{OUT}}$  over-voltage (OV) conditions. When  $V_{\text{OUT}}$  exceeds the OVP threshold (default 120% of  $V_{\text{OUT\_SET}}$ ), OVP is triggered. There are three OVP modes that are selectable via the I²C: discharge mode (default), stop switching mode, and latch-off mode.

In discharge mode, LS-FET turns on to discharge V<sub>OUT</sub> when a OV fault is detected. LS-FET remains on until its current reaches the negative current limit. In stop switching mode, the MPM3593 stops switching when an OV fault is detected and resumes switching once the fault is removed. In latch-off mode, the MPM3593 stops operating when OVP is triggered until the device starts up again.

#### Input Over-Voltage Protection (OVP)

The MPM3593 offers an optional input OVP. The OVP threshold can be set to 28V, 34V, or 40V. If  $V_{\rm IN}$  exceeds the OVP threshold, then the MPM3593 stops switching. The device resumes normal operation once the input OVP is removed. OVP is a non-latch protection. The input OVP threshold and hysteresis can be set via the I<sup>2</sup>C interface.

#### Thermal Shutdown

The MPM3593 provides over-temperature protection by monitoring the IC temperature internally. Over-temperature protection prevents the chip from operating at an exceedingly high temperature. If the junction temperature ( $T_J$ ) exceeds the threshold, the MPM3593 shuts down. Once  $T_J$  drops with a hysteresis (default 25°C), the device resumes operation by initiating a SS. Over-temperature protection is a non-latch protection. The over-temperature protection threshold and hysteresis can be set via the I²C interface.

# Floating Driver and Bootstrap (BST) Charging

An internal bootstrap (BST) capacitor ( $C_{BST}$ ) supplies the floating power MOSFET driver. The floating driver has its own UVLO protection with a 2.4V rising threshold and 200mV hysteresis. When the LS-FET is on, the  $C_{BST}$  voltage is charged to about 5V from VCC via a P-channel MOSFET pass transistor.

When the voltage from BST to SW ( $V_{BST-SW}$ ) drops below the UVLO threshold, the HS-FET turns off and the LS-FET turns on with a high-side (HS) minimum off time to conduct and refresh the charge on  $C_{BST}$ .

#### **Low-Dropout Operation (BST Refresh)**

To improve dropout, the MPM3593 is designed to operate at close to 100% duty cycle if  $V_{\rm BST-SW}$  exceeds its UVLO threshold. When  $V_{\rm IN}$  drops, the HS-FET remains on and close to 100% duty cycle to maintain output regulation until  $V_{\rm BST-SW}$  falls below the UVLO threshold.

Since the supply current sourced from  $C_{\text{BST}}$  is low, the BST charge refresh occurs infrequently and the HS-FET can remain on for more switching cycles. Thus, the switching regulator's effective duty cycle is high. During the regulator's dropout, the effective duty cycle is mainly influenced by the voltage drops across the power MOSFET, inductor resistance, low-side (LS) diode, and PCB resistance.

#### I<sup>2</sup>C Control and Default Output Voltage (V<sub>OUT</sub>)

When the MPM3593 is enabled, EN is pulled high and  $V_{\text{IN}}$  exceeds UVLO. The MPM3593 starts up to a default  $V_{\text{OUT}}$ , after which the I<sup>2</sup>C bus can communicate with the master to set the internal configuration using valid I<sup>2</sup>C commands.

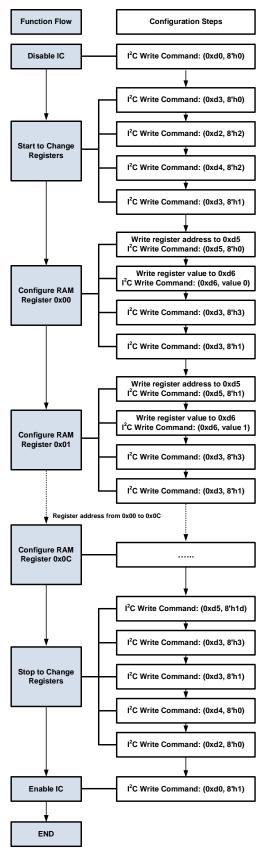

Configure  $V_{\text{OUT}}$  by adjusting  $V_{\text{REF}}$  and the output FB divider ratio. Before adjusting  $V_{\text{OUT}}$  or changing any other register value, write 0x00 to register 0h to send an operation off command from the master controller, which disables the output. Then send commands to adjust the necessary parameters. After that, the MPM3593 resumes operation by receiving an operation on command. The MPM3593 does not support adjusting the internal RAM parameters on the fly, including  $V_{\text{OUT}}$  (see Figure 9 on page 22). It is recommended to exclusively use the MPS communication interface and GUI to get access

to the MPM3593. If access through a local microcontroller unit (MCU) is required, contact MPS for more application information.

#### Frequency Dithering for Low EMI

The MPM3593 supports frequency dithering to reduce EMI, especially for EMI-sensitive applications. By using spread-spectrum modulation, the converter's frequency spectrum is spread, which in turn spreads the energy of the switching harmonics across a wider band. This reduces the switching harmonic amplitude and helps meet stringent EMI requirements. The frequency dithering range and cycle can be set via the I<sup>2</sup>C interface.

# Multi-Page One-Time Programmable (OTP) Memory (10)

The MPM3593 includes three pages of one-time programmable (OTP) memory to permanently store the desired settings.

To ensure long-term reliability, a differential OTP cell is used instead of a single-ended OTP cell. Data is stored on two floating-gate avalanche-injection metal-oxide semiconductor (FAMOS) devices, and output comparators are used for differential reading.

The first page of the multi-page OTP memory is configured with the manufacturer default values. The second and third pages can be configured using MPS's GUI. Once the device is enabled, the default values on the first page set the control parameters in the registers. If there is data on other pages, the newest configuration is automatically loaded into the I<sup>2</sup>C registers. The GUI checks whether the part is completely configured as well as the remaining blank pages. For more information about the I<sup>2</sup>C register configuration, see the Register Map section on page 23 and the Register Description section on page 25.

#### Note:

The V<sub>OUT</sub> bias function must be disabled before configuring the MPM3593's multi-page OTP memory.

#### I<sup>2</sup>C INTERFACE

#### I<sup>2</sup>C Serial Interface

The I2C is a two-wire, bidirectional serial interface that consists of a data line (SDA) and a clock line (SCL). The lines are externally pulled to a bus voltage (V<sub>BUS</sub>) when they are idle. A master device connected to the line generates the SCL signal and device address, then arranges the communication sequence. The MPM3593 interface is an I<sup>2</sup>C slave that supports fast mode (400kHz), which adds flexibility to the power supply solution. The MPM3593's SDA and SCL can be pulled up from 1.8V to 5V for different systems. V<sub>OUT</sub>, the transition slew rate, other interesting parameters can be instantaneously controlled via the I<sup>2</sup>C interface.

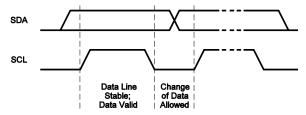

#### **Data Validity**

A clock pulse is generated for each transferred data bit. The data on the SDA line must be stable during the clock's high period. The data line's high or low state can only change when the SCL line's clock signal is low (see Figure 5).

Figure 5: Bit Transfer on the I<sup>2</sup>C Bus

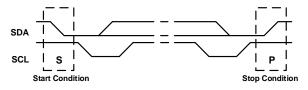

#### **Start and Stop Commands**

The start (S) and stop (P) commands are signaled by the master device, indicating the beginning and the end of the I2C transfer. In the start condition, the SDA signal transitions from high to low while the SCL remains high. In the stop condition, the SDA signal transitions from low to high while the SCL remains high (see Figure 6).

Figure 6: Start and Stop Conditions

The master always generates the start and stop commands. After the start command, the bus is busy and is not free until at least 4.7µs after the stop command. If a repeated start (Sr) command is generated instead of a stop command, then the bus stays busy. The start and repeated start conditions are functionally identical.

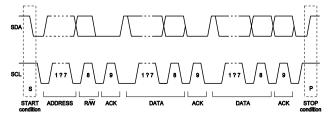

#### **Transfer Data**

Each byte on the SDA line must be 8 bits long and followed by an acknowledge (ACK) bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse, so that it remains stable and low during the clock pulse's high period.

Figure 7 shows a complete data transfer.

Figure 7: A Complete Data Transfer

After the start command, a 7-bit slave address is sent, followed by an 8th data direction bit (R/W), where 1 = read to indicate a data request, and 0 = write to indicate a transmission. A data transfer is always terminated by a stop command generated by the master. However, if a master wants to continue communicating on the bus, it can generate a repeated start command and address another slave without having to generate a stop command.

#### I<sup>2</sup>C Update Sequence

The MPM3593 requires a start command, valid I<sup>2</sup>C address, register address byte, and data byte for a single data update. The MPM3593 acknowledges receiving each byte by pulling the SDA line low during a single clock pulse's high period. A valid I2C address selects the MPM3593. The MPM3593 performs an update on the least significant bit (LSB) byte's falling edge.

#### I<sup>2</sup>C Chip Address

The I<sup>2</sup>C address is configured via the ADD pin. The MPM3593 supports eight addresses for up to eight voltage rails that are configured via the ADD resistor (R<sub>ADD</sub>). The master sends a 7-bit address, followed by an 8th data direction bit to indicate a read/write (R/W) operation.

Table 1 shows I<sup>2</sup>C address setting details.

Table 1: I<sup>2</sup>C Address Setting

| 1% Resistor (kΩ) | I <sup>2</sup> C Address |

|------------------|--------------------------|

| 0 to 20          | 21h                      |

| 23 to 45         | 22h                      |

| 49 to 71.5       | 23h                      |

| 73.5 to 97.3     | 24h                      |

| 100 to 124       | 25h                      |

| 127 to 147       | 26h                      |

| 150 to 174       | 27h                      |

| >178             | 28h                      |

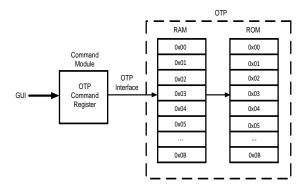

#### I<sup>2</sup>C Interface Diagram Block

MPS's GUI can send I2C commands to the MPM3593 to generate the OTP interface time that controls the OTP to process RAM/ROM operation. Figure 8 shows the I2C interface diagram block.

Figure 8: I<sup>2</sup>C Interface Diagram Block

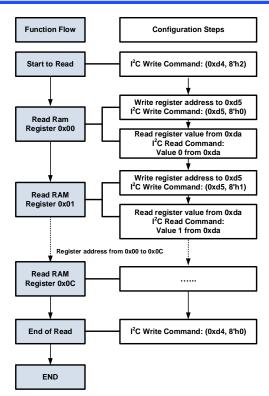

Note that the registers included in the Register Map section on page 23 are not directly addressed via the I2C. The MPM3593 uses an internal command module to access user registers. These commands are supported by the GUI and are not fully described in this datasheet. Please contact MPS or visit the MPS website to download the GUI. In addition, users can access the RAM and ROM with a customized controller. If a local MCU is required to write, read, or configure the device, please contact MPS for more application information. Figure 9 and Figure 10 on page 22 show the R/W operation of the RAM registers.

Figure 9: MPM3593 RAM Registers Write Operation Process

Figure 10: MPM3593 RAM Registers Read Operation Process

4/1/2024

# **REGISTER MAP**

| Add | R/W | D7                                       | D6                                                                   | D5                                                                        | D4                                | D3                           | D2                 | D1                               | D0                        |                             |  |              |                       |

|-----|-----|------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------|------------------------------|--------------------|----------------------------------|---------------------------|-----------------------------|--|--------------|-----------------------|

| 00h | R/W |                                          |                                                                      | REFER                                                                     | RENCE_VOLTAGE                     | (DAC)                        | •                  |                                  |                           |                             |  |              |                       |

| 01h | R/W | FREQUENCY_<br>DITHERING<br>(EN disabled) | FREQUENCY<br>_DITHERING<br>(dithering<br>cycle)                      | FREQUENCY<br>_DITHERING<br>(dithering<br>range)                           | INPUT_OVP_<br>HYSTERESIS          | INPUT_OVP_<br>THRESHOLD      |                    | FB_DIVID                         | ER_RATIO                  |                             |  |              |                       |

| 02h | R/W | N/A                                      | PHASE_<br>SHIFT                                                      |                                                                           | SWI                               | TCHING_                      | FREQUE             | ENCY                             |                           |                             |  |              |                       |

| 03h | R/W | COMPENSAT                                | TION (C <sub>COMP2</sub> )                                           | COMP                                                                      | ENSATION (R <sub>T</sub> )        |                              |                    | COMPENSATION                     | V (R <sub>COMP</sub> )    |                             |  |              |                       |

| 04h | R/W | SOFT_STA                                 | ART_TIME                                                             | SLOPE_COMPENSATION COMPENSAT                                              |                                   | SLOPE_COMPENSATION COMPENSAT |                    | SLOPE_COMPENSATION COMPENS       |                           | SLOPE_COMPENSATION COMPENSA |  | COMPENSATION | (C <sub>COMP1</sub> ) |

| 05h | R/W | N/A                                      | EN_RISING_                                                           | HRESHOLD EN_RISING_ VIN_UVLO_RISING_ HYSTERESIS THRESHOLD                 |                                   | VIN_UVLO_<br>HYSTERESIS      |                    |                                  |                           |                             |  |              |                       |

| 06h | R/W | SCP_N                                    | SCP_MODE PEAK_CURRENT_LIMIT_THRESHOLD VALLEY_CURRENT_LIMIT_THRESHOLD |                                                                           |                                   |                              | N/A                |                                  |                           |                             |  |              |                       |

| 07h | R/W | OVE<br>TEMPERATURE<br>RISING_TH          | _PROTECTION_                                                         | OTP_<br>HYSTERESIS                                                        | OUTPUT_OVP_                       | MODE                         |                    | JT_OVP_RISING<br>HRESHOLD        | OUTPUT_OVP<br>_HYSTERESIS |                             |  |              |                       |

| 08h | R/W | PG_LOWER_<br>HYSTERESIS                  | PG_LOWER_<br>RISING_<br>THRESHOLD                                    | PG_UPPER_<br>HYSTERESIS                                                   | PG_UPPER_<br>RISING_<br>THRESHOLD |                              | P_<br>CTION_<br>ME | SCP_<br>TRIGGERED_<br>FB_VOLTAGE | N/A                       |                             |  |              |                       |

| 09h | R/W | /FT_SETTING                              | SYNCIN/OUT                                                           | HICCUP_ SWITCHING_SLEW_ SWITCHING_SLEW_ DUTY RATE (falling) RATE (rising) |                                   |                              |                    | N/A                              |                           |                             |  |              |                       |

| 0Ah | R/W |                                          | N/A                                                                  |                                                                           |                                   |                              |                    |                                  |                           |                             |  |              |                       |

| 0Bh | R/W |                                          | AAM_MODE_                                                            | OUT_BIAS                                                                  | NA                                |                              |                    |                                  |                           |                             |  |              |                       |

# **REGISTER DESCRIPTION**

| Register<br>Description                  | Add  | Bits   | Default<br>Code | Default<br>Value   | Range/Values                                                                    | Min<br>Value | Max<br>Value | Resolution<br>/LSB | Units                         |

|------------------------------------------|------|--------|-----------------|--------------------|---------------------------------------------------------------------------------|--------------|--------------|--------------------|-------------------------------|

| Reference Voltage (DAC)                  | 0x00 | D[7:0] | 01100100        | 1                  | 0.6V to 2.55V                                                                   | 0.60         | 2.55         | 0.01               | V                             |

| FB Divider Ratio                         | 0x01 | D[1:0] | 01              | 1/5                | 1/2, 1/5, 1/5, 1                                                                | 1/5          | 1            | -                  | -                             |

| Input OVP<br>Threshold                   | 0x01 | D[3:2] | 00              | No OVP             | No OVP, 28V,<br>34V, 40V                                                        | 28           | 40           | -                  | V                             |

| Input OVP<br>Hysteresis                  | 0x01 | D[4]   | 1               | 3.5                | 5.5, 3.5                                                                        | 3.5          | 5.5          | -                  | % of V <sub>IN</sub>          |

| Frequency<br>Dithering (Range)           | 0x01 | D[5]   | 1               | 3/48               | 3/28, 3/48                                                                      | 3/48         | 3/28         | -                  | f <sub>SW</sub>               |

| Frequency Dithering (Cycle)              | 0x01 | D[6]   | 1               | 150                | 120, 150                                                                        | 120          | 150          |                    | μs                            |

| Frequency<br>Dithering                   | 0x01 | D[7]   | 0               | Disable            | Disable, enable                                                                 | -            | -            | -                  | -                             |

| Switching<br>Frequency                   | 0x02 | D[5:0] | 001010          | 500                | 250 to 2500                                                                     | 250          | 2500         | 50                 | kHz                           |

| Phase Shift                              | 0x02 | D[6]   | 0               | 0                  | 0, 180                                                                          | 0            | 180          | -                  | ٥                             |

| Reserved                                 | 0x02 | D[7]   | 0               | N/A                | -                                                                               | -            | -            | -                  | -                             |

| Compensation, (R <sub>COMP</sub> )       | 0x03 | D[2:0] | 011             | 700                | 400, 500, 600,<br>700, 800, 900,<br>1000, 1100                                  | 400          | 1100         | -                  | kΩ                            |

| Compensation (R <sub>T</sub> )           | 0x03 | D[5:3] | 011             | 60                 | 0, 20, 40, 60,<br>80, 100, 120,<br>140                                          | 0            | 140          | -                  | kΩ                            |

| Compensation (C <sub>COMP2</sub> )       | 0x03 | D[7:6] | 00              | 0.5                | 0.5                                                                             |              |              | -                  | pF                            |

| Compensation (C <sub>COMP1</sub> )       | 0x04 | D[2:0] | 000             | 40                 | 40, 45                                                                          | 40           | 45           | -                  | pF                            |

| Slope<br>Compensation                    | 0x04 | D[5:3] | 000             | 750                | 750, 600, 450,<br>300, 750, 900,<br>1050, 1200                                  | 300          | 1200         | -                  | mV                            |

| Soft-Start Time                          | 0x04 | D[7:6] | 01              | 1                  | 0.5, 1, 2, 4                                                                    | 0.5          | 4            | -                  | ms                            |

| V <sub>IN</sub> UVLO<br>Hysteresis       | 0x05 | D[0]   | 1               | 4                  | 2, 4                                                                            | 2            | 4            | -                  | % of V <sub>IN_UVLO_VTI</sub> |

| V <sub>IN</sub> UVLO Rising<br>Threshold | 0x05 | D[3:1] | 000             | 3.2                | 3.2, 3.8, 4.4, 5,<br>5.6, 6.2, 6.8, 7.4                                         | 3.2          | 7.4          | -                  | V                             |

| EN Rising<br>Hysteresis                  | 0x05 | D[4]   | 0               | 220                | 220, 420                                                                        | 220          | 420          | -                  | mV                            |

| EN Rising<br>Threshold                   | 0x05 | D[6:5] | 01              | 1.4                | 1.2, 1.4,1.6, 2                                                                 | 1.2          | 2            | -                  | V                             |

| Reserved                                 | 0x05 | D[7]   | 0               | N/A                | -                                                                               | -            | -            | -                  | -                             |

| Reserved                                 | 0x06 | D[0]   | 0               | N/A                | -                                                                               | -            | -            | -                  | -                             |

| Valley Current Limit<br>Threshold        | 0x06 | D[2:1] | 10              | 4                  | 2, 3, 4                                                                         | 2            | 4            | -                  | А                             |

| Peak Current Limit<br>Threshold          | 0x06 | D[5:3] | 000             | 5                  | 5, 6, 7, 8, 4, 3, 2                                                             | 2            | 8            | -                  | Α                             |

| SCP Mode                                 | 0x06 | D[7:6] | 00              | Hiccup             | Hiccup, latch,<br>switching with<br>non-hiccup,<br>switching with<br>non-hiccup | -            | -            | -                  | -                             |

| Output OVP<br>Hysteresis                 | 0x07 | D[0]   | 0               | 5.7                | 5.7, 3.2                                                                        | 3.2          | 5.7          | -                  | % of V <sub>OUT_SET</sub>     |

| Output OVP Rising<br>Threshold           | 0x07 | D[2:1] | 01              | 120                | 110, 120, 130                                                                   | 110          | 130          | -                  | % of V <sub>OUT_SET</sub>     |

| Output OVP Mode                          | 0x07 | D[4:3] | 01              | Stopping switching | Discharge,<br>stopping<br>switching, latch,<br>latch                            | -            | -            | -                  | -                             |

# REGISTER DESCRIPTION (continued)

| Register<br>Description                      | Add  | Bits   | Default<br>Code | Default<br>Value | Range/Values                                                                                    | Min<br>Value | Max<br>Value | Resolution /LSB | Units                     |

|----------------------------------------------|------|--------|-----------------|------------------|-------------------------------------------------------------------------------------------------|--------------|--------------|-----------------|---------------------------|

| Over-Temperature<br>Protection<br>Hysteresis | 0x07 | D[5]   | 0               | 25               | 25, 50                                                                                          | 25           | 50           | -               | °C                        |

| Over-Temperature Protection Rising Threshold | 0x07 | D[7:6] | 10              | 175              | 125, 150, 175                                                                                   | 125          | 175          | -               | °C                        |

| Reserved                                     | 0x08 | D[0]   | 0               | N/A              | -                                                                                               | -            | -            | -               | -                         |

| SCP Triggered FB<br>Voltage                  | 0x08 | D[1]   | 0               | 50               | 50, 75                                                                                          | 50           | 75           | -               | % of V <sub>REF</sub>     |

| SCP Detection<br>Time                        | 0x08 | D[3:2] | 01              | 128              | 256, 128, 64, 32                                                                                | 32           | 256          | -               | f <sub>SW</sub>           |

| PG Upper Rising<br>Threshold                 | 80x0 | D[4]   | 0               | 110              | 110, 115                                                                                        | 110          | 115          | -               | % of V <sub>OUT_SET</sub> |

| PG Upper<br>Hysteresis                       | 80x0 | D[5]   | 0               | 5.5              | 5.5, 3                                                                                          | 3            | 5.5          | -               | % of V <sub>OUT SET</sub> |

| PG Lower Rising<br>Threshold                 | 0x08 | D[6]   | 0               | 89               | 89, 84                                                                                          | 84           | 89           | -               | % of V <sub>OUT SET</sub> |

| PG Lower<br>Hysteresis                       | 0x08 | D[7]   | 0               | 5.5              | 5.5, 3                                                                                          | 3            | 5.5          | -               | % of V <sub>OUT_SET</sub> |

| Reserved                                     | 0x09 | D[0]   | 0               | N/A              | -                                                                                               | -            | -            | -               |                           |

| Switching Slew<br>Rate (Rising) (11)         | 0x09 | D[2:1] | 00              | 1                | 1, 2, 3, 4                                                                                      | 1            | 4            | -               | V/ns                      |

| Switching Slew<br>Rate (Falling) (11)        | 0x09 | D[4:3] | 00              | 1                | 1, 2, 3, 4                                                                                      | 1            | 4            | -               | V/ns                      |

| Hiccup Duty (On Time)                        | 0x09 | D[5]   | 0               | 10               | 10, 20                                                                                          | 10           | 20           | -               | %                         |

| SYNC In/Out                                  | 0x09 | D[6]   | 1               | SYNC in          | SYNC out,<br>SYNC in                                                                            | -            | -            | -               | -                         |

| /FT Setting                                  | 0x09 | D[7]   | 1               | Auto-<br>reset   | EN must restart<br>to reset the fault<br>status; Auto-<br>reset when fault<br>is removed        | -            | -            | -               |                           |

| AAM/CCM Control                              | 0x0A | D[0]   | 0               | AAM<br>mode      | AAM mode,<br>CCM                                                                                | -            | -            | -               |                           |

| Reserved                                     | 0x0A | D[7:1] | 0101000         | N/A              | -                                                                                               | -            | -            | -               |                           |

| Reserved                                     | 0x0B | D[0]   | 0               | N/A              | -                                                                                               | -            | -            | -               |                           |

| V <sub>OUT</sub> BIAS                        | 0x0B | D[2:1] | 00              | BIAS             | No BIAS, BIAS,<br>BIAS in sleep<br>mode only                                                    | -            | -            | -               |                           |

| PKC                                          | 0x0B | D[3]   | 1               | PKC              | PKC                                                                                             | -            | -            | -               |                           |

| AAM Threshold<br>(PKC)                       | 0x0B | D[7:4] | 1000            | 530              | Disable, 605,<br>680, 755, 830,<br>905, 980, 1055,<br>530, 455, 380,<br>305, 225, 150,<br>75, 0 | 0            | 1055         | -               | mA                        |

#### Note:

11) To limit the SW spike, do not use a switching slew rate above 2V/ns when the input exceeds 30V.

© 2024 MPS. All Rights Reserved.

#### APPLICATION INFORMATION

#### Setting the Output Voltage (Vout)

The MPM3593 has two options for setting  $V_{OUT}$ : internal divider mode and external divider mode. In internal divider mode, the internal FB reference voltage ( $V_{FB}$ ) and output FB divider ratio ( $D_{FB}$ ) are adjusted via the I<sup>2</sup>C. Based on REG00h, D[7:0], set  $V_{FB}$  between 0.6 and 2.55V at 10mV/LSB. Based on REG01h, D[0:1], set  $D_{FB}$  to 1/5, 1/2, and 1.  $V_{OUT}$  depends on  $V_{FB}$  and  $D_{FB}$ , and can be calculated with Equation (1):

$$V_{OUT} = \frac{V_{FB}}{D_{FB}} \tag{1}$$

For example, if  $V_{FB}$  is 1V and  $D_{FB}$  is 1/5, then  $V_{OUT}$  is 5V.

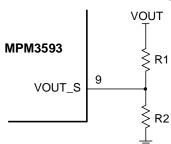

In external divider mode,  $D_{FB}$  should be set to 1 and  $V_{FB}$  can be set between 0.6V and 2.55V. Adjust the values of the external divider resistors connected to VOUT to set  $V_{OUT}$  (see Figure 11).

Figure 11: External Divider Mode

V<sub>OUT</sub> in external divider mode can be calculated with Equation (2):

$$V_{OUT} = \frac{R1 + R2}{R2} \times V_{FB}$$

(2)

The external divider resistance is recommended to be between  $10k\Omega$  and  $100k\Omega$ .

#### Selecting the Input Capacitor (C<sub>IN</sub>)

The step-down converter has a discontinuous input current ( $I_{\text{IN}}$ ), and requires a capacitor to supply AC current to the converter while maintaining the DC  $V_{\text{IN}}$ . For the best performance, it is recommended to use low-ESR capacitors. Ceramic capacitors with X5R or X7R dielectrics are strongly recommended due to their low ESR and small temperature coefficients.

For most applications, a  $4.7\mu\text{F}$  to  $10\mu\text{F}$  capacitor at the input is sufficient. To absorb high-frequency switching noise, it is strongly recommended to use another lower-value capacitor (e.g.  $0.1\mu\text{F}$ ) with a small package size (0603). Place the small-size capacitor as close to the VIN and GND pins as possible.

The input capacitor ( $C_{IN}$ ) requires an adequate ripple current rating to absorb the switching  $I_{IN}$ .  $C_{IN}$ 's RMS current can be estimated with Equation (3):

$$I_{CIN} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(3)

The worst-case condition occurs at  $V_{IN} = 2 x V_{OUT}$ , which can be calculated with Equation (2):

$$I_{CIN} = \frac{I_{LOAD}}{2} \tag{4}$$

For simplification, choose a  $C_{\text{IN}}$  with an RMS current rating that exceeds half of the maximum load current.

$C_{\text{IN}}$  can be electrolytic, tantalum, or ceramic. When using electrolytic or tantalum capacitors, place a small, high-quality, ceramic capacitor (e.g.  $0.1\mu\text{F}$ ) as close to the IC as possible. When using ceramic capacitors, ensure that the capacitor has sufficient capacitance to prevent excessive voltage ripple at input. The input voltage ripple ( $\Delta V_{\text{IN}}$ ) caused by the capacitance can be estimated with Equation (5):

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_{SW} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(5)

#### Selecting the Output Capacitor (Cout)

The output capacitor ( $C_{OUT}$ ) maintains the DC  $V_{OUT}$ . It is recommended to use ceramic, tantalum, or low-ESR electrolytic capacitors. For the best results, low-ESR capacitors are recommended to effectively limit the output voltage ripple ( $\Delta V_{OUT}$ ).  $\Delta V_{OUT}$  can be estimated with Equation (6):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \cdot (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \cdot (R_{\text{ESR}} + \frac{1}{8f_{\text{SW}} \times C_{\text{OUT}}}) \tag{6}$$

Where L is the fixed inductance at  $3\mu H$ , and  $R_{ESR}$  is the  $C_{OUT}$ 's equivalent series resistance (ESR).

When using ceramic capacitors, the capacitance dominates the impedance at  $f_{SW}$  and causes the majority of  $\Delta V_{OUT}$ . For simplification,  $\Delta V_{OUT}$  can be estimated with Equation (7):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_{\text{SW}}^2 \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})$$

(7)

For tantalum or electrolytic capacitors, the ESR dominates the impedance at  $f_{SW}$ . For simplification,  $\Delta V_{OUT}$  can be approximated with Equation (8):

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}}) \times R_{ESR}$$

(8)

The  $C_{\text{OUT}}$  characteristics also affect the stability of the regulation system. The MPM3593 can be optimized for a wide range of capacitance and ESR values.

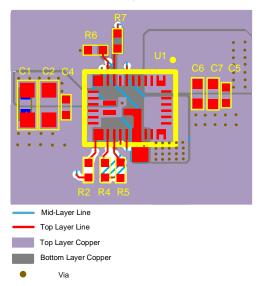

#### **PCB Layout Guidelines**

PCB layout is critical for stable operation. A 4-layer layout is recommended to improve thermal performance. For the best results, refer to Figure 12 and follow the guidelines below:

- Keep the C<sub>IN</sub> power loop as small as possible.

- Connect a large ground plane directly to PGND. If the bottom layer is a ground plane, add vias near PGND.

- Ensure that the high-current paths at GND and VIN have short, direct, and wide traces.

- Place the ceramic C<sub>IN</sub>, especially the smallsize bypass C<sub>IN</sub> ,as close to VIN and PGND as possible to minimize high-frequency noise.

- Connect VIN, VOUT, and GND to a large copper area to cool the chip, which improves thermal performance and long-term reliability.

- Place an integrated GND at the mid-layer or bottom layer.

- Use multiple vias to connect the power planes to the mid-layers.

Figure 12: Recommended PCB Layout (12)

#### Note:

12) This PCB layout covers a full range of specs. For specific cases such as having a higher f<sub>SW</sub>, lower V<sub>IN</sub>, or lower I<sub>OUT</sub>, a much smaller layout size can also be achieved by selecting smaller packages for the capacitors.

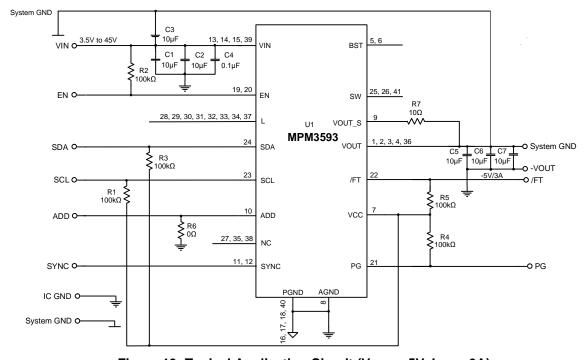

## TYPICAL APPLICATION CIRCUITS (13) (14)

Figure 12: Typical Application Circuit (V<sub>OUT</sub> = 3.3V/5V/12V, I<sub>OUT</sub> = 3A)

Figure 13: Typical Application Circuit (Vout = -5V, lout = 3A)

#### Notes:

- 13) If  $V_{\text{OUT}}$  exceeds 9V, use a  $100\Omega$  resistor for R7 and ensure that the  $V_{\text{OUT}}$  bias function is disabled.

- 14) If  $V_{OUT}$  exceeds 8V, ensure that  $V_{IN}$  does not exceed 24V.

# **DEFAULT OTP CONFIGURATION**

Table 2: MPM3593GQY-0001 Suffix Code Configuration

| OTP Items                     | Values   |

|-------------------------------|----------|

| Reference Voltage (DAC)       | 1V       |

| FB Divider Ratio              | 1/5      |

| Output Voltage                | 5V       |

| Mode                          | AAM Mode |

| SCP Mode                      | Hiccup   |

| Soft-Start Time               | 1ms      |

| Switching Slew Rate (Rising)  | 1V/ns    |

| Switching Slew Rate (Falling) | 1V/ns    |

| Valley Current Limit          | 4A       |

| Peak Current Limit            | 5A       |

| Switching Frequency           | 500kHz   |

| OTP Rising Threshold          | 175°C    |

| OTP Configuration Code        | 0x0001   |

Table 3: MPM3593GQY-0001 Suffix Code Register Value

| Suffix Code | Register | Hex Value |

|-------------|----------|-----------|

| 0001        | 0x00     | 64h       |

| 0001        | 0x01     | 71h       |

| 0001        | 0x02     | 0Ah       |

| 0001        | 0x03     | 1Bh       |

| 0001        | 0x04     | 40h       |

| 0001        | 0x05     | 21h       |

| 0001        | 0x06     | 04h       |