# 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### **FEATURES**

- 1.5W isolated DC/DC converter

- Programmable asymmetrical output voltages

- 9 18VDC input voltage range

- For IGBT/Si/SiC/Cascode GaN gate drive bias voltages

- High 5kVAC/1min reinforced isolation / 1.4kVDC working voltage

- High dV/dt immunity with 150kV/µs CMTI

- Full load 1.5W from -40°C to +90°C

- Less than 3.5pF isolation capacitance

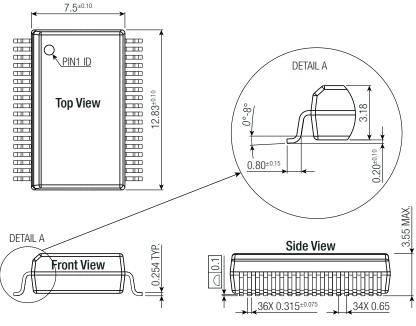

- Compact 7.5x12.83mm SMD package

- 3 year warranty

Dimensions (LxWxH):  $12.83 \times 7.5 \times 3.55$ mm (0.51 x 0.30 x 0.14 inch) 0.1g (0.0032 oz)

#### **SAFETY & EMC**

#### **APPLICATIONS**

### DESCRIPTION

The R12C2T12/R 1.5W isolated DC/DC converter is a versatile solution designed for isolated gate bias voltages, particularly for transistors such as IGBTs, Si and SiC MOSFETs, and Cascode GaNs. This compact converter features a wide input voltage range of 9 - 18VDC and programmable asymmetrical output voltages, ensuring precise control and performance optimization for power electronics applications. With high 5kVAC/1min isolation, 1.4kVDC working voltage, high 150kV/µs CMTI, and remarkable stability up to 120°C (0.5W), it offers superior reliability, even under harsh high power, high frequency switching environments. The ultra-low isolation capacitance, less than 3.5pF, ensures minimal noise propagation across the isolation barrier. All of these exceptional features are packaged in a compact 7.5 x 12.83mm SMD form factor, making it an ideal choice for all isolated gate bias voltage needs.

| SELECTION GUIDE |                                 |                                                                                         |                                |                           |

|-----------------|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------------------------|

| Part<br>Number  | Input Voltage<br>Range<br>[VDC] | Output Voltage<br>Range <sup>(1)</sup><br>[VDC]                                         | Output Current<br>max.<br>[mA] | Efficiency<br>typ.<br>[%] |

| R12C2T12/R      | 9 - 18                          | $V_{OUT+} = 2.5 - 15.5$<br>$V_{OUT-} = (-2.5) - (-15.5)^{(2)}$<br>$V_{TOTAL} = 10 - 18$ | I+= +100mA<br>I-= -12mA        | 47                        |

Note1:  $V_{\text{OUT+}}$  and  $V_{\text{OUT-}}$  can be set from 2.5VDC to 15.5VDC or -2.5VDC to -15.5VDC respectively but the total

must be within the range of 10VDC to 18VDC. For more information see "Typical Application" below.

Note2: For V<sub>OUT</sub>- between 0V and -2.5V please contact techsupport@recom-power.com

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

| ABSOLUTE MAXIMUM RATINGS (measured @ T <sub>AMB</sub> = 25°C, nom. V <sub>IN</sub> , full load and after warm-up unless otherwise stated) |                                                                                         |         |      |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------|------|--------|--|--|

| Parameter                                                                                                                                 | Symbol                                                                                  | Min.    | Тур. | Max.   |  |  |

|                                                                                                                                           | V <sub>IN</sub> to PGND                                                                 | -0.3VDC |      | 32VDC  |  |  |

| Absolute maximum voltage                                                                                                                  | CTRL, PG to PGND                                                                        | -0.3VDC |      | 7VDC   |  |  |

|                                                                                                                                           | $V_{\text{OUT+}},$ COM, FBV $_{\text{OUT+}},$ FBV $_{\text{OUT-}}$ to $V_{\text{OUT-}}$ | -0.3VDC |      | 32VDC  |  |  |

| Maximum internal power losses <sup>(3)</sup>                                                                                              | $T_{AMB} = +25^{\circ}C$                                                                |         |      | 2.45W  |  |  |

| Maximum output power                                                                                                                      | $V_{TOTAL} = V_{OUT+}$ to $V_{OUT-}$ , $T_{AMB} = +25$ °C                               |         |      | 2.5W   |  |  |

| Junction Temperature                                                                                                                      |                                                                                         | -40°C   |      | +150°C |  |  |

| Storage Temperature                                                                                                                       |                                                                                         | -65°C   |      | +150°C |  |  |

Note3: Exceeding maximum allowable power dissipation causes the device to enter thermal shut down which protects the device from permanent damage.

| Parameter                          | Symbol          | Condition                                            | Min.    | Min. Typ. |               |

|------------------------------------|-----------------|------------------------------------------------------|---------|-----------|---------------|

| Input Voltage Range                | V <sub>IN</sub> | refer to "Derating Graph"                            | 9VDC    | 12VDC     | Max.<br>18VDC |

| Lladar Valtara Laglant (LIVI O)(4) |                 | rising                                               | 7.8VDC  | 8.2VDC    | 8.5VDC        |

| Under Voltage Lockout (UVLO)(4)    |                 | falling                                              | 7VDC    | 7.4VDC    | 7.7VDC        |

| Over Voltage Lockout (OVLO)        |                 | rising                                               | 20.9VDC | 22VDC     | 23.1VDC       |

|                                    |                 | falling                                              | 19VDC   | 20VDC     | 21VDC         |

| Soft Start Time                    |                 |                                                      |         | 10ms      |               |

| Standby Current                    | Ι <sub>Q</sub>  | $V_{CTRL}$ = 0VDC, $V_{IN}$ = 8VDC to 18VDC          |         |           | 600μΑ         |

| Quiescent Current                  |                 | $V_{CTRL}$ = 5VDC, $V_{IN}$ = 8VDC to 18VDC, no load |         |           | 40mA          |

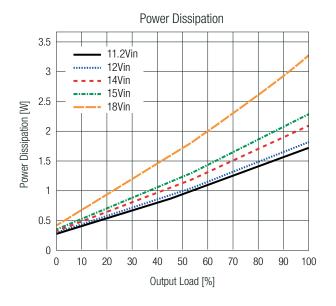

| Power Dissipation                  |                 | refer to "Power Dissipation"                         |         | 2.36W     |               |

| Switching Frequency                |                 | V <sub>IN</sub> = 12VDC, V <sub>OUT</sub> = 12VDC    |         | 20.5MHz   |               |

Note4: The R12C2T12/R can operate at  $V_N$ = 8VDC as long as  $V_N$  is higher as UVLO rising during start up.

| REGULATIONS                           |                 |                                                                 |           |        |           |  |  |

|---------------------------------------|-----------------|-----------------------------------------------------------------|-----------|--------|-----------|--|--|

| Parameter                             | Symbol          | Condition                                                       | Min.      | Тур.   | Max.      |  |  |

|                                       | V <sub>FB</sub> | FBV <sub>OUT+</sub> or FBV <sub>OUT-</sub> to V <sub>OUT-</sub> | OVDC      | 2.5VDC | 5.5VDC    |  |  |

| Feedback Voltage <sup>(5)</sup>       |                 | $V_{\text{OUT+}}$ to $V_{\text{OUT-}}$ in regulation            | 2.4675VDC | 2.5VDC | 2.5325VDC |  |  |

| Feedback V <sub>OUT+</sub> Hysteresis |                 | hysteresis at the FBV <sub>OUT+</sub> pin                       | 9mV       | 10mV   | 12.3mV    |  |  |

| Output Voltage Accuracy               |                 | 0.1% of FB resistors                                            | -1.3%     |        | 1.3%      |  |  |

Note5: For isolated gate driver applications, one positive and one negative output are needed. In this case,  $V_{OUT+}$  to  $V_{OUT-}$  is the total output voltage, and the middle point becomes the reference point. Because the total voltage between  $V_{OUT+}$  and  $V_{OUT-}$  is always regulated through the FBV<sub>OUT+</sub> feedback, the COM pin only must regulate the middle point voltage so that it can give the correct positive and negative voltages. The COM control is achieved through FBV<sub>OUT-</sub> pin as described in "Adjustability" section.

## 1.5W / 9V-18VDC / 36 Pin SSOP Package

BASIC CHARACTERISTICS (measured @ T<sub>AMB</sub>= 25°C, nom. V<sub>IN</sub>, full load and after warm-up unless otherwise stated)

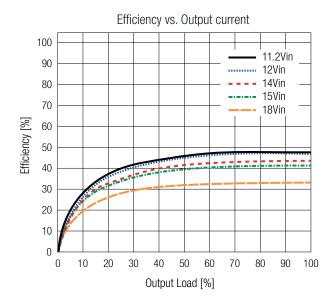

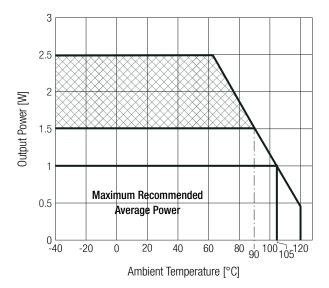

#### **Derating Graph**

Note6: Exceeding maximum allowable power dissipation causes device to enter thermal shutdown

which protects device from permanent damage.

Note7: Keep the average power at 1.5W max. or peak power 2.5W for 5 seconds max.

Note8: Test with Recom 50x50mm standard EVM board with 70µm copper, double layer

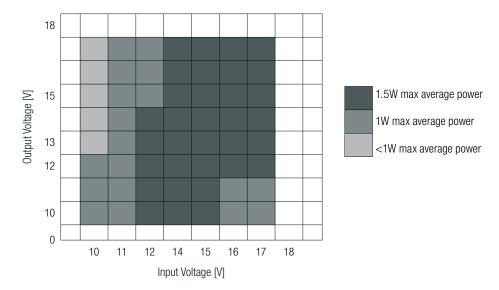

#### Input and output voltage power limitations

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

| ADJUSTABILITY           |                                        |        |      |                                        |  |  |  |

|-------------------------|----------------------------------------|--------|------|----------------------------------------|--|--|--|

| Parameter               | Condition                              | Min.   | Тур. | Max.                                   |  |  |  |

| Output Valtaga Trimming | V <sub>OUT+</sub> to V <sub>OUT-</sub> | 10VDC  |      | 18VDC                                  |  |  |  |

| Output Voltage Trimming | AGND to V <sub>OUT-</sub>              | 2.5VDC |      | V <sub>out+</sub> to V <sub>out-</sub> |  |  |  |

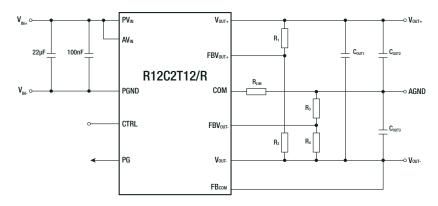

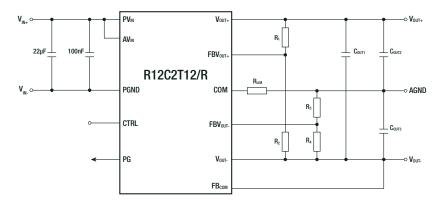

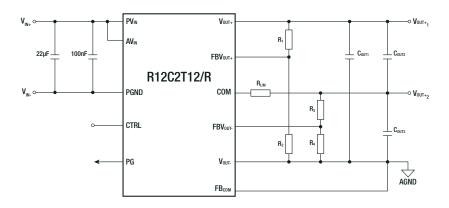

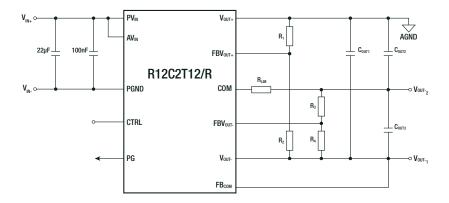

The R12C2T12/R module creates two regulated outputs. It can be configured as a single output converter,  $V_{OUT-}$  to  $V_{OUT-}$  only, or a dual-output converter,  $V_{OUT-}$  to  $V_{OUT-}$  and COM to  $V_{OUT-}$ . Even though the module uses  $V_{OUT-}$  as the reference point to create two positive output voltages, the outputs can use COM as the reference point and become a positive and a negative output.

These two outputs are controlled independently through hysteresis control. Furthermore, the  $V_{OUT-}$  to  $V_{OUT-}$  is the main output, and COM to  $V_{OUT-}$  uses the main output as its input to create a second regulated output voltage.

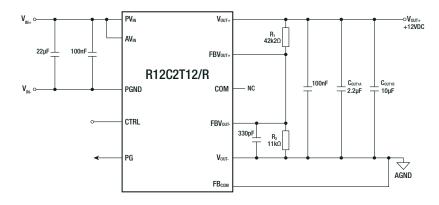

#### **Typical Application**

$V_{TOTAL}$  = 10-18VDC,  $P_{MAX}$  = 2.5 watts

#### Example

To set the device into dual configuration, for example to +13/-5V, start to define main output voltage as the sum of both desired voltages (|13V| + |-5V| = 18V). 18V are  $V_{OUT-}$ . Then set the negative output.

- +13/-5 V<sub>TOTAL</sub>= 18VDC, V<sub>OUT</sub>= -5VDC

- +15/-3  $V_{TOTAL} = 18VDC$ ,  $V_{OUT} = -3VDC$

- +10/-5  $V_{TOTAL} = 15VDC, V_{OUT} = -5VDC$

Note9: Set V<sub>TOTAL</sub> first and afterwards V<sub>OUT-</sub>, V<sub>TOTAL</sub> must be between 10VDC and 18VDC

## 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### TRIM FUNCTION

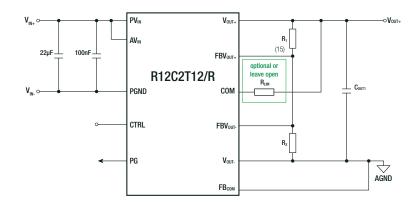

#### Setting the Main Output - Single Configuration

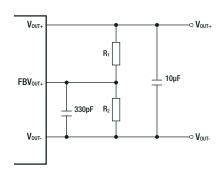

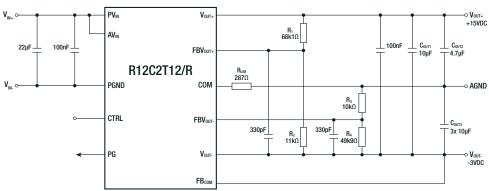

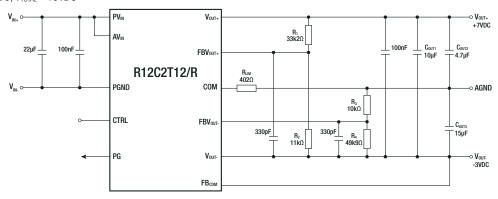

The  $V_{0UT+}$  to  $V_{0UT-}$  output is the primary module output, regulated by the sensed voltage on FBV<sub>0UT+</sub> pin. The  $V_{0UT+}$  to  $V_{0UT-}$  voltage is sensed through a voltage divider (R1 and R2). When FBV<sub>0UT+</sub> voltage is below the turn-off threshold (approx. 10mV above the 2.5V reference), the power stage operates, raising the output voltage. Once the output reaches the turn-off threshold, the power stage turns off, causing the voltage to drop due to load current. When the output voltage falls below the turn-on threshold (approx. 10 mV below the 2.5V reference), the power stage is reactivated. Precise voltage reference and hysteresis control ensure accurate regulation. For enhanced noise immunity, add a 330pF capacitor between FBV<sub>0UT+</sub> and V<sub>0UT-</sub> pins, avoiding excessive capacitance to prevent output voltage ripple or stability issues. If only a single output is required, connect FBV<sub>0UT+</sub> to FBV<sub>0UT+</sub> and leave COM pin open.

#### Calculation

$$R_1 = \frac{(V_{OUT+} - V_{ref})}{V_{ref}} \times R_2$$

#### Example

$$R_1 = \frac{(18V - 2.5V)}{(2.5V)} \times 11k\Omega = 68k2\Omega$$

Recommended resistor values for common V<sub>OUT+</sub>:

| V <sub>OUT+</sub> [VDC] | $R_2[\Omega]$ | R <sub>1</sub> [Ω] |

|-------------------------|---------------|--------------------|

| 10                      |               | 33k2               |

| 11                      |               | 37k4               |

| 12                      |               | 42k2               |

| 13                      | 11k           | 46k4               |

| 14                      |               | 51k1               |

| 15                      |               | 54k9               |

| 16                      |               | 59k                |

| 17                      |               | 63k4               |

| 18                      |               | 68k1               |

\*(according to E96)

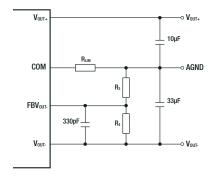

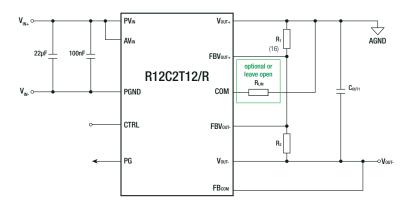

#### Setting the Second Output - Dual Configuration

For isolated gate drivers,  $V_{OUT-}$  to  $V_{OUT-}$  provides the regulated total voltage with the midpoint as the reference. The COM pin regulates the midpoint voltage for accurate positive and negative outputs based on FBV<sub>OUT+</sub> feedback.

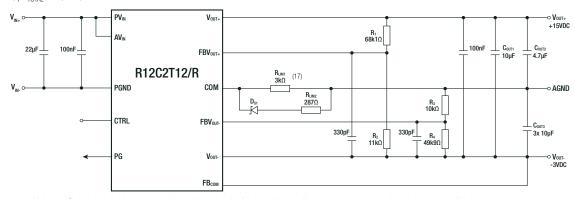

In Figure below, COM to  $V_{OUT}$  is monitored through R3 and R4 on FBV<sub>OUT</sub>. A 330pF capacitor on FBV<sub>OUT</sub> filters noise. Charging resistor activation, controlled by FBV<sub>OUT</sub>, raises COM to  $V_{OUT}$  voltage. After reaching the stop charging threshold, the charging resistor turns off. The discharge resistor, with a 20mV hysteresis, is then controlled by FBV<sub>OUT</sub>.

The COM to  $V_{OUT}$  regulator protects against prolonged high-side FET activation during a COM to  $V_{OUT}$  short. It monitors COM pin voltage, adjusting the high-side FET duty ratio. If COM pin voltage is below 0.645V while FBV<sub>OUT</sub> is under 2.48V, a 20% duty ratio control overrides normal hysteresis. When COM pin voltage exceeds 0.73V, duty ratio control is disabled, and normal operation resumes.

#### Calculation

$$R_3 = \frac{(V_{OUT-} - V_{ref})}{V_{ref}} \times R_4$$

#### Example

$$R_3 = \frac{(5V - 2.5V)}{2.5V} \times 49k9\Omega = 49k9\Omega$$

Recommended resistor values for common V<sub>OUT</sub>.:

| V <sub>OUT-</sub> [VDC] | $R_4[\Omega]$ | $R_3[\Omega]$ |

|-------------------------|---------------|---------------|

| 3                       | 49k9          | 10k           |

| 4                       |               | 30k1          |

| 5                       |               | 49k9          |

| 9                       |               | 130k          |

\*(according to E96)

Note10: To achieve -2.5V on the  $V_{OUT}$ , output remove R4 and use a value between  $10k\Omega$  and  $100k\Omega$  for R3.

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

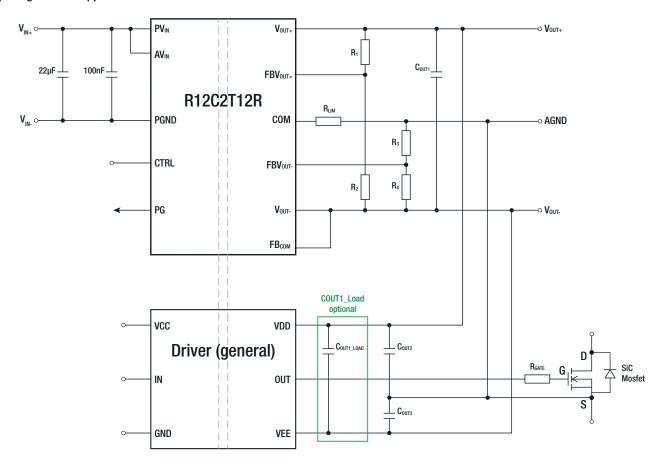

#### CAPACITOR SELECTION

For CIN place a  $10^{-}\mu\text{F}$  or more and a  $0.1^{-}\mu\text{F}$  high-frequency decoupling capacitor in parallel close to VIN pins. A capacitance greater than  $10\mu\text{F}$  can be used to reduce the voltage ripple when the series impedance from the voltage source to the VIN pins is large. For COUT1 add a  $2.2\mu\text{F}$  or more and a  $100\mu\text{F}$  capacitor for high-frequency decoupling of VOUT+ to VOUT-. Place the capacitors close to the VOUT+ and VOUT- pins. A capacitance greater than  $2.2\mu\text{F}$  can be used to reduce the output voltage ripple. The selection of COUT2 and COUT3 is based on the gate charge requirement for the gate driver load, the charge balancing during the start-up, and the expected maximum current loading. COUT2 and COUT3 capacitors should be placed close to the load. Calculate COUT2 first.

#### Minimal COUT2 Calculation

$$C_{out2} \stackrel{\text{(11)}}{=} \frac{Q}{V_{out+} * \frac{V_{pp}}{100}}$$

| P                 | Unit             |     |

|-------------------|------------------|-----|

| Q                 | gate charge      | nC  |

| V <sub>PP</sub>   | accepted Ripple  | %   |

| $V_{\text{OUT+}}$ | output voltage + | VDC |

Recommended COUT2 value is about 10 times higher than the calculated minimum. For simplification, it is recommended to use values for COUT2 between 2.2uF and 10uF. Use the following simplified formula to calculate minimal value of COUT3:

#### Calculation

$$C_{out3} = \frac{V_{out+}}{V_{out-}} \times 1.1 \times C_{out2}$$

#### Example +15/-3 Outputs

$$c_{out2} = \frac{55nC}{15V * \frac{1\%}{100}} = 0.366 \mu F$$

selected COUT2 = 4.7 $\mu$ F

$$c_{out3} = \frac{V_{OUT+}}{V_{OUT-}} \times 1.1 \times COUT2$$

| Pa                | Value            |       |

|-------------------|------------------|-------|

| Q                 | gate charge      | 55nC  |

| V <sub>PP</sub>   | accepted Ripple  | 1%    |

| V <sub>OUT+</sub> | output voltage + | 15VDC |

| V <sub>OUT-</sub> | output voltage - | 3VDC  |

| $c_{out3} = \frac{15VDC}{3VDC} \times 1.1 \times 4.7 \mu F = 25.85 \mu F$ | user selected COUT3 = 3x10μF |

|---------------------------------------------------------------------------|------------------------------|

| $L_{OUT3} = \frac{3VDC}{3VDC} \times 1.1 \times 4.7 \mu F = 25.85 \mu F$  | user selected cours = sxrupr |

| CIN          | min. COUT1 (VOUT+ to VOUT-) | VOUT+ to COM | VOUT- to COM | recommended<br>COUT2 | recommended<br>COUT3 |

|--------------|-----------------------------|--------------|--------------|----------------------|----------------------|

| 10μF + 100nF | 2.2µF + 100nF               | 15VDC        | 3VDC         | 4.7μF                | 3x10μF               |

| 10μF + 100nF | 2.2µF + 100nF               | 7VDC         | 3VDC         | 4.7μF                | 15µF                 |

Note11:  $(V_{OUT+}N_{OUT-})^*1.1$  defines the minimal COUT3 to COUT2 ratio. Consider all capacitace connected to VOUT+ to COM in the system as COUT2 and then calculate the minimal COUT3. If COUT3 in the system is lower than the calculated minimum, the device may not start.

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### **CAPACITOR SELECTION**

#### Typical gate drive application

In order to reduce the number of capacitors needed for COUT2 and COUT3, an additional capacitor COUT1\_LOAD can be added at the load (driver circuit in the figure above) between VOUT+ and VOUT- rails.

| COUT1_LOAD value<br>[uF] | COUT2 value<br>[%] | COUT3 value<br>[%] |

|--------------------------|--------------------|--------------------|

| Not used                 | 100%               | 100%               |

| 4.7uF                    | 60%                | 60%                |

| 10uF                     | 40%                | 40%                |

| 22uF                     | 30%                | 30%                |

For +15V/-3V configuration without using COUT1\_LOAD capacitor the recommended values of COUT2 = 4.7uF and COUT3 =  $3 \times 10uF$ . By using 10uF as COUT1\_LOAD, the value of COUT2 can be reduced to 40% of its original value. COUT2 can be then reduced from 4.7uF to 2.2uF. The minimal ratio of COUT3 to COUT3 has to fulfilled, so the same equation as before applies to COUT3 calculation.

$$c_{out3} = \frac{V_{out+}}{V_{out-}} \times 1.1 \times COUT2$$

$$C_{OUT3} = \frac{15VDC}{3VDC} \times 1.1 \times 2.2 \mu F = 12.1 \mu F$$

The closest higher value is 15uF. The number of COUT3 capacitors have been reduced from 3 pieces to 1 piece. In total the design contains 1 capacitor less.

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### **DEFINING RLIM**

When the device has been configured to dual positive or dual negative configuration, set up the RLIM resistor as the maximum load current ( $I_{OUT\_max}$ ) needed for  $V_{OUT\_}$  to COM path using following equation:

#### Calculation

$$\mathbf{R}_{\mathit{LIM}} = \frac{V_{\mathit{OUT-}}}{I_{\mathit{OUT-}} - \mathit{max}} - R_{\mathit{LIM\_internal}}$$

\*  $R_{LIM\_internal} = 30\Omega$

\*  $I_{OUT-max}$  = depends on application

Example  $R_{LIM}$  for  $V_{OUT}$  = 5VDC

$$R_{LIM} = \frac{5V}{12mA} - 30\Omega = 383\Omega$$

\*  $I_{OUT-max}$  has been defined as 12mA for the target application

When the device has been configured to dual output configuration with one positive and one negative output, set up the RLIM resistor using following equation:

#### Calculation

$$R_{LIM} = \frac{V_{OUT-}}{38 \times V_{OUT-} \times COUT3 + 0.005} - R_{LIM\_internal}$$

#### Example RLIM for $V_{\text{OUT-}} = 5V$ and COUT3 = 40uF

$$R_{LIM} = \frac{5V}{38 \times 5V \times 0.00004F + 0.005} - 30\Omega = 367\Omega$$

\* selected RLIM 10% lower=332 Ohm

Note12: The equation assumes 15% tolerance of the COUT3 capacitor and certain response time to transient conditions and load for the driver circuit. Higher value of the limiting resistor can be used in case the power losses have to be minimized. Contact RECOM for further assistance to calculate the right RLIM value for your application.

| CONTROL FUNCTION          |                          |        |       |        |

|---------------------------|--------------------------|--------|-------|--------|

| Parameter                 | Condition                | Min.   | Тур.  | Max.   |

| Control Pin Voltage       | CTRL pin to PGND         | OVDC   |       | 5.5VDC |

| ON/OFF CTRL               | rising                   |        |       | 2.1VDC |

| ONVOFF GIRL               | falling                  | 0.8VDC |       |        |

| Input Current             | no load                  |        |       | 40mA   |

| input current             | full load                |        | 270mA |        |

| Input Current of CTRL Pin | V <sub>CTRL</sub> = 5.0V |        | 5μΑ   | 18µA   |

| POWER GOOD OPERATING CONDITIONS  |                                                                                                     |                        |        |                         |

|----------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|--------|-------------------------|

| Parameter                        | Condition                                                                                           | Min.                   | Тур.   | Max.                    |

| PowerGood threshold              | PG of negated                                                                                       | 90% of V <sub>FB</sub> |        | 110% of V <sub>FB</sub> |

| PowerGood pin voltage            | PG pin to PGND                                                                                      | OVDC                   |        | 5.5VDC                  |

| Primary side soft start time out | Timer begins when V <sub>IN</sub> > UVLO and CTRL= High and reset when Powergood pin indicates Good |                        | 28.4ms |                         |

| AGND REGULATIONS HYSTERESIS                                  |                                                                 |           |         |           |  |

|--------------------------------------------------------------|-----------------------------------------------------------------|-----------|---------|-----------|--|

| Parameter                                                    | Condition                                                       | Min.      | Тур.    | Max.      |  |

| Feedback regulation reference voltage                        | AGND to V <sub>OUT</sub> -                                      | 2.4675VDC | 2.5VDC  | 2.5325VDC |  |

| COM pin Short Charge comparator rising threshold to exit PWM | rising                                                          |           | 0.73VDC |           |  |

| On-Time during COM pin Short Charge PWM mode                 | COM pin $<$ 0.645VDC, while FBV $_{\text{out}}$ pin $<$ 2.48VDC |           | 1.2µs   |           |  |

| Off-Time during COM pin Short Charge PWM mode                | COM pin $<$ 0.645VDC, while FBV $_{\text{out}}$ pin $<$ 2.48VDC |           | 5µs     |           |  |

| OUTPUT UNDER VOLTAGE LOCKOUT                                    |                                |      |        |      |

|-----------------------------------------------------------------|--------------------------------|------|--------|------|

| Parameter                                                       | Condition                      | Min. | Тур.   | Max. |

| UVLO rising threshold (V <sub>OUT+</sub> to V <sub>OUT-</sub> ) | Voltage at FBV <sub>OUT+</sub> |      | 0.9VDC |      |

| UVLO hysteresis (V <sub>OUT+</sub> to V <sub>OUT-</sub> )       | Voltage at FBV <sub>ouт+</sub> |      | 0.3VDC |      |

| OUTPUT OVER VOLTAGE LOCKOUT |                                                               |          |       |          |

|-----------------------------|---------------------------------------------------------------|----------|-------|----------|

| Parameter                   | Condition                                                     | Min.     | Тур.  | Max.     |

| OVLO rising threshold       | Voltage from VouT+ to VouT-, rising                           | 29.45VDC | 31VDC | 32.55VDC |

| OVLO falling threshold      | Voltage from V <sub>OUT+</sub> to V <sub>OUT-</sub> , falling | 27.55VDC | 29VDC | 30.45VDC |

| COMMON MODE TRANSIENT IMMUNITY (CMTI) |           |      |      |          |

|---------------------------------------|-----------|------|------|----------|

| Parameter                             | Condition | Min. | Тур. | Max.     |

| Common Mode Transient Immunity        |           |      |      | ±150V/ns |

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

| PROTECTIONS                                       |                                                     |      |            |           |

|---------------------------------------------------|-----------------------------------------------------|------|------------|-----------|

| Parameter                                         | Condition                                           | Min. | Тур.       | Max.      |

| Over Power Protection (OPP)                       |                                                     |      |            | latch-off |

| Over Temperature Protection <sup>(13)</sup> (OTP) |                                                     |      |            | latch-off |

| Over Temperature Shutdown Setpoint                |                                                     |      | 160°C±10°C |           |

| Over Temperature Shutdown Hysteresis              | cool down after latch-off before restart is enabled |      | 30°C±5°C   |           |

Note13: The R12C2T12/R integrates power stages with over-temperature protection. If temperatures exceed limits, it stops switching and enters a latch-off protection mode.

| Parameter                | Condition                                                       | Min. | Тур.       | Max.         |

|--------------------------|-----------------------------------------------------------------|------|------------|--------------|

|                          | junction to case                                                |      | 28.5K/W    |              |

| Thermal Impedance        | junction to board                                               |      | 25.9K/W    |              |

|                          | junction to ambient, refer to "Note8"                           |      | 52.3K/W    |              |

| TCD.                     | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001              |      |            | ±2k\         |

| ESD                      | Charged-device model (CDM), per JEDEC specification JESD22-C101 | 1    |            | ±500\        |

| Moisture Sensitive Level |                                                                 |      | Level 3, 2 | 260°C, 168hr |

| Parameter                                 |                 | Condition                                               | Min.   | Тур. | Max.         |

|-------------------------------------------|-----------------|---------------------------------------------------------|--------|------|--------------|

| Comparative tracking index (CTI)          | DIN             | EN 60112 (VDE 0303-11); IEC 60112                       |        | 600V |              |

|                                           |                 | Rated mains voltage ≤ 300 VRMS                          |        |      | I-IV         |

| Overvoltage Category                      |                 | Rated mains voltage ≤ 600 VRMS                          |        |      | I-IV         |

|                                           | F               | Rated mains voltage ≤ 1000 VRMS                         |        |      | I-III        |

| Isolation Voltage <sup>(14)</sup>         |                 | tested in qualification                                 |        |      | 5kVAC/1min.  |

| isolation voitage                         |                 | tested in production                                    |        |      | 6kVAC/1sec.  |

| Repetitive peak isolation voltage         |                 | AC voltage (bipolar)                                    |        |      | 1.4kVp       |

| · · · · · · · · · · · · · · · · · · ·     |                 | age (sine wave) Time dependent dielectric               |        |      | 1000VRMS     |

| Working isolation voltage <sup>(15)</sup> |                 | breakdown (TDDB) test                                   |        |      | 1000111110   |

|                                           |                 | DC voltage                                              |        |      | 1.4kVDC      |

| Transient isolation voltage               |                 | tested in qualification                                 |        |      | 7kVp/1min.   |

| Transient isolation voltage               |                 | tested in production                                    |        |      | 8.4kVp/1sec. |

| Impulse voltage                           |                 | waveform per IEC 62368-1                                |        |      | 7.6kVp       |

| Surge isolation voltage                   |                 | waveform per IEC 62368-1                                |        |      | 10kVp        |

|                                           |                 | VIO= 500VDC, TA= 25°C                                   | 1000GΩ |      |              |

| Isolation Resistance                      | input to output | $VIO = 500VDC$ , $100^{\circ}C \le TA \le 125^{\circ}C$ | 100GΩ  |      |              |

|                                           |                 | VIO= 500VDC at TS= 150°C                                | 1GΩ    |      |              |

| Isolation Capacitance                     |                 | input to output                                         |        |      | 3.5pF        |

| Internal Clearance                        |                 | transformer power isolation                             | 120µm  |      |              |

| internal clearance                        |                 | capacitive signal isolation                             | 15.4µm |      |              |

| External Clearance                        |                 |                                                         | 8mm    |      |              |

| External Creepage                         |                 |                                                         | 8mm    |      |              |

Note14: High voltage isolation testing of a barrier component can degrade isolation capability. RECOM therefore strongly

advises against repeated high-voltage isolation testing. If required, reduce specified retest voltage by 20%.

Note15: When the insulation in the R12C2T12/R series is not used as a safety barrier, i.e. provides functional isolation only, continuous or switched voltages across the barrier up to 1.4kVp are sustainable. This is established by measuring the partial discharge inception voltage in accordance with IEC60270. Please contact techsupport@recom-power.com for further information.

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

### APPLICATION INFORMATION

#### Dual Output (one positive, one negative)

#### Single Output (positive)

#### Single Output (negative)

Note16: Use RLIM only for very low load cases (<15mA) and when very high switching frequency is used (>250kHz) the RLIM value should be at least 1k $\Omega$ .

#### **Dual Output (both positive)**

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

### APPLICATION INFORMATION

#### **Dual Output (both negative)**

### **APPLICATION EXAMPLES**

#### Dual Output (one positive, one negative)

$V_{OUT+} = 15VDC$ ,  $V_{OUT-} = 3VDC$ ,  $V_{TOTAL} = 18VDC$

#### Dual Output (one positive, one negative) - RDR configuration

$V_{OUT+} = 15VDC$ ,  $V_{OUT-} = 3VDC$ ,  $V_{TOTAL} = 18VDC$

Note17: Using a Schottky diode and a resistor in paralel with a resistor allows programming the charge and discharge current independently. This RDR configuration greatly reduces power losses of the device.

#### **Dual Output (one positive, one negative)**

$V_{\text{OUT+}} = 7 \text{VDC}, V_{\text{OUT-}} = 3 \text{VDC}, V_{\text{TOTAL}} = 10 \text{VDC}$

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

### **APPLICATION EXAMPLES**

#### Single Output (positive)

$V_{OUT} = 12VDC$

| DIMENSION & PHYSICAL CHARACTERISTICS |      |                         |  |

|--------------------------------------|------|-------------------------|--|

| Parameter                            | Туре | Value                   |  |

| Dimension (LxWxH)                    |      | 12.83 x 7.5 x 3.55mm    |  |

| Differsion (Exwxn)                   |      | 0.51 x 0.30 x 0.14 inch |  |

| Weight                               |      | 0.1g typ.               |  |

| Weight                               |      | 0.0032 oz               |  |

#### **Dimension Drawing (mm)**

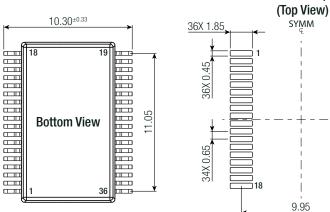

### Recommended Footprint Details

R0.05 TYP.

SYMM

19

Tolerances:  $x.x = \pm 0.1 mm$  $x.xx = \pm 0.05 mm$

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### **DIMENSION & PHYSICAL CHARACTERISTICS**

#### Pad Information

| Pad #              | Function            | Description                                                                                                                                                                            |

|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 5, 8, 9, 10, |                     |                                                                                                                                                                                        |

| 11, 12, 13, 14,    | PGND                | Primary side power ground. Place several vias to copper pours for thermal relief.                                                                                                      |

| 15, 16, 17, 18     |                     |                                                                                                                                                                                        |

| 3                  | PG                  | Power good open-drain output. Low when UVLO, OVLO, UVP, OVP, and OTP are not triggered.                                                                                                |

| 4                  | CTRL                | Pull high to enable the device. Connect to ground to disable the device.                                                                                                               |

| 6                  | $AV_{IN}$           | Primary side analog input. Connect a 330pF ceramic capacitor between AV <sub>N</sub> and pin 5. Connect pin6 to pin7.                                                                  |

| 7                  | PV <sub>IN</sub>    | Primary side power input. Connect a 0.1μF and a 22μF ceramic capacitor to pin 8.                                                                                                       |

| 19, 20, 21, 22,    |                     |                                                                                                                                                                                        |

| 23, 24, 25, 26,    | $V_{\text{OUT-}}$   | Secondary side negative output voltage.                                                                                                                                                |

| 27, 30, 31, 36     |                     |                                                                                                                                                                                        |

| 28, 29             | $V_{\text{OUT+}}$   | Secondary side positive output voltage. Connect a $10\mu F$ and $0.1\mu F$ ceramic capacitor between $V_{0UT+}$ and $V_{0UT-}$ .                                                       |

| 32                 | COM                 | Connect current limiting resistor to COM node of circuit. See application example or "Defining RLIM" section.                                                                          |

| 33                 | FBV <sub>out-</sub> | $FBV_{\text{OUT}} \ Feedback \ (COM-V_{\text{OUT-}}) \ output \ voltage \ sense \ pin \ used \ to \ set \ the \ output \ (COM-V_{\text{OUT-}}) \ voltage.$                             |

| 34                 | FBV <sub>out+</sub> | $FBV_{\text{OUT}} \ Feedback \ (V_{\text{OUT+}} - V_{\text{OUT-}}) \ output \ voltage \ sense \ pin \ used \ to \ set \ the \ output \ (V_{\text{OUT+}} - V_{\text{OUT-}}) \ voltage.$ |

| 35                 | FB <sub>COM</sub>   | Use as reference for FBV <sub>OUT+</sub> and FBV <sub>OUT-</sub> .                                                                                                                     |

#### LAYOUT GUIDELINES

The R12C2T12/R integrated isolated power solution simplifies system design and reduces board area usage. Follow these guidelines for proper PCB layout to achieve optimal performance:

- Place decoupling capacitors as close as possible to the device pins. On the primary side, place the capacitors between pin 7 (power V<sub>IN</sub>) and pins 8−18 (power GND). Optionally, place a capacitor between pin 6 (analog V<sub>IN</sub>) and pins 1, 2, and 5 (analog GNDP). Always put lower values and smaller packages as close to the IC pins as possible.

- For the isolated secondary side, place the capacitors between pin 28, 29 (V<sub>ουτ+</sub>) and pins 19–25, 30–31, 35–36 (V<sub>ουτ-</sub>). Put capacitors between V<sub>ουτ+</sub> and V<sub>ουτ-</sub> close to the IC.

- The capacitors between V<sub>OUT-</sub>/COM and COM/V<sub>OUT-</sub> should be placed near the output device (gate driver input).

- Connection of Feedback circuit to FBCOM (pin 35) should be separated from V<sub>OUT</sub>. plane. Use one short trace to connect this pin to the feedback low-side resistors. Place FB resistors and capacitors close to each other and close to the IC.

- Separate the traces from the COM pin and the FB<sub>Vout</sub>- pin while routing. If possible, use a via near the FB<sub>vout</sub>- pin to route the feedback connection through a different layer.

- Sense connections should be connected to the capacitors at the output device (gate drivers).

- The package of the module dissipates heat through the GNDP and V<sub>OUT</sub>. pins. Ensure sufficient copper around the IC, preferably connected to the ground plane through multiple vias, is present on the GNDP and V<sub>OUT</sub>. pins. A minimum of four layers and using 2oz copper in internal layers are recommended for optimal thermal PCB design.

- We recommend connecting the  $V_{IN}$ , GND,  $V_{OUT+}$ , and  $V_{OUT-}$  pins to internal ground or power planes through multiple vias. Alternatively, make the traces connected to these pins as wide as possible to minimize losses.

- Pay close attention to the spacing between the primary side and the output signals on the outer layers of the PCB. The effective creepage and

clearance of the system are reduced if the gap between the primary and isolated sides is smaller than that of the R12C2T12/R package pins.

Avoid placing any traces under the module.

# 1.5W / 9V-18VDC / 36 Pin SSOP Package

#### **EMC FILTERING SUGGESTIONS ACCORDING TO EN55032**

The successful EMC filtering of the R12C2T12/R requires the selection of suitable components, correct PCB layout, and mechanical shielding of the application where the module is used. Here are some additional notes for the PCB layout:

- Optionally, inner layers can be used to create a high-frequency bypass capacitor between GNDP and VOUT- to mitigate radiated emissions.

Overlapping these layers can be beneficial for reducing radiated emissions. However, this solution might not be suitable for applications requiring fast dV/dt switching. Suitable core thickness and material can help set the correct minimum allowed capacitance between primary and secondary side.

- If the isolation requirements permit, place the internal ground power plane (GNDP) under the module package area. This can serve as partial shielding for the device, helping to reduce radiated emissions.

- If the primary side and isolated secondary output ground planes cannot overlap (as per previous notes), mechanical shielding may be necessary to

meet EN55032 Class B requirements. We recommend connecting the metal shielded box to the primary GND.

| Parameter                     | Ту                       | pe                    | Value                                               |

|-------------------------------|--------------------------|-----------------------|-----------------------------------------------------|

| Dealersing Dimension (LyMAII) | Suffix -R: tape and reel | reel diameter + width | 330.2mm + 24.4mm height<br>13inch + 0.96inch height |

| Packaging Dimension (LxWxH)   | Suffix -CT: mois         | ture barrier bag      | 100 x 150 x 30 mm<br>3.94 x 5.90 x 1.18 inch        |

| Dealessing Overtity           | Suffix -R: ta            | ape and reel          | 750pcs                                              |

| Packaging Quantity            | Suffix -CT: mois         | ture barrier bag      | 10pcs                                               |

| Storage Temperature Range     |                          |                       | -40°C to +125°C                                     |

| Storage Humidity              | non-con                  | ndensing              | 5% - 95% RH max.                                    |

The product information and specifications may be subject to changes even without prior written notice. The product has been designed for various applications; its suitability lies in the responsibility of each customer. The products are not authorized for use in safety-critical applications without RECOM's explicit written consent. A safety-critical application is an application where a failure may reasonably be expected to endanger or cause loss of life, inflict bodily harm or damage property. The applicant shall indemnify and hold harmless RECOM, its affiliated companies and its representatives against any damage claims in connection with the unauthorized use of RECOM products in such safety-critical applications.