# MCP6571/1R/1U/2/4

# 1.8V, 40 ns Low-Power Push-Pull Output Comparator

#### **Features**

- Propagation Delay at V<sub>DD</sub> = 5.5V:

- 40 ns (typical) high-to-low

- 33 ns (typical) low-to-high

- Low Quiescent Current: 70 µA (maximum per comparator)

- Low Input Offset Voltage: ±7 mV (maximum)

- Supply Voltage Range: 1.8V to 5.5V

- · Rail-to-Rail Input

- · Power-on-Reset

- Small Packages:

- Singles in SC70-5, SOT-23-5

- Dual in SOIC-8, MSOP-8

- Quad in SOIC-14, TSSOP-14

- Extended Temperature Range:-40°C to +125°C

- AEC Q100 Qualified see "Product Identification System (Automotive)"

#### **Applications**

- · Automotive

- · Portable Equipment

- · Medical Diagnostic Equipment

- RC Timers

- · Sensor Conditioning

#### **Design Aids**

- · SPICE Macro Models

- · Analog Demonstration and Evaluation Boards

- · Application Notes

### **Related Devices**

• Open-Drain Output: MCP6576/6R/6U/7/9

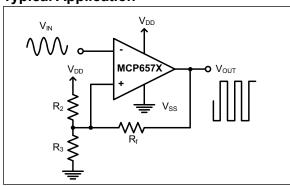

## **Typical Application**

#### **Description**

The Microchip Technology Inc. MCP6571/1R/1U/2/4 family of CMOS/TTL compatible comparators operate with a single-supply voltage, as low as 1.8V, while drawing low-quiescent current (70  $\mu$ A, maximum per comparator). This family of comparators incorporate a Power-on-Reset feature that keeps the output high impedance until the supply voltage V<sub>DD</sub> rises to a sufficient voltage to control the comparator. They also have a low-input offset voltage ( $\pm$ 7 mV, maximum).

These comparators are optimized for low-power, single supply applications with greater than rail-to-rail input operation. Internal input hysteresis eliminates output switching due to internal input noise voltage, reducing current draw. These comparators are provided with push-pull outputs.

This family is offered in single (MCP6571), dual (MCP6572) and quad (MCP6574) packages. All devices are designed using an advanced CMOS process and fully specified in the extended temperature range from -40°C to +125°C.

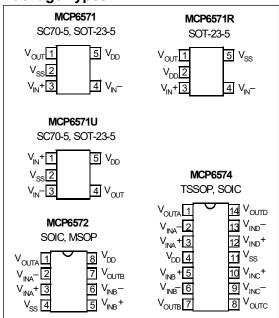

#### **Package Types**

#### 1.0 ELECTRICAL CHARACTERISTICS

## 1.1 Absolute Maximum Ratings<sup>†</sup>

| V <sub>DD</sub> – V <sub>SS</sub>                                  | 6V                                 |

|--------------------------------------------------------------------|------------------------------------|

| Current at Input Pins (V <sub>IN</sub> +, V <sub>IN</sub> -)       | ±2 mA                              |

| Analog Inputs (V <sub>IN</sub> +, V <sub>IN</sub> -) <sup>††</sup> | $V_{SS} - 0.5V$ to $V_{DD} + 0.5V$ |

| All Other Inputs and Outputs                                       | $V_{SS} - 0.3V$ to $V_{DD} + 0.3V$ |

| Difference Input Voltage                                           | V <sub>DD</sub> – V <sub>SS</sub>  |

| Output Short-Circuit Current (Note 1)                              | Continuous                         |

| Storage Temperature                                                | 65°C to +150°C                     |

| Maximum Junction Temperature (T <sub>J</sub> )                     | +1.50°C                            |

| ESD Protection on All Pins (HBM; CDM)                              | ≥ 2 kV; 1.5 kV                     |

Note 1: Short-circuit to ground, one comparator per package

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

†† See Section 4.1.2 "Input Voltage Limits".

## 1.2 Specifications

#### TABLE 1-1: DC ELECTRICAL SPECIFICATIONS

**Electrical Characteristics**: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+} = V_{SS}$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{DD}/2$ ,  $R_L = 10 \text{ k}\Omega$  to  $V_L$  and  $C_L = 15 \text{ pF}$ . **Parameters** Sym. Min. Max. Units **Conditions** Typ. **Power Supply** Supply Voltage  $V_{DD}$ 1.8 5.5 V Power-on-Reset Voltage (1)  $V_{POR}$ ٧ 1.6 Quiescent Current per 35 μΑ  $I_O = 0$ ,  $V_{OUT} = High$  $I_Q$ Comparator  $I_O = 0$ ,  $V_{OLIT} = Low$ 30 45 70 μΑ Power Supply Rejection Ratio **PSRR** 60 80 dB  $V_{CM} = V_{DD}/2$ Input Input Offset Voltage (2) -7 +7  $V_{CM} = V_{DD}/2$ Vos mV Input Offset Drift with  $\Delta V_{OS}/\Delta T_{A}$ μV/°C  $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ ±1 **Temperature** Input Hysteresis Voltage (2)  $V_{CM} = V_{DD}/2$ 1 6 mV  $V_{HYST}$ Input Bias Current and Impedance Input Bias Current ±1 pΑ  $I_B$ 20 pΑ  $T_A = 85$ °C 50 T<sub>A</sub>= 125°C pΑ Input Offset Current  $I_{OS}$ ±1 pΑ 10<sup>13</sup>||4 Common Mode Input Impedance  $\Omega || pF$  $Z_{CM}$ 10<sup>13</sup>||2 Differential Input Impedance **Z**DIFF  $\Omega || pF$

**Note 1:** The output is high impedance until V<sub>DD</sub> exceeds V<sub>POR</sub>.

2: V<sub>OS</sub> is the center of the input-referred trip points. Hysteresis is the difference between the trip points.

mΑ

μs

$V_{DD} = 5.5V$

$V_{DD} = 0V \text{ to } 5.5V$

## TABLE 1-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics**: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+} = V_{SS}$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{DD}/2$ ,  $R_L = 10 \text{ k}\Omega$  to  $V_L$  and  $C_L = 15 \text{ pF}$ . Units Conditions **Parameters** Sym. Max. **Common Mode**  $T_{\Delta}$ = -40°C to +125°C, Common Mode Input Voltage  $V_{CMR}$  $V_{SS} - 0.2$  $V_{DD} + 0.2$ ٧ Range Guaranteed by Characterization.  $V_{DD} = 5.5V$ Common Mode Rejection Ratio **CMRR** 54 75 dB  $V_{CM} = V_{CML}$  to  $V_{CMH}$ **Push-Pull Output**  $V_{OL}, V_{OH} | V_{SS} + 0.2$ ٧ Output Voltage Swing  $V_{DD} - 0.2$  $V_{DD}$  = 5.5V,  $I_{OUT}$  = 4 mA  $V_{SS} + 0.3$  $V_{DD} - 0.42$  $V_{DD} = 1.8V, I_{OUT} = 4 \text{ mA}$ **Output Short-Circuit Current**  $I_{SC}$ ±10 mΑ  $V_{DD} = 1.8V$

t<sub>start</sub>

±80

11

#### TABLE 1-2: AC ELECTRICAL SPECIFICATIONS

Startup Time

**Electrical Characteristics**: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+} = V_{SS}$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{DD}/2$ ,  $R_L = 10 \text{ k}\Omega$  to  $V_L$  and  $C_L = 15 \text{ pF}$ . **Parameters** Sym. Min. Max. Units **Conditions** Typ. **Propagation Delay** High-to-Low, 100mV Overdrive 40  $V_{DD} = 5.5V, V_{CM} = V_{DD}/2$  $t_{PHI}$ ns Low-to-High, 100mV Overdrive 33 ns  $V_{DD} = 5.5V, V_{CM} = V_{DD}/2$  $t_{PLH}$ Propagation Delay Skew (1) ±5  $V_{DD} = 5.5V, V_{CM} = V_{DD}/2$ ns t<sub>PDS</sub> Rise Time  $V_{DD} = 5.5V, V_{CM} = V_{DD}/2$  $t_R$ 5 ns **Fall Time**  $V_{DD} = 5.5V, V_{CM} = V_{DD}/2$ 5 ns  $t_F$ Maximum Toggle Frequency 8 MHz  $V_{DD} = 5.5V$  $f_{TG}$ 7 MHz  $V_{DD} = 1.8V$ **Noise** Input Noise Voltage 400  $\mu V_{P-P}$ f = 10 Hz to 100 kHz  $E_{ni}$

**Note 1:** Propagation delay skew is defined as:  $t_{PDS} = t_{PLH} - t_{PHL}$ .

**Note 1:** The output is high impedance until  $V_{DD}$  exceeds  $V_{POR}$ .

<sup>2:</sup> V<sub>OS</sub> is the center of the input-referred trip points. Hysteresis is the difference between the trip points.

TABLE 1-3: TEMPERATURE SPECIFICATIONS

| <b>Electrical Characteristics:</b> Unless otherwise indicated, $V_{DD} = +1.8V$ to +5.5V and $V_{SS} = GND$ . |                |      |      |      |       |            |

|---------------------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|------------|

| Parameters                                                                                                    | Sym.           | Min. | Тур. | Max. | Units | Conditions |

| Temperature Ranges                                                                                            |                |      |      |      |       |            |

| Operating Temperature Range                                                                                   | T <sub>A</sub> | -40  | _    | +125 | °C    | Note 1     |

| Storage Temperature Range                                                                                     | T <sub>A</sub> | -65  | _    | +150 | °C    |            |

| Thermal Package Resistances                                                                                   |                |      |      |      |       |            |

| Thermal Resistance, 5L-SC70                                                                                   | $\theta_{JA}$  | _    | 331  | _    | °C/W  |            |

| Thermal Resistance, 5L-SOT-23                                                                                 | $\theta_{JA}$  | _    | 221  | _    | °C/W  |            |

| Thermal Resistance, 8L-MSOP                                                                                   | $\theta_{JA}$  | _    | 206  | _    | °C/W  |            |

| Thermal Resistance, 8L-SOIC                                                                                   | $\theta_{JA}$  | _    | 150  | _    | °C/W  |            |

| Thermal Resistance, 14L-TSSOP                                                                                 | $\theta_{JA}$  | _    | 100  | _    | °C/W  |            |

| Thermal Resistance, 14L-SOIC                                                                                  | $\theta_{JA}$  | _    | 120  | _    | °C/W  |            |

Note 1: The internal junction temperature (T<sub>.I</sub>) must not exceed the absolute maximum specification of +150°C.

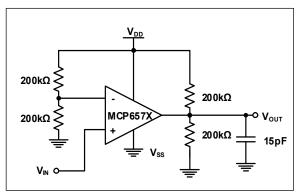

## 1.3 Test Circuit Configuration

This test circuit configuration is used to determine the AC and DC specifications.

**FIGURE 1-1:** AC and DC Test Circuit for the Push-Pull Output Comparators.

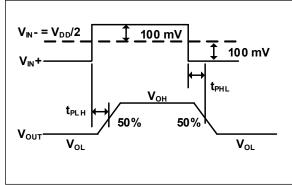

#### 1.4 Propagation Measurement

The following diagram is used to determine the propagation delay measurements.

FIGURE 1-2: Propagation Delay Timing Diagram

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+}$  =  $V_{SS}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $V_L$  =  $V_{DD}/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_L$  and  $C_L$  = 15 pF.

## 2.1 DC Inputs

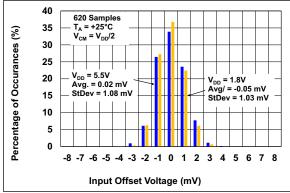

**FIGURE 2-1:** Input Offset Voltage Histogram.

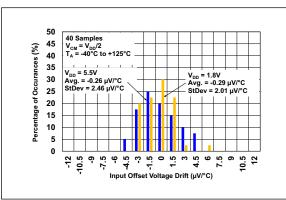

**FIGURE 2-2:** Input Offset Voltage Drift Histogram.

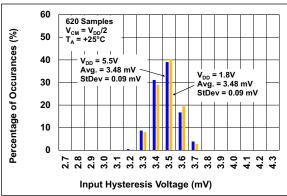

FIGURE 2-3: Input Hysteresis Voltage Histogram.

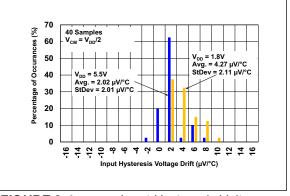

**FIGURE 2-4:** Input Hysteresis Voltage Drift Histogram.

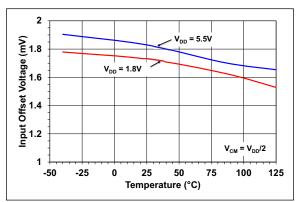

**FIGURE 2-5:** Input Offset Voltage vs. Temperature.

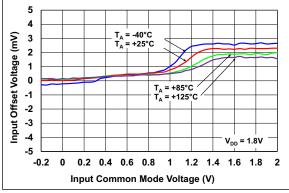

**FIGURE 2-6:** Input Offset Voltage vs. Common Mode Input Voltage  $(V_{DD} = 1.8V)$ .

# MCP6571/1R/1U/2/4

Note: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+}$  =  $V_{SS}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $V_L$  =  $V_{DD}/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_L$  and  $C_L$  = 15 pF.

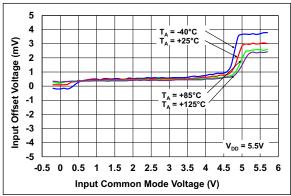

**FIGURE 2-7:** Input Offset Voltage vs. Common-Mode Input Voltage  $(V_{DD} = 5.5V)$ .

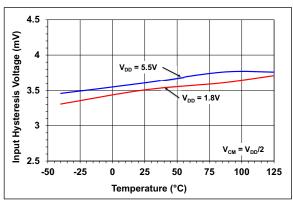

**FIGURE 2-8:** Input Hysteresis Voltage vs. Ambient Temperature.

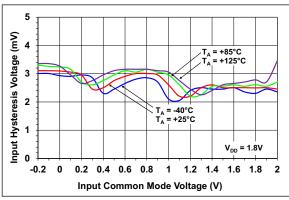

**FIGURE 2-9:** Input Hysteresis Voltage vs. Common Mode Input Voltage  $(V_{DD} = 1.8V)$ .

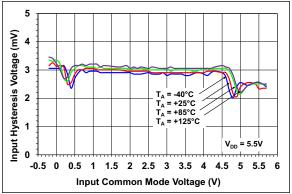

**FIGURE 2-10:** Input Hysteresis Voltage vs. Common Mode Input Voltage  $(V_{DD} = 5.5V)$ .

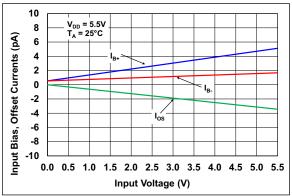

**FIGURE 2-11:** Input Bias, Offset Current vs. Input Voltage.

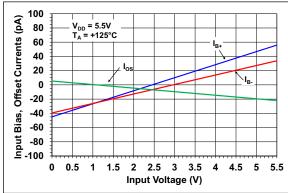

FIGURE 2-12: Input Bias, Offset Current vs. Input Voltage (High Temp).

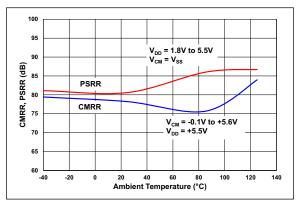

FIGURE 2-13: CMRR, PSRR vs. Temperature.

Note: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+}$  =  $V_{SS}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $V_L$  =  $V_{DD}/2$ ,  $V_L$  = 10 k $\Omega$  to  $V_L$  and  $C_L$  = 15 pF.

## 2.2 Other DC Voltages and Currents

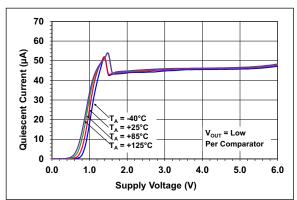

**FIGURE 2-14:** Quiescent Current vs. Power Supply Voltage (Output Low).

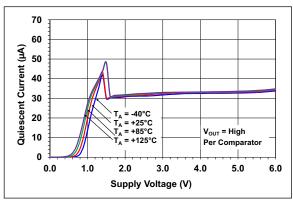

**FIGURE 2-15:** Quiescent Current vs. Power Supply Voltage (Output High).

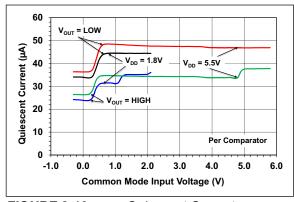

**FIGURE 2-16:** Quiescent Current vs. Common Mode Input Voltage.

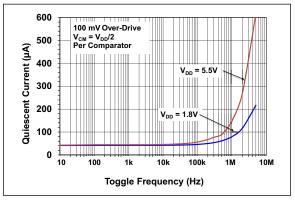

**FIGURE 2-17:** Quiescent Current vs. Toggle Frequency.

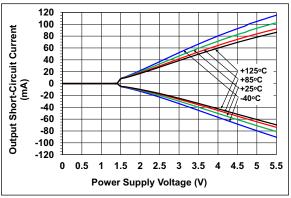

**FIGURE 2-18:** Output Short-Circuit Current vs. Power Supply Voltage.

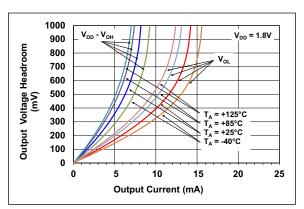

**FIGURE 2-19:** Output Voltage Headroom vs. Output Current ( $V_{DD} = 1.8V$ ).

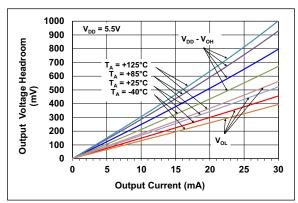

**FIGURE 2-20:** Output Voltage Headroom vs. Output Current ( $V_{DD} = 5.5V$ ).

Note: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+}$  =  $V_{SS}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $V_L$  =  $V_{DD}/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_L$  and  $C_L$  = 15 pF.

## 2.3 Time Response

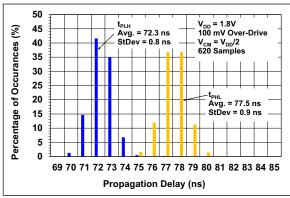

**FIGURE 2-21:** High-to-Low and Low-to-High Propagation Delay Histogram  $(V_{DD} = 1.8V)$ .

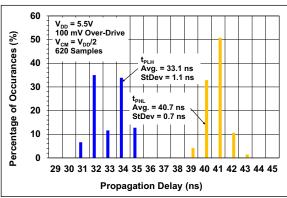

**FIGURE 2-22:** High-to-Low and Low-to-High Propagation Delay Histogram  $(V_{DD} = 5.5V)$ .

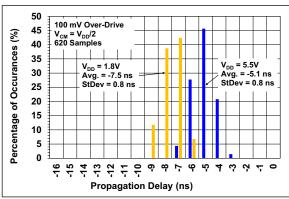

FIGURE 2-23: Propagation Delay Skew Histogram.

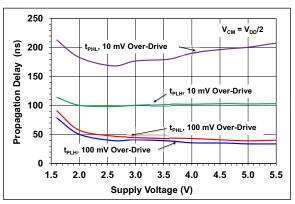

**FIGURE 2-24:** Propagation Delay vs. Power Supply Voltage.

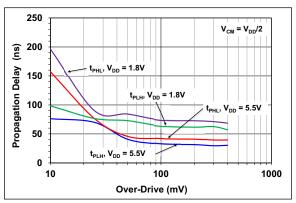

**FIGURE 2-25:** Propagation Delay vs. Input Overdrive.

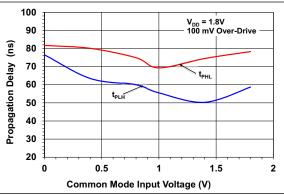

**FIGURE 2-26:** Propagation Delay vs. Common Mode Input Voltage ( $V_{DD} = 1.8V$ ).

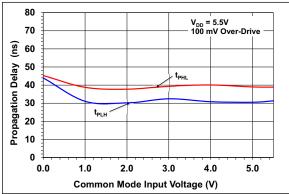

Note: Unless otherwise indicated,  $T_A$ = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$ = GND,  $V_{IN-}$  =  $V_{DD}/2$ ,  $V_{IN+}$  =  $V_{SS}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $V_L$  =  $V_{DD}/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_L$  and  $C_L$  = 15 pF.

**FIGURE 2-27:** Propagation Delay vs. Common Mode Input Voltage ( $V_{DD} = 5.5V$ ).

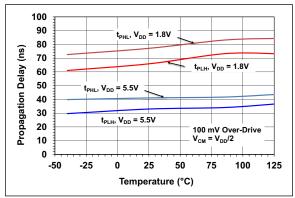

**FIGURE 2-28:** Propagation Delay vs. Temperature.

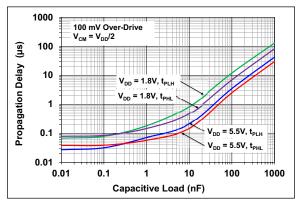

**FIGURE 2-29:** Propagation Delay vs. Load Capacitance.

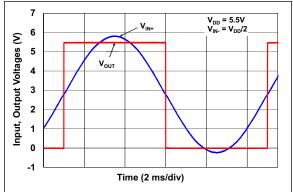

FIGURE 2-30: Input and Output Signal, No Phase Reversal.

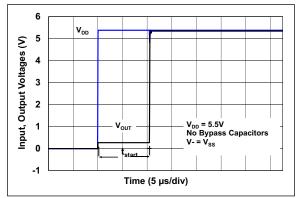

FIGURE 2-31: Startup Time.

# MCP6571/1R/1U/2/4

## 3.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 3-1, Table 3-2, and Table 3-3.

TABLE 3-1: PIN FUNCTION TABLE - SINGLES

| MCP6571             | MCP6571R      | MCP6571U                            | Symbol            | Description           |

|---------------------|---------------|-------------------------------------|-------------------|-----------------------|

| 5-Lead SC70, SOT-23 | 5-Lead SOT-23 | 5-Lead SC70, SOT-23                 | Symbol            | Description           |

| 1                   | 1             | 4                                   | V <sub>OUT</sub>  | Digital Output        |

| 2                   | 5             | 2                                   | V <sub>SS</sub>   | Negative Power Supply |

| 3                   | 3             | 1                                   | V <sub>IN</sub> + | Noninverting Input    |

| 4                   | 4             | 3 V <sub>IN</sub> - Inverting Input |                   | Inverting Input       |

| 5                   | 2             | 1 11                                |                   | Positive Power Supply |

TABLE 3-2: PIN FUNCTION TABLE - DUALS

| MCP6572           | Cumbal             | Description                      |

|-------------------|--------------------|----------------------------------|

| 8-Lead MSOP, SOIC | Symbol             | Description                      |

| 1                 | V <sub>OUTA</sub>  | Digital Output; Comparator A     |

| 2                 | V <sub>INA</sub> - | Inverting Input; Comparator A    |

| 3                 | V <sub>INA</sub> + | Noninverting Input; Comparator A |

| 4                 | $V_{SS}$           | Negative Power Supply            |

| 5                 | V <sub>INB</sub> + | Noninverting Input; Comparator B |

| 6                 | V <sub>INB</sub> - | Inverting Input; Comparator B    |

| 7                 | V <sub>OUTB</sub>  | Digital Output; Comparator B     |

| 8                 | $V_{DD}$           | Positive Power Supply            |

TABLE 3-3: PIN FUNCTION TABLE - QUADS

| MCP6574             | Cumbal             | Description                      |

|---------------------|--------------------|----------------------------------|

| 14-Lead TSSOP, SOIC | Symbol             | Description                      |

| 1                   | V <sub>OUTA</sub>  | Digital Output; Comparator A     |

| 2                   | V <sub>INA</sub> - | Inverting Input; Comparator A    |

| 3                   | V <sub>INA</sub> + | Noninverting Input; Comparator A |

| 4                   | $V_{DD}$           | Positive Power Supply            |

| 5                   | V <sub>INB</sub> + | Noninverting Input; Comparator B |

| 6                   | V <sub>INB</sub> - | Inverting Input; Comparator B    |

| 7                   | $V_{OUTB}$         | Digital Output; Comparator B     |

| 8                   | V <sub>OUTC</sub>  | Digital Output; Comparator C     |

| 9                   | V <sub>INC</sub> - | Inverting Input; Comparator C    |

| 10                  | V <sub>INC</sub> + | Noninverting Input; Comparator C |

| 11                  | V <sub>SS</sub>    | Negative Power Supply            |

| 12                  | V <sub>IND</sub> + | Noninverting Input; Comparator D |

| 13                  | V <sub>IND</sub> - | Inverting Input; Comparator D    |

| 14                  | V <sub>OUTD</sub>  | Digital Output; Comparator D     |

#### 3.1 Digital Outputs

The comparator outputs ( $V_{OUTx}$ ) are CMOS push-pull, digital outputs. They are designed to be compatible with CMOS and TTL logic, and are capable of driving heavy DC or capacitive loads.

### 3.2 Analog Inputs

The comparator noninverting and inverting inputs  $(V_{INx}^+, V_{INx}^-)$  are high-impedance CMOS inputs with low bias currents.

## 3.3 Power Supply Pins $(V_{SS}, V_{DD})$

The positive power supply ( $V_{DD}$ ) is 1.8V to 5.5V higher than the negative power supply ( $V_{SS}$ ). For normal operation, the other pins are at voltages between  $V_{SS}$  and  $V_{DD}$ .

Typically, these parts are used in a single (positive) supply configuration. In this case,  $V_{SS}$  is connected to ground and  $V_{DD}$  is connected to the supply.  $V_{DD}$  will need a local bypass capacitor (typically 0.01  $\mu$ F to 0.1  $\mu$ F) within 2 mm of the  $V_{DD}$  pin. These pins can share a bulk capacitor with nearby analog parts (within 100 mm), but it is not required.

#### 4.0 APPLICATION INFORMATION

The MCP6571/1R/1U/2/4 is a family of push-pull output comparators. They are suitable for a wide range of high-speed applications requiring low power consumption.

#### 4.1 Comparator Inputs

#### 4.1.1 NORMAL OPERATION

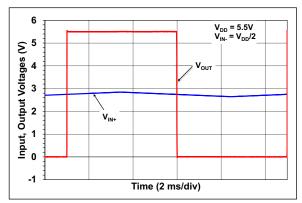

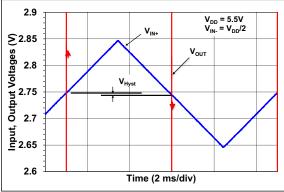

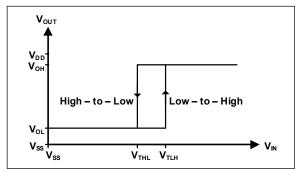

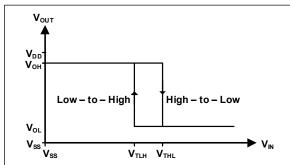

The MCP6571/1R/1U/2/4 devices have internally set hysteresis, VHYST, that is small enough to maintain input offset accuracy across the entire input common mode range and large enough to eliminate output chattering caused by the comparator's own input noise voltage, ENI. Figure 4-1 shows the output voltage with a 100 mV ramping input voltage ( $V_{IN+}$ ) across the reference voltage ( $V_{IN-}$ ), while Figure 4-2 has a smaller voltage scale to better show the different trigger points on the input voltage.

FIGURE 4-1: Input Voltage Hysteresis.

FIGURE 4-2: Input Voltage Hysteresis (Smaller Voltage Scale).

#### 4.1.2 INPUT VOLTAGE LIMITS

In order to prevent damage and/or improper operation of the comparator, the circuit must limit the voltages at the input pins (see Section 1.1, Absolute Maximum Ratings†).

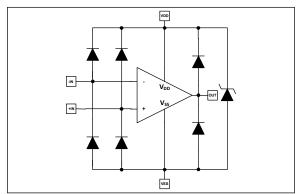

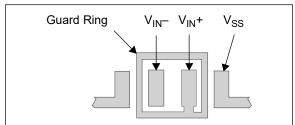

The Electrostatic Discharge (ESD) protection on the inputs can be depicted as shown in Figure 4-3. This structure was chosen to protect the input transistors against many, but not all, overvoltage conditions and to minimize the Input Bias ( $I_B$ ) current.

FIGURE 4-3: Simplified Analog Input ESD Structures.

The input ESD diodes clamp the inputs when they try to go more than one diode drop below  $V_{SS}$ . They also clamp any voltages that go well above  $V_{DD}$ ; their breakdown voltage is high enough to allow normal operation. At 0.5V above  $V_{DD}$  or below  $V_{SS}$ , the input currents are typically less than 5 mA. Very fast ESD events that meet the specifications are limited so that damage does not occur.

#### 4.1.3 INPUT CURRENT LIMITS

In order to prevent damage and/or improper operation of the comparator, the circuit must limit the currents into the input pins (see Section 1.1, Absolute Maximum Ratings†).

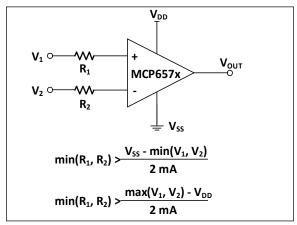

Figure 4-4 shows one approach to protecting these inputs. The resistors  $R_1$  and  $R_2$  limit the possible currents in or out of the input pins through the ESD diodes to either  $V_{DD}$  or  $V_{SS}$ .

FIGURE 4-4: Protecting the Analog Inputs.

#### 4.1.4 PHASE REVERSAL

The MCP6571/1R/1U/2/4 comparator use CMOS transistors at the input. They are designed to prevent phase inversion when the input pins exceed the supply voltages. Figure 2-30 shows an input voltage exceeding both supplies with no resulting phase inversion.

#### 4.1.5 POWER-ON RESET (POR)

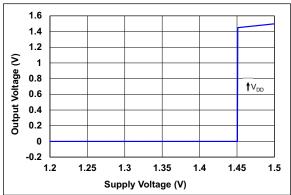

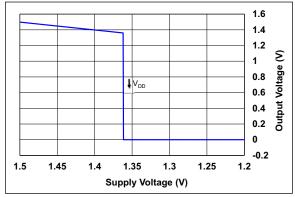

The MCP6571/2/4 comparator family is provided with a Power-on Reset (POR) circuit which sets the output to high impedance until the supply voltage ( $V_{DD}$ ) exceeds the POR threshold. When the supply voltage exceeds the POR threshold, the output will drive to the correct state determined by the input pins. Figure 4-5 shows a typical output voltage waveform with a rising supply voltage ( $V_{DD}$ ). This plot indicates the output is enabled after  $V_{DD}$  exceeds 1.45V. Figure 4-6 shows the output voltage waveform for the same part when the supply voltage is decreasing. This plot indicates that the output is disabled when  $V_{DD}$  falls below 1.36V.

FIGURE 4-5: POR with Rising Supply Voltage (typical).

FIGURE 4-6: POR with Falling Supply Voltage (typical).

#### 4.2 Push-Pull Output

The push-pull output is designed to be compatible with both CMOS and TTL logic, while the output transistors are configured to give rail-to-rail output performance. They are driven with circuitry that minimizes any switching current (shoot-through current from supply to supply) when the output is transitioned from high-to-low or from low-to-high. Refer to Figures 2-19 and 2-20 for more information.

#### 4.3 Externally Set Hysteresis

The MCP6571/1R/1U/2/4 family of comparators are provided with a small internal hysteresis voltage between the rising and falling trigger levels. Larger levels of hysteresis can be achieved by using external resistors.

The input offset voltage ( $V_{OS}$ ) is the center (or average) of the input-referred low to high and high to low trip points. Where as the input hysteresis voltage ( $V_{HYST}$ ) is the difference between the same trip points. Hysteresis reduces output chattering when one input is slowly moving past the other and thus reduces dynamic supply current.

# MCP6571/1R/1U/2/4

#### 4.3.1 NONINVERTING CIRCUIT

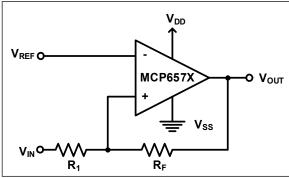

Figure 4-7 shows a noninverting circuit for single supply applications using just two external resistors. The resulting hysteresis diagram is shown in Figure 4-8. The trip points ( $V_{TLH}$  and  $V_{THL}$ ) can be determined by Equation 4-1.

FIGURE 4-7: Noninverting Circuit with Hysteresis.

**FIGURE 4-8:** Hysteresis Diagram for Noninverting circuit.

### **EQUATION 4-1:**

$$V_{TLH} = V_{REF} \left( 1 + \frac{R_1}{R_F} \right) - V_{OL} \left( \frac{R_1}{R_F} \right)$$

$$V_{THL} = V_{REF} \left( 1 + \frac{R_1}{R_F} \right) - V_{OH} \left( \frac{R_1}{R_F} \right)$$

Where:

$$V_{TLH} = Trip \ Voltage \ from \ Low-to-High$$

$$V_{THL} = Trip \ Voltage \ from \ High-to-Low$$

### 4.3.2 INVERTING CIRCUIT

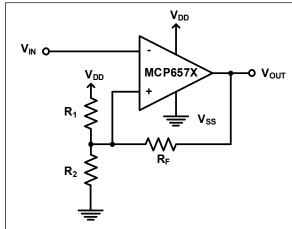

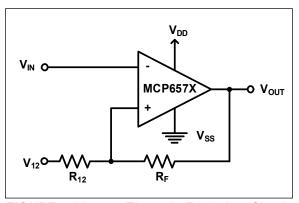

Figure 4-9 shows an inverting circuit for single supply applications using three external resistors. The resulting hysteresis diagram is shown in Figure 4-10. The trip points ( $V_{TLH}$  and  $V_{THL}$ ) can be determined by Equation 4-3.

FIGURE 4-9: Inverting Circuit with Hysteresis.

FIGURE 4-10: Hysteresis Diagram for Inverting circuit.

FIGURE 4-11: Thevenin Equivalent Circuit.

Where  $R_{12}$  and  $V_{12}$  can be calculated as shown in Equation 4-2, and the trip points ( $V_{TLH}$  and  $V_{THL}$ ) can be determined by Equation 4-3.

### **EQUATION 4-2:**

$$R_{12} = \frac{R_1 R_2}{R_1 + R_2}$$

$$V_{12} = \frac{R_2}{R_1 + R_2} \times V_{DD}$$

#### **EQUATION 4-3:**

$$V_{THL} = V_{OH} \left( \frac{R_{12}}{R_{12} + R_F} \right) + V_{12} \left( \frac{R_F}{R_{12} + R_F} \right)$$

$$V_{TLH} = V_{OL} \left( \frac{R_{12}}{R_{12} + R_F} \right) + V_{12} \left( \frac{R_F}{R_{12} + R_F} \right)$$

Where:

$V_{TLH}$  = Trip Voltage from Low-to-High

$V_{THL}$  = Trip Voltage from High-to-Low

## 4.4 Start-up

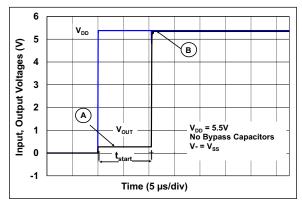

The MCP6571/1R/1U/2/4 family of parts quickly controls the output when power ( $V_{DD}$ ) is initially applied to the device (start-up). Bypass capacitors are removed during the start-up testing to minimize the inrush currents (see Figure 4-12). The start-up time is measured from when  $V_{DD}$  is applied to when the output toggles high.

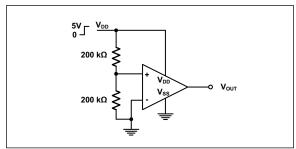

FIGURE 4-12: Start-Up Test Circuit.

Figure 4-13 shows the power supply voltage (blue line) for the MCP6572 and the output voltage (black line). When power is first applied to the MCP6572, the output is turned off (Point A) and is high impedance until VPOR is exceeded. After 11  $\mu$ s (typical), the output is turned on (Point B) and  $V_{OUT}$  toggles high.

FIGURE 4-13: Start-Up Test Waveforms.

#### 4.5 Capacitive Loads

This family of comparators has a push-pull output. When the output switches there can be an increase in output sinking or sourcing current during the transition.

Excessive capacitive loads can increase the supply current and propagation delay or decrease slew rate during the output transitions.

Figure 2-29 shows the increase in propagation delay with an increase in output capacitance. Figure 2-17 shows the increase in quiescent current with the increase in toggle frequency (rate of transitions from low-to-high, high-to-low).

#### 4.6 Supply Bypass

The MCP6571/1R/1U/2/4 family of comparators power supply pin ( $V_{DD}$  for single-supply) should have a local bypass capacitor (i.e., 0.01  $\mu F$  to 0.1  $\mu F$ ) within 2 mm for good edge rate performance.

#### 4.7 PCB Surface Leakage

In applications where low input bias current is critical, the Printed Circuit Board (PCB) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low-humidity conditions, a typical resistance between nearby traces is  $10^{12}\Omega$ . A 5V difference would cause 5 pA of current to flow, which is greater than the MCP6571/1R/1U/2/4's bias current at +25°C (±1 pA, typical).

The easiest way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 4-14.

FIGURE 4-14: Example Guard Ring Layout for Inverting Gain.

- 1. Inverting Configuration (Fig and Figure 4-14)

- a) Connect the guard ring to the noninverting pin (V<sub>IN</sub>+). This biases the guard ring to the same reference voltage as the comparator (e.g. V<sub>DD</sub>/2 or ground).

- b) Connect the inverting input pin (V<sub>IN</sub>-) to the input pad without touching the guard ring.

- 2. Noninverting Configuration (Figure 4-7)

- a) Connect the noninverting input pin (V<sub>IN</sub>+) to the input pad without touching the guard ring.

- b) Connect the guard ring to the inverting pin (V<sub>IN</sub>-).

#### 4.8 Unused Comparators

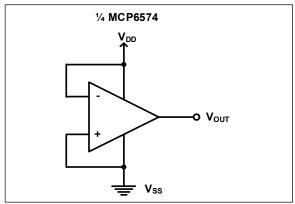

An unused comparator in a dual (MCP6572) or quad (MCP6574) package should be configured as shown in Figure 4-15. These circuits prevent the output from toggling and causing crosstalk. It uses the minimum number of components and draws minimal current.

FIGURE 4-15: Unused Comparators.

#### 4.9 Application Circuits

#### 4.9.1 WINDOW COMPARATOR

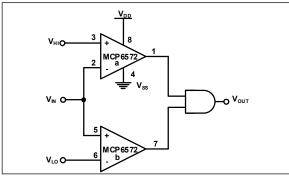

The MCP6571/2/4 comparator can be used to create a windowed comparator. Figure 4-16 shows one approach using the MCP6572 dual comparator with an AND gate. The AND gate output will produce a logic high when the input voltage is between  $V_{LO}$  and  $V_{HI}$  ( $V_{HI}$  >  $V_{LO}$ ).

FIGURE 4-16: Windowed Comparator.

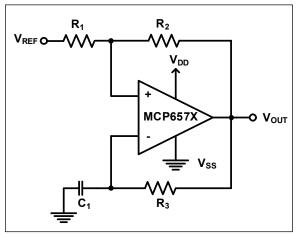

#### 4.9.2 BISTABLE MULTIVIBRATOR

A simple bistable multivibrator design is shown in Figure 4-17.  $V_{REF}$  needs to be between the power supplies ( $V_{SS}$  = GND and  $V_{DD}$ ) to achieve oscillation. The output duty cycle changes with  $V_{RFF}$ .

FIGURE 4-17: Bistable Multivibrator.

#### 5.0 DESIGN AIDS

Microchip Technology Inc. provides the basic design tools needed for the MCP6571/1R/1U/2/4 comparator.

#### 5.1 SPICE Macro Model

The latest SPICE macro model for the comparator MCP6571/1R/1U/2/4 is available on the Microchip website at www.microchip.com. This model is intended to be an initial design tool that works well in the comparator's linear region of operation over the temperature range. See the model file for information on its capabilities.

Bench testing is a very important part of any design and cannot be replaced with simulations. Also, simulation results using this macro model need to be validated by comparing them to the data sheet specifications and characteristic curves.

# 5.2 Analog Demonstration and Evaluation Boards

Microchip offers a broad spectrum of Analog Demonstration and Evaluation Boards that are designed to help you achieve faster time to market. For a complete listing of these boards and their corresponding user's guides and technical information, visit the Microchip website at www.microchip.com/analog tools.

Some boards that are especially useful are:

- MCP6XXX Amplifier Evaluation Board 2 (P/N DS51668)

- MCP6XXX Amplifier Evaluation Board 3 (P/N DS51673)

- 8-Pin SOIC/MSOP/TSSOP/DIP Evaluation Board (P/N SOIC8EV)

- 5/6-Pin SOT-23 Evaluation Board (P/N VSUPEV2)

- 14-Pin SOIC/TSSOP/DIP Evaluation Board (P/N SOIC14EV)

#### 5.3 Application Notes

The following Microchip Analog Design Note and Application Notes are available on the Microchip web site at <a href="https://www.microchip.com/appnotes">www.microchip.com/appnotes</a>, and are recommended as supplemental reference resources.

AN895 – "Oscillator Circuits For RTD Temperature Sensors", DS00895

#### 6.0 PACKAGING INFORMATION

#### 6.1 **Package Marking Information**

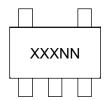

5-Lead SC70 (MCP6571/1U)

| Device                        | Marking |  |  |  |

|-------------------------------|---------|--|--|--|

| MCP6571                       | AELNN   |  |  |  |

| MCP6571U                      | AEMNN   |  |  |  |

| Note: Applies to E Load SC 70 |         |  |  |  |

Example:

**Note:** Applies to 5-Lead SC-70.

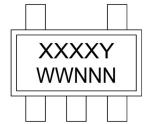

5-Lead SOT-23 (MCP6571/1U/1R)

| Device   | Marking |  |  |  |  |

|----------|---------|--|--|--|--|

| MCP6571  | 571AY   |  |  |  |  |

| MCP6571U | 571UY   |  |  |  |  |

| MCP6571R | 571RY   |  |  |  |  |

|          |         |  |  |  |  |

Note: Applies to 5-Lead SOT-23.

Legend: XX...X Customer-specific information

Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

# **Package Marking Information (Continued)**

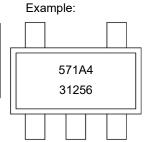

8-Lead MSOP

XXXXX

YWWNNN

O

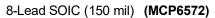

14-Lead SOIC (150 mil) (MCP6574)

14-Lead TSSOP (MCP6574)

Example:

6572

432256

#### Example:

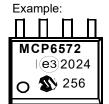

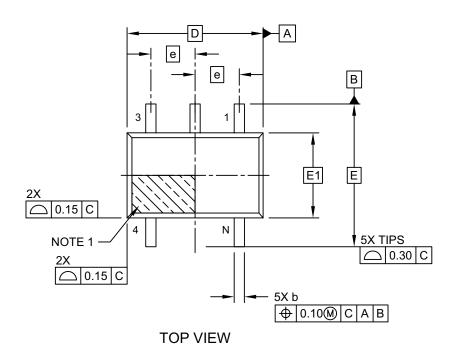

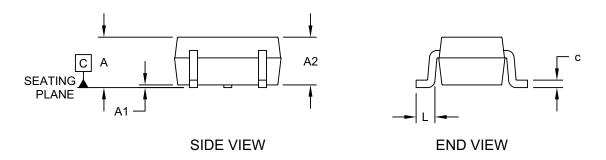

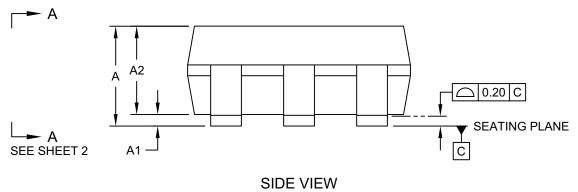

## 5-Lead Plastic Small Outline Transistor (LT) [SC70]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-061-LT Rev E Sheet 1 of 2

## 5-Lead Plastic Small Outline Transistor (LT) [SC70]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | Limits      | MIN      | NOM  | MAX  |

| Number of Pins           | N           |          | 5    |      |

| Pitch                    | е           | 0.65 BSC |      |      |

| Overall Height           | Α           | 0.80     | -    | 1.10 |

| Standoff                 | A1          | 0.00     | -    | 0.10 |

| Molded Package Thickness | A2          | 0.80     | -    | 1.00 |

| Overall Length           | D           | 2.00 BSC |      |      |

| Overall Width            | Е           | 2.10 BSC |      |      |

| Molded Package Width     | E1          | 1.25 BSC |      |      |

| Terminal Width           | b           | 0.15     | -    | 0.40 |

| Terminal Length          | L           | 0.10     | 0.20 | 0.46 |

| Lead Thickness           | С           | 0.08     | -    | 0.26 |

#### Notes:

Note:

- Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or

- protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-061-LT Rev E Sheet 2 of 2

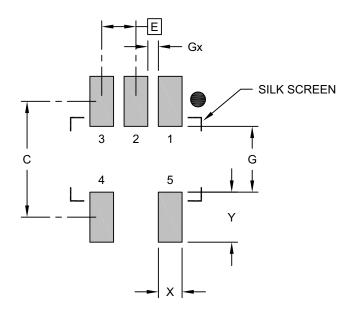

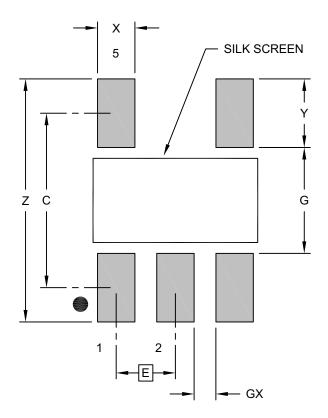

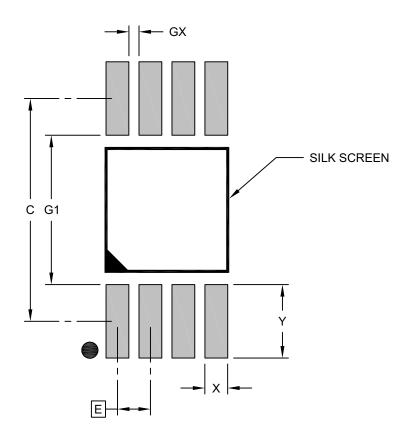

# 5-Lead Plastic Small Outline Transistor (LT) [SC70]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                       | Units            | N        | S    |      |

|-----------------------|------------------|----------|------|------|

| Dimension             | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch         | Е                | 0.65 BSC |      |      |

| Contact Pad Spacing   | С                |          | 2.20 |      |

| Contact Pad Width     | Х                |          |      | 0.45 |

| Contact Pad Length    | Υ                |          |      | 0.95 |

| Distance Between Pads | G                | 1.25     |      |      |

| Distance Between Pads | Gx               | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2061-LT Rev E

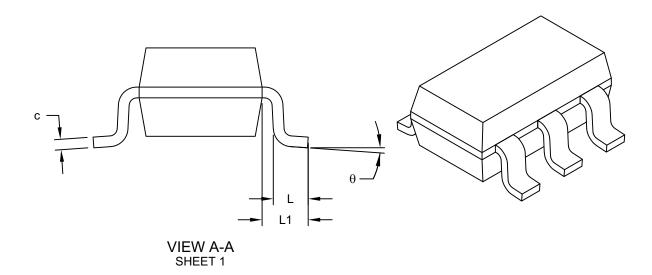

# 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-091-OT Rev H Sheet 1 of 2

## 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |          |      |

|--------------------------|-------------|-------------|----------|------|

| Dimension Limits         |             | MIN         | NOM      | MAX  |

| Number of Pins           | N           |             | 5        |      |

| Pitch                    | е           |             | 0.95 BSC |      |

| Outside lead pitch       | e1          |             | 1.90 BSC |      |

| Overall Height           | Α           | 0.90        | ı        | 1.45 |

| Molded Package Thickness | A2          | 0.89        | -        | 1.30 |

| Standoff                 | A1          | ı           | ı        | 0.15 |

| Overall Width            | Е           | 2.80 BSC    |          |      |

| Molded Package Width     | E1          |             | 1.60 BSC |      |

| Overall Length           | D           |             | 2.90 BSC |      |

| Foot Length              | L           | 0.30        | 1        | 0.60 |

| Footprint                | L1          | 0.60 REF    |          |      |

| Foot Angle               | θ           | 0°          | -        | 10°  |

| Lead Thickness           | С           | 0.08 - 0.26 |          |      |

| Lead Width               | b           | 0.20 - 0.51 |          |      |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-091-OT Rev H Sheet 2 of 2

# 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |          |      |      |

|-------------------------|-------------|----------|------|------|

| Dimension Limits        |             | MIN      | NOM  | MAX  |

| Contact Pitch           | Е           | 0.95 BSC |      |      |

| Contact Pad Spacing     | С           |          | 2.80 |      |

| Contact Pad Width (X5)  | Х           |          |      | 0.60 |

| Contact Pad Length (X5) | Υ           |          |      | 1.10 |

| Distance Between Pads   | G           | 1.70     |      |      |

| Distance Between Pads   | GX          | 0.35     |      |      |

| Overall Width           | Z           |          |      | 3.90 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2091-OT Rev H

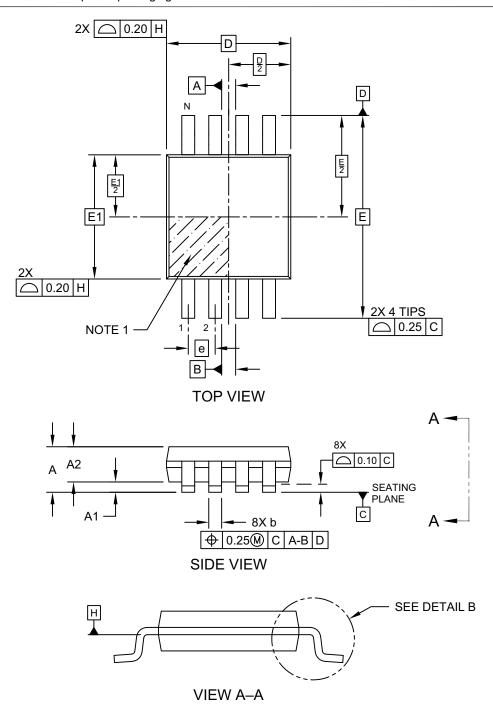

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057-SN Rev K Sheet 1 of 2

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N  | IILLIMETER | S        |      |

|--------------------------|----|------------|----------|------|

| Dimension Limits         |    | MIN        | NOM      | MAX  |

| Number of Pins           | Ν  |            | 8        |      |

| Pitch                    | е  |            | 1.27 BSC |      |

| Overall Height           | Α  | ı          | 1        | 1.75 |

| Molded Package Thickness | A2 | 1.25       | -        | -    |

| Standoff §               | A1 | 0.10       | -        | 0.25 |

| Overall Width            | Е  |            | 6.00 BSC |      |

| Molded Package Width     | E1 | 3.90 BSC   |          |      |

| Overall Length           | D  | 4.90 BSC   |          |      |

| Chamfer (Optional)       | h  | 0.25       | -        | 0.50 |

| Foot Length              | L  | 0.40       | 1        | 1.27 |

| Footprint                | L1 |            | 1.04 REF |      |

| Lead Thickness           | С  | 0.17       | -        | 0.25 |

| Lead Width               | b  | 0.31       | -        | 0.51 |

| Lead Bend Radius         | R  | 0.07       | -        | _    |

| Lead Bend Radius         | R1 | 0.07       | _        | _    |

| Foot Angle               | θ  | 0°         | _        | 8°   |

| Mold Draft Angle         | θ1 | 5°         | _        | 15°  |

| Lead Angle               | θ2 | 0°         | _        | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-057-SN Rev K Sheet 2 of 2

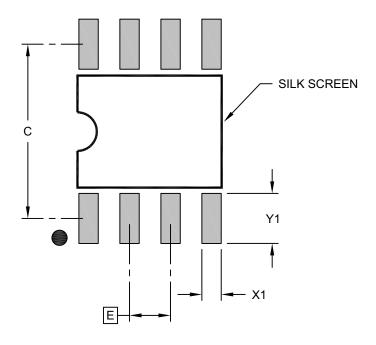

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                         | Units            |          |      | S    |

|-------------------------|------------------|----------|------|------|

| Dimension               | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch           | E                | 1.27 BSC |      |      |

| Contact Pad Spacing     | С                |          | 5.40 |      |

| Contact Pad Width (X8)  | X1               |          |      | 0.60 |

| Contact Pad Length (X8) | Y1               |          |      | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2057-SN Rev K

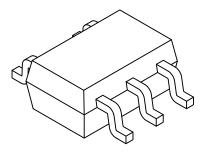

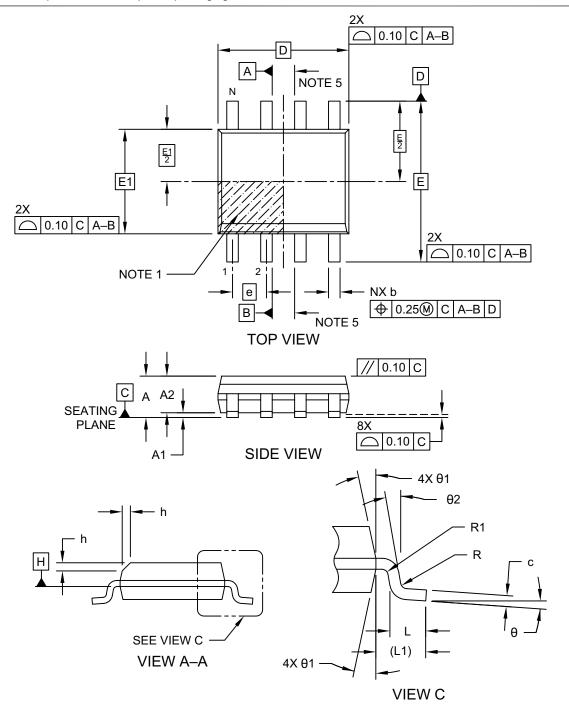

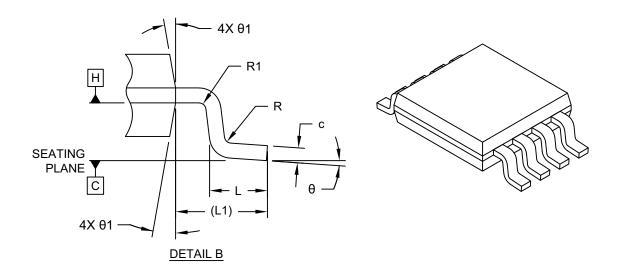

# 8-Lead Plastic Micro Small Outline Package (MS) - 3x3 mm Body [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-111-MS Rev F Sheet 1 of 2

## 8-Lead Plastic Micro Small Outline Package (MS) - 3x3 mm Body [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |             |          |      |

|--------------------------|------------------|-------------|----------|------|

|                          | Dimension Limits | MIN         | NOM      | MAX  |

| Number of Terminals      | N                |             | 8        |      |

| Pitch                    | е                |             | 0.65 BSC |      |

| Overall Height           | А                | _           | _        | 1.10 |

| Standoff                 | A1               | 0.00        | _        | 0.15 |

| Molded Package Thickness | A2               | 0.75        | 0.85     | 0.95 |

| Overall Length           | D                | 3.00 BSC    |          |      |

| Overall Width            | E                | 4.90 BSC    |          |      |

| Molded Package Width     | E1               | 3.00 BSC    |          |      |

| Terminal Width           | b                | 0.22 – 0.40 |          |      |

| Terminal Thickness       | С                | 0.08 – 0.23 |          |      |

| Terminal Length          | L                | 0.40        | 0.60     | 0.80 |

| Footprint                | L1               | 0.95 REF    |          |      |

| Lead Bend Radius         | R                | 0.07 – –    |          | _    |

| Lead Bend Radius         | R1               | 0.07 – –    |          | _    |

| Foot Angle               | θ                | 0°          | _        | 8°   |

| Mold Draft Angle         | θ1               | 5°          | _        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111-MS Rev F Sheet 2 of 2

# 8-Lead Plastic Micro Small Outline Package (MS) - 3x3 mm Body [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### **RECOMMENDED LAND PATTERN**

|                                 | Units            |          |     | S    |

|---------------------------------|------------------|----------|-----|------|

| Dimension                       | Dimension Limits |          | NOM | MAX  |

| Contact Pitch                   | Е                | 0.65 BSC |     |      |

| Contact Pad Spacing             | С                | 4.40     |     |      |

| Contact Pad Width (X8) X        |                  |          |     | 0.45 |

| Contact Pad Length (X8)         | Υ                |          |     | 1.45 |

| Contact Pad to Contact Pad (X4) | G1               | 2.95     |     |      |

| Contact Pad to Contact Pad (X6) | GX               | 0.20     |     |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2111-MS Rev F

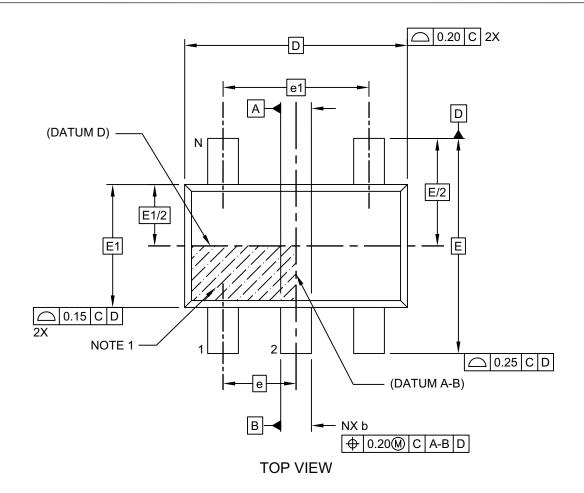

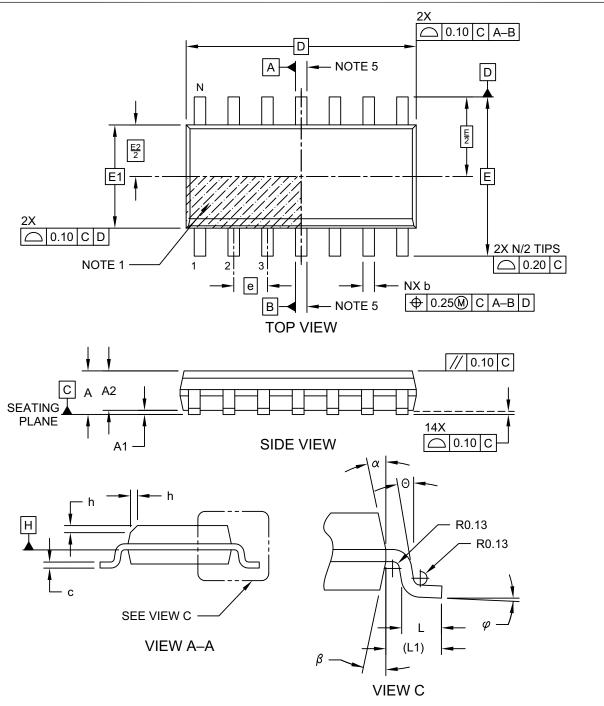

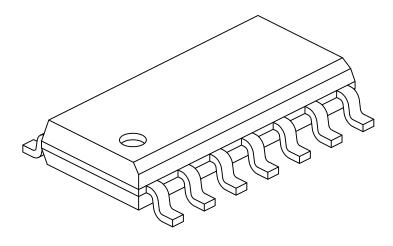

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065-SL Rev D Sheet 1 of 2

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimensior                | MIN         | NOM      | MAX      |      |  |

| Number of Pins           | N           |          | 14       |      |  |

| Pitch                    | е           |          | 1.27 BSC |      |  |

| Overall Height           | Α           | ı        | ı        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25     | ı        | -    |  |

| Standoff §               | A1          | 0.10     | ı        | 0.25 |  |

| Overall Width            | Е           | 6.00 BSC |          |      |  |

| Molded Package Width     | E1          | 3.90 BSC |          |      |  |

| Overall Length           | D           | 8.65 BSC |          |      |  |

| Chamfer (Optional)       | h           | 0.25     | ı        | 0.50 |  |

| Foot Length              | L           | 0.40     | ı        | 1.27 |  |

| Footprint                | L1          | 1.04 REF |          |      |  |

| Lead Angle               | Θ           | 0°       | -        | 1    |  |

| Foot Angle               | φ           | 0°       | -        | 8°   |  |

| Lead Thickness           | С           | 0.10     | -        | 0.25 |  |

| Lead Width               | b           | 0.31     | -        | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°       | -        | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -        | 15°  |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065-SL Rev D Sheet 2 of 2

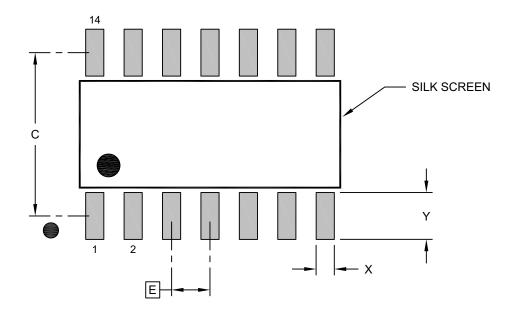

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | Units            |  |          | S    |

|--------------------------|------------------|--|----------|------|

| Dimension                | Dimension Limits |  |          | MAX  |

| Contact Pitch            | Е                |  | 1.27 BSC |      |

| Contact Pad Spacing      | С                |  | 5.40     |      |

| Contact Pad Width (X14)  | Х                |  |          | 0.60 |

| Contact Pad Length (X14) | Υ                |  |          | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065-SL Rev D

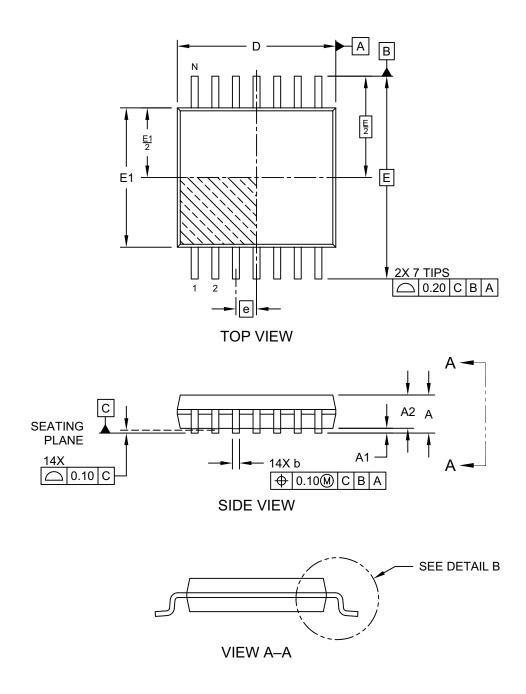

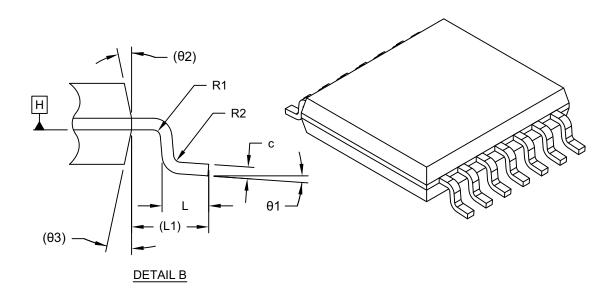

# 14-Lead Plastic Thin Shrink Small Outline Package [ST] - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087-ST Rev F Sheet 1 of 2

## 14-Lead Plastic Thin Shrink Small Outline Package [ST] - 4.4 mm Body [TSSOP]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |

|--------------------------|-------------|----------|----------|------|

| Dimensi                  | MIN         | NOM      | MAX      |      |

| Number of Terminals      | N           |          | 14       |      |

| Pitch                    | е           |          | 0.65 BSC |      |

| Overall Height           | Α           | ı        | _        | 1.20 |

| Standoff                 | A1          | 0.05     | _        | 0.15 |

| Molded Package Thickness | A2          | 0.80     | 1.00     | 1.05 |

| Overall Length           | D           | 4.90     | 5.00     | 5.10 |

| Overall Width            | Е           | 6.40 BSC |          |      |

| Molded Package Width     | E1          | 4.30     | 4.40     | 4.50 |

| Terminal Width           | b           | 0.19     | _        | 0.30 |

| Terminal Thickness       | С           | 0.09     | _        | 0.20 |

| Terminal Length          | L           | 0.45     | 0.60     | 0.75 |

| Footprint                | L1          | 1.00 REF |          |      |

| Lead Bend Radius         | R1          | 0.09     | _        | _    |

| Lead Bend Radius         | R2          | 0.09     | _        | _    |

| Foot Angle               | θ1          | 0°       | _        | 8°   |

| Mold Draft Angle         | θ2          | _        | 12° REF  | -    |

| Mold Draft Angle         | θ3          | _        | 12° REF  | _    |

#### Notes:

- Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087-ST Rev F Sheet 2 of 2

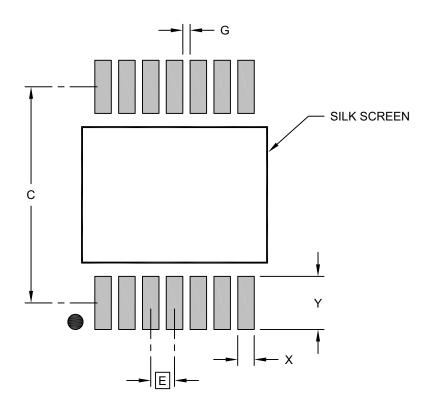

# 14-Lead Plastic Thin Shrink Small Outline Package [ST] – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | N                | <b>IILLIMETER</b> | S    |      |

|----------------------------------|------------------|-------------------|------|------|

| Dimension                        | Dimension Limits |                   |      | MAX  |

| Contact Pitch                    | Е                | 0.65 BSC          |      |      |

| Contact Pad Spacing              | C                |                   | 5.90 |      |

| Contact Pad Width (X14) X        |                  |                   |      | 0.45 |

| Contact Pad Length (X14)         | Υ                |                   |      | 1.45 |

| Contact Pad to Contact Pad (X12) | G                | 0.20              |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2087-ST Rev F

# MCP6571/1R/1U/2/4

NOTES:

## APPENDIX A: REVISION HISTORY

## Revision B (May 2025)

- Updated Table 1-2.

- Changed the LTY SC70 package outline drawings to the correct LT SC70 package outline drawings.

## **Revision A (January 2025)**

• Original release of this document.

# MCP6571/1R/1U/2/4

NOTES:

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.               | <u>X</u> ( 1)                | <u>-X</u>                                                                                          | <u>/XX</u>                    | <u>xxx</u> ( <u>2</u> )   | Examples:         |                                                               |

|------------------------|------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|-------------------|---------------------------------------------------------------|

| Device                 | Tape and Option              | Reel Temperature<br>Range                                                                          | Package                       | CLASS                     | a)MCP6571T-E/LT:  | Tape and Reel,<br>Extended temperature,<br>5LD SC-70 package  |

| Device:                | MCP6571T                     | Single Comparator (SC-70, SOT-23)                                                                  | (Tape and R                   | eel)                      | b)MCP6571T-E/OT:  | Tape and Reel, Extended temperature, 5LD SOT-23 package       |

|                        | MCP6571RT<br>MCP6571UT       | Single Comparator                                                                                  |                               | , , , , ,                 | c)MCP6571RT-E/OT: | Tape and Reel,<br>Extended temperature,<br>5LD SOT-23 package |

|                        | MCP6572T                     | (SC-70, SOT-23)  Dual Comparator  (Tape and Reel for                                               | SOIC, MSOF                    | P)                        | d)MCP6571UT-E/LT: | Tape and Reel,<br>Extended temperature<br>5LD SC-70 package   |

|                        | MCP6574T                     | Quad Comparator<br>(Tape and Reel for                                                              |                               | SOIC)                     | e)MCP6571UT-E/OT: | Tape and Reel,<br>Extended temperature<br>5LD SOT-23 package  |

| Temperatui<br>Package: |                              | = -40°C to +125°C<br>stic Package (SC-70<br>CP6571 only)                                           |                               |                           | a)MCP6572T-E/SN:  | Tape and Reel,<br>Extended temperature<br>8LD SOIC package    |

|                        | (MC                          | stic Small Outline tra<br>CP6571 only)<br>stic Small Outline, (3                                   | ·                             | ,                         | b)MCP6572T-E/MS:  | Tape and Reel, Extended temperature 8LD MSOP package          |

|                        | (MC<br>MS = Plas             | CP6572 only)<br>stic MSOP, 8-lead                                                                  |                               | sau                       | a)MCP6574T-E/ST:  | Tape and Reel, Extended temperature                           |

|                        | ST = Plas                    | CP6572 only)<br>stic Thin Shrink Sma<br>lead (MCP6574 only                                         | `                             | l mm),                    | b)MCP6574T-E/SL:  | 14LD TSSOP package Tape and Reel, Extended temperature        |

|                        | SL = Plas                    | stic Small Outline, (3<br>CP6574 only)                                                             | ,                             | lead                      |                   | 14LD SOIC package                                             |

| Class:                 | (Blank) = Nor<br>VAO = Auto  | n-Automotive<br>omotive                                                                            |                               |                           |                   |                                                               |

| Note 1:                | number descr<br>purposes and | Reel identifier only iption. This identifier is not printed on the p Sales Office for pall option. | is used for o<br>device packa | rdering<br>ge. Check with |                   |                                                               |

| 2:                     | Automotive pa                | arts are AEC-Q100 o                                                                                | ualified. Grad                | de 1.                     |                   |                                                               |

# PRODUCT IDENTIFICATION SYSTEM (AUTOMOTIVE)

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.             | <u>X</u> ( 1)                                       | <u>-</u> X                                                                                    | <u>/XX</u>                                       | <u>XXX<sup>(</sup> 2)</u>             | Examples:             |                                                                         |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------|-----------------------|-------------------------------------------------------------------------|

| Device               | Tape and Ree<br>Option                              | Temperature<br>Range                                                                          | Package                                          | CLASS                                 | a)MCP6571T-E/LTVAO:   | Tape and Reel, Automotive,<br>Extended temperature,5LD<br>SC-70 package |

| Device:              | 4T - Obsessed - O                                   | · · · · · · · · · · · · · · · · · · ·                                                         |                                                  |                                       | b)MCP6571T-E/OTVAO:   | Tape and Reel, Automotive, Extended temperature,                        |

| MCP657               | (SC-70,                                             | omparator (Tape a<br>SOT-23)                                                                  | ina Reei)                                        |                                       |                       | 5LD SOT-23 package                                                      |

| MCP657               | 1RT Single Co<br>(SOT-23)                           | omparator (Tape a<br>)                                                                        | and Reel)                                        |                                       | c)MCP6571RT-E/OTVAO:  | Tape and Reel, Extended temperature, 5LD SOT-23 package                 |

| MCP657               | 1UT Single Co<br>(SC-70, S                          | omparator (Tape a<br>SOT-23)                                                                  | and Reel)                                        |                                       | d)MCP6571UT-E/LTVAO:  | Tape and Reel, Automotive, Extended temperature,                        |

| MCP657               |                                                     | nparator<br>d Reel for SOIC, I                                                                | MSOP)                                            |                                       | e)MCP6571UT-E/OTVAO:  | 5LD SC-70 package Tape and Reel, Automotive                             |

| MCP657               |                                                     | mparator<br>d Reel for TSSOF                                                                  | and SOIC)                                        |                                       | C/MOI 00/101-2/01VA0. | Extended temperature, 5LD SOT-23 package                                |

| Temperature Package: | e Range: E =                                        | -40°C to +125°                                                                                | С                                                |                                       | a)MCP6572T-E/SNVAO:   | Tape and Reel, Automotive, Extended temperature,                        |

|                      | LT= Plastic Pac<br>(MCP6571 only                    | ckage (SC-70), 5-l<br>/)                                                                      | ead                                              |                                       | b)MCP6572T-E/MSVAO:   | 8LD SOIC package Tape and Reel, Extended temperature,                   |

|                      | OT=Plastic Sm<br>(MCP6571 only                      | all Outline transis  /)                                                                       | tor (SOT-23)                                     | ), 5-lead                             |                       | 8LD MSOP package                                                        |

|                      | SN=Plastic Sm<br>(MCP6572 only                      | all Outline, (3.90 ı<br>/)                                                                    | mm), 8-lead                                      |                                       | a)MCP6574T-E/STVAO:   | Tape and Reel, Extended temperature,                                    |

|                      | MS=Plastic MS<br>(MCP6572 only                      | •                                                                                             |                                                  |                                       | b)MCP6574T-E/SLVAO:   | 14LD TSSOP package<br>Tape and Reel,                                    |

|                      | ST=Plastic Thir<br>14-lead (MCP6                    | n Shrink Small Ou<br>574 only)                                                                | tline (4.4 mr                                    | n),                                   |                       | Extended temperature,<br>14LD SOIC package                              |

|                      | SL=Plastic Sm<br>(MCP6574 only                      | all Outline, (3.90 r<br>/)                                                                    | nm), 14-lead                                     | i                                     |                       |                                                                         |

| Class:               | (Blank)= Non-                                       | Automotive                                                                                    |                                                  |                                       |                       |                                                                         |

|                      | VAO = Auto                                          | motive                                                                                        |                                                  |                                       |                       |                                                                         |

|                      | catalog part nu<br>for ordering pu<br>package. Chec | Reel identifier onlumber description. rposes and is notok with your Microability with the Tap | This identific<br>printed on the<br>chip Sales C | er is used<br>ne device<br>Office for |                       |                                                                         |

| 2:                   |                                                     | rts are AEC-Q100                                                                              |                                                  | •                                     |                       |                                                                         |

## **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at <a href="https://www.microchip.com/en-us/about/legal-information/microchip-trademarks">https://www.microchip.com/en-us/about/legal-information/microchip-trademarks</a>.

ISBN: 979-8-3371-1267-1

## **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code.

Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.