# SiWT917 Wi-Fi® and Bluetooth® LE Radio Co-Processor Connectivity Module Datasheet

Silicon Labs' SiWT917 Radio Co-procesor (RCP) Module is a comprehensive multiprotocol wireless sub-system. It has an integrated built-in wireless subsystem and power-management. It has a multi-threaded Network Wireless Processor (NWP) running up to 160 MHz. The wireless subsystem integrates baseband digital signal processing, analog front-end, calibration eFuse, 2.4 GHz RF transceiver, and integrated power amplifier thus providing a fully-integrated solution for a range of hosted wireless applications.

The SiWT917 module is a complete solution offered with robust and fully-upgradeable software stacks, global regulatory certifications, advanced development and debugging tools, and documentation that simplifies and minimizes the development cycle of your end-product, helping to accelerate its time-to-market. The modules come with modular radio type approvals for various countries, including USA (FCC), Canada (IC/ISED), and Japan (MIC), and are in compliance with the relevant EN standards (including EN 300 328 v2.2.2) for conformity with the directives and regulations in the EU and UK.

# SiWT917 applications include:

- · Smart Home

- · Security Cameras

- HVAC

- · Smart Appliances

- · Health and Fitness

- · Pet Tracker

- · Smart Cities

- · Smart Meters

- · Industrial Wearable

- · Smart Buildings

- · Smart hospitals

### **KEY FEATURES**

- Wi-Fi 6 Single Band 2.4 GHz 20 MHz 1x1 stream IEEE 802.11 b/g/n/ax

- · Bluetooth LE 5.4

- Wi-Fi 6 Benefits: TWT for improved efficiency and longer battery life, MU-MIMO/OFDMA for Higher Throughput, network capacity and low latency

- WLAN Tx power up to +17.5 dBm with integrated PA

- Bluetooth LE Tx power up to +17 dBm with integrated PA

- WLAN Rx sensitivity as low as -95.5 dBm

- Wi-Fi 4 Standby Associated mode current:

71 μA @ 1-second beacon listen interval

- Operating temperature: -40 °C to +85 °C

- Operating supply range: 3.0 V 3.63 V

- Supply voltage for GPIOs: 1.71 V to 3.63

### 1. Feature List

### • Wi-Fi<sup>1</sup>

- Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi STA + BLE

- Support for 802.11ax 20 MHz non-AP STA mandatory features (such as OFDMA, MU-MIMO) and optional features of individual Target wake-up time (iTWT), Broadcast TWT (bTWT)<sup>3</sup>, Intra PPDU power save<sup>3</sup>, SU extended range (ER), DCM (Dual Carrier Modulation). DL MU-MIMO, DL/UL OFDMA, MBSSID<sup>1</sup>, BFRP, Spatial Re-use<sup>1</sup>, BSS Coloring<sup>1</sup>, and NDP feedback upto 4 antennas

- Transmit power up to +17.5 dBm with integrated PA

- · Receive sensitivity as low as -95.5 dBm

- Data Rates: 802.11b: 1, 2, 5.5, 11 Mbps; 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range [MHz]: 2412 2462 (North America, default), 2412 - 2472 (Europe, and other countries where applicable), 2412 - 2484 (Japan)

- · PTA Coexistence with Zigbee/Thread/Bluetooth

### Intelligent Power Management

- Power optimizations leveraging multiple power domains and partitioned sub systems

- Many system-, component-, and circuit-level innovations and optimizations

- · Different Power Modes

- · Deep sleep mode with only timer active

### Bluetooth

- · Transmit power up to +17 dBm with integrated PA

- Receive sensitivity LE 1 Mbps: -96 dBm, LR 125 kbps: -105.5 dBm

- · Operating Frequency Range: 2.402 GHz 2.480 GHz

- Supports Bluetooth® Low Energy (LE): High Speed (1 Mbps and 2 Mbps) and Long Range (LE Coded PHYs, 125 kbps and 500 kbps; these are referred to as "LR" throughout this data sheet)

- Advertising extensions

- · Data length extensions

- · LL privacy

- · LE dual role

- · BLE acceptlist

- 2 Simultaneous BLE Connections (2 Peripheral, 2 Central, or 1 Central & 1 Peripheral)

### · RF Features

- · Integrated baseband processor with calibration memory

- Integrated RF transceiver, high-power amplifier, balun and T/R switch

### · Wireless Sub-System Power Consumption

- Wi-Fi 4 Standby Associated mode current: 71 μA @ 1-second beacon listen interval

- · Wi-Fi 1 Mbps Listen current: 16.5mA

- · Wi-Fi LP mode Rx current: 22 mA

- Deep sleep current 11 μA

# Operating Conditions

- Operating supply range: 3.0 V to 3.63 V

- Supply voltage for GPIOs: 1.71 V to 3.63 V

- Operating temperature: -40 °C to +85 °C

### · Software and Regulatory Certifications

- · Wi-Fi Alliance: Wi-Fi 4. Wi-Fi 6

- · Bluetooth SIG Qualification

- Regulatory certifications: FCC (USA), IC/ISED (Canada), CE (EU), UKCA (UK), MIC (Japan), KC (South Korea)<sup>3</sup>, NCC (Taiwan), SRRC (China)<sup>3</sup>, ACMA (Australia), RSM (New Zealand)

- 1. For a detailed list of software features and available profiles, refer to the Software Reference Manuals or contact Silicon Labs for availability. For latest certification information, refer to regulatory app notes or contact Silicon Labs for availability.

- 2. All power and performance numbers are under ideal conditions.

- 3. For information about Software roadmap features and additional certification information, contact Silicon Labs for availability and timeline. Certifications for KC (South Korea) and SRRC (China) are still pending.

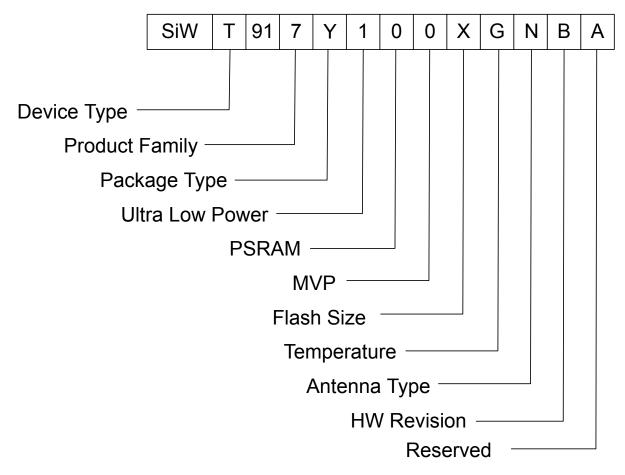

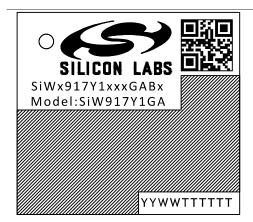

# 2. Ordering Information

Figure 2.1. Ordering Guide

Table 2.1. Orderable Part Number (OPN) Decoder

| Field           | Options                  |

|-----------------|--------------------------|

| Device Type     | T: RCP (Transceiver)     |

|                 | N: NCP                   |

|                 | G: SoC                   |

| Product Family  | 7: Ultra-low power       |

| Package Type    | Y: PCB Modules           |

| Ultra Low Power | 1: ULP Features enabled  |

| PSRAM           | 0: No PSRAM Support      |

|                 | 1: External PSRAM        |

|                 | 2: 2 MB In-Package PSRAM |

|                 | 4: 8 MB In-Package PSRAM |

| MVP             | 0: MVP Features disabled |

|                 | 1: MVP Features enabled  |

| Field        | Options                     |  |  |  |

|--------------|-----------------------------|--|--|--|

| Flash Size   | X: No In-Package Flash      |  |  |  |

|              | L: 4 MB In-Package Flash    |  |  |  |

|              | M: 8 MB In-Package Flash    |  |  |  |

| Temperature  | <b>G</b> : -40 °C to +85 °C |  |  |  |

| Antenna Type | N: No antenna               |  |  |  |

|              | A: Built-in antenna         |  |  |  |

| HW Revision  | B: Revision B               |  |  |  |

| Reserved     | A: Reserved                 |  |  |  |

# **Table 2.2. Part Ordering Options**

| Module OPN       | Protocol stack      | Freq<br>Band | Antenna             | MVP | Flash/<br>RAM(kB) | GPIO | Temp<br>Range       | Packag-<br>ing   |

|------------------|---------------------|--------------|---------------------|-----|-------------------|------|---------------------|------------------|

| SiWT917Y100XGNBA | BLE 5.4 Wi-<br>Fi 6 | 2.4 GHz      | No Anten-<br>na     | No  | No                | 41   | -40 °C to<br>+85 °C | Tape and<br>Reel |

| SiWT917Y100XGABA | BLE 5.4 Wi-<br>Fi 6 | 2.4 GHz      | Built in<br>Antenna | No  | No                | 41   | -40 °C to<br>+85 °C | Tape and<br>Reel |

- 1. Throughout this document, the modules are referred to by their ordering codes above, or by their model names of SiW917Y1GN and SiW917Y1GA, respectively for the hardware variants with no antenna and with integral antenna, or by their marketing/friendly name of SiWT917.

- 2. Devices are shipped without firmware loaded.

# **Table of Contents**

| 1. | . Feature List                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 2                                                                                 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|

| 2. | . Ordering Information .............................                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | 3                                                                                 |

| 3. | . Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 8                                                                                 |

| 4. | . Block Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | 9                                                                                 |

| 5. | . System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | 11                                                                                |

|    | 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | 11                                                                                |

|    | 5.2 WLAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | 11                                                                                |

|    | 5.2.1 MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                                                                                   |

|    | 5.3 Bluetooth                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |                                                                                   |

|    | 5.3.1 MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                                                                                   |

|    | 5.4 RF Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | 13                                                                                |

|    | 5.4.1 Receiver and Transmitter Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                   |

|    | 5.5.1 Highlights                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | 13                                                                                |

|    | 5.5.3 Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |                                                                                   |

|    | 5.6 Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | 14                                                                                |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                                                                   |

| 6. | . Pinout and Pin Description ...........................                                                                                                                                                                                                                                                                                                                                                                                                                      | . '                                     | 15                                                                                |

|    | Pinout and Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                                                                                   |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16                                                                          |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>16                                                                    |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · · · · · · · · · · · · · · · · ·       | 15<br>16<br>16<br>17                                                              |

|    | 6.1 Pin Diagram          6.2 Pin Description          6.2.1 RF and Control Interfaces          6.2.2 Power and Ground Pins          6.2.3 Peripheral Interfaces                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>16<br>17                                                              |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>16<br>17<br>18                                                        |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>17<br>18<br><b>23</b>                                                 |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24                                           |

|    | 6.1 Pin Diagram .  6.2 Pin Description .  6.2.1 RF and Control Interfaces .  6.2.2 Power and Ground Pins .  6.2.3 Peripheral Interfaces .  7.1 Absolute Maximum Ratings .  7.2 Recommended Operating Conditions .  7.3 DC Characteristics .  7.3.1 RESET_N Pin and POC_IN Pins .                                                                                                                                                                                              | - 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>24                               |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>24                               |

|    | 6.1 Pin Diagram .  6.2 Pin Description .  6.2.1 RF and Control Interfaces .  6.2.2 Power and Ground Pins .  6.2.3 Peripheral Interfaces .  Electrical Specifications .  7.1 Absolute Maximum Ratings .  7.2 Recommended Operating Conditions .  7.3 DC Characteristics .  7.3.1 RESET_N Pin and POC_IN Pins .  7.3.2 Power On Control (POC) and Reset .  7.3.3 Thermal Characteristics .                                                                                      |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>24<br>25<br>26                   |

|    | 6.1 Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>24<br>25<br>26<br>26             |

|    | 6.1 Pin Diagram . 6.2 Pin Description . 6.2.1 RF and Control Interfaces . 6.2.2 Power and Ground Pins . 6.2.3 Peripheral Interfaces .  Electrical Specifications . 7.1 Absolute Maximum Ratings . 7.2 Recommended Operating Conditions . 7.3 DC Characteristics . 7.3.1 RESET_N Pin and POC_IN Pins . 7.3.2 Power On Control (POC) and Reset . 7.3.3 Thermal Characteristics . 7.3.4 Digital I/O Signals . 7.4 AC Characteristics . 7.4.1 Clock Specifications .              |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>25<br>26<br>27<br>27             |

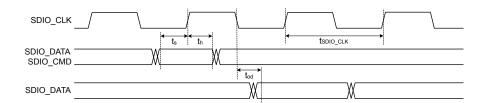

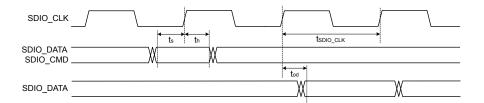

|    | 6.1 Pin Diagram  6.2 Pin Description  6.2.1 RF and Control Interfaces  6.2.2 Power and Ground Pins  6.2.3 Peripheral Interfaces  Flectrical Specifications  7.1 Absolute Maximum Ratings.  7.2 Recommended Operating Conditions  7.3 DC Characteristics.  7.3.1 RESET_N Pin and POC_IN Pins  7.3.2 Power On Control (POC) and Reset  7.3.3 Thermal Characteristics  7.3.4 Digital I/O Signals  7.4 AC Characteristics.  7.4.1 Clock Specifications.  7.4.2 SDIO 2.0 Secondary |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>25<br>26<br>27<br>27<br>28       |

|    | 6.1 Pin Diagram . 6.2 Pin Description . 6.2.1 RF and Control Interfaces . 6.2.2 Power and Ground Pins . 6.2.3 Peripheral Interfaces .  Electrical Specifications . 7.1 Absolute Maximum Ratings . 7.2 Recommended Operating Conditions . 7.3 DC Characteristics . 7.3.1 RESET_N Pin and POC_IN Pins . 7.3.2 Power On Control (POC) and Reset . 7.3.3 Thermal Characteristics . 7.3.4 Digital I/O Signals . 7.4 AC Characteristics . 7.4.1 Clock Specifications .              |                                         | 15<br>16<br>17<br>18<br><b>23</b><br>24<br>24<br>25<br>26<br>27<br>27<br>28<br>29 |

|    | 7.5.2 WLAN 2.4 GHz Receiver Characteristics on High-Performance (HP) Mode   | .31  |

|----|-----------------------------------------------------------------------------|------|

|    | 7.5.3 WLAN 2.4 GHz Receiver Characteristics on Low-Power (LP) Mode          | .33  |

|    | 7.5.4 Bluetooth Transmitter Characteristics on High-Performance (HP) Mode   | .34  |

|    | 7.5.5 Bluetooth Transmitter Characteristics on Low-Power (LP) 0 dBm RF Mode | .35  |

|    | 7.5.6 Bluetooth Receiver Characteristics for 1 Mbps Data Rate               |      |

|    | 7.5.7 Bluetooth Receiver Characteristics for 2 Mbps Data Rate               |      |

|    | 7.5.8 Bluetooth Receiver Characteristics for 125 kbps Data Rate             |      |

|    | 7.5.9 Bluetooth Receiver Characteristics for 500 kbps Data Rate             | .39  |

|    | 7.6 Typical Current Consumption                                             | .40  |

|    | 7.6.1 WLAN 2.4 GHz                                                          |      |

|    | 7.6.2 Bluetooth LE                                                          | .42  |

| 8  | Reference Schematics, BOM, and Layout Guidelines                            | 43   |

| Ο. |                                                                             |      |

|    | 8.1 SiW917Y1GN Schematics for Parts with RF Pin                             |      |

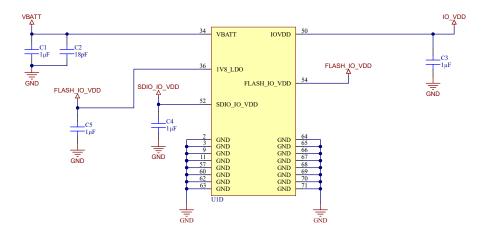

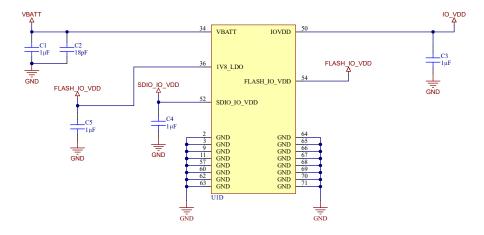

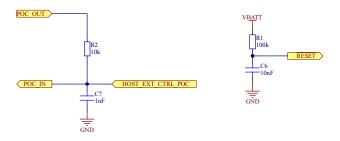

|    | 8.1.1 System Supplies                                                       |      |

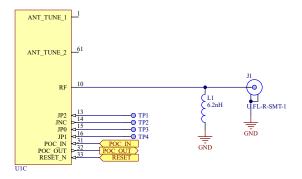

|    | 8.1.2 RF, Debug, and Reset Connection                                       |      |

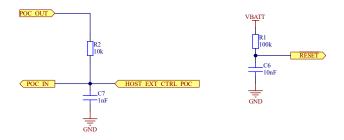

|    | 8.1.4 Reset                                                                 |      |

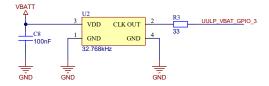

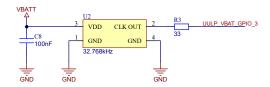

|    | 8.1.5 LF Clock Option                                                       |      |

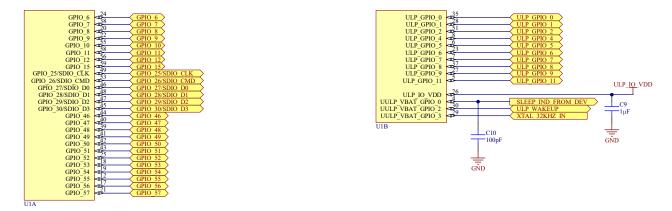

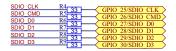

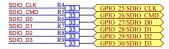

|    | 8.1.6 Host Interface                                                        |      |

|    | 8.1.7 Bill of Materials                                                     |      |

|    |                                                                             |      |

|    | 8.2 SiW917Y1GA Schematics for Parts with Integral Antenna                   |      |

|    | 8.2.2 RF, Debug, and Reset Connection                                       |      |

|    | 8.2.3 GPIO Connection                                                       |      |

|    | 8.2.4 Reset                                                                 |      |

|    | 8.2.5 LF Clock Option                                                       |      |

|    | 8.2.6 Host Interface                                                        |      |

|    | 8.2.7 Bill of Materials                                                     |      |

|    | 8.3 Layout Guidelines                                                       |      |

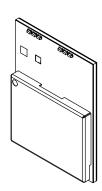

|    | 8.3.1 Installation Guide for SiW917Y1GN Module                              |      |

|    | 8.3.2 Installation Guide for SiW917Y1GA Module                              |      |

|    |                                                                             |      |

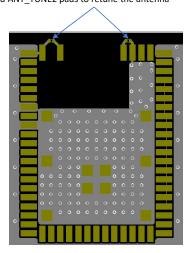

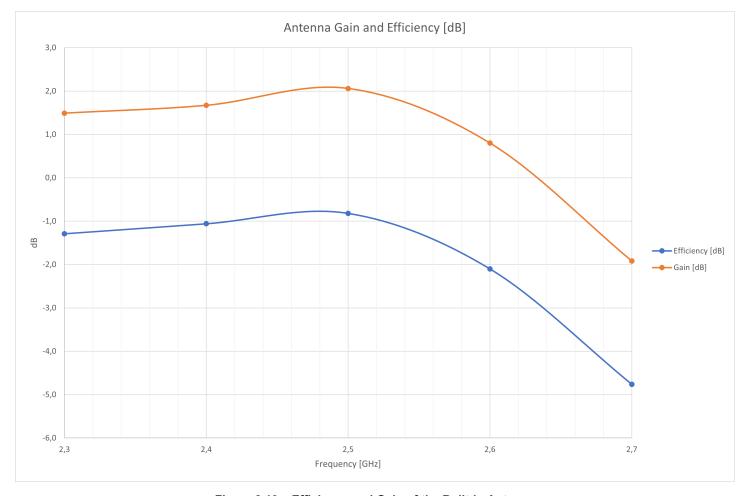

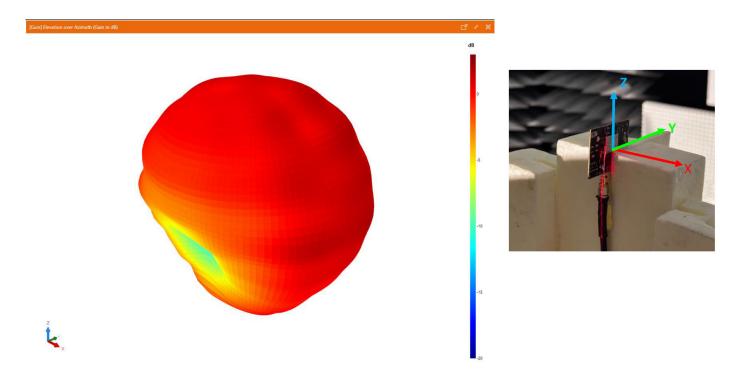

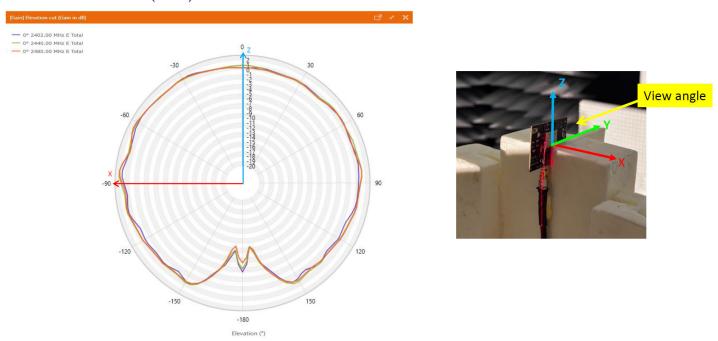

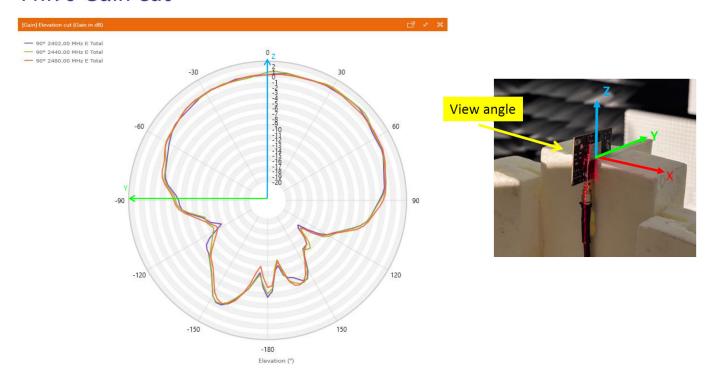

|    | 8.4 SiW917Y1GA Antenna Radiation and Efficiency                             |      |

|    | 8.4.2 Proximity to Human Body                                               |      |

|    |                                                                             |      |

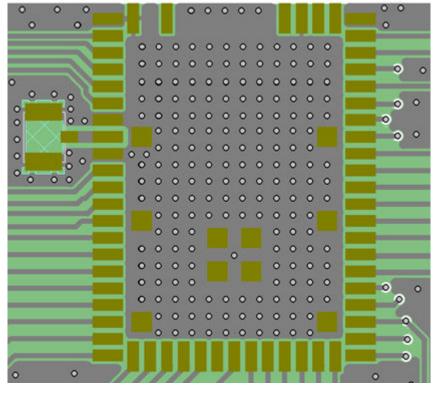

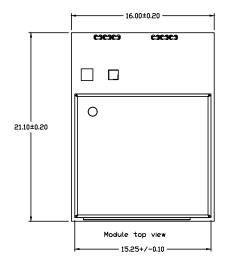

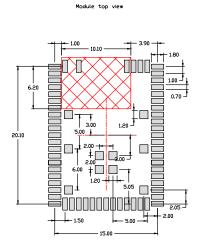

| 9. | Package Specifications                                                      | . 59 |

|    | 9.1 Dimensions                                                              | .59  |

|    | 9.2 Package Outline                                                         | .59  |

|    | 9.2.1 Pin Locations                                                         |      |

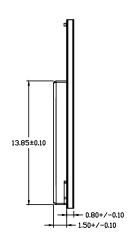

|    | 9.3 PCB Landing Pattern                                                     |      |

|    | 9.4 Module Marking Information                                              |      |

|    |                                                                             |      |

|    | 9.5 Moisture Sensitivity Level                                              | .64  |

| 10 | . Soldering Recommendations                                                 | . 65 |

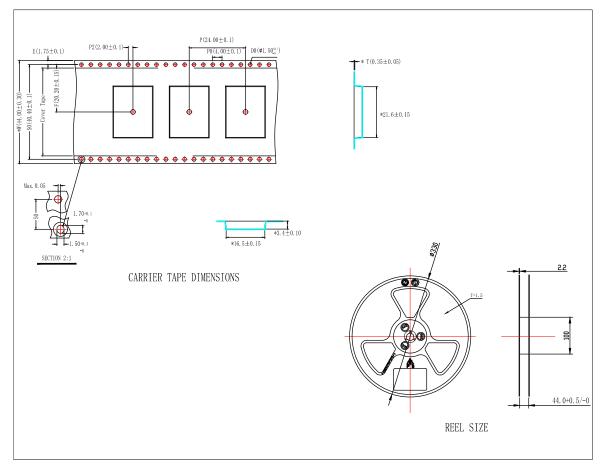

| 11 | . Tape and Reel                                                             | .66  |

| 12. Certifications                                       | <br>67  |

|----------------------------------------------------------|---------|

| 12.1 Qualified Antennas                                  | <br>.67 |

| 12.2 CE and UKCA - EU and UK                             | <br>.68 |

| 12.3 FCC - USA                                           | <br>.68 |

| 12.4 ISED - Canada                                       | <br>.71 |

| 12.5 MIC - Japan                                         | <br>.73 |

| 12.6 KC - South Korea (Pending)                          | <br>.74 |

| 12.7 NCC - Taiwan                                        | <br>.75 |

| 12.8 SRRC - China (Pending)                              | <br>.76 |

| 12.9 ACMA - Australia                                    | <br>.76 |

| 12.10 RF Exposure and Proximity to Human Body            | <br>.77 |

| 12.11 Bluetooth Qualification                            | <br>.78 |

| 13. Documentation and Support .......................... | <br>79  |

| 14. Revision History                                     | <br>80  |

# 3. Applications

### **Smart Home**

Smart Locks, Light Emitting Diode (LED) lights, Door-bell cameras, Washers/Dryers, Refrigerators, Thermostats, Consumer Security cameras, Voice Assistants, etc.

# **Other Consumer Applications**

Toys, Smart dispensers, Weighing scales, Fitness Monitors, Blood pressure monitors, Blood sugar monitors, Portable cameras, etc.

### Other Applications (Medical, Industrial, Retail, Agricultural, Smart City, etc.)

Infusion pumps, Sensors/actuators in Manufacturing, Smart Meters, Automotive After-market, Security Cameras, Gateways, etc.

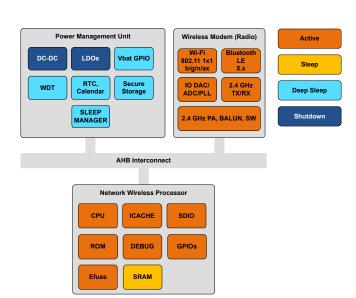

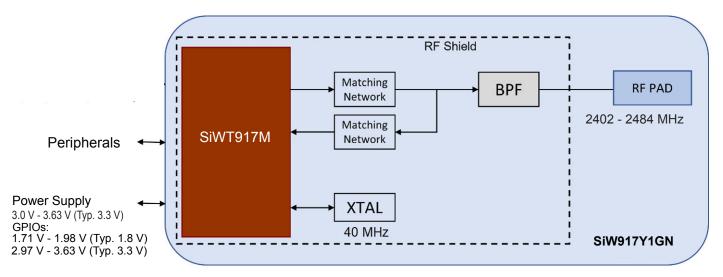

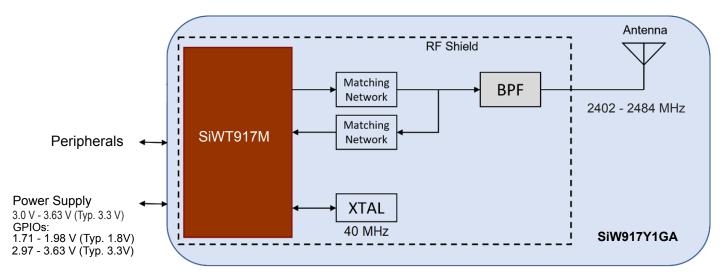

# 4. Block Diagrams

Figure 4.1. SiW917Y1GN (Without Antenna) Module Block Diagram

Figure 4.2. SiW917Y1GA (With Antenna) Module Block Diagram

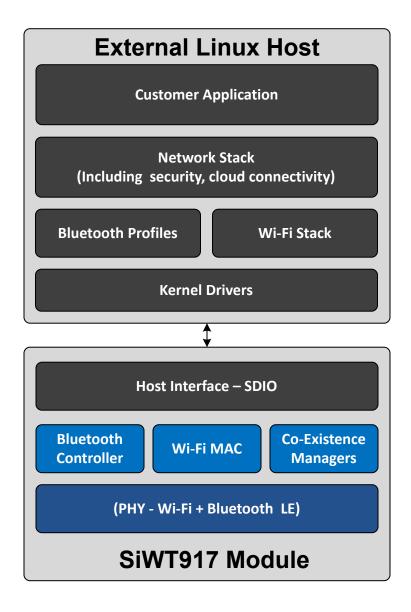

Figure 4.3. SiWT917 RCP Software Architecture

# 5. System Overview

### 5.1 Introduction

SiWT917 module running the RCP mode of operation includes a Network Wireless Processor (NWP) 4-Threaded processor running up to 160 MHz. The wireless subsystem has power, clocks/PLLs, bus-matrices, and memory to support transciever functionality with minimal external resources.

### **5.2 WLAN**

- Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax.

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi + BLE

- Wi-Fi 6 Features: Individual Target wake-up time (iTWT), Broadcast TWT (bTWT),SU extended range (ER), DCM (Dual Carrier Modulation), DL MU-MIMO, DL/UL OFDMA, MBSSID, BFRP, Spatial Re-use, BSS Coloring, and NDP feedback up to 4 antennas

- · Integrated PA

- Data Rates 802.11b: up to 11 Mbps; 802.11g: up to 54 Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range [MHz]: 2412 2462 (North America, default), 2412 2472 (Europe, and other countries where applicable), 2412 2484 (Japan)

### 5.2.1 MAC

- · Conforms to IEEE 802.11b/g/n/ax standards for MAC

- · Hardware accelerators for AES

- WPA, WPA2, WPA3 and WMM support

- · AMPDU aggregation for high performance

- Firmware downloaded from host based on application

### 5.2.2 Baseband Processing

- Supports 11b: DSSS for 1, 2 Mbps and CCK for 5.5, 11 Mbps

- · Supports all OFDM data rates

- 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps

- 802.11ax, 802.11n: MCS 0 to MCS 7

- · High-performance multipath handling in OFDM, DSSS, and CCK modes

### 5.3 Bluetooth

### **Key Features**

- · Transmit power up to +17 dBm with integrated PA

- Receive sensitivity LE 1 Mbps: -94 dBm, LE 2 Mbps: -91.5 dBm, LR 500 Kbps: -101.5 dBm, LR 125 kbps: -105.5 dBm

- Operating Frequency Range: 2.402 GHz 2.480 GHz

- Supports Bluetooth® Low Energy (LE): High Speed (1 Mbps and 2 Mbps) and Long Range (LE Coded PHYs, 125 kbps and 500 kbps; these are referred to as "LR" throughout this data sheet)

- · Extended Advertising

- · Extended Advertising scanning

- · Periodic Advertising

- · Periodic Advertising scanning

- · Periodic Advertising list

- · Periodic advertising synchronization

- · Data length extensions

- · LL privacy 1.2

- · LE Secure connections

- LE channel selection algorithm 2 (CSA#2)

- · LE dual role

- · BLE acceptlist

- Two simultaneous BLE connections (2 peripheral or 2 central, or 1 central and 1 peripheral)

- · BLE Mesh (4 nodes) for limited switch use case.

### 5.3.1 MAC

### Link Manager

- · Creation, modification & release of physical links

- · Connection establishment between Link managers of two Bluetooth devices

- · Link supervision is implemented in Link Manager

- · Link power control is done depending on the inputs from Link Controller

- · Enabling & disabling of encryption & decryption on logical links

# **Link Controller**

- · Encodes and decodes header of BLE packets

- · Manages flow control, acknowledgment, re-transmission requests, etc.

- · Stores the last packet status for all physical transports

- · Indicates the success status of packet transmission to upper layers

- · Indicates the link quality to the LMP layer

### **Device Manager**

- Executes HCI Commands

- Controls Scan & Connection processes

- · Controls all BLE Device operations except data transport operations

- · BLE Controller state transition management

- · Anchor point synchronization & management

- Scheduler

# 5.3.2 Baseband Processing

· Supports BLE 1 Mbps, 2 Mbps and Long Range 125 kbps, 500 kbps

### 5.4 RF Transceiver

- SiWT917 features two highly configurable RF transceivers supporting WLAN 11b/g/n/ax and Bluetooth LE wireless protocols. Both

RF transceivers together operating in multiple modes covering High Performance (HP) and Low Power (LP) operations. List of operating modes are given in the next section.

- It contains two fully integrated fractional-N frequency synthesizers having reference from internal oscillator with 40 MHz crystal. One

of the synthesizers is a low-power architecture which also caters single-bit data modulation feature for Bluetooth LE protocols.

### 5.4.1 Receiver and Transmitter Operating Modes

The available radio operating modes are as follows:

- WLAN HP TX WLAN High-Performance Transmitter

- · WLAN HP RX WLAN High-Performance Receiver

- · WLAN LP RX WLAN Low-Power Receiver

- BLE HP TX Bluetooth LE High-Performance Transmitter

- · BLE HP RX Bluetooth LE High-Performance Receiver

- BLE LP TX Bluetooth LE Low-Power Transmitter

- · BLE LP RX Bluetooth LE Low-Power Receiver

Note: All the TX / RX modes are automatically controlled by radio firmware and not individually selectable.

### 5.5 Power Architecture

The Power Control Hardware implements the control sequences for transitioning between different power states (Active/Standby/Sleep/Shutdown).

### 5.5.1 Highlights

- Two integrated buck switching regulators (High performance and ULP) to enable efficient Voltage Scaling across wide operating mode currents ranging from <1 µA to 170 mA</li>

- · Multiple voltage domains with Independent voltage scaling of each domain.

- Fine grained power-gating including peripherals, buses and pads, thereby reducing power consumption when the peripheral/buses/ pads are inactive.

- Flexible switching between different Active states with controls from Software.

- Hardware based wakeup from Standby/Sleep/Shutdown states.

- All the peripherals are clock gated by default thereby reducing the power consumption in inactive state.

- · Low wakeup times as configurable by Software.

### 5.5.2 System Power Supply Configurations

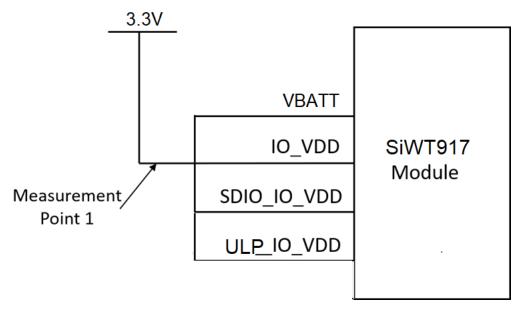

SiWT917 module support highly flexible power supply configurations for various application scenarios. Two application scenarios are listed below.

- 3.3 V single supply A single 3.3 V supply derived from the system PMU can be input to all I/O supplies.

- 1.8 V and 3.3 V supply A 1.8 V supply derived from the system PMU can be input to all I/O supplies except VBATT.

# 5.5.3 Power Management

The SiWT917 module have an internal power management subsystem, including DC-DC converters and linear regulators. This subsystem generates all the voltages required by the module to operate from a wide variety of input sources.

- · Input voltage (3.3 V) on pin VBATT

- Input voltage (1.8 V or 3.3 V) on pin IO\_VDD, SDIO\_IO\_VDD and ULP\_IO\_VDD

- Input voltage (1.8 V) on pin FLASH IO VDD

- Nominal Output 1.8 V and 48 mA maximum load on pin 1V8 LDO

# **5.6 Memory Architecture**

There are on chip Read Only Memory (ROM) and Random Access Memory (RAM).

The NWP processor has the following memory:

- Embedded SRAM up to 672 KB total

- 448 KB of ROM

- 16 KB of Instruction cache (I cache)

- eFuse of 1024 bytes (used to store primary boot configuration and calibration parameters)

# 6. Pinout and Pin Description

# 6.1 Pin Diagram

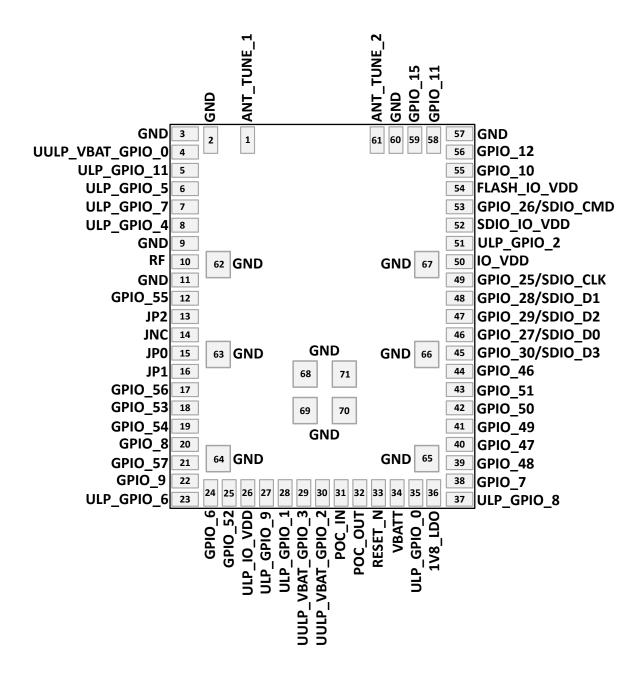

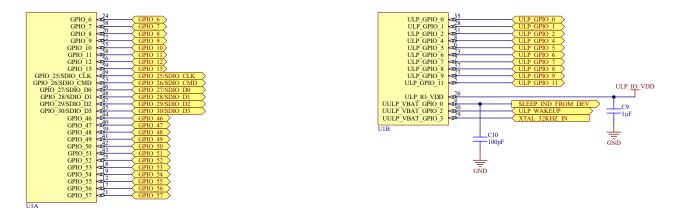

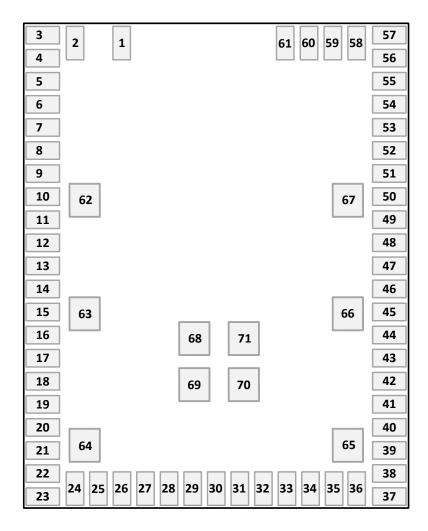

Figure 6.1. SiWT917 Pin Diagram

# 6.2 Pin Description

Table 6.1. List of Pins in IC (SiWT917M), Not Available in the Modules

| Pin Name            | QFN I/O Supply Domain | Direction | Initial State (Power up, Active Reset) | Description                          |

|---------------------|-----------------------|-----------|----------------------------------------|--------------------------------------|

| RF_BLETX            | RF_AVDD               | Output    | NA                                     | BLE 8 dBm RF Output                  |

| ULP_GPIO_10         | ULP_IO_VDD            | Inout     | HighZ                                  | Default: HighZ                       |

|                     |                       |           |                                        | Sleep: HighZ                         |

| XTAL_32KHZ_P        | NA                    | Inout     | NA                                     | Analog Pin. 32KHZ XTAL<br>Connection |

| XTAL_32KHZ_N        | NA                    | Inout     | NA                                     | Analog Pin. 32KHZ XTAL<br>Connection |

| UULP VBAT GPIO 1    | VBATT                 | Inout     | HighZ                                  | Default: High                        |

| 0021 _12,11_01 10_1 | V 57 ( ) 1            | mout      | 1 119112                               | Sleep: High                          |

# 6.2.1 RF and Control Interfaces

Table 6.2. Chip Packages - RF and Control Interfaces

| Pin Name   | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                  |

|------------|------------|------------------------|-----------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANT_TUNE_1 | 1          | N/A                    | Input     | N/A                                         | SiW917Y1GA: External fine-tuning option for the integral antenna; connect same tuning circuit on both ANT_TUNE1 and ANT_TUNE2 pins; leave floating if no fine-tuning is desired on the integral antenna; SiW917Y1GN: leave this pin floating |

| RF         | 10         | VBATT                  | Inout     | N/A                                         | Connect to antenna with a 50-Ω impedance as per the reference schematics                                                                                                                                                                     |

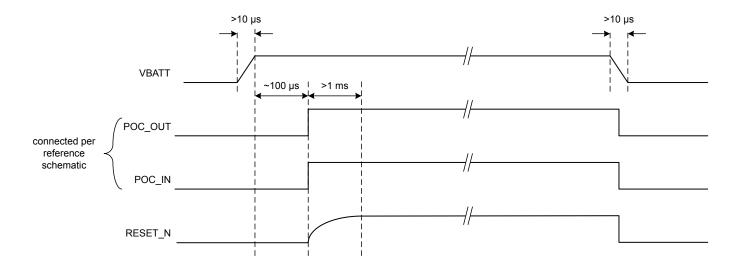

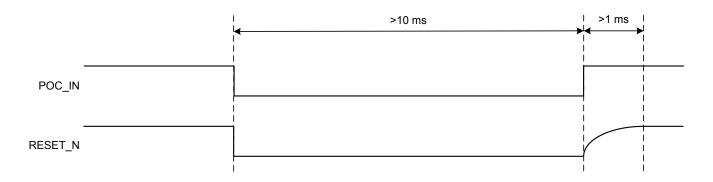

| POC_IN     | 31         | VBATT                  | Input     | NA                                          | This is an input to the chip which resets all analog and digital blocks in the device. It should be made high only after supplies are valid.                                                                                                 |

| POC_OUT    | 32         | VBATT                  | Output    | NA                                          | This is internally generated. Initially, it is low. But it becomes high when the supply (VBATT) is valid.                                                                                                                                    |

| RESET_N    | 33         | VBATT                  | Inout     | NA                                          | Active-low reset asynchronous reset signal, which resets only digital blocks. RESET_N will be pulled low if POC_IN is low.                                                                                                                   |

| ANT_TUNE_2 | 61         | N/A                    | Input     | N/A                                         | SiW917Y1GA: External fine-tuning option for the integral antenna; connect same tuning circuit on both ANT_TUNE1 and ANT_TUNE2 pins; leave floating if no fine-tuning is desired on the integral antenna; SiW917Y1GN: leave this pin floating |

# 6.2.2 Power and Ground Pins

Table 6.3. Chip Packages - Power and Ground Pins

| Pin Name     | Pin No.                             | Туре   | Direction | Description                                                                                              |

|--------------|-------------------------------------|--------|-----------|----------------------------------------------------------------------------------------------------------|

| ULP_IO_VDD   | 26                                  | Power  | Input     | I/O supply for ULP I/Os. Refer to GPIOs section for details on which GPIOs have this as the I/O supply.  |

| VBATT        | 34                                  | Power  | Input     | Power supply for the module.                                                                             |

| 1V8_LDO      | 36                                  | Power  | Output    | Output of 1.8 V LDO.                                                                                     |

| IO_VDD       | 50                                  | Power  | Input     | I/O Supply for GPIOs. Refer to GPIOs section for details on which GPIOs have this as the I/O supply.     |

| SDIO_IO_VDD  | 52                                  | Power  | Input     | I/O Supply for SDIO I/Os. Refer to GPIOs section for details on which GPIOs have this as the I/O supply. |

| FLASH_IO_VDD | 54                                  | Power  | Input     | Unused for RCP device. Connect to 1V8_LDO.                                                               |

| GND          | 2, 3, 9,<br>11, 57,<br>60,<br>62-71 | Ground |           | Common ground pins.                                                                                      |

# 6.2.3 Peripheral Interfaces

Table 6.4. Chip Packages - Peripheral Interfaces

| Pin Name         | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|------------|------------------------|-----------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UULP_VBAT_GPIO_0 | 4          | VBATT                  | Output    | High                                        | Default: High                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |            |                        |           |                                             | Sleep: High                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |            |                        |           |                                             | This pin can be configured by software to be any of the following.  • SLEEP_IND_FROM_DEV: This signal is used to send an indication to the Host processor. An indication is sent when the chip enters (logic low) and exits (logic high) the ULP Sleep mode. Supply domain for UULP_VBAT_GPIOs is VBATT and the supported voltage range is defined in Table 7.2 Recommended Operating Conditions on page 24. |

| ULP_GPIO_11      | 5          | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

| ULP_GPIO_5       | 6          | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

| ULP_GPIO_7       | 7          | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

| ULP_GPIO_4       | 8          | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO_55          | 12         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

| JP2              | 13         | IO_VDD                 | Input     | Pullup                                      | Default: JP2                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | JP2 - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                                                                                                                                               |

| JNC              | 14         | IO_VDD                 | Output    | Pullup                                      | Default: JNC                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | JNC - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                                                                                                                                               |

| JP0              | 15         | IO_VDD                 | Input     | Pullup                                      | Default: JP0                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |            |                        |           |                                             | JP0 - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                                                                                                                                               |

| Pin Name   | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                         |

|------------|------------|------------------------|-----------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| JP1        | 16         | IO_VDD                 | Input     | Pullup                                      | Default: JP1                                                                                                        |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

|            |            |                        |           |                                             | JP1 - Reserved. Connect to a test point for debugging purposes                                                      |

| GPIO_56    | 17         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_53    | 18         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_54    | 19         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_8     | 20         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_57    | 21         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_9     | 22         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| ULP_GPIO_6 | 23         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

|            |            |                        |           |                                             | This pin can be configured by software to be any of the following.                                                  |

|            |            |                        |           |                                             | PTA_PRIO: "PTA Priority" input signal is<br>part of 3-wire coexistence (Packet Traf-<br>fic Arbitration) interface. |

| GPIO_6     | 24         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| GPIO_52    | 25         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| ULP_GPIO_9 | 27         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

| ULP_GPIO_1 | 28         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                      |

|            |            |                        |           |                                             | Sleep: HighZ                                                                                                        |

|            |            |                        |           |                                             | This pin can be configured by software to be any of the following                                                   |

|            |            |                        |           |                                             | PTA_REQ: "PTA Request" input signal<br>is part of 3-wire coexistence (Packet<br>Traffic Arbitration) interface.     |

| Pin Name         | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                                                                 |

|------------------|------------|------------------------|-----------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

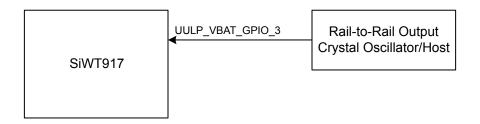

| UULP_VBAT_GPIO_3 | 29         | VBATT                  | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: EXT_32KHZ_IN                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                                             | This pin can be configured by software to be any of the following.                                                                                                                                                                                                                          |

|                  |            |                        |           |                                             | EXT_32KHZ_IN: This pin can be used to feed external clock from a host processor or from external crystal oscillator. Supply domain for UULP_VBAT_GPIOs is VBATT and the supported voltage range is defined in Table 7.2 Recommended Operating Conditions on page 24.                        |

| UULP_VBAT_GPIO_2 | 30         | VBATT                  | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: ULP_WAKEUP                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                                             | After bootloading, this signal is an active-high input to indicate that the device should wakeup from its Ultra Low Power (ULP) sleep mode. Supply domain for UULP_VBAT_GPIOs is VBATT and the supported voltage range is defined in Table 7.2 Recommended Operating Conditions on page 24. |

| ULP_GPIO_0       | 35         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| ULP_GPIO_8       | 37         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| GPIO_7           | 38         | IO_VDD                 | Inout     | HighZ                                       | Default:HighZ                                                                                                                                                                                                                                                                               |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

|                  |            |                        |           |                                             | This pin can be configured by software to be any of the following.                                                                                                                                                                                                                          |

|                  |            |                        |           |                                             | PTA_GRANT: "PTA Grant" output signal is part of 3-wire coexistence (Packet Traffic Arbitration) interface.                                                                                                                                                                                  |

| GPIO_48          | 39         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| GPIO_47          | 40         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| GPIO_49          | 41         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| GPIO_50          | 42         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| GPIO_51          | 43         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                              |

|                  |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                |

| Pin Name         | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) |                       | Description                                      |       |  |

|------------------|------------|------------------------|-----------|---------------------------------------------|-----------------------|--------------------------------------------------|-------|--|

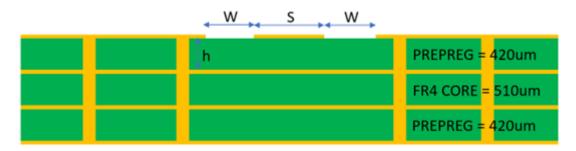

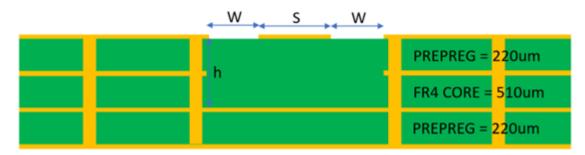

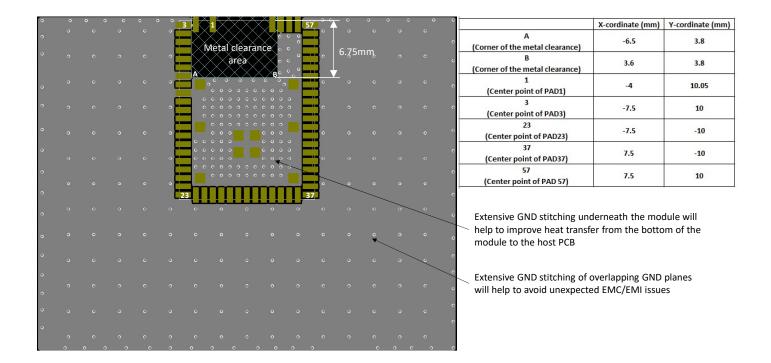

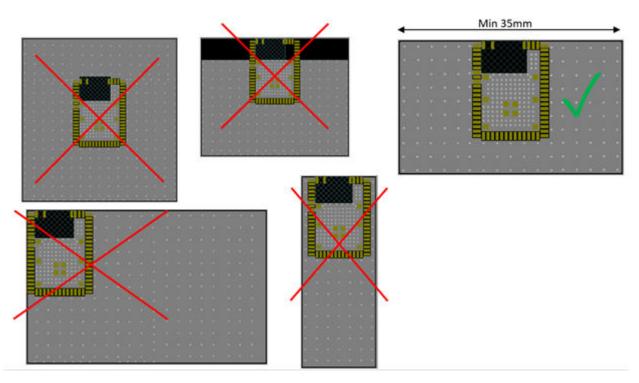

| GPIO_46          | 44         | IO_VDD                 | Inout     | HighZ                                       | Default: High         | Z                                                |       |  |