# **Product Change Notification: SYST-25GKII385**

Date:

02-Jul-2025

# **Product Category:**

**Motor Control Sips**

# **Notification Subject:**

dsPIC33CDVL64MC106 Family Silicon Errata and Data Sheet Clarification

## **Affected CPNs:**

SYST-25GKII385\_Affected\_CPN\_07022025.pdf SYST-25GKII385\_Affected\_CPN\_07022025.csv

## **Notification Text:**

#### SYST-25GKII385

Microchip has released a new Document for the dsPIC33CDVL64MC106 Family Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at dsPIC33CDVL64MC106 Family Silicon Errata and Data Sheet Clarification.

**Notification Status:** Final

**Description of Change:**

Added silicon revision D3.

Added silicon issue 10 (MOSFET Gate Driver).

**Impacts to Data Sheet:** None.

**Reason for change:** To Improve Productivity.

**Change Implementation Status:** Complete

**Date Document Changes Effective:** 02 Jul 2025

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices::N/A

### **Attachments:**

dsPIC33CDVL64MC106 Family Silicon Errata and Data Sheet Clarification

Please contact your local Microchip sales office with questions or concerns regarding this notification.

#### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> <u>home page</u> select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from

| Affected | Catal | og ] | Part 1 | Num | bers ( | CPN |  |

|----------|-------|------|--------|-----|--------|-----|--|

|----------|-------|------|--------|-----|--------|-----|--|

DSPIC33CDV64MC106-E/M8

DSPIC33CDV64MC106-E/M8VAO

DSPIC33CDV64MC106-I/M8

DSPIC33CDV64MC106T-H/M8

DSPIC33CDV64MC106T-H/M8VAO

DSPIC33CDV64MC106-H/M8

DSPIC33CDV64MC106-H/M8VAO

DSPIC33CDV64MC106T-I/M8

DSPIC33CDV64MC106T-E/M8

DSPIC33CDV64MC106T-E/M8VAO

DSPIC33CDVL64MC106-E/M8

DSPIC33CDVL64MC106-E/M8VAO

DSPIC33CDVL64MC106-I/M8

DSPIC33CDVL64MC106T-H/M8

DSPIC33CDVL64MC106T-H/M8VAO

DSPIC33CDVL64MC106-H/M8

DSPIC33CDVL64MC106-H/M8VAO

DSPIC33CDVL64MC106T-I/M8

DSPIC33CDVL64MC106T-E/M8

DSPIC33CDVL64MC106T-E/M8V01

DSPIC33CDVL64MC106T-E/M8VAO

Date: Tuesday, July 1, 2025

# dsPIC33CDVL64MC106 Family Silicon Errata and Data Sheet Clarification

The dsPIC33CDVL64MC106 family devices that you have received conform functionally to the current Device Data Sheet (DS70005441**E**), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the dsPIC33CDVL64MC106 silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (D3).

Data Sheet clarifications and corrections start on page 8, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB® IDE and Microchip's programmers, debuggers and emulation tools, which are available at the Microchip corporate website (www.microchip.com).

For example, to identify the silicon revision level using MPLAB IDE in conjunction with a hardware debugger:

- Using the appropriate interface, connect the device to the hardware debugger.

- 2. Open an MPLAB IDE project.

- 3. Configure the MPLAB IDE project for the appropriate device and hardware debugger.

- 4. Based on the version of MPLAB IDE you are using, do one of the following:

- a) For MPLAB IDE 8, select <u>Programmer ></u> Reconnect.

- For MPLAB X IDE, select <u>Window > Dash-board</u> and click the **Refresh Debug Tool**.

#### TABLE 1: SILICON DEVREY VALUES

| Part Number        | Device ID <sup>(1)</sup> | Revision ID for Silicon Revision |        |         |  |  |

|--------------------|--------------------------|----------------------------------|--------|---------|--|--|

| Fait Number        | Device ID.               | D1                               | D2     | D3      |  |  |

| dsPIC33CDVL64MC106 | 0x991A                   | 0x0001                           | 0x0002 | 0,,0003 |  |  |

| dsPIC33CDV64MC106  | 0x991B                   | 0.0001                           | 0x0002 | 0x0003  |  |  |

Note 1: The Device IDs (DEVID and DEVREV) are located at the last two implemented addresses of configuration memory space. They are shown in hexadecimal in the format "DEVID DEVREV".

### TABLE 2: SILICON ISSUE SUMMARY

|                          | F                        | Item   |                                                                                                                               | Affec | cted Revis | ions |

|--------------------------|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|

| Module                   | Feature                  | Number | Issue Summary                                                                                                                 | D1    | D2         | D3   |

| CPU                      | div.sd<br>Instruction    | 1.     | When using the signed 32-by-16-bit division instruction, div.sd, the Overflow bit is not getting set when an overflow occurs. | Х     | X          | Х    |

| I2C                      | Interrupt                | 2.     | In Client mode, an incorrect interrupt is generated with DHEN = 1.                                                            | Х     | Х          | Х    |

| I2C                      | Idle                     | 3.     | SFRs are reset in Idle mode.                                                                                                  | Х     | Х          | Х    |

| Oscillator               | VCO Dividers             | 4.     | Main and auxiliary PLL external VCO dividers can fail to output the clock signal.                                             | Х     | Х          | Х    |

| PWM                      | Time Base<br>Capture     | 5.     | The PWM Capture Status (CAP) flag will not set again under certain conditions.                                                | Х     | Х          | Х    |

| UART                     | Sleep                    | 6.     | When waking from Sleep with a UART reception, SLPEN needs to be set in addition to WAKE = 1.                                  | Х     | Х          | Х    |

| UART                     | IrDA <sup>®</sup>        | 7.     | IrDA <sup>®</sup> not functional.                                                                                             | Х     | Х          | Х    |

| MOSFET<br>Gate<br>Driver | Sleep Mode               | 8.     | The MOSFET Gate Driver may not function as expected if Sleep mode is enabled.                                                 | Х     |            |      |

| MOSFET<br>Gate<br>Driver | XUVLO Fault<br>Detection | 9.     | After any device Reset, when the High-side driver is enabled for the first time, an erroneous XUVLO FAULT may be triggered.   | Х     | Х          | Х    |

| MOSFET<br>Gate<br>Driver | Sleep Mode               | 10.    | The MOSFET Gate Driver may fail to wake from Sleep mode if using the LIN Transceiver's INH output as the WAKE source.         | Х     | Х          |      |

#### Silicon Errata Issues

Note:

This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (**D3**).

#### 1. Module: CPU

When using the Signed 32-by-16-Bit Division instruction, div.sd, the Overflow bit may not always get set when an overflow occurs. This errata only affects operations in which at least one of the following conditions is true:

- · Dividend and divisor differ in sign

- Dividend > 0x3FFFFFF

- Dividend < 0xC0000000

#### Work around

The application software must perform both of the following actions to handle possible undetected overflow conditions:

- a) The value of the dividend must always be constrained to be in the following range: 0xC0000000 ≤ Dividend ≤ 0x3FFFFFFF.

- b) If the dividend and divisor differ in sign (e.g., the dividend is negative and divisor is positive), then after executing the div.sd instruction or the compiler built-in function, \_\_builtin\_divsd(), inspect the sign of the resultant quotient. If the quotient is found to be a positive number, then treat it as an overflow condition.

#### **Affected Silicon Revisions**

| <b>)</b> 1 | D2 | D3 |  |  |  |

|------------|----|----|--|--|--|

| Χ          | Χ  | Χ  |  |  |  |

### 2. Module: I<sup>2</sup>C

In Cilent mode with DHEN = 1 (Data Hold Enable), if software sends a NACK, a Client interrupt is asserted at the 9th falling edge of the clock.

#### Work around

Software should ignore the Cilent interrupt that is asserted after sending a NACK.

#### **Affected Silicon Revisions**

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Χ  | Χ  |  |  |  |

### 3. Module: I<sup>2</sup>C

In Client mode, the SFRs are reset when the device is in Idle and the module is set for discontinue in Idle (I2CSIDL).

#### Work around

None.

#### **Affected Silicon Revisions**

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Χ  | Χ  |  |  |  |

#### 4. Module: Oscillator

At PLL start-up, the main PLL VCO dividers may occasionally halt and not provide a clock output. The VCO dividers can be selected as clock sources for different peripheral modules, including the ADC, PWM, DAC, UART, etc. VCO divider outputs, Fvco/2, Fvco/3, Fvco/4 and Fvcodiv, are affected.

#### Work around

- Use another clock source, such as the Fosc or PLL Output (FPOLLO), instead of the VCO dividers.

- If the application requires the VCO divider, test the clock source before using the peripheral in the end application. System resources, including a timer, I/O pin state or interrupts, can be used to detect and verify peripheral activity for a presence of the VCO divider clock output. Any type of Reset may recover the VCO divider clock (Software Reset, WDT, MCLR or POR).

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Х  | Х  |  |  |  |

#### 5. Module: PWM

When using a PWM Control Input (PCI) to trigger a time base capture, the Capture Status flag, CAP (PGxSTAT[5]), may not set again under certain conditions. When a subsequent PWM capture event occurs while, or just after, reading the current capture value from the PGxCAP register, the Capture Status flag, CAP, will not set again.

#### Work around

Read the PWM Generator Capture (PGxCAP) register at a known time to avoid the condition. The timing of the PGxCAP read operation can be scheduled by using PWM Generator x interrupt or any of the PWM event interrupts corresponding to the PCI event that triggered the time base capture. Read the PGxCAP value after the CAP bit has set within the interrupt.

#### **Affected Silicon Revisions**

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Х  | Х  |  |  |  |

#### 6. Module: UART

When waking from Sleep with a UART reception, SLPEN needs to be set in addition to WAKE = 1.

#### Work around

Set the SPLEN bit in addition to WAKE before entering Sleep.

#### **Affected Silicon Revisions**

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Χ  | Χ  |  |  |  |

#### 7. Module: UART

The IrDA® module is not functional.

#### Work around

None.

#### **Affected Silicon Revisions**

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Х  | Х  |  |  |  |

#### 8. Module: MOSFET Gate Driver

When the MOSFET gate driver HVDD is momentarily sustained at near the POR threshold of 2.7V to 3.2V, followed by device normal operation, and if the MOSFET gate driver entered into Sleep mode, it appears not to wake up from Sleep. The momentarily-sustained HVDD condition could occur with rising or falling HVDD. Only the Sleep mode is affected.

#### Work around

Use Standby mode of operation for the MOSFET gate driver, if the application desires lower power than the Active mode. Do not use Sleep mode on the MOSFET gate driver.

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  |    |    |  |  |  |

#### 9. Module: MOSFET Gate Driver

After any device Reset, when the High-side driver is enabled for the first time, an erroneous XUVLO (External MOSFET Under Voltage Lock Out) FAULT may be triggered. This will disable the HSx outputs. This issue affects only the XUVLO fault on High-side gate drivers.

#### Work around

Clear the XUVLO upon initiating High-side gate drive sequence using one of the below work around options. After the work around

sequence, read the STAT0 and STAT1 registers to ensure the FAULT has been cleared successfully. Once the initial FAULT is cleared, the device will resume normal operation.

#### Work around #1

- 1. Monitor FAULT signal until active.

- 2. Disable Output Enable (OE) pin.

- 3. Delay up to  $400 \mu$ S.

- 4. Enable OE pin.

#### **EXAMPLE 1: WORK AROUND #1 CODE SEQUENCE**

#### Work around #2

- 1. Monitor FAULT signal until active.

- 2. Disable Output Enable (OE) pin.

- Send new configuration data to CFG0 via DE2 communication pin.

- 4. Enable OE pin.

#### **EXAMPLE 2:** WORK AROUND #2 CODE SEQUENCE

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Χ  | Χ  | Χ  |  |  |  |

#### 10. Module: MOSFET Gate Driver

When utilizing the VREG output of the MOSFET Gate Driver module to power the host processor and relying on LIN Transceiver bus activity to generate a wake-up event, a timing conflict may occur. If the MOSFET Gate Driver is in Sleep mode, the edge from the LIN\_INH output that triggers the wake event may fail to be detected by the MOSFET Gate Driver. This situation occurs if the incoming rising edge happens before the setup time required to put the MOSFET Gate Driver into Sleep mode has been satisfied. This could lead to the gate driver not waking up as expected.

#### Work around

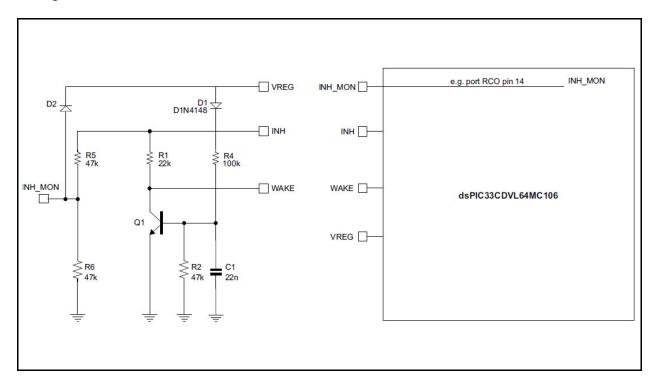

Implement the external HW circuit and SW routine below to delay any incoming rising edge on the WAKE pin ≥ t\_SLEEP + tWAIT\_SETUP.

Figure 1: Wake Extender Circuit

In conjunction with the additional hardware in Figure 1, the node labeled "INH MON" should be utilized as an input to the dsPIC DSC to monitor the state of the LIN Transceiver module to ensure the LIN device is in Sleep mode prior to sending the Sleep command to the gate driver. Since INH MON is a product of LIN INH, it will be low when LIN EN is set low. After INH MON is confirmed to be in a Low state via software, the host dsPIC DSC can proceed with putting the gate driver to sleep after tSLEEP MIN has elapsed. Figure 2 shows a block diagram of the recommended software flow. See sections Section 17.1.6, Enable Input Pin (LIN EN) and Section 17.1.7, Inhibit Output Pin (LIN INH) in the data sheet DS70005441E for details on the functionality of pins LIN EN and LIN INH for the LIN Transceiver.

Potential deadlock, separate timeout required Set LIN EN = low **Application Low Power** mode requested Wait for INH MON = low Set OE low MCP8021 Sleep mode requested via host Start timer for tSLEEPmin no Wait for expected response INH MON = from MCP8021 confirming high? Sleep mode configuration yes no Set OE and LIN\_EN high Timer Elapsed? Sleep aborted. yes Change configuration in MCP8021 CFG0, Sleep = 0 via host command Resume Application

Figure 2: Wake Extender Example Software Flow

| D1 | D2 | D3 |  |  |  |

|----|----|----|--|--|--|

| Х  | Χ  |    |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS70005441**E**):

**Note 1:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

# APPENDIX A: DOCUMENT REVISION HISTORY

Rev A Document (3/2023)

Initial version of this document; issued for revision D1.

Rev B Document (6/2023)

Added silicon issue 8 (MOSFET Gate Driver).

The I<sup>2</sup>C standard uses the terminology "Master" and "Slave". The equivalent Microchip terminology used in this document is "Host" and "Client", respectively.

Rev C Document (1/2024)

Added silicon revision D2.

Rev D Document (2/2024)

Added silicon issue 9 (MOSFET Gate Driver).

Rev E Document (6/2025)

Added silicon revision D3.

Added silicon issue 10 (MOSFET Gate Driver).

NOTES:

# **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at <a href="https://www.microchip.com/en-us/about/legalinformation/microchip-trademarks">https://www.microchip.com/en-us/about/legalinformation/microchip-trademarks</a>.

ISBN: 979-8-3371-0956-5

## **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code.

Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.