## Authentication, security for consumables and peripherals

UFDFPN8

XDFN3 X2F-PSON6

### Product status

STSAFE-L010

#### **Features**

- Authentication of consumables and peripherals

- · Usage monitoring with secure counters

- Nonvolatile memory zones with user-defined access rights

### **Security features**

- · Secure system solution

- Secure MCU

- Secure STSAFE-L010 operating system for authentication and data management

- Unique serial number on each die

- Monitoring of environmental parameters

- Protection mechanism against faults

- Protection against side-channel attacks

- Advanced asymmetric cryptography

- Advanced asymmetric cryptography relying on ECC with 256 bits key length (Edwards curves Ed25519)

#### **Hardware features**

- 32 Kbytes of secure nonvolatile memory

- Flash memory

- 10 years data retention at 25°C

- 100 000 erase/program cycles endurance at 25°C

- Supply voltage

- 1.62 V to 5.5 V

- · Operating temperature:

- − −25°C to 85°C

#### **Protocol**

- ST1Wire communication interface on one I/O

- Up to 100 kbps communication speed

- I<sup>2</sup>C communication interface

- Up to 100 kHz communication speed

- 7-bit addressing mode

#### **Packages**

- ECOPACK-compliant UFDFPN 8-lead ultrathin profile fine pitch dual flat packages

- X2F-PSON6 package (under commercial conditions)

- XDFN3 package for direct contact (under commercial conditions)

## 1 Description

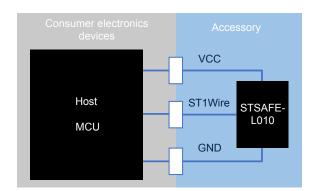

The STSAFE-L010 system-on-chip is a secure element providing authentication and data management services to a local host.

The primary function of the STSAFE-L010 is to allow the peripheral or consumable to which it is attached to be authenticated by a host for the latter to discriminate between wanted and unwanted peripheral or consumable.

The STSAFE-L010 authentication is performed by generating a digital signature over a challenge sent by the host (traceability data or zone data can be added to the challenge to authenticate it). It uses an Ed25519 signature private key that is unique for each chip and loaded at ST secure personalization center.

On top of authentication, STSAFE-L010 comes with a unique ID and offers a usage monitoring service with decrement-only counters.

A 32 Kbytes nonvolatile memory can be configured in memory zones with different access rights, so that a given zone can always be read but not modified, like manufacturing data, or can freely be modified during the life of the product, to track the way it is used for instance.

Figure 1. STSAFE-L010 connection diagram

T7550V1

DS15016 - Rev 2 page 2/42

## 1.1 Pin and signal description

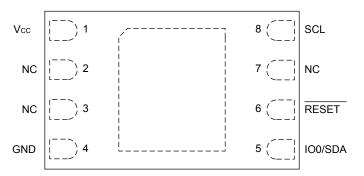

Figure 2. UFDFPN8 pinout - Top view

Figure 3. X2F-PSON6 pinout - Top view

Note: For the X2F-PSON6 package,  $V_{CC}$  and  $\overline{RESET}$  are internally wired to pin 6

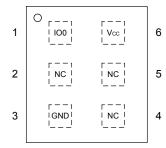

Figure 4. DFN3 pinout - Top view

Note: For the DFN3 package,  $V_{CC}$  and  $\overline{RESET}$  are internally wired to pin 3 ( $V_{CC}$ )

DS15016 - Rev 2 page 3/42

JT75516V1

| Signal          | Name                      | Description                                                                                                                                                                                                                  |

|-----------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | Power supply              | The 1.62 V to 5.5 V supply voltage is supported for powering all internal STSAFE-L010 functions.                                                                                                                             |

| GND             | Supply and signals ground | Ground reference pin for power and all I/O signals.                                                                                                                                                                          |

| RESET           | Reset                     | This input signal is used to reset STSAFE-L010. The RESET pin is pull-down by default meaning that the device is reset if connected to ground or if the pin is floating. The device is active if the RESET pin is tied high. |

| IO0/SDA         | Serial input/<br>output   | This I/O signal is used to transfer data into and out of STSAFE-L010.                                                                                                                                                        |

| SCL             | Serial clock              | Serial clock for I2C data flow synchronization.                                                                                                                                                                              |

| NC              | _                         | Not connected internally.                                                                                                                                                                                                    |

**Table 1. Signal descriptions**

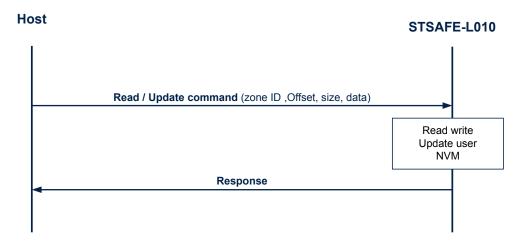

### 1.2 Data management and usage monitoring

The STSAFE-L010 includes a secure memory storage intended for storage and device usage monitoring. The user memory region consists of up to 64 partitions (zones) with one-way counter. Each zone can be individually written, read, and updated. The following sequence diagram illustrate the use of read, write, and update commands.

Figure 5. STSAFE-L010 data read/update sequence

The data partition is set during chip manufacturing and can be customized on specific demand. Access to each zone can be restricted and locked using a set of attributes.

Overview of zone attributes:

- Type: indicating whether the zone has a one-way counter or not.

- **Data segment**: the zone data excluding the one-way counter (if any). The data segment can be absent (length is 0) when the zone type indicates that there is a one-way counter. When there is no one-way counter, the data segment cannot be absent.

- One-way counter value: 3-bytes unsigned integer. Absent if zone type indicates that there is no one-way counter.

- Read access conditions (AC): in increasing order of strictness

- Always.

- Never.

- Read AC change right: A boolean indicating whether the read access conditions and read AC change right can be changed to a stricter value.

DS15016 - Rev 2 page 4/42

- Update access conditions: in increasing order of strictness

- Always.

- Never.

- **Update AC changes the right flag**: A boolean indicating whether the update access conditions, and the *update change right flag* can be updated to stricter conditions.

#### 1.2.1 Device authentication

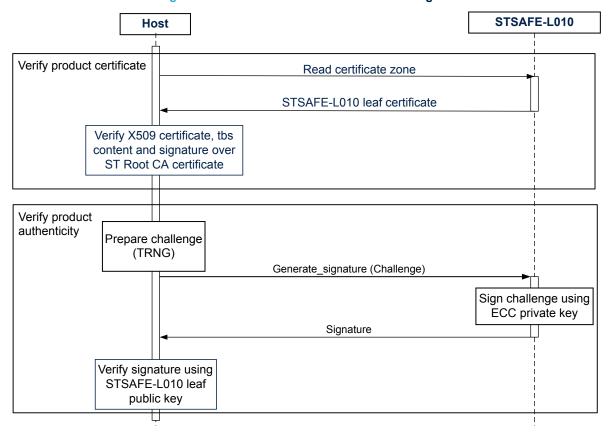

The *ECC* authentication is one of the primary services offered by the STSAFE-L010. This service provides a standardized approach to protect the brand ecosystem and the device against cloning. The device authentication relies on two factors:

- The verification of a unique identity composed of a unique *ECC* key pair and a pre-provisioned certificate in the STSAFE-L010.

- On the capabilities of the STSAFE-L010 to protect and never expose the ECC private key used during identity verification.

As illustrated in Figure 6, the pre-provisioned leaf-public key, is shared in a certificate signed by STMicroelectronics where STMicroelectronics acts as a certificate authority (*CA*). Any entity that needs to authenticate the device must first ensure the integrity and authenticity of the certificate by verifying the STSAFE-L010 certificate using a root *CA* self-signed certificate provided by STMicroelectronics. This confirms that the device certificate has been issued by STMicroelectronics and that its content is not altered. When the certificate is verified, the authenticity of the device is confirmed by sending a challenge to be signed by the device unique private key and verified using the public key shared within the device leaf-certificate.

Figure 6. STSAFE-L010 ECC authentication diagram

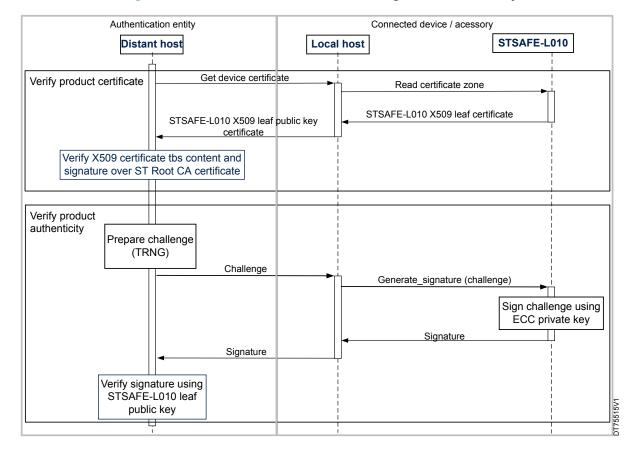

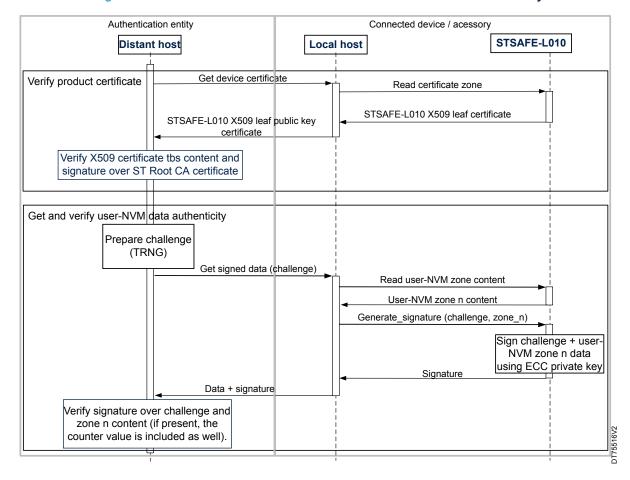

Figure 7 , illustrates the STSAFE-L010 authentication process on distant/external entity.

DS15016 - Rev 2 page 5/42

Figure 7. STSAFE-L010 ECC Authentication diagram on distant entity

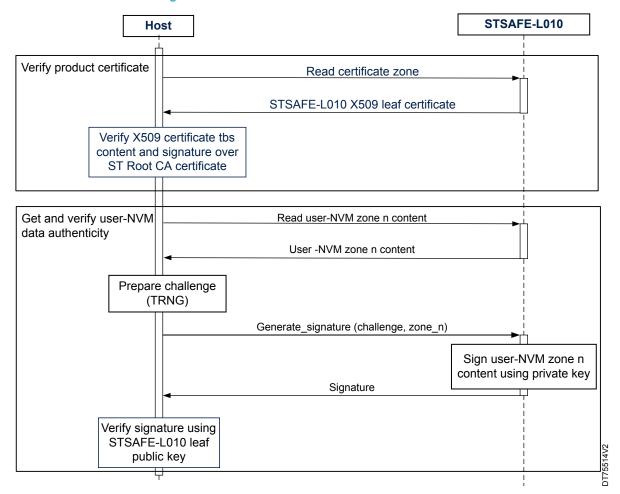

#### 1.2.2 User NVM data authentication

In complement to standard usage of the STSAFE-L010 *NVM* space as a storage area, the STSAFE-L010 offers developers with the possibility to enforce integrity and authenticity of the information coming from the secure element. It also protects against unwanted data manipulation on the bus.

As illustrated in Figure 8, the STSAFE-L010 unique key pair can be used to sign/verify the data exchanged on the communication bus from an STSAFE-L010 to the host . As for the standard authentication process, a two-step approach is to be followed to guarantee the authenticity of the data:

- Verification of the device certificate using the STMicroelectronics root CA to guarantee the leaf-public key authenticity.

- Verifying the signature generated by the STSAFE-L010 using its ECC private key over specific user-NVM zone content and the leaf certificate public-key.

DS15016 - Rev 2 page 6/42

Figure 8. STSAFE-L010 user NVM data authentication

Figure 9 illustrates the STSAFE-L010 authenticated data exchange process with distant/external entity.

DS15016 - Rev 2 page 7/42

Figure 9. STSAFE-L010 user NVM data authentication on distant/external entity

DS15016 - Rev 2 page 8/42

## 2 Ecosystem

### 2.1 Services

The STSAFE-L010 comes ready to use, with pre-provisioned keys.

STMicroelectronics offers key provisioning services for storage of customer credentials in a secure, certified environment.

### 2.2 Software

The STSAFE-L010 is provided with a host software library that can be ported to a wide range of general-purpose microcontrollers or microprocessors. This library includes a command wrapper, cryptographic library as well as authentication and NVM update services.

### 2.3 Hardware

An STM32 Nucleo-64 extension is available as a reference design, and to accelerate the development of a secure solution with STSAFE-L010. This hardware allows the developer to benefit from the full STM32 Cube/Nucleo ecosystem.

DS15016 - Rev 2 page 9/42

### 3 STSAFE-L010 command set

#### **ECHO**

Returns as response the data received as command.

#### **RESET**

Closes any on-going secure session between host and STSAFE-L010 device then reboots the STSAFE-L010.

#### **HIBERNATE**

Sets the product in low-power consumption mode. In hibernate state, the device remains powered but loses its session context. Exiting from hibernate state can be performed by triggering the Reset pin or toggling data I/O. The device restart is equivalent to a restart after a reset or power on reset (POR).

#### DECREMENT

Decrements the one-way counter in a counter zone. When the counter reaches zero, the command is refused. In complement to the counter, the command can update the associated data segment with provided data.

It is also possible to change the access conditions (AC) to the counter/segment to a stricter value than the current one.

#### **READ**

Used to read data from a data partition zone. It reads the data starting from the specified offset within the zone and with the requested length. It checks the access conditions and only return the data starting from the specified offset up to the zone boundary.

This command can also be used to change the read access conditions of the zone to a stricter value.

#### **UPDATE**

Used to update data in a zone. It checks if the written data exceeds the zone boundary. When this occurs, it does not perform the operation.

This command can also be used to change the update access conditions of the zone to a stricter value; for example, when writing data only once. This command is applicable only on User-NVM zones without counter. For zone with counter the update is done through dedicated decrement command.

#### **GENERATE SIGNATURE**

This command generates an EdDSA signature over challenge, with the following optional data to sign:

- User NVM zone content

- STSAFE-L010 traceability information

### **REPEAT RESPONSE**

Request STSAFE-L010 device to send again the last response frame.

#### **PUT DATA**

Used to modify specific device configuration attributes.

#### **GET DATA**

Used to get status on device configuration attributes.

DS15016 - Rev 2 page 10/42

### 4 Communication interfaces

The STSAFE-L010 device supports ST1Wire and *I*<sup>2</sup>C communication interface. It acts as target on all the supported interfaces.

### 4.1 ST1Wire interface

The ST1Wire protocol is a custom protocol developed by STMicroelectronics to reduce the number of contacts required to perform bidirectional point to point communication between an applicative system (host) and a secure element (*SE*) device from STMicroelectronics.

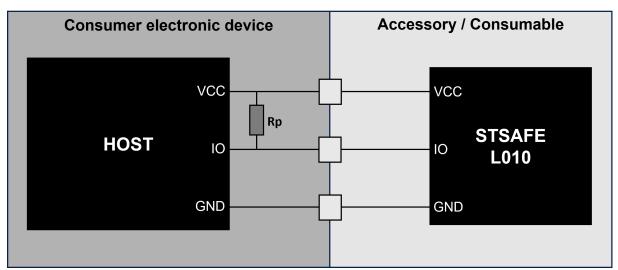

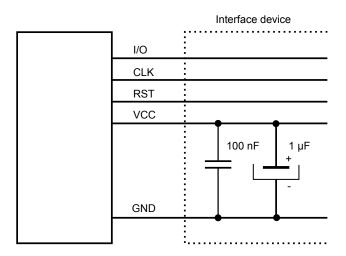

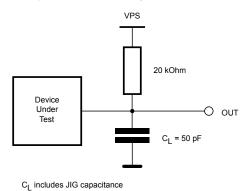

The hardware implementation of the ST1Wire bus is illustrated below:

Figure 10. ST1Wire 3-contact implementation

The ST1Wire protocol is based on a single serial data line that carries information between a single master device (host) and one STSAFE-L010 device.

The ST1Wire protocol is a half-duplex protocol where the host can communicate with only one STSAFE-L010 device and in only one direction at a time.

. The host and the STSAFE-L010 are alternatively sender and receiver depending on the type of Frame to be exchanged on the bus. Specific bus arbitration based on ST1Wire Line steady state detection and byte acknowledge requires both master and slave communication I/O to be configured in open drain mode .

The bus pull-up resistor (Rp) must be selected, based on the I/Os electrical characteristics of master device and STSAFE-L010 devices. The following conditions must be met for Rp value selection:

$$VIL_{max\_host} > VCC^* \frac{Ron_{host}}{Rp + Ron_{host}}$$

$$VIL_{max\_stsafe\_lo10} > VCC^* \frac{Rons_{stsafe\_lo10}}{Rp + Ron_{stsafe\_lo10}}$$

$$IOL_{max\_host} > \frac{VCC}{Rp + Ron_{host}}$$

$$IOL_{max\_stsafe\_lo10} > \frac{VCC}{Rp + Ron_{host}}$$

To be compliant with the ST1Wire electrical requirements, the host must use an open-drain I/O to interface with the bus. This allows the bus to be in two states:

DS15016 - Rev 2 page 11/42

- **Idle state**: Line is at high level V<sub>ST1Wire\_H</sub> for more than T<sub>cyc\_HOST\_min</sub>. Neither host nor any STSAFE-L010 devices drive the line. There is no communication on the bus.

- Communicating state: Line is driven alternatively by the host and the STSAFE-L010 device for frame exchange. During frame exchange both entities act alternatively as transmitter and receiver on the line. Transmitter and receiver cannot hold the line low for a time period higher than T<sub>cyc\_HOST\_max</sub>. Except when the host sends an ST1Wire start of frame (SOF). Refer to Section 4.1.3: Frame protocol description for more details

Note: For voltage and timings, refer to the Section 5.8: ST1Wire electrical characteristics.

#### 4.1.1 Bit-transfer

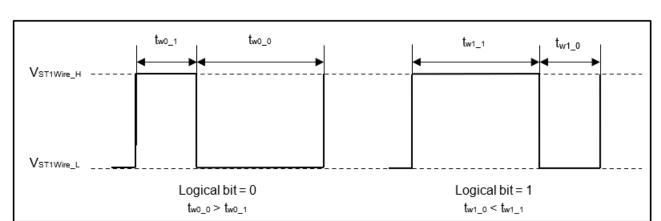

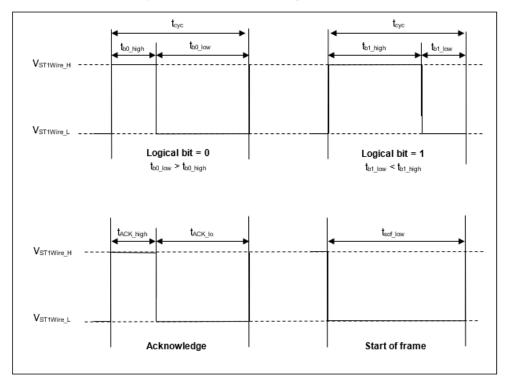

The ST1Wire protocol encodes bits by applying pulse width modulation (PWM) of the ST1Wire data line. See the bit encoding representation in Figure 2.

Figure 11. Bit encoding

Logical bits are encoded with a  $V_{ST1Wire\_H}$  pulse, followed by a  $V_{ST1Wire\_L}$  pulse. The table below shows the encoding rules.

Note: For information on allowed durations, refer to Section 5.8: ST1Wire electrical characteristics.

Logical value

Condition

Comment

0

$t_{W0_0} > t_{W0_1}$ .

duration of  $V_{ST1Wire_L} >$  duration of  $V_{ST1Wire_H}$

1

$t_{W1_0} < t_{W1_1}$ .

duration of  $V_{ST1Wire_H}$

Table 2. Logical bit encoding

The  $V_{ST1Wire\_H}$  and  $V_{ST1Wire\_L}$  depends on physical bus implementation and characteristics of both STSAFE-L010 and host I/O.

### 4.1.2 Byte transfer

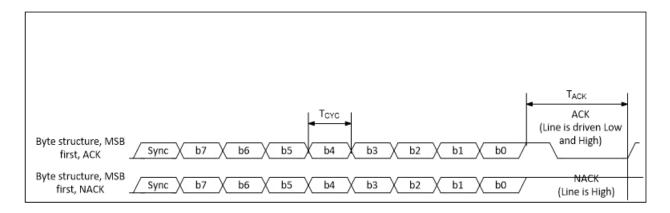

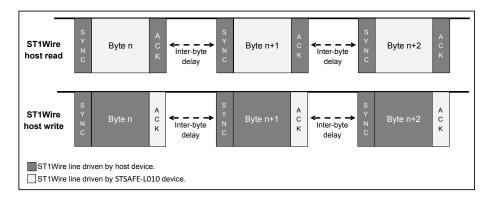

The ST1Wire interface transfer unit is the byte. Bytes are encapsulated in a data structure containing three parts, as illustrated in the image below.

DS15016 - Rev 2 page 12/42

Figure 12. Byte structure

- Sync: First symbol of the byte transfer. The sync symbol is always generated by the ST1Wire host device and consists in a low level (V<sub>ST1Wire\_L</sub>) pulse. As before the sync symbol, the ST1Wire is in idle state at (V<sub>ST1Wire\_H</sub>), the implementation of the sync symbol can consist in generating a bit with a logic "1".

- **Byte**: Contains the byte to transfer. Bits in the byte are transferred in series. After the last bit has been sent to the interface, the transmitter releases the interface, which is set high. It then polls the line for a reply which is called the **ACK**.

- ACK: A byte acknowledge symbol generated by the receiver at each byte transfer. This symbol informs the transmitter whether or not the current byte has been received correctly and if the receiver is ready to receive the next byte.

- ACK: A high pulse followed by a low pulse. The ST1Wire line is driven high (V<sub>ST1Wire\_H</sub>), and then low (V<sub>ST1Wire\_L</sub>) and then the ST1Wire line is released again to (V<sub>ST1Wire\_H</sub>). A new byte can then be immediately released by the transmitter. As before the back symbol, the ST1Wire is in idle mode at (V<sub>ST1Wire\_H</sub>), the implementation of the ACK symbol can consist in generating a logic "0" bit.

- NACK = ST1Wire line stays at ST1Wire\_H level for more than T<sub>ACK</sub>.

The ACK symbol duration ( $T_{ACK}$ ) is bounded to [ $2xT_{CYC}$ ]. The transmitter detects that a NACK has occurred when  $T_{ACK}$  has expired, and no "low" pulse of the appropriate length has been received. If the receiver NACKs a byte, the transfer is aborted. The bus is in idle state and the master must repeat the transfer from the beginning.

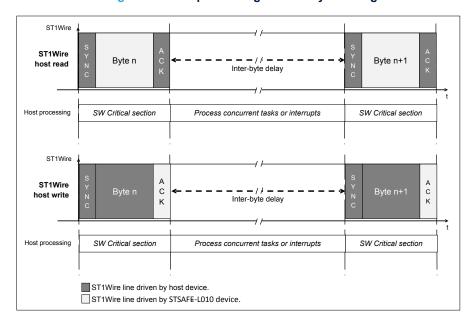

The ST1Wire protocol supports inter-byte delay as illustrated in the figure below. The inter-byte delay slows down the communication between the master and the STSAFE-L010 device. The inter-byte duration must be managed by the ST1Wire master when generating the Sync bit for each byte to be read or written. During the inter-byte delay, the line must be kept at  $V_{ST1Wire\ H}$ .

Figure 13. ST1Wire inter-byte delay

T755021/1

DS15016 - Rev 2 page 13/42

On host systems running specific *OS* or *RTOS*, it is recommended to use critical software section during byte transfer. Critical software sections ensure correct byte read timings and byte write timings on the ST1Wire bus. During a critical section, the host must disable all interrupt and potential *OS/RTOS* concurrent task management. As represented in the figure below. To minimize the impact of the critical section at system/host level, the interbyte delay allows the host to process interrupts and concurrent *OS* tasks between each ST1Wire byte transfer.

Figure 14. Host processing vs inter-byte management

DT75505V1

#### 4.1.3 Frame protocol description

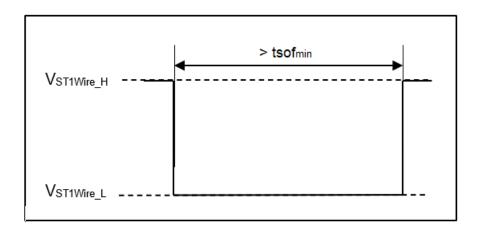

When the ST1Wire bus is in the idle state, the host can initiate the communication by sending an ST1Wire SOF followed by either a command frame (CF) or a response frame.

DS15016 - Rev 2 page 14/42

Figure 15. ST1Wire start of frame (SOF)

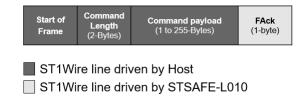

Figure 16. STSAFE-L010 ST1Wire command frame

#### Important:

A command frame must always be followed by a response frame. If an error is reported on the bus, the whole command plus responses which were exchanged must be repeated.

An ST1Wire command frame is always composed of the following elements.

- Start of frame (SOF): V<sub>ST1Wire</sub> line is pulled low for a minimum duration t<sub>SOF min</sub> duration.

- **Command length (2-byte):** Defines the command type and payload size. The command frame length must always be superior to 0x0000.

- Command payload (n-byte): Command data with content aligned with STSAFE-L010 device user manual

- Frame acknowledge (FAck) (1-byte):Both command and status frames must be acknowledged (ACK) by the slave using an FAck byte equal to 0x20. Other values are considered as a NACK. In the case the slave NACK the frame, the ST1Wire is moved into Idle state.

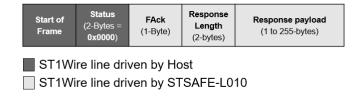

Figure 17. STSAFE-L010 ST1Wire response frame

An ST1Wire response frame is always composed of the following elements.

- Start of frame (SOF): VST1Wire line pulled LOW for a minimum duration t<sub>SOF</sub> min duration.

- Status byte (2-byte): must be equal to 0x0000. This byte notifies the STSAFE-L010 device that a

response to the previous command is requested.

DS15016 - Rev 2 page 15/42

- Frame acknowledge (FAck) (1-byte):Status frames acknowledgement by the slave using an FAck byte equal to 0x20. Other values are considered as a NACK. In the case where the slave NACKs the frame, the ST1Wire is moved into idle state.

- Response length (2-byte):length of the response payload to be sent by the STSAFE-L010 device.

- Response payload (n-byte):Response data with content aligned with STSAFE-L010 device User Manual

DS15016 - Rev 2 page 16/42

### 5 AC/DC characteristics

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristic tables that follow are derived from tests performed under the measurement conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

### 5.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter                                                                  | Value                         | Unit |

|------------------|----------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                                             | -0.3 to 6.5                   | V    |

| V <sub>IO</sub>  | Input or output voltage relative to ground                                 | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| T <sub>A</sub>   | Ambient operating temperature                                              | -25 to +85                    | °C   |

| T <sub>STG</sub> | Storage temperature (Refer to package specification)                       | -65 to +150                   | °C   |

| V <sub>ESD</sub> | Electrostatic discharge voltage according to JESD22-A114, Human Body Model | 4000                          | V    |

Note:

Stresses listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 5.2 Recommended power supply filtering

Supply filtering is recommended as shown in Figure 18.

Figure 18. Recommended filtering capacitors on VCC

Table 4. Maximum V<sub>CC</sub> rising slope

| Symbol           | Parameter                            | Value | Unit |

|------------------|--------------------------------------|-------|------|

| S <sub>VCC</sub> | Maximum V <sub>CC</sub> rising slope | 5     | V/µs |

DS15016 - Rev 2 page 17/42

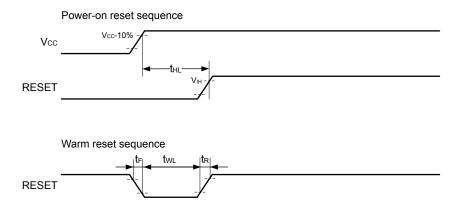

### 5.3 AC characteristics

$T_A = -25~^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , unless otherwise specified.

Table 5. 1.8 V and 3 V AC characteristics

| Symbol                               | Parameter                                                    | Condition                   | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------------------------------------------------------------|-----------------------------|------|------|------|------|

| t <sub>WLReset</sub> <sup>(1)</sup>  | Pulse width for reset                                        | -                           | 5    | -    | -    | μs   |

| t <sub>HLReset</sub>                 | Minimum time for reset active after power-up                 | -                           | 80   | -    | -    | μs   |

| t <sub>BOOT</sub>                    | Delay between V <sub>CC</sub> reaching the POR threshold and | -                           | _    | 10   | 20   | ms   |

| 48001                                | STSAFE-L010 ready to receive first command                   | -                           |      | 10   | 20   | 1113 |

| t <sub>R</sub> , t <sub>FReset</sub> | Reset rise and fall time                                     | -                           | -    | -    | 1    | μs   |

| t <sub>R</sub> , t <sub>F</sub> I/O  | I/O rise and fall time                                       | Load capacitance<br>= 30 pF | -    | -    | 1    | μs   |

<sup>1.</sup> Anylow pulse (from `1' to `0', then `0' to `1') shorter than 100 ns is ignored. Reset is not guaranteed for pulses between 100 ns and 500 ns; reset is guaranteed for pulses longer than 500 ns.

### **5.4** DC characteristics

$T_A = -25$  °C to 85 °C, unless otherwise specified.

Note: The voltage on all inputs or outputs must not exceed  $V_{CC}$  + 0.3 V or be less than -0.3 V.

**Table 6. DC characteristics**

| Symbol          | Parameter                                       | Condition | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------------------------|-----------|------|------|------|------|

| POR             | Power-on-reset voltage                          | -         | -    | 1.45 | 1.61 | V    |

| V <sub>cc</sub> | Standard operating voltage (1.8 V to 5 V ± 10%) | -         | 1.62 | -    | 5.5  | V    |

Table 7. 1.8 V DC characteristics (V<sub>CC</sub> = 1.8 V ±10%)

| Symbol           | Parameter                       | Condition                                   | Min.                  | Тур. | Max.                   | Unit |

|------------------|---------------------------------|---------------------------------------------|-----------------------|------|------------------------|------|

| V <sub>IL</sub>  | Input low voltage (RESET, I/O)  | -                                           | 0                     | -    | 0.2 × V <sub>CC</sub>  | V    |

| V <sub>IH</sub>  | Input high voltage (RESET, I/O) | -                                           | 0.7 × V <sub>CC</sub> | -    | V <sub>CC</sub>        | V    |

| I <sub>I</sub> L | Input low current (I/O)         | 0 < V <sub>IL</sub> < 0.2 × V <sub>CC</sub> | -100                  | -    | 1                      | μΑ   |

| 'IL              | Input low current (RESET)       | 0 < V <sub>IL</sub> < 0.2 × V <sub>CC</sub> | -1                    | -    | 10                     | μΑ   |

| I <sub>IH</sub>  | Input high current (I/O)        | $0.7 \times V_{CC} < V_{IH} < V_{CC}$       | -100                  | -    | 1                      | μΑ   |

| I <sub>IH</sub>  | Input high current (RESET)      | $0.7 \times V_{CC} < V_{IH} < V_{CC}$       | -1                    | -    | 10                     | μΑ   |

| V <sub>OL</sub>  | Output low voltage (I/O)        | I <sub>OLMAX</sub> = 1 mA                   | 0                     | -    | 0.15 × V <sub>CC</sub> | V    |

DS15016 - Rev 2 page 18/42

Table 8. 3 V DC characteristics ( $V_{CC} = 3 \text{ V} \pm 10\%$ )

| Symbol          | Parameter                       | Condition                                   | Min.                  | Тур. | Max.                   | Unit |

|-----------------|---------------------------------|---------------------------------------------|-----------------------|------|------------------------|------|

| V <sub>IL</sub> | Input low voltage (RESET, I/O)  | -                                           | 0                     | -    | 0.2 × V <sub>CC</sub>  | V    |

| V <sub>IH</sub> | Input high voltage (RESET, I/O) | -                                           | 0.7 × V <sub>CC</sub> | -    | V <sub>CC</sub>        | V    |

|                 | Input low current (I/O)         | 0 < V <sub>IL</sub> < 0.2 × V <sub>CC</sub> | -200                  | -    | 1                      | μΑ   |

| IIL             | Input low current (RESET)       | 0 < V <sub>IL</sub> < 0.2 × V <sub>CC</sub> | -1                    | -    | 10                     | μA   |

|                 | Input high current (I/O)        | $0.7 \times V_{CC} < V_{IH} < V_{CC}$       | -200                  | -    | 1                      | μA   |

| IIH             | Input high current (RESET)      | $0.7 \times V_{CC} < V_{IH} < V_{CC}$       | -1                    | -    | 10                     | μA   |

| V <sub>OL</sub> | Output low voltage (I/O)        | I <sub>OLMAX</sub> = 4 mA                   | 0                     | -    | 0.15 x V <sub>CC</sub> | V    |

### 5.5 Performance and power consumption characteristics

$T_A$  = -25 °C to 85 °C, unless otherwise specified.

Table 9. 1.8 V and 3 V power consumption characteristics

| Symbol                   | Parameter                                                | Conditions | Тур. | Max. | Unit |

|--------------------------|----------------------------------------------------------|------------|------|------|------|

| ICCPROC                  | Supply current when executing instructions stored in ROM | -          | 1.3  | 4    | mA   |

| I <sub>CCHibernate</sub> | Supply current in hibernate mode                         | -          | 1    | 2    | μA   |

| I <sub>CCReset</sub>     | Supply current in reset                                  | -          | 0.2  | 0.5  | mA   |

### 5.6 Timings

Figure 19. Power-on and warm reset sequences

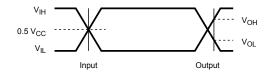

### 5.7 AC measurement conditions

$T_A$  = -25 °C to 85 °C, f = 1 MHz, unless otherwise specified.

Table 10. AC measurement conditions

| Parameter                 | Value                              |

|---------------------------|------------------------------------|

| Input rise and fall times | 10 ns (max.)                       |

| Input pulse voltage       | V <sub>IL</sub> to V <sub>IH</sub> |

DS15016 - Rev 2 page 19/42

| Parameter                       | Value                              |  |

|---------------------------------|------------------------------------|--|

| Input timing reference voltage  | 0.5 × V <sub>CC</sub>              |  |

| Output timing reference voltage | V <sub>OL</sub> to V <sub>OH</sub> |  |

Figure 20. AC testing input/output waveforms

Figure 21. AC testing load circuit

Table 11. Capacitance on IO pad

| Symbol           | Parameter          | Min. | Max. | Unit |

|------------------|--------------------|------|------|------|

| C <sub>IN</sub>  | Input capacitance  | -    | 30   | pF   |

| C <sub>OUT</sub> | Output capacitance | -    | 30   | pF   |

### 5.8 ST1Wire electrical characteristics

The following tables give the electrical characteristic of the ST1Wire protocol.

Table 12. ST1Wire 3-contacts DC characteristics (1.62 to 5.5 V; -25°C to 85°C; CL = 20 pF; Pull-up = 1.375  $k\Omega$ )

| Symbol                       | Description                                       | Min. | Max. | Unit |

|------------------------------|---------------------------------------------------|------|------|------|

| t <sub>b0_low_</sub> STSAFE  | STSAFE-L010 logical '0' bit low pulse duration    | 4.9  | 7.4  | μs   |

| t <sub>b0_high_</sub> STSAFE | STSAFE-L010 logical '0' bit high pulse duration   | 1.7  | 3.5  | μs   |

| t <sub>b1_low_STSAFE</sub>   | STSAFE-L010 logical '1' low pulse duration        | 1.8  | 3.7  | μs   |

| t <sub>b1_high_</sub> STSAFE | STSAFE-L010 logical '1' bit high pulse duration   | 5.3  | 6.6  | μs   |

| tack_high_stsafe             | STSAFE-L010 byte acknowledge high pulse duration. | 2    | 3.9  | μs   |

| tack_low_stsafe              | STSAFE-L010 byte acknowledge low pulse duration.  | 4.1  | 5.2  | μs   |

| t <sub>cyc_HOST</sub>        | HOST bit duration                                 | 10   | 200  | μs   |

DS15016 - Rev 2 page 20/42

| Symbol                            | Description                                                              | Min. | Max. | Unit                  |

|-----------------------------------|--------------------------------------------------------------------------|------|------|-----------------------|

| t <sub>b0_low_</sub> HOST         | HOST logical '0' bit low pulse duration                                  | 0.6  | 0.75 | t <sub>cyc_HOST</sub> |

| t <sub>b0_high_</sub> HOST        | HOST logical '0' bit high pulse duration                                 | 0.25 | 0.4  | t <sub>cyc_HOST</sub> |

| t <sub>b1_low_</sub> HOST         | HOST logical '1' low pulse duration                                      | 0.25 | 0.4  | t <sub>cyc_HOST</sub> |

| t <sub>b1_high_</sub> HOST        | HOST logical '1' bit high pulse duration                                 | 0.6  | 0.75 | t <sub>cyc_HOST</sub> |

| t <sub>ACK_high_HOST</sub>        | HOST byte acknowledge high pulse duration.                               | 0.1  | -    | us                    |

| t <sub>ACK_low_</sub> HOST        | HOST byte acknowledge low pulse duration.                                | 0.5  | 20   | μs                    |

| t <sub>sof_low_</sub> HOST        | HOST Start of frame low pulse duration                                   | 37   | -    | μs                    |

| t <sub>sync_low_HOST</sub>        | HOST sync bit low pulse duration                                         | 5.1  | 11.9 | μs                    |

| t <sub>inter-byte</sub>           | HOST sync bit high pulse duration                                        | 3.1  | -    | μs                    |

| <sup>t</sup> SoF_low_to_sync_high | Delay between rising edge of SoF and beginning of t <sub>sync_high</sub> | 3.6  | 5    | μs                    |

Figure 22. ST1Wire DC timings description

DS15016 - Rev 2 page 21/42

## 6 Package information

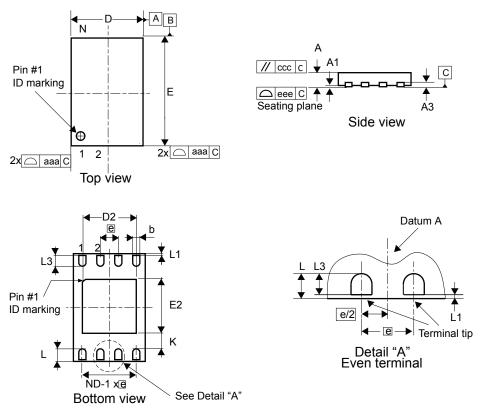

### 6.1 UFDFPN8 package specification

This section provides specific information concerning the  $2 \times 3 \times 0.50$  mm, 8 lead, ultra thin, fine-pitch, dual flat, no-lead package (UFDFPN8).

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

Figure 23. UFDFPN8 package

DS15016 - Rev 2 page 22/42

### 6.1.1 UFDFPN8 package information

Figure 24. UFDFPN8 - 8-lead, 2 × 3 mm, 0.5 mm pitch ultra thin profile fine pitch dual flat package outline

ZWb\_ME\_V1

- 1. Maximum package warpage is 0.05 mm.

- 2. Exposed copper is not systematic and can appear partially or totally according to the cross-section.

- 3. Drawing is not to scale.

Table 13. UFDFPN8 - 8-lead, 2 × 3 mm, 0.5 mm pitch ultra thin profile fine pitch dual flat package mechanical data

| Symbol | millimeter | s                      |      | inches <sup>(1)</sup> |                          |       |  |

|--------|------------|------------------------|------|-----------------------|--------------------------|-------|--|

| Symbol | Min.       | Тур.                   | Max. | Min.                  | Тур.                     | Max.  |  |

| Α      | 0.45       | 0.55                   | 0.60 | 0.018                 | 0.022                    | 0.024 |  |

| A1     | 0.00       | 0.02                   | 0.05 | 0.000                 | 0.001                    | 0.002 |  |

| b (2)  | 0.20       | 0.25                   | 0.30 | 0.008                 | 0.010                    | 0.012 |  |

| D      | 1.90       | 2.0                    | 2.10 | 0.075                 | 0.079                    | 0.083 |  |

| D2     | 1.20       | -                      | 1.60 | 0.047                 | -                        | 0.063 |  |

| E      | 2.90       | 3.00                   | 3.10 | 0.114                 | 0.118                    | 0.122 |  |

| E2     | 1.20       | -                      | 1.60 | 0.047                 | -                        | 0.063 |  |

| е      | -          | 0.5 BSC <sup>(3)</sup> | -    | -                     | 0.020 BSC <sup>(3)</sup> | -     |  |

| K      | 0.30       | -                      | -    | 0.012                 | -                        | -     |  |

| L      | 0.30       | -                      | 0.50 | 0.012                 | -                        | 0.020 |  |

| L1     | -          | -                      | 0.15 | -                     | -                        | 0.006 |  |

DS15016 - Rev 2 page 23/42

| Symbol             | millimet | millimeters |      |       | inches <sup>(1)</sup> |       |  |

|--------------------|----------|-------------|------|-------|-----------------------|-------|--|

| Symbol             | Min.     | Тур.        | Max. | Min.  | Тур.                  | Max.  |  |

| L3                 | 0.30     | -           | -    | 0.012 | -                     | -     |  |

| aaa                | -        | -           | 0.15 | -     | -                     | 0.006 |  |

| bbb                | -        | -           | 0.10 | -     | -                     | 0.004 |  |

| ccc                | -        | -           | 0.10 | -     | -                     | 0.004 |  |

| ddd                | -        | -           | 0.05 | -     | -                     | 0.002 |  |

| eee <sup>(4)</sup> | -        | -           | 0.08 | -     | -                     | 0.003 |  |

- 1. Values in inches are converted from mm and rounded to 3 decimal digits.

- 2. Dimension b applies to plated terminal and is measured between 0.15 and 0.30 mm from the terminal tip.

- 3. Basic spacing between centers.

- 4. Applied for exposed die paddle and terminals. Excludes embedding part of exposed die paddle from measuring.

### 6.1.2 Recommended footprint information for UFDFPN8 (landing pattern)

The figure below describes ST recommendations in terms of the printed circuit board landing pattern for the UFDFPN8  $2 \times 3$  mm package.

Figure 25. Recommended footprint for UFDFPN8

#### 1. All dimensions are in millimeters.

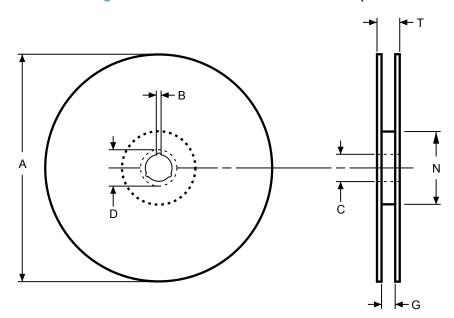

### 6.1.3 UFDFPN8 tape and reel packing

Surface-mount packages can be supplied with tape and reel packing. The reels have a 13" typical diameter. They contain 5000 devices each.

Reels are in plastic, either antistatic or conductive, with a black conductive cavity tape. The cover tape is transparent antistatic or conductive.

The devices are positioned in the cavities with the identifying pin (normally Pin "1") on the same side as the sprocket holes in the tape.

The STMicroelectronics Tape & Reel specifications are compliant to the EIA 481-A standard specification.

Table 14. UFDFPN8 package on tape and reel

| Package          | Description           | Tape width | Tape pitch | Reel diameter | Quantity per reel |

|------------------|-----------------------|------------|------------|---------------|-------------------|

| UFDFPN8 2 × 3 mm | Flat package, no lead | 8 mm       | 4 mm       | 13 in.        | 5000              |

DS15016 - Rev 2 page 24/42

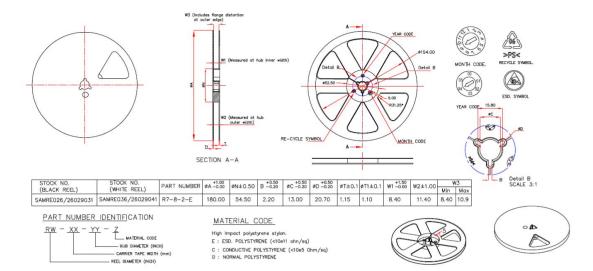

Figure 26. Dimensions of a 13" reel for 8 mm tape

Table 15. UFDFPN8 reel dimensions

| Reel size | Tape size | A Max. | B Min. | С        | D Min. | G Max. | N Min. | T Max. | Unit |

|-----------|-----------|--------|--------|----------|--------|--------|--------|--------|------|

| 13"       | 8         | 330    | 1.5    | 13 ±0.25 | 20.2   | 8.6    | 100    | 14.4   | mm   |

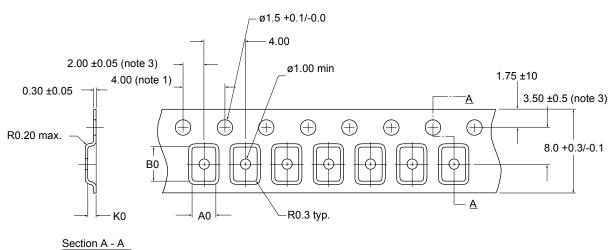

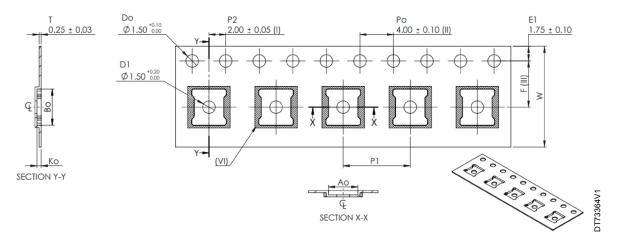

Figure 27. Embossed carrier tape for UFDFPN8

- 1. Cumulative tolerance of ten sprocket hole pitches: ±0.2.

- 2. Camber in compliance with EIA 481.

- 3. Pocket position relative to sprocket hole measured as the true position of the pocket, not pocket hole.

- 4. All dimensions are in millimeters.

- 5. Unless otherwise noted, tolerances are ±0.02 for one decimal place and ±0.10 for two decimal places.

- 6. A0 = 2.30; Bo = 3.30; K0 = 0.75.

DS15016 - Rev 2 page 25/42

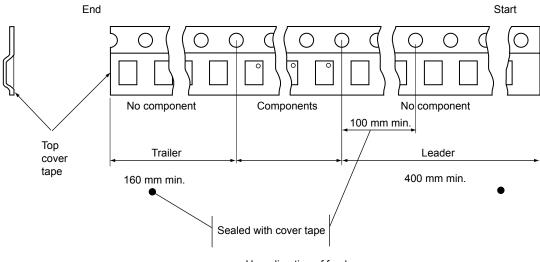

Figure 28. Leader and trailer for UFDFPN8

User direction of feed

Die orientation into the tape - Leader and trailer

DS15016 - Rev 2 page 26/42

B0ML\_XDFN\_4x3-2x0-35\_3L\_MEV1

## 6.2 DFN3 package specification

### 6.2.1 XDFN3 package information

XDFN3 is an three-terminal, 4 × 3.2 mm, extremely thin dual flat no lead package.

E1 E

A3 A1

Figure 29. XDFN3 package outline

- 1. Drawing is not to scale.

- 2. This stands for C0.15

DS15016 - Rev 2 page 27/42

| Table 16  | XDFN3    | nackage | mechanical    | data |

|-----------|----------|---------|---------------|------|

| Table 10. | . ADI NJ | Dackade | IIICCIIaiiica | uata |

| Symbol             |                          | Millimeters <sup>(1)(2)</sup> |      |  |

|--------------------|--------------------------|-------------------------------|------|--|

| Symbol             | Min.                     | Тур.                          | Max. |  |

| А                  | -                        | -                             | 0.38 |  |

| A1                 | -                        | -                             | 0.05 |  |

| A3                 |                          | 0.10 REF                      |      |  |

| D                  | 3.90                     | 4.00                          | 4.10 |  |

| D1                 | 1.05                     | 1.10                          | 1.15 |  |

| E                  | 3.10                     | 3.20                          | 3.30 |  |

| E1                 | 2.80                     | 2.85                          | 2.90 |  |

| е                  | 1.240 BSC <sup>(3)</sup> |                               |      |  |

| F                  |                          | 0.21 REF                      |      |  |

| f                  | 0.14 REF                 |                               |      |  |

| G                  | 0.175 REF                |                               |      |  |

| N (number of pins) | 3(4)                     |                               |      |  |

- 1. Dimensioning and tolerancing schemes according to ASME Y14.5M-1994.

- 2. All values are in millimeters rounded to the second decimal except for N.

- 3. Basic space between centers.

- 4. Total number of terminals

### 6.2.2 XDFN3 4 x 3.2 x 0.35 tape and reel packing

Surface-mount packages can be supplied with tape and reel packing. The reels have a 13" typical diameter. They contain 5000 devices each.

Reels are in plastic, either antistatic or conductive, with a black conductive cavity tape. The cover tape is transparent antistatic or conductive.

The devices are positioned in the cavities with the identifying pin (normally pin "1") on the same side as the sprocket holes in the tape.

The STMicroelectronics tape and reel specifications are compliant with the EIA 481-A standard specification.

Table 17. XDFN3 4 x 3.2 x 0.35 packages on tape and reel

| Package | Description   | Tape width | Tape pitch  | Reel diameter | Quantity per reel |

|---------|---------------|------------|-------------|---------------|-------------------|

| B0ML    | XDFN 4×3.2 3L | 12 mm      | 8.00 ± 0.10 | 13"           | 5000 units        |

DS15016 - Rev 2 page 28/42

A C

Figure 30. XDFN3 4 x 3.2 x 0.35 reel diagram

Table 18. XDFN3 4 x 3.2 x 0.35 reel dimensions

| Reel size  | Tape size | A Max. | B Min.  | С                    | D Min.   | G Max.   | N Min. | T Max.   | Unit            |

|------------|-----------|--------|---------|----------------------|----------|----------|--------|----------|-----------------|

| 13" Hub 7" | 12 mm     | 332 mm | 1.50 mm | 13 + 0.50 / -0.20 mm | 20.20 mm | 14.40 mm | 176 mm | 18.40 mm | 5000 units/reel |

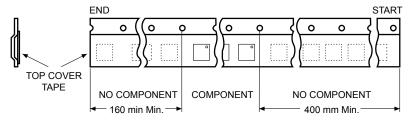

Figure 31. XDFN3 4 x 3.2 x 0.35 Leader and trailer

USER DIRECTION OF FEED

DS15016 - Rev 2 page 29/42

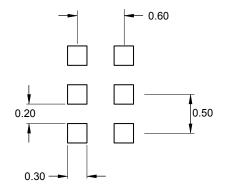

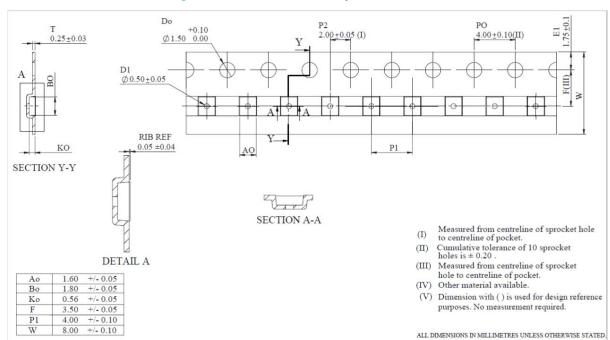

Figure 32. Embossed carrier tape for XDFN3 4 x 3.2 x 0.35

- 1. Measured from center line of sprocket hole to center line of pocket (I)

- 2. Cumulative tolerance of 10 sprocket hole pitch =  $\pm$  0.20 (II).

- 3. Measured from center line of sprocket hole to center line of pocket (III)

- 4. Other materials available

- 5. Dimension with () is used for design reference purposes. No measurement required

- 6. Shinning imprint (It occurs in all pockets) (VI)

- 7. SPOT patented by C\_PAK

Note: The roman numerals in brackets refer to specific notes in Figure 32

Table 19. Carrier tape dimensions for XDFN3 4 x 3.2 x 0.35

| Package                 | A0          | В0          | K0          | F           | P1          | W                   | Unit |

|-------------------------|-------------|-------------|-------------|-------------|-------------|---------------------|------|

| XDFN3 4 x 3.2 x 0.35 mm | 3.50 ± 0.10 | 4.30 ± 0.10 | 0.50 ± 0.10 | 5.50 ± 0.05 | 8.00 ± 0.10 | 12.00 +0.30 / -0.10 | mm   |

### 6.3 GQFN6 package specification

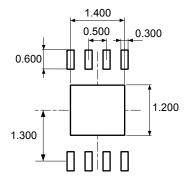

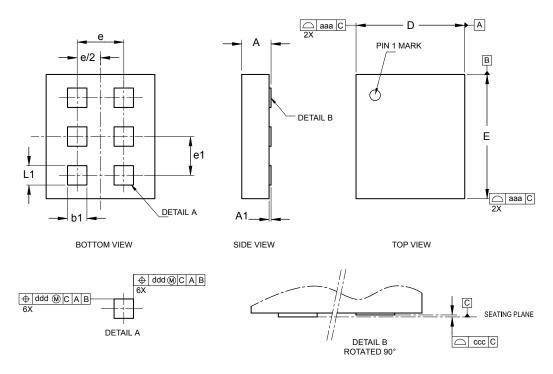

### **6.3.1** X2F-PSON6 package information (B0G5)

This X2F-PSON is a 6-lead, 1.4 x 1.6 mm, plastic ultra and super thin small outline, non-leaded package.

DS15016 - Rev 2 page 30/42

Figure 33. X2F-PSON6 - Outline

1. Drawing is not to scale.

DS15016 - Rev 2 page 31/42

| Cumbal           | millimeters |          |      | inches <sup>(1)</sup> |           |       |  |  |

|------------------|-------------|----------|------|-----------------------|-----------|-------|--|--|

| Symbol           | Min         | Тур      | Max  | Min                   | Тур       | Max   |  |  |

| A <sup>(2)</sup> | 0.35        | -        | 0.40 | 0.014                 | -         | 0.016 |  |  |

| A1               | 0           | -        | 0.05 | 0                     | -         | 0.002 |  |  |

| L1               | 0.20        | 0.25     | 0.30 | 0.007                 | 0.009     | 0.012 |  |  |

| b1               | 0.20        | 0.25     | 0.30 | 0.007                 | 0.009     | 0.012 |  |  |

| D                |             | 1.40 BSC |      |                       | 0.055 BSC |       |  |  |

| E                |             | 1.6 BSC  |      | 0.063 BSC             |           |       |  |  |

| е                |             | 0.60 BSC |      | 0.024 BSC             |           |       |  |  |

| e1               |             | 0.50 BSC |      | 0.020 BSC             |           |       |  |  |

| N <sup>(3)</sup> |             |          |      | 6                     |           |       |  |  |

| aaa              | -           | 0.05     | -    | -                     | 0.002     | -     |  |  |

| ccc              | -           | 0.03     | -    | -                     | 0.001     | -     |  |  |

| ddd              | -           | 0.10     | -    | -                     | 0.004     | -     |  |  |

Table 20, X2F-PSON - Mechanical data

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- 2. X2F-PSON stands for plastic ultra and super thin small outline, non-leaded package family

- Super thin profile:  $0.30 \text{ mm} < A \le 0.40 \text{ mm}$

- 3. Total number of terminals

Figure 34. X2F-PSON6 - Footprint example

1. Dimensions are express in mm.

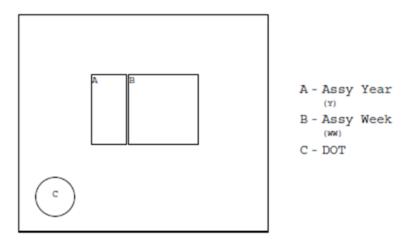

### 6.3.2 X2F-PSON6 package marking

The following figure shows the device marking for the X2F-PSON6 package.

DS15016 - Rev 2 page 32/42

Figure 35. X2F-PSON6 package marking

### 6.3.3 X2F-PSON6 tape and reel packing

X2F-PSON6 packages can be supplied with tape and reel packing. The reels have a 7 inches typical diameter. They contain 5000 devices each.

Figure 36. Dimensions of a 7" reel for 8 mm tape

DS15016 - Rev 2 page 33/42

Figure 37. Embossed carrier tape for X2F-PSON6

DS15016 - Rev 2 page 34/42

# 7 Ordering information

YY = Personalization setup

Note:

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest STMicroelectronics sales office.

DS15016 - Rev 2 page 35/42

## **Revision history**

Table 21. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 01-Jul-2025 | 1        | Initial release. |

| 04-Jul-2025 | 2        | Minor change.    |

DS15016 - Rev 2 page 36/42

### Glossary

AC Access condition

**ACK** Acknowledge

**CA** Certification Authority

**CF** Command frame

**ECC** Elliptic curve cryptography

FAck Frame acknowledge

I/O Input/output

**ID** Identity

I<sup>2</sup>C Inter-integrated circuit

LSB Least significant byte

MAC Message authentication code

**MCU** Microcontroller unit

MSB Most significant byte

**NACK** Not acknowledge

**NVM** Nonvolatile memory

**OS** Operating system

POR Power-on reset

**R-MAC** Response message authentication code

**ROM** Read-only memory

RTOS Real-time operating system

**SE** Secure element

**SOF** Start of frame

DS15016 - Rev 2 page 37/42

## **Contents**

| 1 | Description2 |                                                   |                                                                 |    |  |  |

|---|--------------|---------------------------------------------------|-----------------------------------------------------------------|----|--|--|

|   | 1.1          | Pin an                                            | nd signal description                                           | 3  |  |  |

|   | 1.2          | Data r                                            | management and usage monitoring                                 | 4  |  |  |

|   |              | 1.2.1                                             | Device authentication                                           | 5  |  |  |

|   |              | 1.2.2                                             | User NVM data authentication                                    | 6  |  |  |

| 2 | Eco          | system                                            |                                                                 | 9  |  |  |

|   | 2.1          | Services                                          |                                                                 |    |  |  |

|   | 2.2          | Softwa                                            | are                                                             | 9  |  |  |

|   | 2.3          | Hardw                                             | vare                                                            | 9  |  |  |

| 3 | STS          | AFE-L0                                            | 010 command set                                                 | 10 |  |  |

| 4 | Com          | nmunica                                           | ation interfaces                                                | 11 |  |  |

|   | 4.1          | ST1W                                              | /ire interface                                                  | 11 |  |  |

|   |              | 4.1.1                                             | Bit-transfer                                                    |    |  |  |

|   |              | 4.1.2                                             | Byte transfer                                                   | 12 |  |  |

|   |              | 4.1.3                                             | Frame protocol description                                      | 14 |  |  |

| 5 | AC/I         | AC/DC characteristics1                            |                                                                 |    |  |  |

|   | 5.1          | Absolu                                            | ute maximum ratings                                             | 17 |  |  |

|   | 5.2          | Recon                                             | nmended power supply filtering                                  | 17 |  |  |

|   | 5.3          | AC ch                                             | aracteristics                                                   | 18 |  |  |

|   | 5.4          | DC ch                                             | paracteristics                                                  | 18 |  |  |

|   | 5.5          | Performance and power consumption characteristics |                                                                 |    |  |  |

|   | 5.6          | Timings                                           |                                                                 |    |  |  |

|   | 5.7          | AC measurement conditions                         |                                                                 |    |  |  |

|   | 5.8          | ST1Wire electrical characteristics                |                                                                 |    |  |  |

| 6 | Pacl         | kage in                                           | formation                                                       | 22 |  |  |

|   | 6.1          | •                                                 | PN8 package specification                                       |    |  |  |

|   |              | 6.1.1                                             | UFDFPN8 package information                                     |    |  |  |

|   |              | 6.1.2                                             | Recommended footprint information for UFDFPN8 (landing pattern) | 24 |  |  |

|   |              | 6.1.3                                             | UFDFPN8 tape and reel packing                                   | 24 |  |  |

|   | 6.2          | DFN3                                              | package specification                                           | 27 |  |  |

|   |              | 6.2.1                                             | XDFN3 package information                                       | 27 |  |  |

|   |              | 6.2.2                                             | XDFN3 4 x 3.2 x 0.35 tape and reel packing                      | 28 |  |  |

|   | 6.3          | GQFN                                              | l6 package specification                                        | 30 |  |  |

|   |              | 6.3.1                                             | X2F-PSON6 package information (B0G5)                            | 30 |  |  |

|   |              | 6.3.2                                             | X2F-PSON6 package marking                                       | 32 |  |  |

### STSAFE-L010

|      | 6.3.3          | X2F-PSON6 tape and reel packing |

|------|----------------|---------------------------------|

| 7    | Ordering inf   | ormation                        |

| Rev  | vision history | 36                              |

| List | of tables      | 40                              |

| List | of figures     |                                 |

DS15016 - Rev 2

## **List of tables**

| Table 1.  | Signal descriptions                                                                                           | . 4 |

|-----------|---------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | Logical bit encoding                                                                                          |     |

| Table 3.  | Absolute maximum ratings                                                                                      | 17  |

| Table 4.  | Maximum V <sub>CC</sub> rising slope                                                                          | 17  |

| Table 5.  | 1.8 V and 3 V AC characteristics                                                                              | 18  |

| Table 6.  | DC characteristics                                                                                            | 18  |

| Table 7.  | 1.8 V DC characteristics (V <sub>CC</sub> = 1.8 V ±10%)                                                       | 18  |

| Table 8.  | 3 V DC characteristics (V <sub>CC</sub> = 3 V ± 10%)                                                          | 19  |

| Table 9.  | 1.8 V and 3 V power consumption characteristics                                                               | 19  |

| Table 10. | AC measurement conditions                                                                                     | 19  |

| Table 11. | Capacitance on IO pad                                                                                         | 20  |

| Table 12. | ST1Wire 3-contacts DC characteristics (1.62 to 5.5 V; -25°C to 85°C; CL = 20 pF; Pull-up = 1.375 k $\Omega$ ) | 20  |

| Table 13. | UFDFPN8 - 8-lead, 2 × 3 mm, 0.5 mm pitch ultra thin profile fine pitch dual flat package mechanical data      | 23  |

| Table 14. | UFDFPN8 package on tape and reel                                                                              | 24  |

| Table 15. | UFDFPN8 reel dimensions                                                                                       | 25  |

| Table 16. | XDFN3 package mechanical data                                                                                 | 28  |

| Table 17. | XDFN3 4 x 3.2 x 0.35 packages on tape and reel                                                                | 28  |

| Table 18. | XDFN3 4 x 3.2 x 0.35 reel dimensions                                                                          | 29  |

| Table 19. | Carrier tape dimensions for XDFN3 4 x 3.2 x 0.35                                                              |     |

| Table 20. | X2F-PSON - Mechanical data                                                                                    | 32  |

| Table 21. | Document revision history                                                                                     | 36  |

DS15016 - Rev 2 page 40/42

# **List of figures**

| Figure 1.  | STSAFE-L010 connection diagram                                                                   | . 2 |

|------------|--------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | UFDFPN8 pinout - Top view                                                                        | . 3 |

| Figure 3.  | X2F-PSON6 pinout - Top view                                                                      | . 3 |

| Figure 4.  | DFN3 pinout - Top view                                                                           | . 3 |

| Figure 5.  | STSAFE-L010 data read/update sequence                                                            | . 4 |

| Figure 6.  | STSAFE-L010 ECC authentication diagram                                                           | . 5 |

| Figure 7.  | STSAFE-L010 ECC Authentication diagram on distant entity                                         | . 6 |

| Figure 8.  | STSAFE-L010 user NVM data authentication                                                         | . 7 |

| Figure 9.  | STSAFE-L010 user NVM data authentication on distant/external entity                              | . 8 |

| Figure 10. | ST1Wire 3-contact implementation                                                                 | 11  |

| Figure 11. | Bit encoding                                                                                     | 12  |

| Figure 12. | Byte structure                                                                                   | 13  |

| Figure 13. | ST1Wire inter-byte delay                                                                         | 13  |

| Figure 14. | Host processing vs inter-byte management                                                         | 14  |

| Figure 15. | ST1Wire start of frame (SOF)                                                                     | 15  |

| Figure 16. | STSAFE-L010 ST1Wire command frame                                                                | 15  |

| Figure 17. | STSAFE-L010 ST1Wire response frame                                                               | 15  |

| Figure 18. | Recommended filtering capacitors on VCC                                                          | 17  |

| Figure 19. | Power-on and warm reset sequences                                                                | 19  |

| Figure 20. | AC testing input/output waveforms                                                                | 20  |

| Figure 21. | AC testing load circuit                                                                          | 20  |

| Figure 22. | ST1Wire DC timings description                                                                   | 21  |

| Figure 23. | UFDFPN8 package                                                                                  | 22  |

| Figure 24. | UFDFPN8 - 8-lead, 2 × 3 mm, 0.5 mm pitch ultra thin profile fine pitch dual flat package outline | 23  |

| Figure 25. | Recommended footprint for UFDFPN8                                                                | 24  |

| Figure 26. | Dimensions of a 13" reel for 8 mm tape                                                           | 25  |

| Figure 27. | Embossed carrier tape for UFDFPN8                                                                | 25  |

| Figure 28. | Leader and trailer for UFDFPN8                                                                   |     |

| Figure 29. | XDFN3 package outline                                                                            | 27  |

| Figure 30. | XDFN3 4 x 3.2 x 0.35 reel diagram                                                                | 29  |

| Figure 31. | XDFN3 4 x 3.2 x 0.35 Leader and trailer                                                          | 29  |

| Figure 32. | Embossed carrier tape for XDFN3 4 x 3.2 x 0.35                                                   | 30  |

| Figure 33. | X2F-PSON6 - Outline                                                                              | 31  |

| Figure 34. | X2F-PSON6 - Footprint example                                                                    | 32  |

| Figure 35. | X2F-PSON6 package marking                                                                        | 33  |

| Figure 36. | Dimensions of a 7" reel for 8 mm tape                                                            | 33  |

| Figure 37  | Embossed carrier tape for X2F-PSON6                                                              | 34  |

DS15016 - Rev 2 page 41/42

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DS15016 - Rev 2 page 42/42