# Specifications for LCD module

| Customer          | Avnet                |

|-------------------|----------------------|

| Customer part no. | AES-ACC-DISP-7INCH   |

| Ampire part no.   | AM-8001280GTZQW-T10H |

| Approved by       |                      |

| Date              |                      |

□Preliminary Specification

**■** Formal Specification

**AMPIRE CO., LTD.**

4F., No.116, Sec. 1, Xintai 5th Rd., Xizhi Dist., New Taipei City221, Taiwan (R.O.C.)

新北市汐止區新台五路一段 116號 4樓(東方科學園區 A棟)

TEL:886-2-26967269, FAX:886-2-26967196 or 26967270

| Approved by | Checked by | Organized by |

|-------------|------------|--------------|

| Kokai       | Mark       | Lawlite      |

This Specification is subject to change without notice.

Date: 2024/10/07 AMPIRE CO., LTD. 1

## **RECORD OF REVISION**

| Revision Date                          | Page   | Contents                                                                                | Editor                       |

|----------------------------------------|--------|-----------------------------------------------------------------------------------------|------------------------------|

| 2023/10/23<br>2024/01/08<br>2024/03/19 | <br>27 | New Release<br>TFT-8001280-09-A rename to<br>AM-8001280GTZQW-T10H<br>Update PCB drawing | Mantle<br>Lawlite<br>Lawlite |

| 2024/10/07                             | 27     | Update PCB drawing                                                                      | Lawlite                      |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

|                                        |        |                                                                                         |                              |

## 1. General Descriptions

7 inch Amorphous-TFT-LCD (Thin Film Transistor Liquid Crystal Display) module. This module is composed of a 7" TFT-LCD panel and backlight unit.

#### 1.1 Features

- 7 inch configuration

- 4wire mipi interface

- Driver IC: ILI9881C

- RoHS

- Projective Capacitive Touch

- Touch Controller : ILI2132

- Interface : I2C

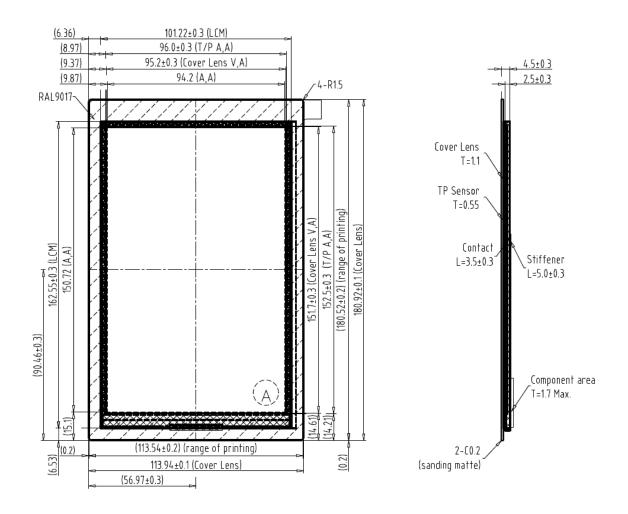

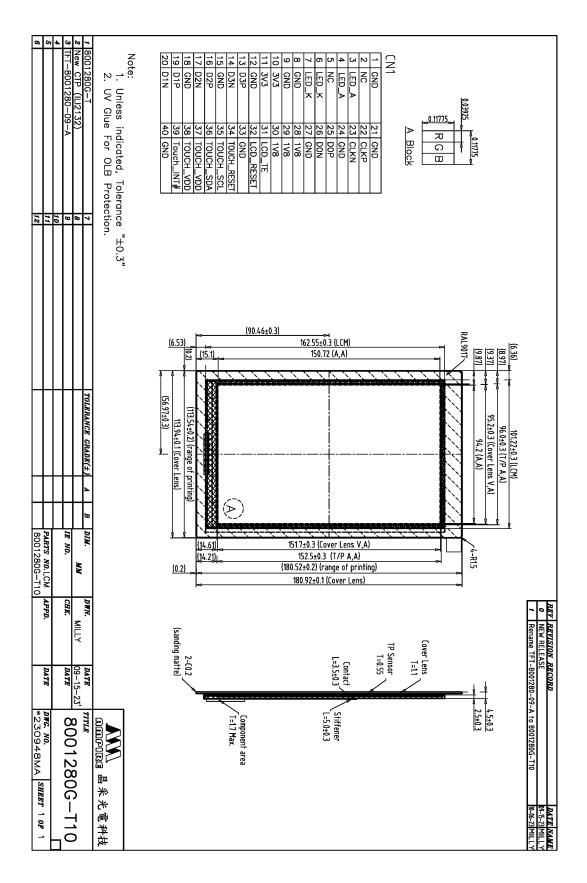

- Cover Lens: 113.94\*180.92\*1.1Tmm. Black frame.

- Optical bonding between LCD and touch panel.

- ◆ Clear display

- ◆ Glare Reduction

- ♦ No Condensation

#### 1.2 Customize

- (1) Bridge board

- (2) FFC

## 1.3 Product Summary

Date: 2024/10/07

| Item              | Specification               | Remark |

|-------------------|-----------------------------|--------|

| LCD Size          | 7.0 inch (Diagonal)         |        |

| Resolution        | 800 x 3 (RGB) x 1280        |        |

| Display Mode      | Normally Black.             |        |

| Pixel pitch       | 0.03925 (W) x 0.11775(H) mm |        |

| Active area       | 94.2(W) x 150.72(H) mm      |        |

| Interface         | MIPI                        |        |

| Color arrangement | RGB-stripe                  |        |

| Luminance         | 340                         | cd/m2  |

| Viewing Direction | All direction               |        |

| Pixel Density     | 216 PPI                     |        |

| Color Depth       | 24 bits                     |        |

## 2. Absolute Maximum Ratings

| Item                  | Symbol | Min. | Max. | Unit                   | Remark |

|-----------------------|--------|------|------|------------------------|--------|

| Power Supply Voltage  | 3V3    | -0.3 | +3.6 | V                      | -      |

| IO Supply voltage     | 1V8    | -0.3 | +3.6 | V                      |        |

| Operating Temperature | TOP    | -20  | 70   | $^{\circ}\!\mathbb{C}$ | Note 1 |

| Storage Temperature   | TST    | -30  | 80   | $^{\circ}\!\mathbb{C}$ | Note 1 |

- Note(1) The maximum rating is defined as above based on the chamber temperature, which might be different from ambient temperature after assembling the panel into the application. Moreover, some temperature-related phenomenon as below needed to be noticed:

- ♦ Background color, contrast and response time would be different in temperatures other than 25°C.

- ♦ Operating under high temperature will decrease LED lifetime.

## 3. Electrical Characteristics

## 3.1 LCD Characteristics

| Item                       | Symbol | Min.    | Тур. | Max.    | Unit | Note      |

|----------------------------|--------|---------|------|---------|------|-----------|

| Power Supply Voltage       | 3V3    | 3.2     | 3.3  | 3.4     | V    |           |

| IO Supply voltage          | 1V8    | 1.74    | 1.8  | 3.4     | V    |           |

| Input Hi Logic Voltage     | VIH    | 0.7*1V8 |      | 1V8     | V    | LCD_RESET |

| Input Low Logic<br>Voltage | VIL    | -0.3    |      | 0.3*1V8 | V    | LCD_RESET |

| Out Hi Logic Voltage       | VOH    | 0.8*1V8 |      | 1V8     | V    | LCD_TE    |

| Out Low Logic<br>Voltage   | VOL    | -0.3    |      | 0.2*1V8 | V    | LCD_TE    |

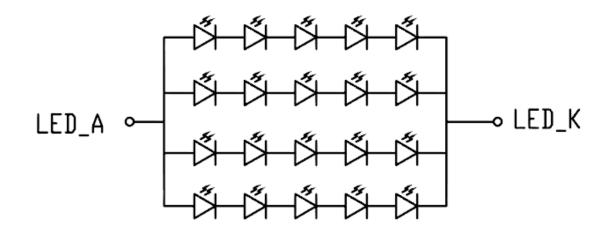

## 3.2 Backlight Characteristics

Date: 2024/10/07

| Item                | Symbol | Min.   | Тур.   | Max. | Unit | Note               |

|---------------------|--------|--------|--------|------|------|--------------------|

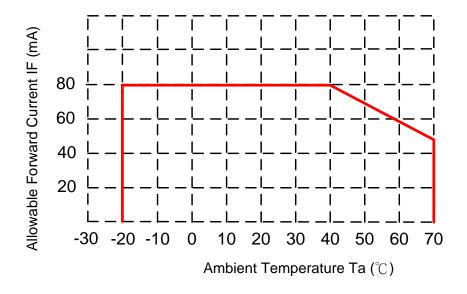

| LED Forward Current | IF     |        | 80     |      | mA   | Ta=25°C            |

| LED Forward Voltage | VF     |        | 15     | 18   | V    | IF=80mA,<br>Ta=25℃ |

| LED life time       |        | 30,000 | 50,000 | -    | Hr   | IF=80mA,<br>Ta=25℃ |

- The constant current source is needed for white LED back-light driving.

- Operating life means brightness goes down to 50% minimum brightness. LED life time is estimated data. Ta=25°C

- When LCM is operated over 40°C ambient temperature, the IF should be follow:

#### 3.4 Touch Panel Unit

#### 3.4.1 Basic Characteristics

| ITEM                                     | SPECIFICATION                     |  |

|------------------------------------------|-----------------------------------|--|

| Туре                                     | Projective Capacitive Touch Panel |  |

| Activation                               | Two-fingers or Single-finger      |  |

| X/Y Position Reporting                   | Absolute Position                 |  |

| Touch Force No contact pressure required |                                   |  |

| Calibration                              | No need for calibration           |  |

| Report Rate                              | Approx 100 points/sec             |  |

| Interface                                | I2C                               |  |

| Control IC                               | ILI2132                           |  |

#### 3.4.2 Electronic Characteristics

Specify the normal operating condition

(GND=0V)

| Item                     | Symbol | Min.    | Тур.  | Max. | Unit | Note |

|--------------------------|--------|---------|-------|------|------|------|

| Power Supply Voltage     | VDD    | 3.0     | 3.3   | 3.6  | ٧    |      |

| Low Level Input Voltage  | VIL    | 0       |       | 0.8  | V    | 1    |

| High Level Input Voltage | VIH    | 0.8*VDD |       | VDD  | V    | 1    |

| Power Consumption        | Ivcc   |         | T.B.D |      | mA   |      |

Note 1: TOUCH\_SDA, TOUCH\_SCL, TOUCH\_RESET

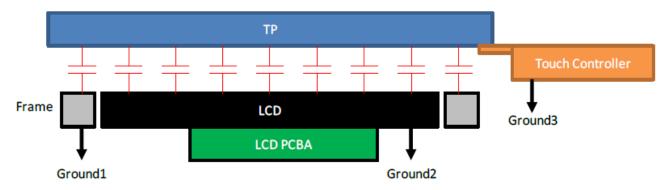

## 3.4.3 Grounding

TP needs to work in environment with stable stray capacitance. In order to minimize the variation in stray capacitance, all conductive mechanical parts must not be floating. Intermittent floating any conductive part around the touch sensor may cause significant stray capacitance change and abnormal touch function. It is recommended to keep all conductive parts having same electrical potential as the GND of the touch controller module.

GND1, GND2 and GND3 should be connected together to have the same ground

## 4. AC Characteristics

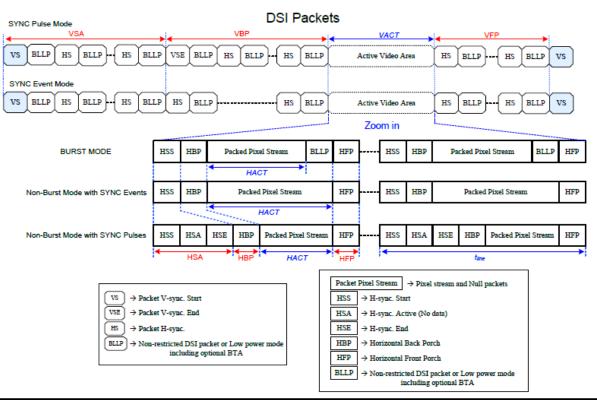

## **DSI** layer definitions

## 13.4.3.1. High Speed Mode - Clock Channel Timing

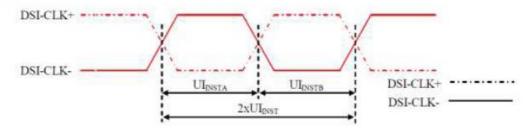

Figure 118 DSI Clock Channel Timing

Table 47 DSI Clock Channel Timing

| Signal     | Symbol               | Parameter               | Min | Max | Unit |

|------------|----------------------|-------------------------|-----|-----|------|

| DSI-CLK+/- | 2xUI <sub>INST</sub> | Double UI instantaneous | 2   | 5   | ns   |

| DSI-CLK+/- | Ulinsta, Ulinsta     | UI instantaneous Half   | 1   | 2.5 | ns   |

Note: UI = UI<sub>INSTA</sub> = UI<sub>INSTB</sub>

## 13.4.3.2. High Speed Mode - Data Clock Channel Timing

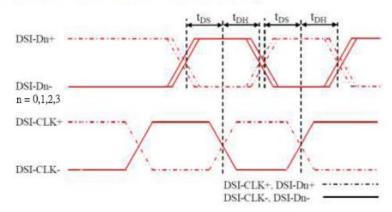

Figure 119 DSI Data to Clock Channel Timings

Table 48 DSI Data to Clock Channel Timings

| Signal               | Symbol | Parameter                | Min     | Max |

|----------------------|--------|--------------------------|---------|-----|

| DOLD / 0400          | tos    | Data to Clock Setup time | 0.15xUI |     |

| DSI-Dn+/-, n=0,1,2,3 | tон    | Clock to Data Hold Time  | 0.15xUI | 9 2 |

#### 13.4.3.3. High Speed Mode - Rise and Fall Timings

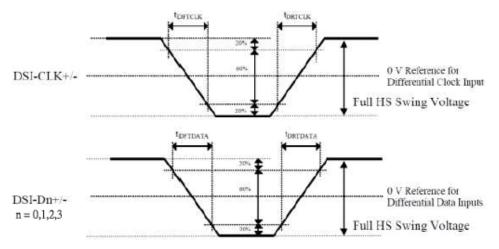

Figure 120 Rise and Fall Timings on Clock and Data Channels

Specification Parameter Symbol Condition Min Max Typ 0.3UI Differential Rise Time for Clock DSI-CLK+/-150 ps **t**DRTCLK (Note) 0.3UI DSI-Dn+/-150 ps Differential Rise Time for Data **t**DRTDATA (Note) n=0.1,2,3 0.3UI Differential Fall Time for Clock DSI-CLK+/-150 ps t<sub>DFTCLK</sub> (Note) 0.3UI DSI-Dn+/-150 ps Differential Fall Time for Data **t**DFTDATA (Note) n=0,1,2,3

Table 49 Rise and Fall Timings on Clock and Data Channels

Note:

The display module has to meet timing requirements, what are defined for the transmitter(MPU) on MIPI D-Phy standard

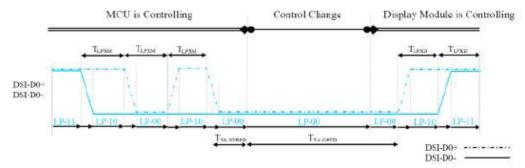

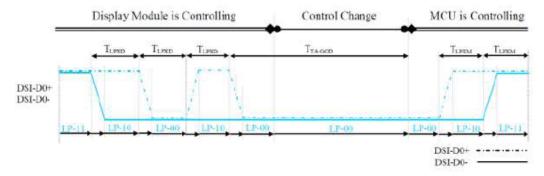

#### 13.4.3.4. Low Speed Mode - Bus Turn Around

Lower Power Mode and its State Periods are illustrated for reference purposes on the Bus Turnaround (BTA) from the MPU to the Display Module (ILI7807D) sequence below.

Figure 121 BTA from the MPU to the Display Module

Lower Power Mode and its State Periods are illustrated for reference purposes on the Bus Turnaround (BTA) from the Display Module (ILI7807D) to the MPU sequence below.

Figure 122 BTA from the Display Module to the MPU

Table 50 Low Power State Period Timings - A

| Signal    | Symbol                | Description                                                                       | Min        | Max                 | Unit |

|-----------|-----------------------|-----------------------------------------------------------------------------------|------------|---------------------|------|

| DSI-D0+/- | T <sub>LPXM</sub>     | Length of LP-00, LP-01, LP-10 or LP-11 periods<br>MPU → Display Module (ILI7807D) | 50         | 75                  | ns   |

| DSI-D0+/- | TLPXD                 | Length of LP-00, LP-01, LP-10 or LP-11 periods<br>Display Module (ILI7807D) → MPU | 50         | 75                  | ns   |

| DSI-D0+/- | T <sub>TA-SURED</sub> | Time-out before the Display Module (ILI7807D) starts driving                      | $T_{LPXD}$ | $2 \times T_{LPXD}$ | ns   |

Table 51 Low Power State Period Timings - B

| Signal    | Symbol               | Description                                        | Time                | Unit |

|-----------|----------------------|----------------------------------------------------|---------------------|------|

| DSI-D0+/- | T <sub>TA-GETD</sub> | Time to drive LP-00 by Display Module (ILI7807D)   | $5 \times T_{LPXD}$ | ns   |

| DSI-D0+/- | T <sub>TA-900</sub>  | Time to drive LP-00 after turnaround request – MPU | $4 \times T_{LPXD}$ | ns   |

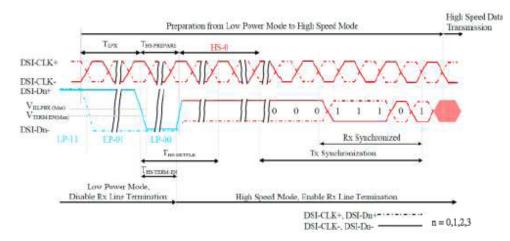

## 13.4.3.5. Data Lanes from Low Power Mode to High Speed Mode

Figure 123 Data Lanes – Low Power Mode to High Speed Mode Timings

Table 52 Data Lanes - Low Power Mode to High Speed Mode Timings

| Signal               | Symbol                  | Description                                                                                | Min     | Max     | Unit |

|----------------------|-------------------------|--------------------------------------------------------------------------------------------|---------|---------|------|

| DSI-Dn+/-, n=0,1,2,3 | T <sub>LPX</sub>        | Length of any Low Power State Period                                                       | 50      | -       | ns   |

| DSI-Dn+/-, n=0,1,2,3 | T <sub>HS-PREPARE</sub> | Time to drive LP-00 to prepare for HS Transmission                                         | 40+4xUI | 85+6xUI | ns   |

| DSI-Dn+/-, n=0,1,2,3 | T <sub>HS-TERM-EN</sub> | Time to enable Data Lane Receiver line termination<br>measured from when Dn crosses VILMAX | •       | 35+4xUI | ns   |

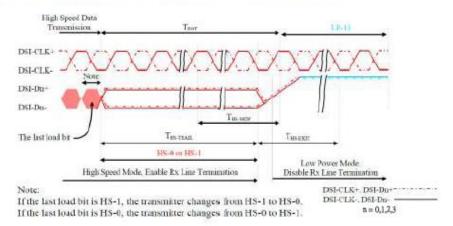

## 13.4.3.6. Data Lanes from High Speed Mode to Low Power Mode

Figure 124 Data Lanes - High Speed Mode to Low Power Mode Timings

Table 53 Data Lanes - High Speed Mode to Low Power Mode Timings

| Signal               | Symbol               | Description                                                                                                            | Min                         | Max     | Unit |

|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|------|

| DSI-Dn+/-, n=0,1,2,3 | T <sub>HS-SIGP</sub> | Time-Out at Display Module (ILI7807D) to ignore transition<br>period of EoT                                            | 40                          | 55+4xUI | ns   |

| DSI-Dn+/-, n=0,1,2,3 | THS-EXIT             | Time to driver LP-11 after HS burst                                                                                    | 100                         | 4       | ns   |

| DSI-Dn+/-, n=0,1,2,3 | THSTRAL              | Time that the transmitter drives the flipped differential state after last payload data bit of a HS transmission burst | max(8*UI,<br>60ns+<br>4*UI) |         | ns   |

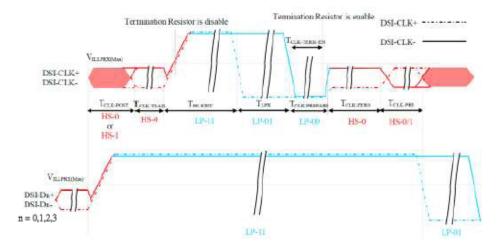

## 13.4.3.7. DSI Clock Burst - High Speed Mode to/from Low Power Mode

Figure 125 Clock Lanes - High Speed Mode to/from Low Power Mode Timings

Table 54 Clock Lanes - High Speed Mode to/from Low Power Mode Timings

| Signal     | Symbol                   | Description                                                                                                             | Min      | Max | Unit |

|------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|-----|------|

| DSI-CLK+/- | T <sub>CLK-POST</sub>    | Time that the MPU shall continue sending HS clock after the last associated Data Lanes has transitioned to LP mode      | 60+52xUI | -   | ns   |

| DSI-CLK+/- | T <sub>CLK-TRAIL</sub>   | Time to drive HS differential state after last payload clock bit of a HS transmission burst                             | 60       | -   | ns   |

| DSI-CLK+/- | T <sub>HS-EXIT</sub>     | Time to drive LP-11 after HS burst                                                                                      | 100      | -   | ns   |

| DSI-CLK+/- | T <sub>CLK-PREPARE</sub> | Time to drive LP-00 to prepare for HS transmission                                                                      | 38       | 95  | ns   |

| DSI-CLK+/- | T <sub>CLK-TERM-EN</sub> | Time-out at Clock Lane to enable HS termination                                                                         | -        | 38  | ns   |

| DSI-CLK+/- | T <sub>CLK-PREPARE</sub> | Minimum lead HS-0 drive period before starting Clock                                                                    | 300      | -   | ns   |

| DSI-CLK+/- | T <sub>CLK-PRE</sub>     | Time that the HS clock shall be driven prior to any associated<br>Data Lane beginning the transition from LP to HS mode | 8xUI     | -   | ns   |

## 13.4.3.8. Timing for DSI video mode

## 4.4 Interface Timings

| Parameters              | Symbols           | Min.        | Typ. | Max.   | Units     |

|-------------------------|-------------------|-------------|------|--------|-----------|

| Vertical sync. active   | VSA               | 2 (Note 6)  | -    | -      | Line      |

| Vertical Back Porch     | VBP               | 14 (Note 6) | -    | -      | Line      |

| Vertical Front Porch    | VFP               | 8 (Note 6)  | (7)  | -      | Line      |

| Active lines per frame  | VACT              | -           | 1280 |        | Line      |

| Horizontal sync. active | HSA               | 2           | -    | -      | Pixel     |

| Horizontal Porch period | HSA + HBP + HFP   | 1.6         | -    | -      | us        |

| Active pixels per line  | HACT              | -           | 720  | -      | Pixel     |

| Bit rate                | BR <sub>bps</sub> | 385         |      | Note 5 | Mbps/lane |

<sup>1</sup> UI=1/Bit rate

HSA(pixel)= (tHSA\*lane number ) / (UI\* pixel format )

HBP(pixel)= (tHBP\*lane number ) / (UI\* pixel format )

HFP(pixel)= (tHFP\*lane number ) / (UI\* pixel format )

$$\label{eq:Rate} \text{Frame Rate} = \frac{\text{BR}_{\text{bps}} \text{ x Lane}_{\text{num}}}{(\text{VACT+VSA+VBP+VFP}) \text{ x (HACT+HSA+HBP+HFP) x Pixel Format}}$$

Example:  $BR_{bps} = 457Mbps/lane$ , 1UI=2.1883ns, Frame rate=60Hz, VACT=1280, VSA=2, VBP=30, VFP=20, HACT=720, HSA=33, HBP=100, HFP=100, Lane\_{num}=4(lane), Pixel Format=24(bit).

#### Note:

Lane<sub>num</sub>: Date lane of MIPI-DSI.

Date: 2024/10/07

- 2. Pixel Format: Please reference to "DSI System Interface".

- 3. The formula exists slightly error because of the host-transmission way.

- 4. The best frame rate setting is from 50 to 60 Hz.

- 5. Please reference to "Table 55 Limited Clock Channel Speed"

- 6. The minimum values of this table mean the limitation of IC without considering the panel GIP.

The actual values of VSA, VBP and VFP will be changed by different panel GIP setting.

Table 55 Limited Clock Channel Speed

| Data type                                                   | Two Lanes speed | Three Lanes speed | Four Lanes<br>speed |

|-------------------------------------------------------------|-----------------|-------------------|---------------------|

| Data Type = 00 1110 (0Eh), RGB 565, 16 UI per Pixel         | 1 Gbps          | 666 Mbps          | 666 Mbps            |

| Data Type = 01 1110 (1Eh), RGB 666, 18 UI per Pixel         | 1 Gbps          | 666 Mbps          | 666 Mbps            |

| Data Type = 10 1110 (2Eh), RGB 666 Loosely, 24 UI per Pixel | 1 Gbps          | 1 Gbps            | 1 Gbps              |

| Data Type = 11 1110 (3Eh), RGB 888, 24 UI per Pixel         | 1 Gbps          | 1 Gbps            | 1 Gbps              |

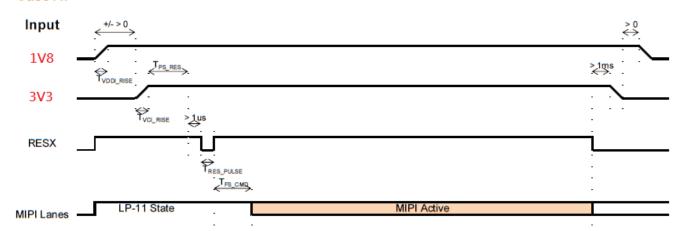

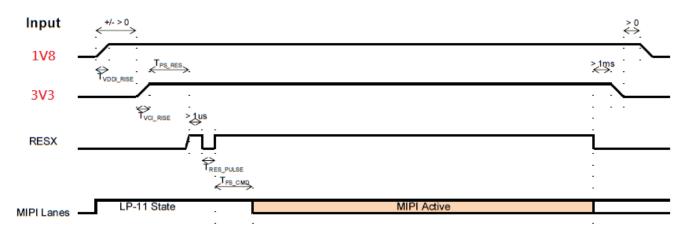

## 4.5 Power ON/OFF Sequence

## Case A:

## Case B:

|              | Symbol                    | Characteristics           | Min. | Тур. | Max. | Units |

|--------------|---------------------------|---------------------------|------|------|------|-------|

| 1 <b>V</b> 8 | $T_{VDDI\_RISE}$          | VDDI Rise time            | 10   | -    | •    | us    |

| 21.42        | -                         | Case A: VCI Rise time     | 130  |      |      |       |

| 3 <b>V</b> 3 | 3V3 T <sub>VCI_RISE</sub> | Case B: VCI Rise time     | 40   | -    | -    | us    |

|              | T <sub>PS_RES</sub>       | VDDI/VCI on to Reset high | 5    | -    | •    | ms    |

|              | T <sub>RES_PULSE</sub>    | Reset low pulse time      | 10   | -    | •    | us    |

|              | T <sub>FS_CMD</sub>       | Reset to first command    | 10   | -    | -    | ms    |

# 5. Timing

| Man.                    | Ol- al | Values |      |      | 11   | Damark              |

|-------------------------|--------|--------|------|------|------|---------------------|

| ltem                    | Symbol | Min.   | Тур. | Max. | Unit | Remark              |

| Clock Frequency         | fclk   | 40.8   | 51.2 | 67.2 | MHz  | Frame rate<br>=60Hz |

| Horizontal display area | thd    |        | 800  |      | DCLK |                     |

| Horizontal Back Porch   | HBP    |        | 20   |      | DCLK |                     |

| Horizontal Pulse Width  | HS     |        | 20   |      | DCLK |                     |

| Horizontal Front Porch  | HFP    |        | 32   |      | DCLK |                     |

| HS Blanking             | thb    |        | 72   |      | DCLK |                     |

| HS period time          | th     |        | 872  |      | DCLK |                     |

| Vertical display area   | tvd    |        | 1280 |      | Н    |                     |

| Vertical Back Porch     | VBP    |        | 6    |      | Н    |                     |

| Vertical Pulse Width    | VS     |        | 4    |      | Н    |                     |

| Vertical Front Porch    | HFP    |        | 8    |      | Н    |                     |

| VS Blanking             | thb    |        | 18   |      | Н    |                     |

| VS period time          | tv     |        | 1298 |      | Н    |                     |

# 6. Interface

| Pin No. | Symbol | I/O | Description                      | Note |

|---------|--------|-----|----------------------------------|------|

| 1       | GND    | Р   | Power Ground                     |      |

| 2       | NC     | -   | No connection                    |      |

| 3       | LED_A  | Р   | Power for LED backlight anode    |      |

| 4       | LED_A  | Р   | Power for LED backlight anode    |      |

| 5       | NC     | -   | No connection                    |      |

| 6       | LED_K  | Р   | Power for LED backlight negative |      |

| 7       | LED_K  | Р   | Power for LED backlight negative |      |

| 8       | GND    | Р   | Power Ground                     |      |

| 9       | GND    | Р   | Power Ground                     |      |

| 10      | 3V3    | Р   | Power Supply voltage Analog      |      |

| 11      | 3V3    | Р   | Power Supply voltage Analog      |      |

| 12      | GND    | Р   | Power Ground                     |      |

| 13      | D3P    | I   | MIPI DSI differential data pair  |      |

| 14      | D3N    | ı   | MIPI DSI differential data pair  |      |

| 15      | GND    | Р   | Power Ground                     |      |

| 16      | D2P    | I   | MIPI DSI differential data pair  |      |

| 17      | D2N    | I   | MIPI DSI differential data pair  |      |

| 18      | GND    | Р   | Power Ground                     |      |

| 19      | D1P    | ı   | MIPI DSI differential data pair  |      |

| 20      | D1N    | ı   | MIPI DSI differential data pair  |      |

| 21      | GND    | Р   | Power Ground                     |      |

| 22      | CLKP   | ı   | MIPI DSI differential CLK pair   |      |

| 23      | CLKN   | I   | MIPI DSI differential CLK pair   |      |

| 24      | GND    | Р   | Power Ground                     |      |

| 25      | D0P    | ı   | MIPI DSI differential data pair  |      |

| 26      | D0N    | I   | MIPI DSI differential data pair  |      |

| 27      | GND    | Р   | Power Ground                     |      |

| 28 | 1V8         | Р   | Power Supply voltage Digital                                    |

|----|-------------|-----|-----------------------------------------------------------------|

| 29 | 1V8         | Р   | Power Supply voltage Digital                                    |

| 30 | 1V8         | Р   | Power Supply voltage Digital                                    |

| 31 | LCD_TE      | 0   | Tearing effect output pin.  Leave the pin open when not in use. |

| 32 | LCD_RESET   | ı   | LCD reset signal, low active                                    |

| 33 | GND         | Р   | Power Ground                                                    |

| 34 | TOUCH_RESET | I   | Touch reset signal, low active                                  |

| 35 | TOUCH_SCL   | I   | Touch IC I2C Bus serial clock                                   |

| 36 | TOUCH_SDA   | I/O | Touch IC I2C Bus serial data                                    |

| 37 | TOUCH_VDD   | Р   | Power Supply voltage touch IC                                   |

| 38 | TOUCH_VDD   | Р   | Power Supply voltage touch IC                                   |

| 39 | TOUCH_INT#  | 0   | Touch IC interrupt. Active Low.                                 |

| 40 | GND         | Р   | Power Ground                                                    |

|    |             |     |                                                                 |

Note (1): Be sure to apply the power voltage as the power sequence spec.

## 7. Optical Specifications

## 7.1 TFT Optical Characteristics

| Item                  |       | Symbol   | Condition | Min.  | Тур.    | Max.  | Unit              | Remark                         |  |

|-----------------------|-------|----------|-----------|-------|---------|-------|-------------------|--------------------------------|--|

|                       |       | θТ       |           | 70    | 85      | -     |                   |                                |  |

| View Ang              | loo   | θВ       | CR≧10     | 70    | 85      | -     | Dograd            | Noto(2)                        |  |

| view Ang              | 162   | θL       | OIX≦ IU   | 70    | 85      | -     | Degree            | Note(2)                        |  |

|                       |       | θR       |           | 70    | 85      | -     |                   |                                |  |

| Contrast Ratio        |       | CR       | θ=0°      | (700) | (1000)  | -     |                   | Left/right 0°<br>Top/bottom 5° |  |

| Response <sup>-</sup> | Time  | TON+TOFF | 25℃       | -     | 25      | 35    | ms                | Note(1)(4)                     |  |

|                       | White | Х        |           | -0.05 | (0.313) |       |                   |                                |  |

|                       |       | у        |           |       | (0.329) |       |                   |                                |  |

|                       | Red   | Х        |           |       | T.B.D   |       |                   | l                              |  |

| Chromoticity          |       | у        |           |       | T.B.D   | +0.05 |                   | Noto(1)(E)                     |  |

| Chromaticity          | Croon | Х        |           |       | T.B.D   | +0.05 |                   | Note(1)(5)                     |  |

|                       | Green | у        |           |       | T.B.D   |       |                   |                                |  |

|                       | Dlug  | Х        |           |       | T.B.D   |       |                   |                                |  |

|                       | Blue  | у        |           |       | T.B.D   |       |                   |                                |  |

| Uniformi              | ity   | U        |           | 75    | 80      | -     | %                 | Note(1)(6)                     |  |

| NTSC                  |       |          | CIE1931   | 45    | 50      | -     | %                 |                                |  |

| Luminan               | се    | L        |           | 300   | 340     | -     | cd/m <sup>2</sup> | Note(7)                        |  |

## **Test Conditions:**

- 1. IF= 80mA, the ambient temperature is 25℃.

- 2. The test systems refer to Note (1) and Note (2).

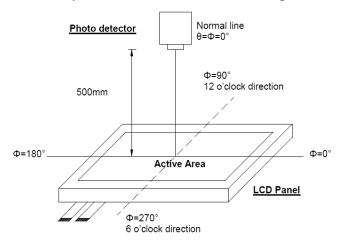

## Definition of optical measurement system

The optical characteristics should be measured in dark room. After 10 Minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

## Note(1) Definition of optical measurement system

The optical characteristics should be measured in dark room. After 30 minutes operation, the optical properties are measured at the center point of the LCD screen. (Response time is measured by Photo detector TOPCON BM-7, other items are measured by BM-7/Field of view: 1° / Height: 500mm.)

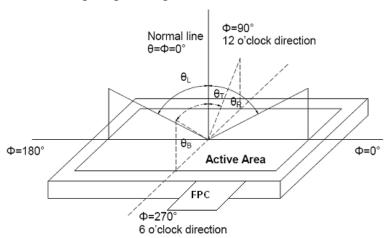

## Note(2) Definition of viewing angle range

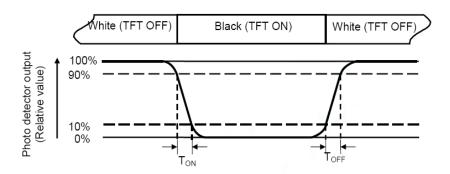

## Note(3) Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time (Ton) is the time between photo detector output intensity changed from 90% to 10%. And fall time (Toff) is the time between photo detector output intensity changed from 10% to 90%.

## Note(4) Definition of contrast ratio

Contrast ratio (CR) =

Luminance measured when LCD on the "White" state

Luminance measured when LCD on the "Black" state

- Note(5) Definition of color chromaticity (CIE1931)

Color coordinated measured at center point of LCD.

- Note(6) All input terminals LCD panel must be ground when measuring the center area of the panel.

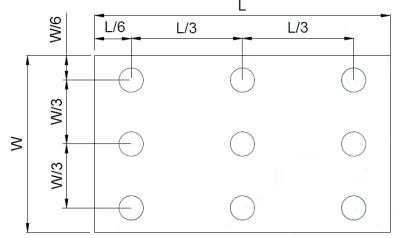

- Note(7) Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer to bellow figure). Every measuring point is placed at the center of each measuring area.

L ---- Active area length W ---- Active area width

Bmax: The measured maximum luminance of all measurement position.

Bmin: The measured minimum luminance of all measurement position.

## 8. Reliability Test Items

| Test Item                                | Test Conditions                                                                                                | Note |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|

| High Temperature Operation               | 70±3°C , t=240 hrs                                                                                             |      |

| Low Temperature Operation                | -20±3°C , t=240 hrs                                                                                            |      |

| High Temperature Storage                 | 80±3°C , t=240 hrs                                                                                             | 1,2  |

| Low Temperature Storage                  | -30±3°C , t=240 hrs                                                                                            | 1,2  |

| Storage at High Temperature and Humidity | 60°C, 90% RH , 240 hrs                                                                                         | 1,2  |

| Thermal Shock Test                       | -20°C (30min) ~ 70°C (30min)<br>100 cycles                                                                     | 1,2  |

| Vibration Test (Packing)                 | Sweep frequency: 10 ~ 55 ~ 10 Hz/1min Amplitude: 0.75mm Test direction: X.Y.Z/3 axis Duration: 30min/each axis | 2    |

- Note(1) Condensation of water is not permitted on the module.

- Note(2) The module should be inspected after 1 hour storage in normal conditions (15-35°C, 45-65%RH).

- Note(3) The module shouldn't be tested over one condition, and all the tests are independent.

- Note(4) All reliability tests should be done without the protective film.

## Definitions of life end point:

- Current drain should be smaller than the specific value.

- Function of the module should be maintained.

- Appearance and display quality should not have degraded noticeably.

- Contrast ratio should be greater than 50% of the initial value.

#### 9. General Precaution

## 9.1 Disassembling or Modification

(1) Do not disassemble or modify the module. It may damage sensitive parts inside LCD module, and may cause scratches or dust on the display. AMPIRE does not warrant the module, if customers disassemble or modify the module.

## 9.2 Breakage of LCD Panel

- (1) If LCD panel is broken and liquid crystal spills out, do not ingest or inhale liquid crystal, and do not contact liquid crystal with skin.

- (2) If liquid crystal contacts mouth or eyes, rinse out with water immediately.

- (3) If liquid crystal contacts skin or cloths, wash it off immediately with alcohol and rinse thoroughly with water.

- (4) Handle carefully with chips of glass that may cause injury, when the glass is broken.

#### 9.3 Electric Shock

- (1) Disconnect power supply before handling LCD module.

- (2) Do not pull or fold the LED cable.

- (3) Do not touch the parts inside LCD modules and the fluorescent LED's connector or cables in order to prevent electric shock.

#### 9.4 Absolute Maximum Ratings and Power Protection Circuit

- (1) Do not exceed the absolute maximum rating values, such as the supply voltage variation, input voltage variation, variation in parts' parameters, environmental temperature, etc., otherwise LCD module may be damaged.

- (2) Please do not leave LCD module in the environment of high humidity and high temperature for a long time.

- (3) It's recommended to employ protection circuit for power supply.

#### 9.5 Operation

- (1) Do not touch, push or rub the polarizer with anything harder than HB pencil lead.

- (2) Use fingerstalls of soft gloves in order to keep clean display quality, when persons handle the LCD module for incoming inspection or assembly.

- (3) When the surface is dusty, please wipe gently with absorbent cotton or other soft material.

- (4) Wipe off saliva or water drops as soon as possible. If saliva or water drops contact with polarizer for a long time, they may cause deformation or color fading.

(5) When cleaning the adhesives, please use absorbent cotton wetted with a little petroleum benzene or other adequate solvent.

#### 9.6 Mechanism

(1) Please mount LCD module by using mounting holes arranged in four corners tightly.

## 9.7 Static Electricity

- (1) Protection film must remove very slowly from the surface of LCD module to prevent from electrostatic occurrence.

- (2) Because LCD modules use CMOS-IC on circuit board and TFT-LCD panel, it is very weak to electrostatic discharge. Please be careful with electrostatic discharge. Persons who handle the module should be grounded through adequate methods.

## 9.8 Strong Light Exposure

(1) The module shall not be exposed under strong light such as direct sunlight. Otherwise, display characteristics may be changed.

## 9.9 Disposal

(1) When disposing LCD module, obey the local environmental regulations.

#### 9.10 Others

- (1) AMIPRE will provide one year warrantee for all products, and three months warrantee for all repairing products.

- (2) Do not keep the LCD at the same display pattern continually. The residual image will happen and it will damage the LCD. Please use screen saver.

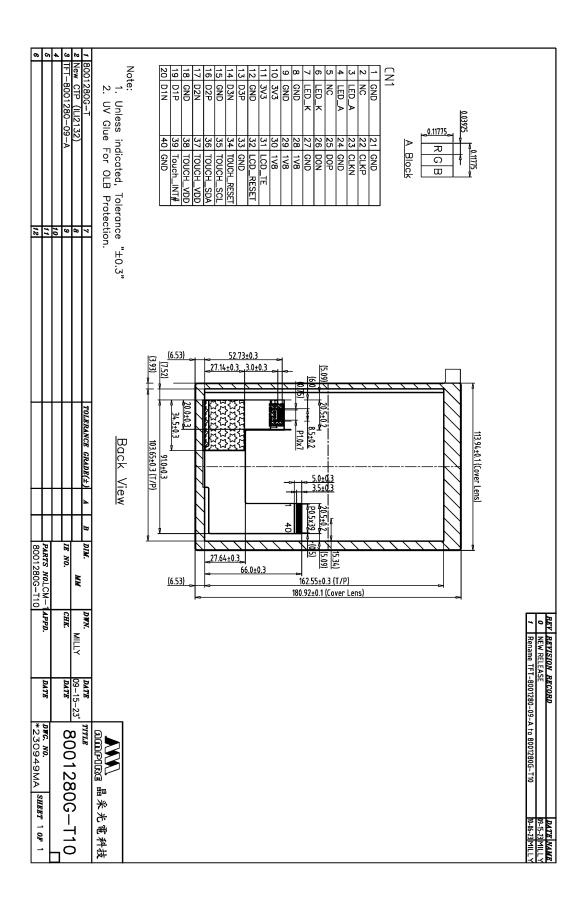

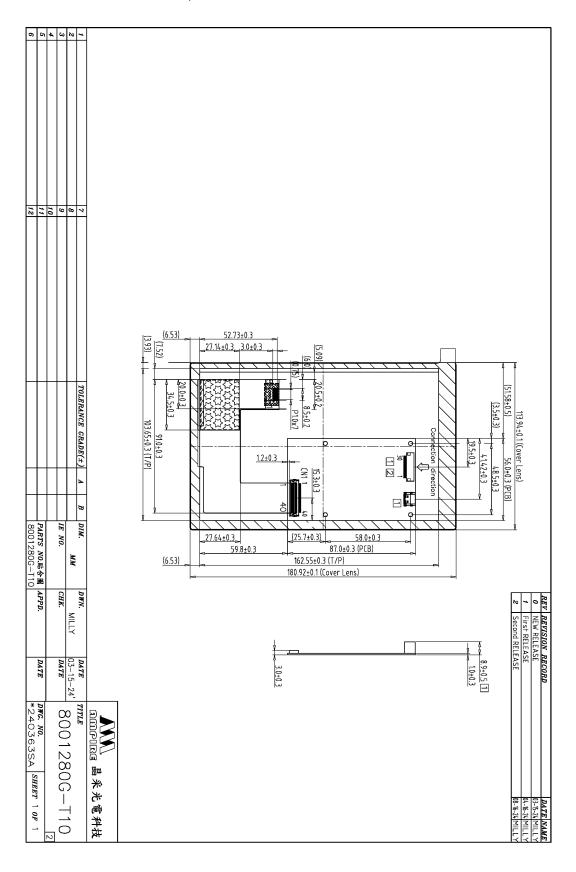

## 10. Outline Dimension

## 11. Bridge Board

PCB Outline: 87\*56 mm, 4L

## Interface

(1). CN1: Connector to LCM FPC (MIPI interface)

(2). CN2: CSF-2481-301R/P0.5 30PIN or equivalent. (4-lane MIPI)

| Pin | Signal name | Description                                           |

|-----|-------------|-------------------------------------------------------|

| 1   | GND         | Ground                                                |

| 2   | DSI_DP3     | MIPI DSI transmit differential signal 3 pair positive |

| 3   | DSI_DN3     | MIPI DSI transmit differential signal 3 pair negative |

| 4   | GND         | Ground                                                |

| 5   | DSI_DP2     | MIPI DSI transmit differential signal 2 pair positive |

| 6   | DSI_DN2     | MIPI DSI transmit differential signal 2 pair negative |

| 7   | GND         | Ground                                                |

| 8   | DSI_DP1     | MIPI DSI transmit differential signal 1 pair positive |

| 9   | DSI_DN1     | MIPI DSI transmit differential signal 1 pair negative |

| 10  | GND         | Ground                                                |

| 11  | DSI_DP0     | MIPI DSI transmit differential signal 0 pair positive |

| 12  | DSI_DN0     | MIPI DSI transmit differential signal 0 pair negative |

| 13  | GND         | Ground                                                |

| 14  | DSI_CKP     | MIPI DSI clock differential signal pair positive      |

| 15  | DSI_CKN     | MIPI DSI clock differential signal pair negative      |

| 16  | GND         | Ground                                                |

| 17  | DSI_TS_RST  | Touch screen reset output                             |

| 18  | DSI_TS_nINT | Touch screen interrupt input                          |

| 19  | I2C4_SDA    | I2C port 4 data                                       |

| 20  | I2C4_SCL    | I2C port 4 clock                                      |

| 21  | DSI_EN      | MIPI DSI backlight enable output                      |

| 22  | DSI_BL_PWM  | MIPI DSI backlight PWM output                         |

| 23  | GND         | Ground                                                |

| 24  | NC          | No connection                                         |

| 25  | NC          | No connection                                         |

| 26  | GND         | Ground                                                |

| 27  | NC          | No connection                                         |

| 28  | VSYS        | 5V power output                                       |

| 29  | VSYS        | 5V power output                                       |

| 30  | VSYS        | 5V power output                                       |

Date: 2024/10/07

(3). Type C USB Connector.

## 12. FFC

## P0.5xL 150mm 30pin

Connect bridge board CN3 and guest board MIPI connector.