# TRH031M 13.56MHz Multi-Protocol READER IC Short Specification Preliminary

### 3ALogics Inc.

7th Floor, Hyundai-Office Bldg, 9-4, Sunae-dong, Bundang-gu, Seongnam-si,

Gyeonggi-do, 463-783, Korea

TEL: +82-31-715-7117 FAX: +82-31-719-7551

Web-site: http://www.3alogics.com

### **Table of Contents**

- 1. Product Overview

- 2. Feature

- 3. Block Diagram

- 4. Pin Assignment

- 5. Pin Descriptions

- 6. Electrical Characteristics

- 7. Package Dimension

# 1 PRODUCT OVERVIEW

TRH031M is a highly integrated multi-protocol reader IC for contactless communication at 13.56MHz. This Chip supports all layers of the ISO14443 Type A, Type B and ISO 15693 standard communication protocol.

The internal transmitter part is able to drive an antenna designed for proximity operation distance (up to 100mm) directly without additional active circuitry. TRH031M also support vicinity standard card protocol ISO 15693). TRH031M can communicate up to 1.5M with external power amplifier in ISO 15693 mode.

The receiver part of TRH031M provides a robust and efficient implementation of a demodulation and decoding circuitry for signals form ISO14443 Type A, Type B and ISO 15693 compatible cards. The receiver and transmitter part works in 3V supply voltage.

The Digital part of TRH031M handles the complete framing and error detection. Also it supports parallel and serial interface which can be directly connected to any 8-bit u-Processor.

# 2 FEATURES

- Highly integrated analog circuitry to demodulate and decode card response

- Buffered output drivers to connect an antenna with minimum number of external components

- Proximity operating distance (up to 100mm)

- Supports ISO/IEC 14443 Type A, Type B and ISO 15693 standards

- Parallel u-Processor interface with internal address latch and IRQ line

- Automatic external Interface type detection

- Automatic and flexible interrupt handling

- Comfortable 64-byte send and receive FIFO-buffer

- Bit- and Byte-oriented framing

- Supports hard reset with low power function and power down control

- Programmable 8-bit timer with pre-scaler

- 3.3V operation for analog Interface

- 3.3V operation for the digital part

- Internal oscillator buffer to connect 13.56 MHz quartz

- Independent power supply pins for digital, analog and transmitter part

- Supports SPI compatible serial interface

- Supports unique card detection function for low power consumption application

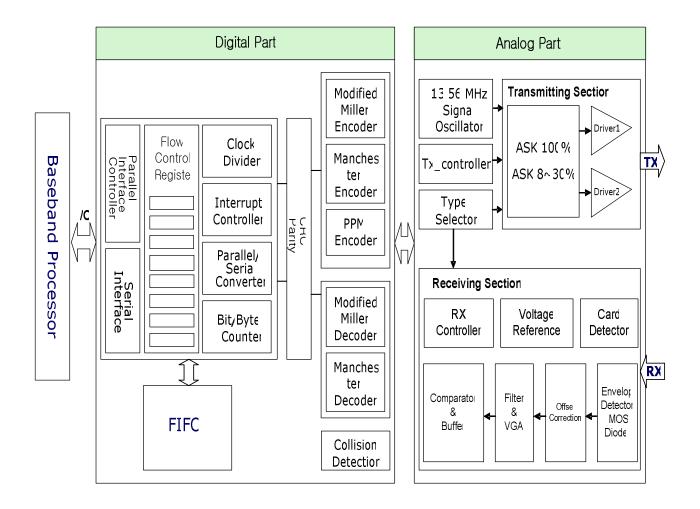

# 3 BLOCK DIAGRAM

Figure 1. TRH031M Block Diagram

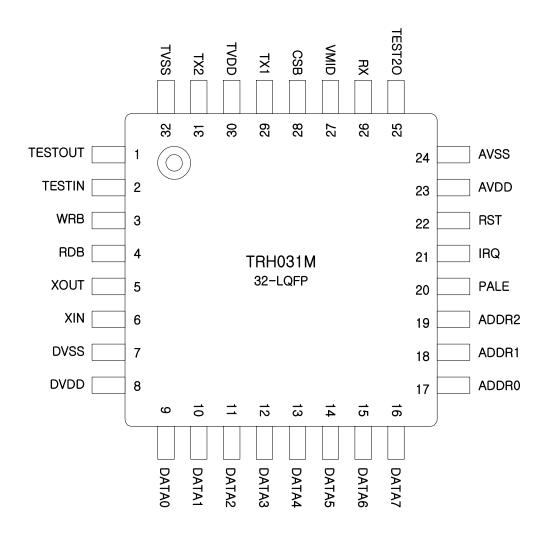

# 4 PIN ASSIGNMENT

Figure 2. TRH031M Pin Assignment (32-LQFP)

# 5 PIN DESCRIPTIONS

| Pin Name         | Type | Pin Description                                                                                                                                                                                                                      |        |

|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| TX1              | О    | Transmitter 1:delivers the modulated 13.56MHz energy carrier                                                                                                                                                                         | 29     |

| TX2              | О    | Transmitter 2;delivers the modulated 13.56MHz energy carrier                                                                                                                                                                         | 31     |

| WRB              | I    | Not Write: strobe to write data(applied on D0 to D7) into the MF RC500 register                                                                                                                                                      | 3      |

| R/NW             | I    | Read Not Write: selects if a read or write cycle shall be performed.                                                                                                                                                                 |        |

| RDB              | I    | Not Read: strobe to read data from the MF RC500 register(applied on D0 to D7)                                                                                                                                                        | 4      |

| NDS              | I    | Not Data Strobe: strobe for the read and the write cycle                                                                                                                                                                             |        |

| PALE             | Ι    | Address Latch Enable: strobe signal to latch DATA0 to DATA5 into the internal address latch when HIGH                                                                                                                                | 20     |

| ADDR0            | I    | Address Line 1: Bit 0 of register address                                                                                                                                                                                            | 17     |

| ADDR1            | I    | Address Line 1: bit 1 of register address                                                                                                                                                                                            | 18     |

| ADDR2            | I    | Address Line 2: bit 2 of register address                                                                                                                                                                                            | 19     |

| RX               | I    | Receiver Input: Input pin for the cards response, which is the load modulated 13.56MHz energy carried, that is coupled out from the antenna circuit.                                                                                 |        |

| RST              | I    | Reset and Power Down: When HIGH, internal current sinks are switched off, the oscillator is inhibited, and the input pads are disconnected from the outside world. With a negative edge on this pin the internal reset phase starts. | 22     |

| XIN              | I    | 13.56MHz Crystal Oscillator Input                                                                                                                                                                                                    | 6      |

| XOUT             | О    | Crystal Oscillator Output: Output of the inverting amplifier of the oscillator.                                                                                                                                                      | 5      |

| IRQ              | О    | Interrupt Request: output to signal an interrupt event                                                                                                                                                                               | 21     |

| TEST2O           | О    | Auxiliary Output: This pin delivers analog test signals. Used for factory test                                                                                                                                                       | 25     |

| TESTIN           | I    | Used at Factory Test                                                                                                                                                                                                                 | 2      |

| TEST1O           | О    | Used at Factory Test                                                                                                                                                                                                                 | 1      |

| VMID             | PWR  | Internal reference voltage: This pin delivers the internal reference voltage.  Note: It has to be supported by means of a 100 nF block capacitor.                                                                                    | 27     |

| TVDD             | PWR  | Transmitter Power Supply; supplies the output stages of TX1 and TX2                                                                                                                                                                  | 30     |

| TVSS             | PWR  | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                         | 32     |

| DVDD             | PWR  | Digital Power Supply                                                                                                                                                                                                                 | 8      |

| DVSS             | PWR  | Digital Ground                                                                                                                                                                                                                       | 7      |

| AVDD             | PWR  | Analog Power Supply                                                                                                                                                                                                                  | 23     |

| AVSS             | PWR  | Analog Ground                                                                                                                                                                                                                        | 24     |

| DATA7 –<br>DATA0 | I/O  | 8-tib Bidirectional Data Bus(Dedicated Address Bus Mode) or Address/Data bus(Multiplexed Address Bus Mode)                                                                                                                           | 16 - 9 |

# 6 ELECTRICAL CHARACTERISTICS

### ABSOLUTE MAXIMUM RATINGS

| Symbol                     | Parameter                                   | MIN  | MAX     | UNIT |

|----------------------------|---------------------------------------------|------|---------|------|

| $T_{ m amb}, \ T_{ m sto}$ | Ambient or storage temperature range        | -45  | +150    | °C   |

| DVDD<br>AVDD<br>TVDD       | DC Power supply                             | -0.5 | 3.5     | V    |

| V <sub>in</sub>            | Absolute voltage on any digital pin to DVSS | -0.5 | DVDD+0. | V    |

| $V_{RX}$                   | Absolute voltage on RX pin to AVSS          | -0.5 | AVDD+0. | V    |

### **OPERATING CONDITION RANGE**

| Symbol    | Parameter                            | neter Conditions  |     | TYP | MAX | UNIT       |

|-----------|--------------------------------------|-------------------|-----|-----|-----|------------|

| $T_{amb}$ | Ambient or storage temperature range | -                 | -25 | +25 | +85 | $^{\circ}$ |

| DVDD      | Digital Power supply                 | DVSS=AVSS=TVSS=0V | 2.7 | 3.0 | 3.3 | V          |

| AVDD      | Analog Power supply                  | DVSS=AVSS=TVSS=0V | 2.7 | 3.0 | 3.3 | V          |

| TVDD      | Transmitter Power supply             | DVSS=AVSS=TVSS=0V | 2.7 | 3.0 | 3.3 | V          |

### **CURRENT CONSUMPTION**

| Symbol        | Parameter                  | Conditions                                       | MIN | ТҮР | MAX  | UNI<br>T |

|---------------|----------------------------|--------------------------------------------------|-----|-----|------|----------|

|               | Digital Supply current     | Idle Command                                     |     | 6   | 12   | mA       |

| $I_{DVDD}$    |                            | Soft Power Down mode                             | 500 | 800 | 1500 | uA       |

|               |                            | Hard Power Down mode                             | 0.5 | 1   | 5    | uA       |

|               | Analog Supply current      | Idle Command, Receiver On                        | 15  | 25  | 50   | mA       |

| $ m I_{AVDD}$ |                            | Idle Command, Receiver Off                       | 5   | 8   | 17   | mA       |

| AVDD          |                            | Soft Power Down mode                             | 0.5 | 1   | 5    | uA       |

|               |                            | Hard Power Down mode                             | 0.5 | 1   | 5    | uA       |

|               |                            | Continuous Wave                                  | 50  | 100 | 150  | mA       |

| $I_{TVDD}$    | Transmitter Supply current | TX1 and TX2 unconnected,<br>TX1RFEn, TX2RFEn = 1 | 3   | 5   | 10   | mA       |

|               |                            | TX1 and TX2 unconnected,<br>TX1RFEn, TX2RFEn = 0 | 40  | 60  | 150  | uA       |

### STANDARD INPUT PIN CHARACTERISTICS

| Symbol     | Parameter             | Conditions   | MIN      | MAX      | UNIT |

|------------|-----------------------|--------------|----------|----------|------|

| $I_{leak}$ | Input Leakage Current | -            | -1.0     | +1.0     | uA   |

| $V_{T}$    | Threshold             | DVDD < 3.0 V | 0.35DVDD | 0.65DVDD | V    |

**<sup>※</sup>** DATA0 to DATA7, ADDR0, ADDR1 have CMOS input characteristics.

### SCHMITT TRIGGER INPUT PIN CHARACTERISTICS

| Symbol                       | Parameter                | Conditions   | MIN      | MAX      | UNIT |

|------------------------------|--------------------------|--------------|----------|----------|------|

| $\mathbf{I}_{\mathrm{leak}}$ | Input Leakage Current    | -            | -1.0     | +1.0     | uA   |

| $V_{T+}$                     | Positive-Going Threshold | DVDD < 3.0 V | 0.35DVDD | 0.65DVDD | V    |

| $V_{T-}$                     | Negative-Going Threshold | DVDD < 3.0 V | 0.35DVDD | 0.65DVDD | V    |

**※** CSB, WRB, RDB, PALE, TESTIN has Schmitt-Trigger characteristics.

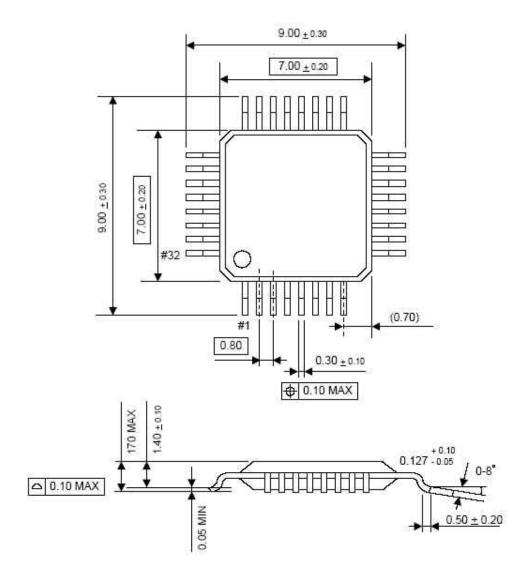

# 7 PACKAGE DIMENSIONS

Figure 3. 32-pin LQFP Package Dimension