Preliminary Data Sheet, V0.9, April 2008

# PMA7110

RF Transmitter IC with embedded 8051 Microcontroller, LF 125kHz ASK Receiver and FSK/ASK 315/434/868/915 MHz Transmitter

Sense & Control

Never stop thinking

Edition 2008-04-28 Published by Infineon Technologies AG, Am Campeon 1-12 85579 Neubiberg, Germany © Infineon Technologies AG 2008-04-28. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or the Infineon Technologies Companies and our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

RF Transmitter IC with embedded 8051 Microcontroller, LF 125kHz ASK Receiver and FSK/ASK 315/434/868/915 MHz Transmitter

Sense & Control

Never stop thinking

#### Revision History:2008-04-28

V0.9

| Page 129           | update typical value of transmit current consumption                                    |

|--------------------|-----------------------------------------------------------------------------------------|

| Page 132           | Update RF characterization for D9 ~ D17                                                 |

| Page 128, Page 141 | Update flash code/data memory program temeprature and erase cycle: B4, O1, O2, O6 ~ O8. |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

|                    |                                                                                         |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: sensors@infineon.com

| 1.1       Overview       9         1.2       Features       10         1.3       Applications       10         2       Functional Description       11         2.1       Pin Description       11         2.2       Functional Block Diagram       28         2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.5.1       Sensor Interfaces and Data Acquisition       41                                                                                                                        | 1       | Product Description        | 9  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------|----|

| 1.3       Applications       10         2       Functional Description       11         2.1       Pin Description       11         2.2       Functional Block Diagram       28         2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.5.1       Sensor Interface and Data Acquisition       41         2.5.1.3       Interface to other s                                                                                                          | 1.1     | Overview                   | 9  |

| 2       Functional Description       11         2.1       Pin Description       11         2.2       Functional Block Diagram       28         2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.3       Interface to other signals       44         2.5.1.4       R                                                                                                          | 1.2     | Features                   | 10 |

| 2.1       Pin Description       11         2.2       Functional Block Diagram       28         2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.1       Sensor Interface       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43 <tr< td=""><td>1.3</td><td>Applications</td><td> 10</td></tr<>                               | 1.3     | Applications               | 10 |

| 2.2       Functional Block Diagram       28         2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.1       Sensor Interface       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43         2.5.1.3       Interface to other signals       44         2.5.1.4       Reference voltages       44 </td <td>2</td> <td></td> <td></td>                                               | 2       |                            |    |

| 2.3       Operating Modes and States       29         2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TIMAX Detector       40         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.1       Sensor Interface       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46                                                                                        | 2.1     |                            |    |

| 2.3.1       Operating mode selection       29         2.3.2       State Description       32         2.3.2.1       INIT State       32         2.3.2.2       RUN State       33         2.3.2.3       IDLE State       33         2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.5.6       Functional Block Description       41         2.5.1       Sensor Interface and Data Acquisition       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46         2.5.1.6       Battery Voltage Monitor       46                                                                               | 2.2     | Functional Block Diagram   | 28 |

| 2.3.2       State Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.3     | Operating Modes and States | 29 |

| 2.3.2.1       INIT State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3.1   | Operating mode selection   | 29 |

| 2.3.2.2       RUN State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.3.2   | State Description          | 32 |

| 2.3.2.3       IDLE State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3.2.1 | INIT State                 | 32 |

| 2.3.2.4       POWER DOWN State       34         2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.4.5       Functional Block Description       41         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43         2.5.1.3       Interface to other signals       44         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46         2.5.2       Memory Organization and Special Function Registers (SFR)       47         2.5.2.1       ROM       48         2.5.2.3 </td <td>2.3.2.2</td> <td>RUN State</td> <td> 33</td> | 2.3.2.2 | RUN State                  | 33 |

| 2.3.2.5       THERMAL SHUTDOWN state       34         2.3.2.6       State Transitions       35         2.3.2.7       Status of PMA7110 Blocks in Different States       37         2.4       Fault protection       40         2.4.1       Watchdog Timer       40         2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.4.5       Functional Block Description       41         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.3       Sensor Interface       41         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46         2.5.1.6       Battery Voltage Monitor       46         2.5.2       FLASH       49         2.5.2.1       ROM       48         2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers<                                                                                                          | 2.3.2.3 | IDLE State                 | 33 |

| 2.3.2.6State Transitions352.3.2.7Status of PMA7110 Blocks in Different States372.4Fault protection402.4.1Watchdog Timer402.4.2VMIN Detector402.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.4.6TMAX Detector402.4.7Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.3.2.4 | POWER DOWN State           | 34 |

| 2.3.2.6State Transitions352.3.2.7Status of PMA7110 Blocks in Different States372.4Fault protection402.4.1Watchdog Timer402.4.2VMIN Detector402.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.4.6TMAX Detector402.4.7Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.3.2.5 | THERMAL SHUTDOWN state     | 34 |

| 2.3.2.7Status of PMA7110 Blocks in Different States372.4Fault protection402.4.1Watchdog Timer402.4.2VMIN Detector402.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.4.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.2FLASH492.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.2.6 |                            |    |

| 2.4Fault protection402.4.1Watchdog Timer402.4.2VMIN Detector402.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.4.5TMAX Detector402.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.3.2.7 |                            |    |

| 2.4.1Watchdog Timer402.4.2VMIN Detector402.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.4.5TMAX Detector402.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.4     |                            |    |

| 2.4.2       VMIN Detector       40         2.4.3       FLASH Memory Checksum       40         2.4.4       ADC Measurement Overflow & Underflow       40         2.4.5       TMAX Detector       40         2.4.5       TMAX Detector       40         2.5       Functional Block Description       41         2.5.1       Sensor Interfaces and Data Acquisition       41         2.5.1.1       Sensor Interface       41         2.5.1.2       Two differential high sensitive interfaces to external Sensors       43         2.5.1.3       Interface to other signals       44         2.5.1.4       Reference voltages       44         2.5.1.5       Temperature Sensor       46         2.5.1.6       Battery Voltage Monitor       46         2.5.2       Memory Organization and Special Function Registers (SFR)       47         2.5.2.1       ROM       48         2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers       51         2.5.3       Microcontroller       57         2.5.4       System Configuration Registers       58         2.5.5       General Purpose Registers (GPR) </td <td>2.4.1</td> <td></td> <td></td>                        | 2.4.1   |                            |    |

| 2.4.3FLASH Memory Checksum402.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.1Sensor Interface412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.4.2   |                            |    |

| 2.4.4ADC Measurement Overflow & Underflow402.4.5TMAX Detector402.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.4.3   |                            |    |

| 2.4.5TMAX Detector402.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.1Sensor Interface412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.4.4   |                            |    |

| 2.5Functional Block Description412.5.1Sensor Interfaces and Data Acquisition412.5.1.1Sensor Interface412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.4.5   |                            |    |

| 2.5.1Sensor Interfaces and Data Acquisition412.5.1.1Sensor Interface412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5     |                            |    |

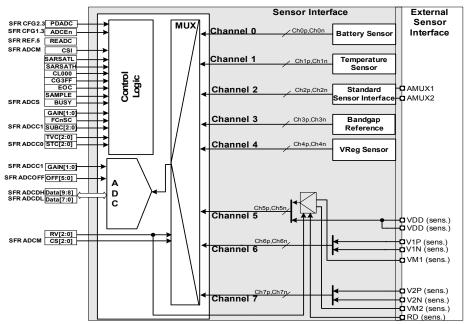

| 2.5.1.1Sensor Interface412.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.5.1   |                            |    |

| 2.5.1.2Two differential high sensitive interfaces to external Sensors432.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.5.1.1 |                            |    |

| 2.5.1.3Interface to other signals442.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5.1.2 |                            |    |

| 2.5.1.4Reference voltages442.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.5.1.3 |                            |    |

| 2.5.1.5Temperature Sensor462.5.1.6Battery Voltage Monitor462.5.2Memory Organization and Special Function Registers (SFR)472.5.2.1ROM482.5.2.2FLASH492.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.5.1.4 |                            |    |

| 2.5.1.6       Battery Voltage Monitor       46         2.5.2       Memory Organization and Special Function Registers (SFR)       47         2.5.2.1       ROM       48         2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers       51         2.5.3       Microcontroller       57         2.5.4       System Configuration Registers       58         2.5.5       General Purpose Registers (GPR)       61         2.5.6       System Controller       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.5.1.5 |                            |    |

| 2.5.2       Memory Organization and Special Function Registers (SFR)       47         2.5.2.1       ROM       48         2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers       51         2.5.3       Microcontroller       57         2.5.4       System Configuration Registers       58         2.5.5       General Purpose Registers (GPR)       61         2.5.6       System Controller       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.5.1.6 |                            |    |

| 2.5.2.1       ROM       48         2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers       51         2.5.3       Microcontroller       57         2.5.4       System Configuration Registers       58         2.5.5       General Purpose Registers (GPR)       61         2.5.6       System Controller       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.5.2   |                            |    |

| 2.5.2.2       FLASH       49         2.5.2.3       RAM       51         2.5.2.4       Special Function Registers       51         2.5.3       Microcontroller       57         2.5.4       System Configuration Registers       58         2.5.5       General Purpose Registers (GPR)       61         2.5.6       System Controller       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.5.2.1 |                            |    |

| 2.5.2.3RAM512.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.5.2.2 |                            |    |

| 2.5.2.4Special Function Registers512.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.5.2.3 |                            |    |

| 2.5.3Microcontroller572.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.5.2.4 |                            |    |

| 2.5.4System Configuration Registers582.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                            |    |

| 2.5.5General Purpose Registers (GPR)612.5.6System Controller62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                            |    |

| 2.5.6 System Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                            |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                            |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.5.6.1 | Wakeup Logic               |    |

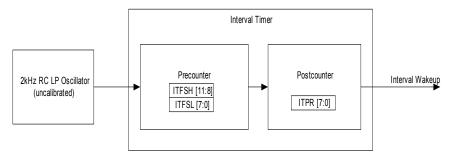

| 2.5.6.2 Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                            |    |

| 2.5.6.3  | Interval Timer Calibration                                 | 69  |

|----------|------------------------------------------------------------|-----|

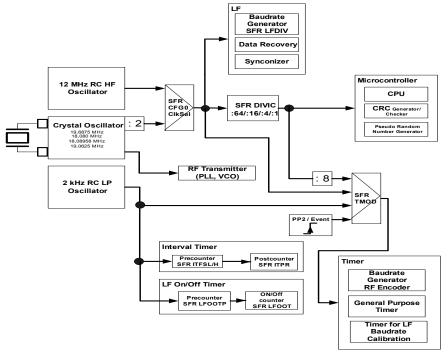

| 2.5.7    | Clock Controller                                           |     |

| 2.5.7.1  | 2 kHz RC LP Oscillator (Low Power)                         | 71  |

| 2.5.7.2  | 12 MHz RC HF Oscillator (High Frequency)                   | 71  |

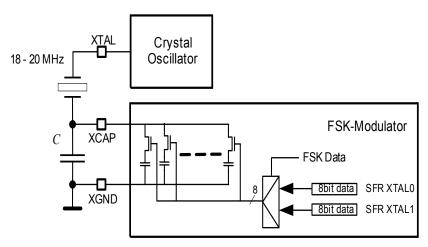

| 2.5.7.3  | Crystal Oscillator                                         | 71  |

| 2.5.8    | Interrupt Sources on the <dev_nameshort1></dev_nameshort1> | 74  |

| 2.5.9    | RF 315/434/868/915 MHz FSK/ASK Transmitter                 | 78  |

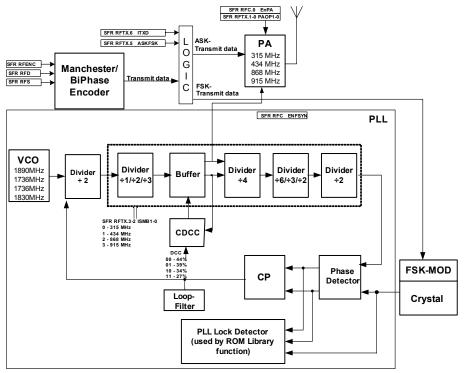

| 2.5.9.1  | Phase Locked Loop PLL                                      | 79  |

| 2.5.9.2  | Power Amplifier PA                                         |     |

| 2.5.9.3  | ASK Modulator                                              | 80  |

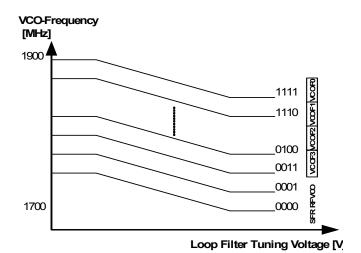

| 2.5.9.4  | Voltage Controlled Oscillator (VCO)                        |     |

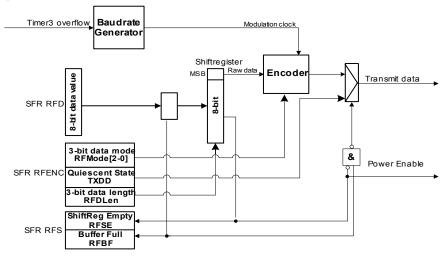

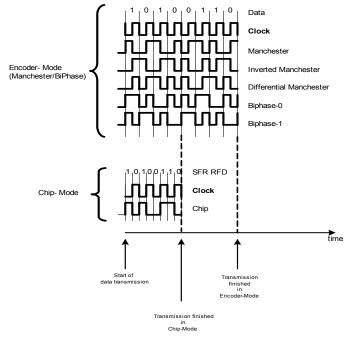

| 2.5.9.5  | Manchester/BiPhase Encoder with bit Rate Generator         | 81  |

| 2.5.10   | LF Receiver                                                |     |

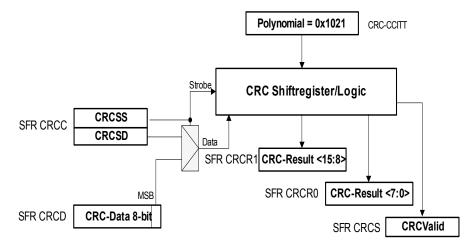

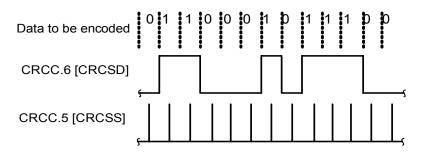

| 2.5.11   | 16Bit CRC (Cyclic Redundancy Check) Generator/Checker      | 86  |

| 2.5.12   | Pseudo Random Number Generator                             | 89  |

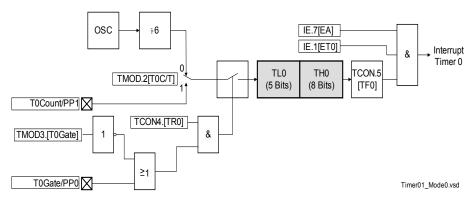

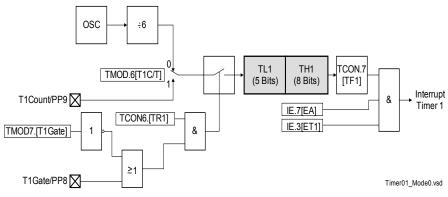

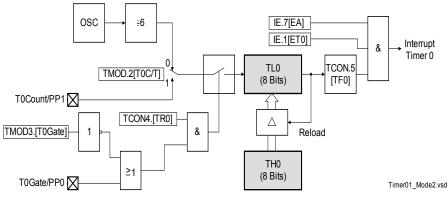

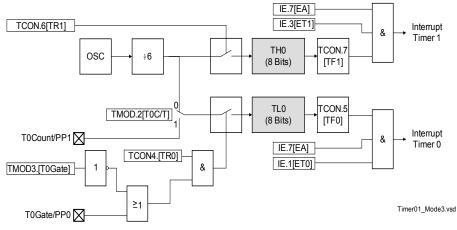

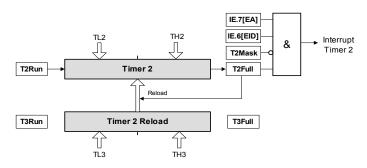

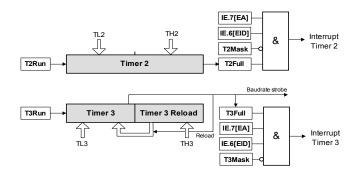

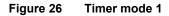

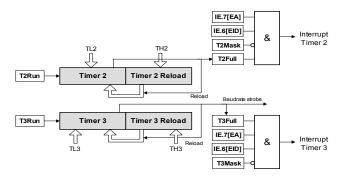

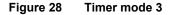

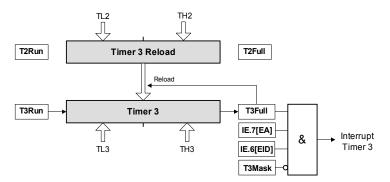

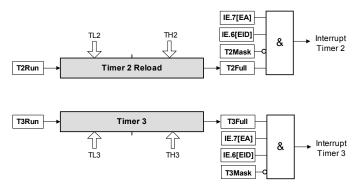

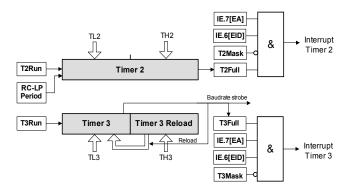

| 2.5.13   | Timer Unit (Timer 0, Timer 1, Timer 2, Timer 3)            | 90  |

| 2.5.13.1 | Basic Timer Configuration                                  |     |

| 2.5.13.2 | General Operation Description Timer 0 and Timer 1          |     |

| 2.5.13.3 | Timer Modes for Timer 2 and Timer 3                        |     |

| 2.5.14   | General Purpose Input/Output (GPIO)                        |     |

| 2.5.14.1 | Peripheral Port Basic Configuration                        | 105 |

| 2.5.14.2 | Spike Suppression on Input Pins                            |     |

| 2.5.14.3 | External Wakeup on PP1-PP4 and PP6-PP9                     |     |

| 2.5.14.4 | Alternative Port Functionality                             |     |

| 2.5.15   | I2C- Interface                                             |     |

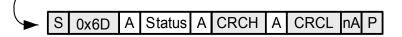

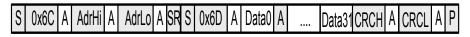

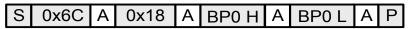

| 2.5.15.1 | Slave mode sequence                                        |     |

| 2.5.15.2 | General call sequence                                      | 114 |

| 2.5.15.3 | Master mode sequence                                       |     |

| 2.5.16   | Serial Peripheral Interface SPI                            |     |

| 2.5.17   | PROGRAMMING mode Operation                                 |     |

| 2.5.17.1 | FLASH Write Line                                           |     |

| 2.5.17.2 | FLASH Erase                                                | 118 |

| 2.5.17.3 | FLASH Check Erase Status                                   | 120 |

| 2.5.17.4 | FLASH Read Line                                            |     |

| 2.5.17.5 | FLASH Set Lockbyte 2                                       |     |

| 2.5.17.6 | FLASH Set Lockbyte 3                                       |     |

| 2.5.17.7 | Read Status                                                |     |

| 2.5.18   | DEBUG mode Operation                                       |     |

| 2.5.18.1 | Debug Special Function Registers                           |     |

| 2.5.18.2 | Debugging Facility                                         |     |

| 2.5.18.3 | Debugger Commands                                          |     |

| 3        | Reference                                                  |     |

| 3.1   | Electrical Data          | 126 |

|-------|--------------------------|-----|

| 3.1.1 | Absolute Maximum Ratings | 126 |

| 3.1.2 | Operating Range          | 127 |

| 3.1.3 | Product Characteristics  | 128 |

| 3.2   | Reference SFR Registers  | 144 |

| 3.3   | Reference Documents      | 157 |

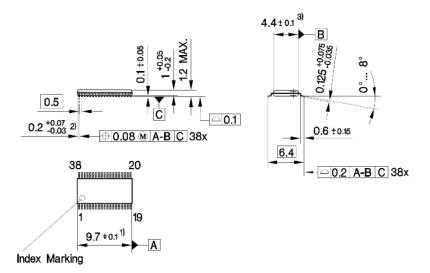

| 4     | Package Outlines         | 158 |

#### **Product Description**

# 1 Product Description

# 1.1 Overview

The PMA7110 is a low power wireless FSK/ASK Transmitter with embedded microcontroller, which offers a single chip solution for various industrial, consumer and automotive applications in frequency bands 315/434/868/915 MHz. With its highly integrated mixed signal peripherals, PMA7110 requires only few external components. The operating voltage range is 1.9 - 3.6 V.

The PMA7110 contains

- 8051 based microcontroller

- Advanced power control system to minimize power consumption

- RF transmitter

- LF receiver

- Multifunctional interface for external Sensors and embedded temperature and battery voltage sensor

Measurement via embedded temperature and voltage sensor, reading signal from analog inputs (e.g. from external analog sensor) are performed under software control, so that the microcontroller can format and prepare this data for the RF transmission.

An intelligent power control system enables the build of ultra low power applications by using powersaving modes.

The integrated microcontroller is instruction set compatible to the standard 8051 processor. It is equipped with various peripherals (e.g. a hardware Manchester/BiPhase Encoder/Decoder and CRC Generator/Checker) enabling an easy implementation of customer-specific applications.

The low power consumption FSK/ASK Transmitter for 315/434/868/915 MHz frequency bands contains a fully integrated VCO, a PLL synthesizer, an ASK/ FSK modulator and an efficient power amplifier. Fine tuning of the center frequency can be done by an on-chip capacitor bank.

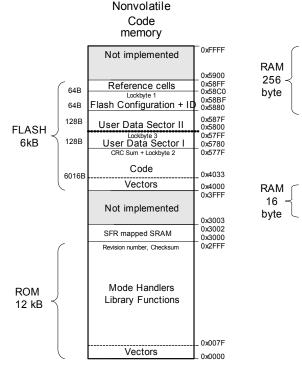

To store the microcontroller application program code and its unique ID-Number, an onchip FLASH memory is integrated. Additional ROM storage is provided for the ROM library functions covering standard tasks required by various applications.

## **Product Description**

# 1.2 Features

- Supply voltage range from 1.9 V up to 3.6 V

- Operating temperature range -40 to +85 °C

- Low supply current

- Temperature sensor

- Battery voltage measurement

- Integrated RF- transmitter for ISM band 315/434/868/915 MHz

- Selectable transmit power 5/8/10 dBm into 50 Ohm load

- · Transmit data rates up to 32kbit/s or 64kchips/s in manchester code

- FSK/ASK modulation capability

- Frequency deviation up to 100 kHz in FSK mode

- Fully integrated VCO and PLL synthesizer

- Crystal oscillator tuning on chip

- LF receiver with input signal amplitude of min. 0.25 mVpp

- LF receiver data rate from 2000 bit up to 4000 bit (Manchester/BiPhase coded)

- 8051 instruction set compatible microcontroller (cycle-optimized)

- 6 kbyte Flash Code and 2x128 bytes flash data memory (for user-application like EEPROM emulation)

- 12 kbyte ROM (for ROM library functions)

- 256 bytes RAM (128 bytes configurable to keep content in Power Down mode), 16 bytes XData memory (supplied in PowerDown)

- I<sup>2</sup>C bus interface

- SPI bus interface

- 10 free programmable bidirectional GPIO pins with on chip pull-up/down resistors

- 4 independent 16 bit timers

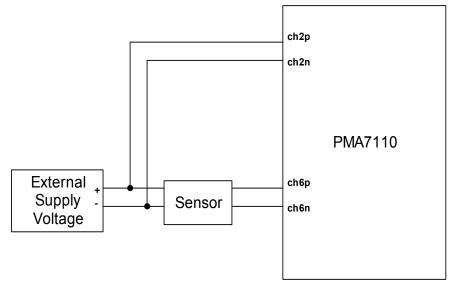

- 10bit ADC with 3 pair differential channels (e.g. as IO for external sensors)

- Wakeup from POWER DOWN state using the Interval Timer, the LF receiver or external wakeup sources connected via a GPIO

- · Manchester/BiPhase encoder and decoder

- Hardware CRC generator

- Pseudo Random Number Generator

- · Watchdog timer

- on chip debugging via I<sup>2</sup>C interface

# Note:In PMA7110 the Thermal Shout down function is not used.

# 1.3 Applications

- · Remote control systems for industrial and consumer applications

- Security- and Alarm-systems

- Home automation systems

- Automatic meter reading

- Active Tagging

# 2 Functional Description

# 2.1 Pin Description

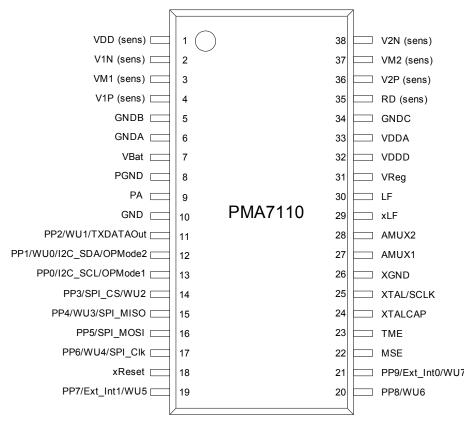

#### Figure 1 Pin-out of PMA7110 in TSSOP38 package

| Table |                                 |         |                                                                                      |                                           |  |  |

|-------|---------------------------------|---------|--------------------------------------------------------------------------------------|-------------------------------------------|--|--|

| Pin   | Name                            | Туре    | Description                                                                          | Comments                                  |  |  |

| 1     | VDD(sens.)                      | Supply  | Sensor positive supply                                                               | same voltage as chip<br>analog supply     |  |  |

| 2     | V1N(sens.)                      | Analog  | Channel1, negative sensor input                                                      | output of wheatstone<br>bridge sensor     |  |  |

| 3     | VM1(sens.)                      | Supply  | Sensor negative supply                                                               | same voltage as chip<br>GND               |  |  |

| 4     | V1P(sens.)                      | Analog  | Channel1, positive sensor input                                                      | output of wheatstone<br>bridge sensor     |  |  |

| 5     | GNDB                            | Supply  | Ground                                                                               |                                           |  |  |

| 6     | GNDA                            | Supply  | Ground                                                                               |                                           |  |  |

| 7     | VBat                            | Supply  | Battery supply voltage                                                               |                                           |  |  |

| 8     | PGND                            | Supply  | RF transmitter ground                                                                |                                           |  |  |

| 9     | PA                              | Analog  | RF transmitter output                                                                |                                           |  |  |

| 10    | GND                             | Analog  | Ground                                                                               |                                           |  |  |

| 11    | PP2/WU1/<br>TXDATAOut           | Digital | GPIO, External wakeup source,<br>Serial output of<br>Manchester/Biphase encoded data | internal<br>pullup/pulldown<br>switchable |  |  |

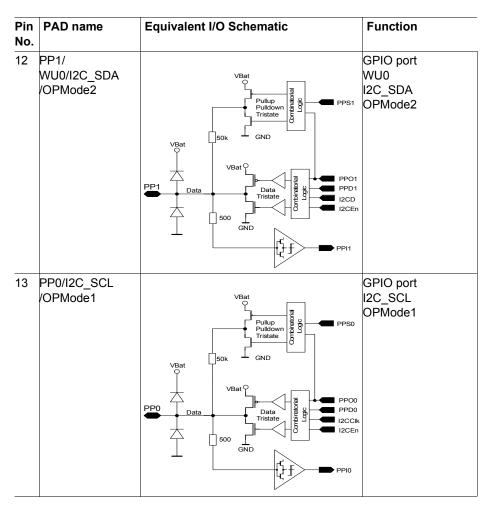

| 12    | PP1/WU0/<br>I2C_SDA/<br>OPMode2 | Digital | GPIO, External wakeup source, I2C<br>bus interface data, Select operation<br>mode    | internal<br>pullup/pulldown<br>switchable |  |  |

| 13    | PP0/<br>I2C_SCL/<br>OPMode1     | Digital | GPIO, I2C bus interface clock,<br>Select operation mode                              | internal<br>pullup/pulldown<br>switchable |  |  |

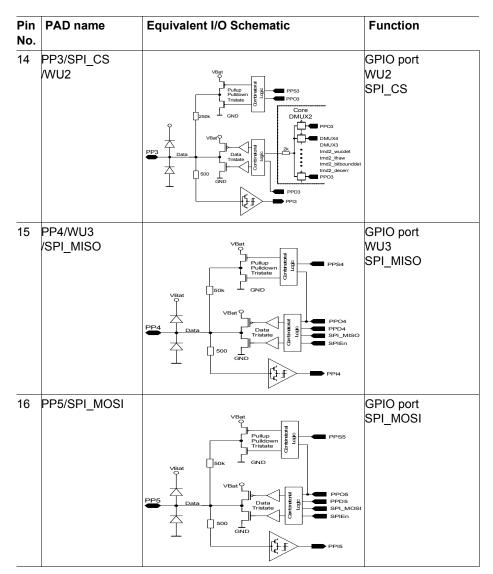

| 14    | PP3/SPI_CS/<br>WU2              | Digital | GPIO, SPI bus interface chip select,<br>External wakeup source                       | internal<br>pullup/pulldown<br>switchable |  |  |

| 15    | PP4/WU3<br>/SPI_MISO            | Digital | GPIO, SPI bus interface master in slave out, External wakeup source                  | internal<br>pullup/pulldown<br>switchable |  |  |

| 16    | PP5/<br>SPI_MOSI                | Digital | GPIO, SPI bus interface master out slave in                                          | internal<br>pullup/pulldown<br>switchable |  |  |

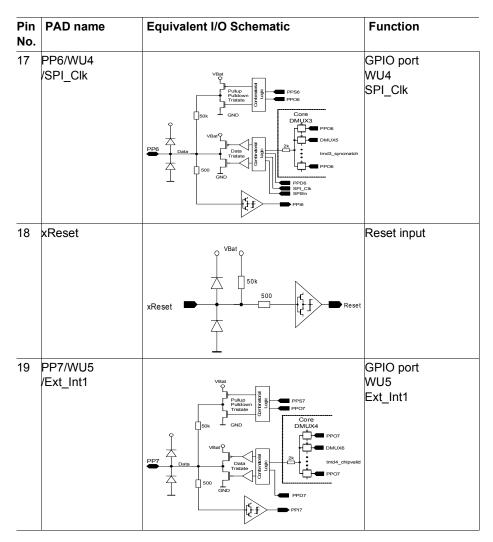

| 17    | PP6/WU4<br>/SPI_Clk             | Digital | GPIO, SPI bus interface clock,<br>External wakeup source                             | internal<br>pullup/pulldown<br>switchable |  |  |

#### Table 1 Pin Description

| lable | Fin Description      |         |                                                                    |                                                                                                |  |  |

|-------|----------------------|---------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| Pin   | Name                 | Туре    | Description                                                        | Comments                                                                                       |  |  |

| 18    | xReset               | Digital | External reset                                                     | low active                                                                                     |  |  |

| 19    | PP7/WU5<br>/Ext_Int1 | Digital | GPIO, External wakeup source                                       | internal<br>pullup/pulldown<br>switchable                                                      |  |  |

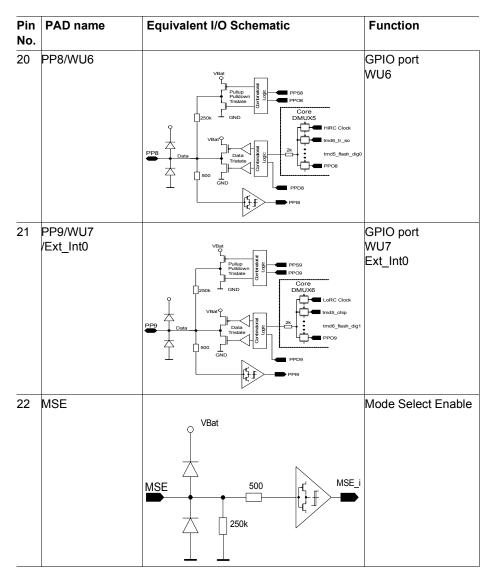

| 20    | PP8/WU6              | Digital | GPIO, External wakeup source                                       | internal<br>pullup/pulldown<br>switchable                                                      |  |  |

| 21    | PP9/WU7<br>/Ext_Int1 | Digital | GPIO, External wakeup source,<br>External Interrupt source         | internal<br>pullup/pulldown<br>switchable                                                      |  |  |

| 22    | MSE                  | Digital | Mode select enable                                                 | high active, set to GND in normal mode                                                         |  |  |

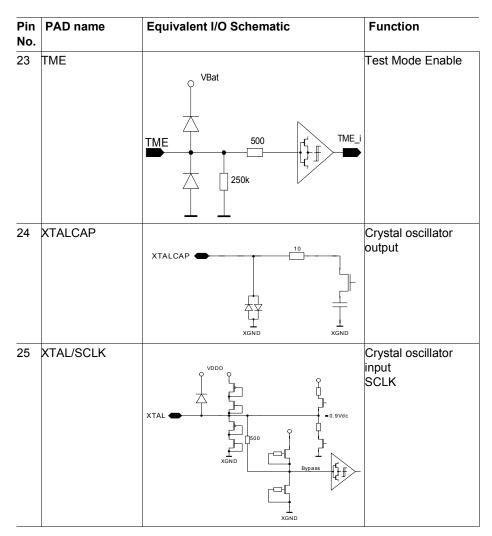

| 23    | TME                  | Digital | Test mode enable                                                   | high active, set to<br>GND in normal mode                                                      |  |  |

| 24    | XTALCAP              | Analog  | Crystal oscillator load capacitance                                |                                                                                                |  |  |

| 25    | XTAL/SCLK            | Analog  | Crystal oscillator input, External reference clock                 |                                                                                                |  |  |

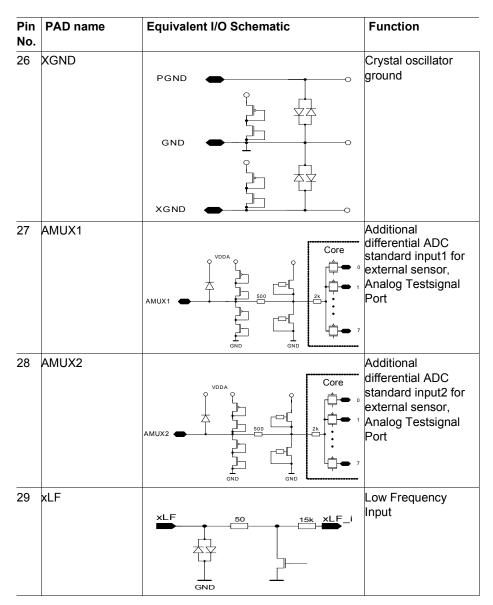

| 26    | XGND                 | Supply  | Crystal oscillator ground                                          |                                                                                                |  |  |

| 27    | AMUX1                | Analog  | additional differential ADC standard<br>input1 for external sensor | connect to GND if not<br>use                                                                   |  |  |

| 28    | AMUX2                | Analog  | additional differential ADC standard input2 for external sensor    | connect to GND if not<br>use                                                                   |  |  |

| 29    | XLF                  | Analog  | Differential LF receiver Input2                                    |                                                                                                |  |  |

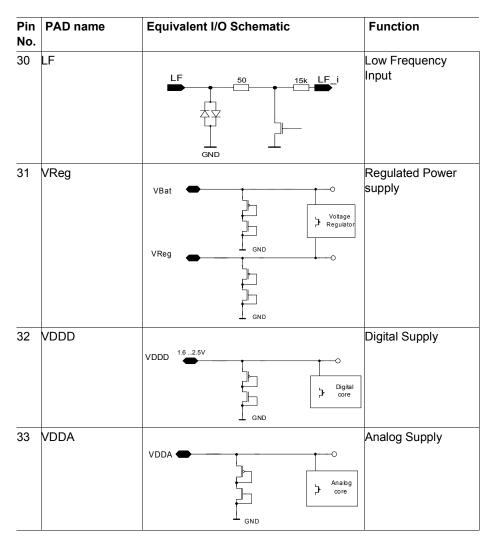

| 30    | LF                   | Analog  | Differential LF receiver Input1                                    |                                                                                                |  |  |

| 31    | VReg                 | Supply  | Internal voltage regulator output                                  | connect to<br>decoupling capacitor<br>(C <sub>BCAP</sub> =100nF)                               |  |  |

| 32    | VDDD                 | Supply  | Digital supply                                                     |                                                                                                |  |  |

| 33    | VDDA                 | Supply  | Analog supply                                                      |                                                                                                |  |  |

| 34    | GNDC                 | Supply  | Ground                                                             |                                                                                                |  |  |

| 35    | RD(sens.)            | Analog  |                                                                    | use only by having<br>diagnostic resistor on<br>sensor bridge,<br>otherwise none<br>connection |  |  |

# Table 1Pin Description

| Pin | Name       | Туре   | Description                     | Comments                              |

|-----|------------|--------|---------------------------------|---------------------------------------|

| 36  | V2P(sens.) | Analog | Channel2, positive sensor input | output of wheatstone<br>bridge sensor |

| 37  | VM2(sens.) | Supply | Sensor negative supply          | same voltage as chip<br>GND           |

| 38  | V2N(sens.) | Analog | Channel2, negative sensor input | output of wheatstone<br>bridge sensor |

Table 1Pin Description

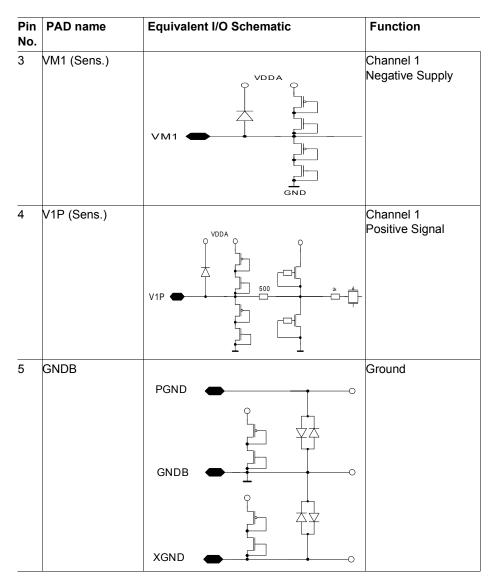

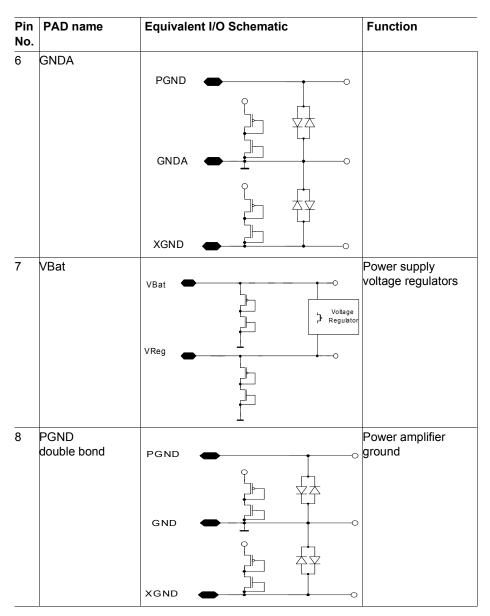

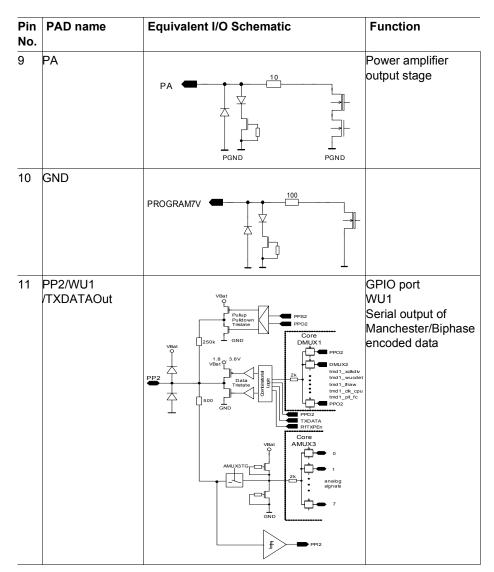

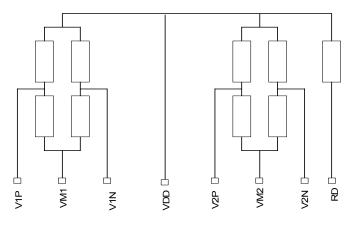

#### Table 2 Pin I/O equivalent schematics

| Pin<br>No. | PAD name    | Equivalent I/O Schematic | Function                                                                             |

|------------|-------------|--------------------------|--------------------------------------------------------------------------------------|

| 34         | GNDC        | PGND<br>O                | Ground                                                                               |

|            |             |                          |                                                                                      |

|            |             |                          |                                                                                      |

| 35         | RD (sens.)  |                          | Connect to<br>diagnostic resister<br>on sensor bridge,<br>otherwise no<br>connection |

| 36         | V2P (sens.) |                          | Channel 2<br>Positve Signal                                                          |

| Pin<br>No. | PAD name    | Equivalent I/O Schematic | Function                     |

|------------|-------------|--------------------------|------------------------------|

| 37         | VM2 (sens.) |                          | Channel 2<br>Negative Supply |

| 38         | V2N (sens.) |                          | Channel 2<br>Negative Signal |

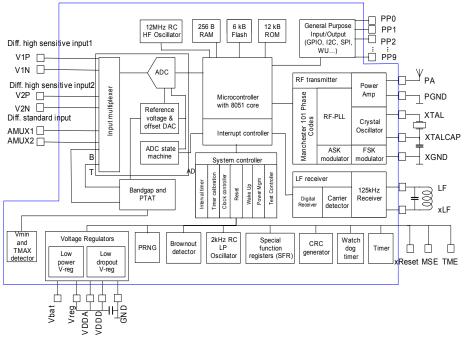

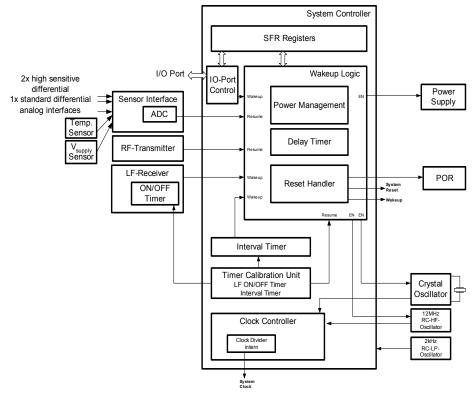

# 2.2 Functional Block Diagram

Figure 2 PMA7110 Block Diagram

# 2.3 Operating Modes and States

The PMA7110 can be operated in four different operating modes.

- NORMAL mode

- PROGRAMMING mode

- DEBUG mode

- (internal production TEST mode)

# 2.3.1 Operating mode selection

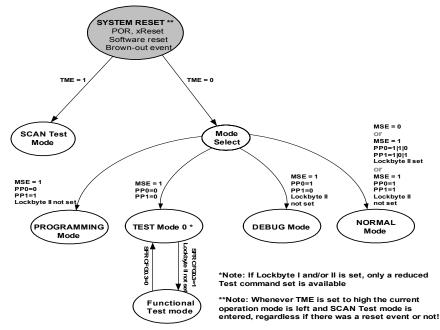

#### Figure 3 Operating mode selection of the PMA7110 after Reset

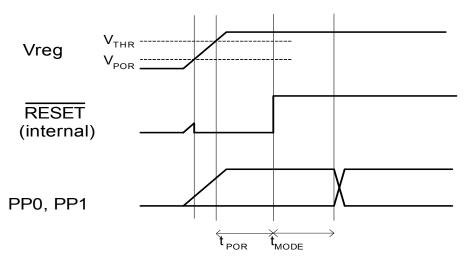

The Mode Select is entered after the System Reset expires and SCAN Test mode is not selected. The levels on the the I/O pins PP0 and PP1 are latched by the System controller and read by the operating system to determine the mode of operation of the device according to **Table 3 "Operating mode selection after Reset" on Page 30**. Therefore also the status of MSE and Lockbyte II from the FLASH are checked. The

MSE, PP0 and PP1 levels must not change after reset release during the whole  $t_{MODE}$  period (see Figure 5 "Power On Reset - operating mode selection" on Page 32).

| тме              | MSE | Lock<br>byte ll | PP0 | PP1 | Operating<br>mode | Devicecontrol               | Hardware<br>restrictions            |

|------------------|-----|-----------------|-----|-----|-------------------|-----------------------------|-------------------------------------|

| 1 <sup>3.)</sup> | х   | x               | x   | x   | SCAN              | external Test<br>machine    | n.a.                                |

| 0                | 0   | x               | х   | x   | NORMAL            | CPU executing<br>from 4000h | Flash write disabled <sup>2)</sup>  |

| 0                | 1   | x               | 0   | 0   | TEST              | TEST mode<br>handler        | None                                |

| 0                | 1   | not<br>set      | 0   | 1   | PROGRAMMING       | PROGRAM<br>mode handler     | None                                |

| 0                | 1   | set             | 0   | 1   | NORMAL            | CPU executing<br>from 4000h | Flash write disabled <sup>2.)</sup> |

| 0                | 1   | not<br>set      | 1   | 0   | DEBUG             | DEBUG mode<br>handler       | Flash write disabled <sup>2.)</sup> |

| 0                | 1   | set             | 1   | 0   | NORMAL            | CPU executing from 4000h    | Flash write disabled <sup>2.)</sup> |

| 0                | 1   | x               | 1   | 1   | NORMAL            | CPU executing<br>from 4000h | Flash write disabled <sup>2.)</sup> |

Table 3

Operating mode selection after Reset

1.) Flash protection is done by hardware. In these modes setting the SFR bits FCS.3 [PROG] and FCS.2 [ERASE] is not possible.

2.) Flash programming and erasing is only possible via ROM Library functions.

3.) Whenever TME is set to high the current mode is left immediately and SCAN Test Mode is entered, regardless if there is a reset or not.

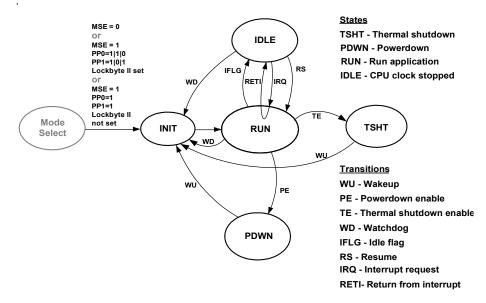

#### Figure 4 NORMAL Mode - State transistion diagram

For low power consumption and safety reasons the PMA7110 supports different operating states - *RUN* state, *IDLE* state and *POWER DOWN* mode and Thermal shutdown state. The device operation in these states is described below.