August 1984 Revised February 1999

## MM74HC4060 14 Stage Binary Counter

### **General Description**

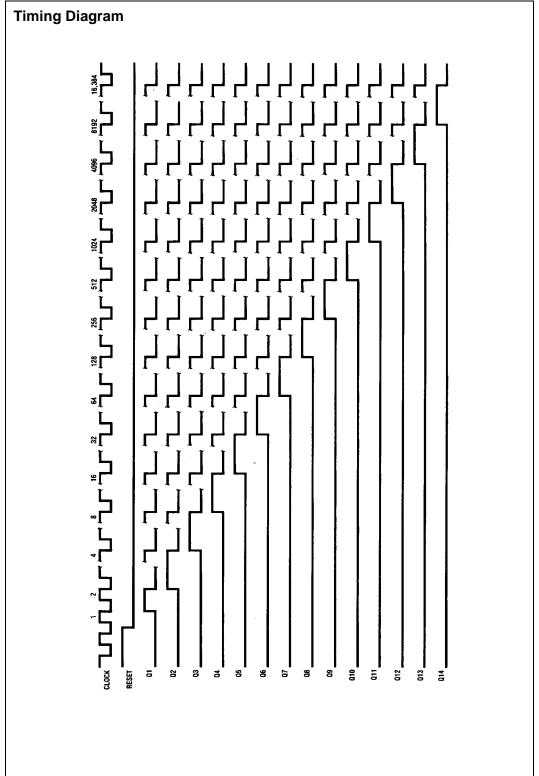

The MM74HC4060 is a high speed binary ripple carry counter. These counters are implemented utilizing advanced silicon-gate CMOS technology to achieve speed performance similar to LS-TTL logic while retaining the low power and high noise immunity of CMOS.

The MM74HC4060 is a 14-stage counter, which device increments on the falling edge (negative transition) of the input clock, and all their outputs are reset to a low level by applying a logical high on their reset input. The MM74HC4060 also has two additional inputs to enable easy connection of either an RC or crystal oscillator.

This device is pin equivalent to the CD4060. All inputs are protected from damage due to static discharge by protection diodes to  $V_{\rm CC}$  and ground.

### **Features**

- Typical propagation delay: 16 ns

- Wide operating voltage range: 2–6V

- Low input current: 1 μA maximum

- Low quiescent current: 80 µA maximum (74 Series)

- Output drive capability: 10 LS-TTL loads

### **Ordering Code:**

| 1             |                |                                                                              |  |  |  |

|---------------|----------------|------------------------------------------------------------------------------|--|--|--|

| Order Number  | Package Number | Package Description                                                          |  |  |  |

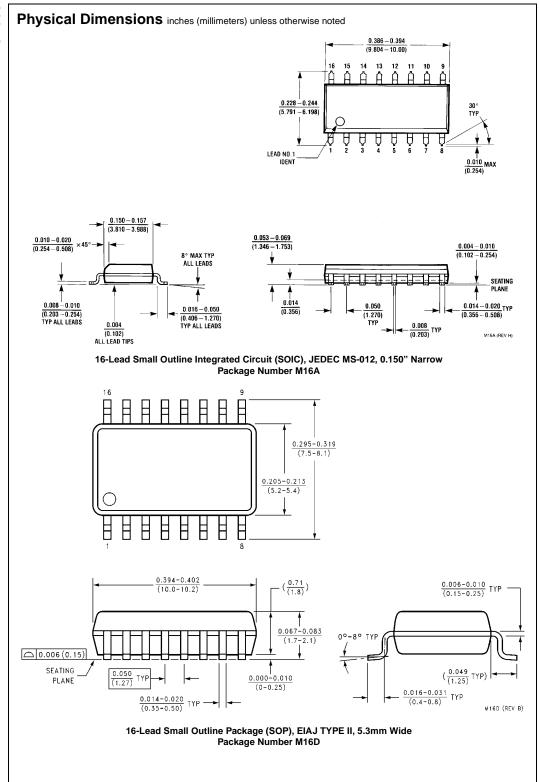

| MM74HC4060M   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |  |  |  |

| MM74HC4060SJ  | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide                |  |  |  |

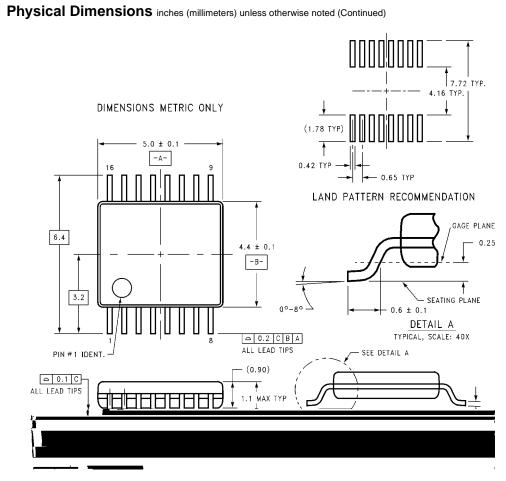

| MM74HC4060MTC | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |  |  |  |

| MM74HC4060N   | N16F           | 16-Lead Plastic Dual-In-Line Package (PDIP) JEDEC MS-001 0 300" Wide         |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

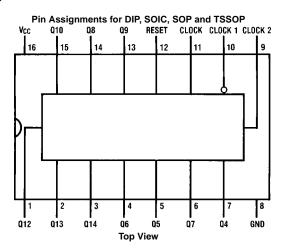

### **Connection Diagram**

## **Absolute Maximum Ratings**(Note 1)

(Note 2)

Supply Voltage (V $_{CC}$ ) -0.5 to +7.0V

DC Input Voltage (V<sub>IN)</sub>

# Recommended Operating Conditions

Note 1: Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating: plastic "N" package:

-12 mW/°C from 65°C to 85°C.

## DC Electrical Characteristics (Note 4)

Note 4: For a power supply of 5V  $\pm$ 10% the worst case output voltages ( $V_{OH}$ , and  $V_{OL}$ ) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case  $V_{IH}$  and  $V_{IL}$  occur at  $V_{CC} = 5.5V$  and 4.5V respectively. (The  $V_{IH}$  value at 5.5V is 3.85V.) The worst case leakage current ( $I_{IN}$ ,  $I_{CC}$ , and  $I_{OZ}$ ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

## **AC Electrical Characteristics**

$V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ ,  $C_L = 15$  pF,  $t_r = t_f = 6$  ns

| Symbol                              | Parameter                          | Conditions | Тур | Guaranteed<br>Limit | Units |

|-------------------------------------|------------------------------------|------------|-----|---------------------|-------|

| f <sub>MAX</sub>                    | Maximum Clock Frequency            |            |     | 30                  | MHz   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay to Q₄    | (Note 5)   | 40  | 20                  | ns    |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay to any Q |            | 16  | 40                  | ns    |

| t <sub>REM</sub>                    | Minimum Reset<br>Removal Time      |            | 10  | 20                  | ns    |

| t <sub>W</sub>                      | Minimum Pulse Width                |            | 10  | 16                  | ns    |

### **AC Electrical Characteristics**

$\rm V_{CC}\,{=}\,2.0V$  to 6.0V,  $\rm C_L\,{=}\,50$  pF,  $\rm t_f\,{=}\,t_f\,{=}\,6$  ns (unless otherwise specified)

| Symbol                              | Parameter                     | Conditions    | V <sub>CC</sub> | T <sub>A</sub> = 25°C |                   | T <sub>A</sub> = -40 to 85°C | T <sub>A</sub> = -55 to 125°C | Units |  |

|-------------------------------------|-------------------------------|---------------|-----------------|-----------------------|-------------------|------------------------------|-------------------------------|-------|--|

| Symbol                              | Parameter                     |               | VCC .           | Тур                   | Guaranteed Limits |                              |                               | Units |  |

| f <sub>MAX</sub>                    | Maximum Operating             |               | 2.0V            |                       | 6                 | 5                            | 4                             | MHz   |  |

|                                     | Frequency                     |               | 4.5V            |                       | 30                | 24                           | 20                            | MHz   |  |

|                                     |                               |               | 6.0V            |                       | 35                | 28                           | 24                            | MHz   |  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation           |               | 2.0V            | 120                   | 380               | 475                          | 171                           | ns    |  |

|                                     | Delay Clock to Q <sub>4</sub> |               | 4.5V            | 42                    | 76                | 95                           | 114                           | ns    |  |

|                                     |                               |               | 6.0V            | 35                    | 65                | 81                           | 97                            | ns    |  |

| t <sub>PHL</sub>                    | Maximum Propagation           |               | 2.0V            | 72                    | 240               | 302                          | 358                           | ns    |  |

|                                     | Delay Reset to any Q          |               | 4.5V            | 24                    | 48                | 60                           | 72                            | ns    |  |

|                                     |                               |               | 6.0V            | 20                    | 41                | 51                           | 61                            | ns    |  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation           |               | 2.0V            |                       | 125               | 156                          | 188                           | ns    |  |

|                                     | Delay Between Stages          |               | 4.5V            |                       | 25                | 31                           | 38                            | ns    |  |

|                                     | $Q_n$ to $Q_{n+1}$            |               | 6.0V            |                       | 21                | 26                           | 31                            | ns    |  |

| t <sub>REM</sub>                    | Minimum Reset                 |               | 2.0V            |                       | 100               | 125                          | 150                           | ns    |  |

|                                     | Removal Time                  |               | 4.5V            |                       | 20                | 25                           | 30                            | ns    |  |

|                                     |                               |               | 6.0V            |                       | 17                | 21                           | 25                            | ns    |  |

| t <sub>W</sub>                      | Minimum Pulse Width           |               | 2.0V            |                       | 80                | 100                          | 120                           | ns    |  |

|                                     |                               |               | 4.5V            |                       | 16                | 20                           | 24                            | ns    |  |

|                                     |                               |               | 6.0V            |                       | 14                | 17                           | 20                            | ns    |  |

| t <sub>r</sub> , t <sub>f</sub>     | Maximum Input Rise and        |               | 2.0V            |                       | 1000              | 1000                         | 1000                          | ns    |  |

|                                     | Fall Time                     |               | 4.5V            |                       | 500               | 500                          | 500                           | ns    |  |

|                                     |                               |               | 6.0V            |                       | 400               | 400                          | 400                           | ns    |  |

| $t_{THL}$ , $t_{TLH}$               | Maximum Output Rise           |               | 2.0V            | 30                    | 75                | 95                           | 110                           | ns    |  |

|                                     | and Fall Time                 |               | 4.5V            | 10                    | 15                | 19                           | 22                            | ns    |  |

|                                     |                               |               | 6.0V            | 9                     | 13                | 16                           | 19                            | ns    |  |

| C <sub>PD</sub>                     | Power Dissipation             | (per package) |                 | 55                    |                   |                              |                               | pF    |  |

|                                     | Capacitance (Note 6)          |               |                 |                       |                   |                              |                               |       |  |

| C <sub>IN</sub>                     | Maximum Input                 |               |                 | 5                     | 10                | 10                           | 10                            | pF    |  |

|                                     | Capacitance                   |               |                 |                       |                   |                              |                               |       |  |

Note 5: Typical Propagation delay time to any output can be calculated using:  $t_P = 17 + 12(N-1)$  ns; where N is the number of the output,  $Q_W$ , at  $V_{CC} = 5V$ .

Note 6:  $C_{PD}$  determines the no load dynamic power consumption,  $P_D = C_{PD} \ V_{CC}^2 \ f+I_{CC} \ V_{CC}$ , and the no load dynamic current consumption,  $I_S = C_{PD} \ V_{CC} \ f+I_{CC}$ .

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC16

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.090 (18.80 - 19.81)(2.286)16 15 14 13 12 11 10 16 15 INDEX AREA 0.250 ± 0.010 $\overline{(6.350 \pm 0.254)}$ PIN NO. 1 PIN NO. 1 1 2 3 4 5 6 7 8 1 2 IDENT OPTION 01 OPTION 02 $\frac{0.065}{(1.651)}$ $\frac{0.130 \pm 0.005}{(3.302 \pm 0.127)}$ $\frac{0.060}{(1.524)}$ TYP 4° TYP OPTIONAL 0.300 - 0.320 (7.620 - 8.128)0.145 - 0.200 $\overline{(3.683 - 5.080)}$ 95°±5° 0.008 = 0.016 (0.203 = 0.406) TYP 90° ± 4° TYP 0.020 $\frac{0.280}{(7.112)}$ 0.125 - 0.150 (3.175 - 3.810) $0.030 \pm 0.015$ MIN $(0.762 \pm 0.381)$ 0.014 = 0.023 (0.356 = 0.584) 0.100 ± 0.010 (0.325 +0.040 -0.015

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

0.050 ± 0.010

(1.270 ± 0.254)

(2.540 ± 0.254)

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

N16E (REV F)