Data Sheet August 1, 2005 FN2894.6

# 20MHz, High Slew Rate, Uncompensated, High Input Impedance, Operational Amplifiers

HA-2520/2525 comprise a series of operational amplifiers delivering an unsurpassed combination of specifications for slew rate, bandwidth and settling time. These dielectrically isolated amplifiers are controlled at close loop gains greater than 3 without external compensation. In addition, these high performance components also provide low offset current and high input impedance.

120V/ $\mu$ s slew rate and 200ns (0.2%) settling time of these amplifiers make them ideal components for pulse amplification and data acquisition designs. These devices are valuable components for RF and video circuitry requiring up to 20MHz gain bandwidth and 2MHz power bandwidth. For accurate signal conditioning designs the HA-2520/2525's superior dynamic specifications are complemented by 10nA offset current, 100M $\Omega$  input impedance and offset trim capability.

## **Ordering Information**

| PART NUMBER               | TEMP.<br>RANGE (°C) |                        |       |

|---------------------------|---------------------|------------------------|-------|

| HA7-2520-2                | -55 to 125          | 8 Ld CERDIP            | F8.3A |

| HA3-2525-5                | 0 to 75             | 8 Ld PDIP              | E8.3  |

| HA3-2525-5Z<br>(See Note) | 0 to 75             | 8 Ld PDIP<br>(Pb-free) | E8.3  |

| HA7-2525-5                | 0 to 75             | 8 Ld CERDIP            | F8.3A |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

| • High Slew Rate                                 |

|--------------------------------------------------|

| • Fast Settling                                  |

| • Full Power Bandwidth                           |

| • Gain Bandwidth (A <sub>V</sub> $\geq$ 3) 20MHz |

| • High Input Impedance                           |

| • Low Offset Current                             |

| Componentian Pin for Unity Gain Canability       |

- Compensation Pin for Unity Gain Capability

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Applications**

- · Data Acquisition Systems

- RF Amplifiers

- Video Amplifiers

- · Signal Generators

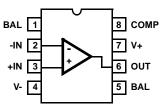

#### **Pinout**

#### HA-2520 (CERDIP) HA-2525 (PDIP, CERDIP) TOP VIEW

#### **Absolute Maximum Ratings**

####

#### **Operating Conditions**

| Temperature Range |                    |

|-------------------|--------------------|

| HA-2520-2         | <br>-55°C to 125°C |

| HA-2525-5         | <br>0°C to 75°C    |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | $\theta_{JA}$ (oC/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|----------------------|------------------------|

| PDIP Package                             | 96                   | N/A                    |

| CERDIP Package                           | 135                  | 50                     |

| Maximum Junction Temperature (Hermetic F | Packages)            | 175°C                  |

| Maximum Junction Temperature (Plastic P  | ackage)              | 150 <sup>o</sup> C     |

| Maximum Storage Temperature Range        | 65                   | OC to 150°C            |

| Maximum Lead Temperature (Soldering 10   |                      |                        |

|                                          |                      |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

# Electrical Specifications V<sub>SUPPLY</sub> = ±15V

|                                         | TEMP<br>(°C) | HA-2520-2 |       |     |       |       |     |                    |

|-----------------------------------------|--------------|-----------|-------|-----|-------|-------|-----|--------------------|

| PARAMETER                               |              | MIN       | TYP   | MAX | MIN   | TYP   | MAX | UNITS              |

| INPUT CHARACTERISTICS                   |              |           |       |     |       |       |     |                    |

| Offset Voltage                          | 25           | -         | 4     | 8   | -     | 5     | 10  | mV                 |

|                                         | Full         | -         | -     | 11  | -     | -     | 14  | mV                 |

| Offset Voltage Drift                    | Full         | -         | 20    | -   | -     | 30    | -   | μV/ <sup>o</sup> C |

| Bias Current                            | 25           | -         | 100   | 200 | -     | 125   | 250 | nA                 |

|                                         | Full         | -         | -     | 400 | -     | -     | 500 | nA                 |

| Offset Current                          | 25           | -         | 10    | 25  | -     | 20    | 50  | nA                 |

|                                         | Full         | -         | -     | 50  | -     | -     | 100 | nA                 |

| Input Resistance (Note 2)               | 25           | 50        | 100   | -   | 40    | 100   | -   | MΩ                 |

| Common Mode Range                       | Full         | ±10.0     | -     | -   | ±10.0 | -     | -   | V                  |

| TRANSFER CHARACTERISTICS                |              |           |       |     |       |       |     |                    |

| Large Signal Voltage Gain               | 25           | 10        | 15    | -   | 7.5   | 15    | -   | kV/V               |

| (Notes 3, 6)                            | Full         | 7.5       | -     | -   | 5     | -     | -   | kV/V               |

| Common Mode Rejection Ratio (Note 4)    | Full         | 80        | 90    | -   | 74    | 90    | -   | dB                 |

| Gain Bandwidth (Notes 2, 5)             | 25           | 10        | 20    | -   | 10    | 20    | -   | MHz                |

| Minimum Stable Gain                     | 25           | 3         | -     | -   | 3     | -     | -   | V/V                |

| OUTPUT CHARACTERISTICS                  | <u> </u>     | ll .      |       | l   |       | ll .  | l . |                    |

| Output Voltage Swing (Note 3)           | Full         | ±10.0     | ±12.0 | -   | ±10.0 | ±12.0 | -   | V                  |

| Output Current (Note 6)                 | 25           | ±10       | ±20   | -   | ±10   | ±20   | -   | mA                 |

| Full Power Bandwidth<br>(Notes 6, 11)   | 25           | 1.5       | 2.0   | -   | 1.2   | 2.0   | -   | MHz                |

| TRANSIENT RESPONSE (A <sub>V</sub> = +3 | 3)           | l         | 1     | I   | 1     |       | ı   | 1                  |

| Rise Time (Notes 3, 7, 8, 10)           | 25           | -         | 25    | 50  | -     | 25    | 50  | ns                 |

| Overshoot (Notes 3, 7, 8, 10)           | 25           | -         | 25    | 40  | -     | 25    | 50  | %                  |

| Slew Rate (Notes 3, 7, 10, 12)          | 25           | ±100      | ±120  | -   | ±80   | ±120  | -   | V/µs               |

| Settling Time (Notes 3, 7, 10, 12)      | 25           | -         | 0.20  | -   | -     | 0.20  | -   | μS                 |

| POWER SUPPLY CHARACTERIS                | STICS        | 1         | ı     | L   | 1     | 1     | 1   | 1                  |

| Supply Current                          | 25           | -         | 4     | 6   | -     | 4     | 6   | mA                 |

# **Electrical Specifications** $V_{SUPPLY} = \pm 15V$ (Continued)

|                                       | TEMP |     | HA-2520-2 |     | HA-2525-5 |     |     |       |

|---------------------------------------|------|-----|-----------|-----|-----------|-----|-----|-------|

| PARAMETER                             | (°C) | MIN | TYP       | MAX | MIN       | TYP | MAX | UNITS |

| Power Supply Rejection Ratio (Note 9) | Full | 80  | 90        | -   | 74        | 90  | -   | dB    |

#### NOTES:

- 2. This parameter value is based on design calculations.

- 3.  $R_L = 2k\Omega$ .

- 4.  $V_{CM}^- = \pm 10V$ .

- 5.  $A_V > 10$ .

- 6.  $V_O = \pm 10.0 V$ .

- 7.  $C_L = 50pF$ .

- 8.  $V_0 = \pm 200 \text{mV}$

- 9.  $\Delta V = \pm 5.0 V$ .

- 10. See Transient Response Test Circuits and Waveforms.

- $\frac{\text{Slew Rate}}{2\pi V_{\text{PEAK}}}$ 11. Full Power Bandwidth guaranteed based on slew rate measurement using: FPBW =

- 12.  $V_{OUT} = \pm 5V$ .

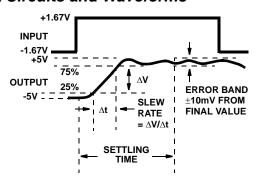

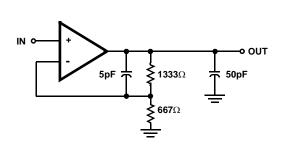

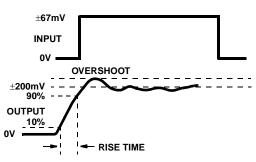

## Test Circuits and Waveforms

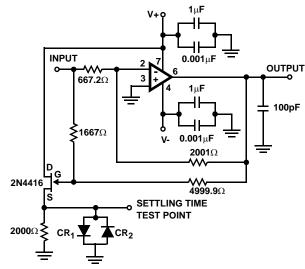

FIGURE 1. SLEW RATE AND SETTLING TIME

FIGURE 3. SLEW RATE AND TRANSIENT RESPONSE

NOTE: Measured on both positive and negative transitions from 0V to +200mV and 0V to -200mV at the output.

**FIGURE 2. TRANSIENT RESPONSE**

#### NOTES:

- 13.  $A_V = -3$ .

- 14. Feedback and summing resistor ratios should be 0.1% matched.

- 15. Clipping diodes CR<sub>1</sub> and CR<sub>2</sub> are optional. HP5082-2810 recommended.

FIGURE 4. SETTLING TIME TEST CIRCUIT

# Test Circuits and Waveforms (Continued)

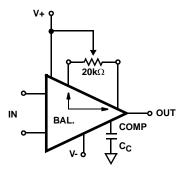

NOTE: Tested offset adjustment range is  $|V_{OS} + 1mV|$  minimum referred to output. Typical ranges are  $\pm 20mV$  with  $R_T = 20k\Omega$ .

FIGURE 5. SUGGESTED  $V_{\mbox{OS}}$  ADJUSTMENT AND COMPENSATION HOOK-UP

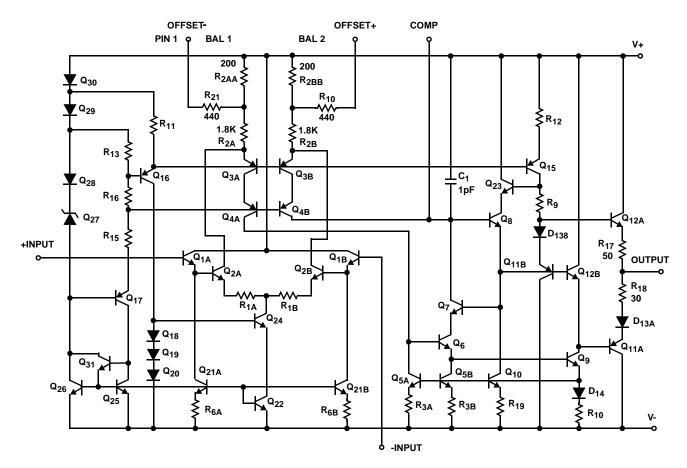

# Schematic Diagram

# **Typical Application**

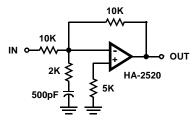

## Inverting Unity Gain Circuit

Figure 6 shows a Compensation Circuit for an inverting unity gain amplifier. The circuit was tested for functionality with supply voltages from  $\pm 4V$  to  $\pm 15V$ , and the performance as tested was: Slew Rate  $\approx 120V/\mu s$ ; Bandwidth  $\approx 10MHz$ ; and Settling Time (0.1%)  $\approx 500ns$ . Figure 7 illustrates the amplifier's frequency response, and it is important to note that capacitance at pin 8 must be minimized for maximum bandwidth.

FIGURE 6. INVERTING UNITY GAIN CIRCUIT

FIGURE 7. FREQUENCY RESPONSE FOR INVERTING UNITY GAIN CIRCUIT

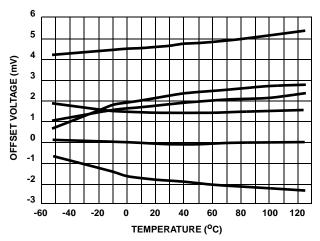

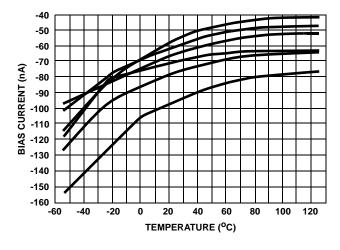

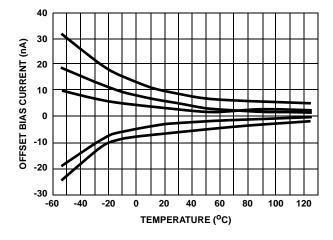

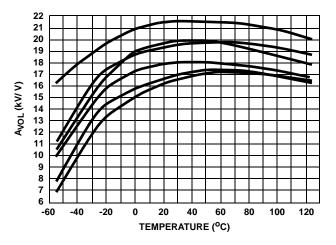

# **Typical Performance Curves** V<sub>S</sub> = ±15V, T<sub>A</sub> = 25°C, Unless Otherwise Specified

FIGURE 8. OFFSET VOLTAGE vs TEMPERATURE (6 TYPICAL UNITS FROM 3 LOTS)

FIGURE 9. BIAS CURRENT vs TEMPERATURE (6 TYPICAL UNITS FROM 3 LOTS)

FIGURE 10. OFFSET CURRENT vs TEMPERATURE (5 TYPICAL UNITS FROM 3 LOTS)

FIGURE 11. OPEN LOOP GAIN vs TEMPERATURE (6 TYPICAL UNITS FROM 3 LOTS)

intersil FN2894.6 August 1, 2005

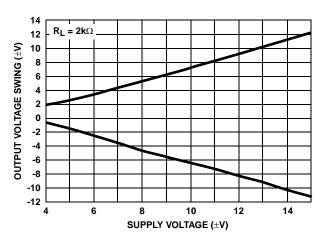

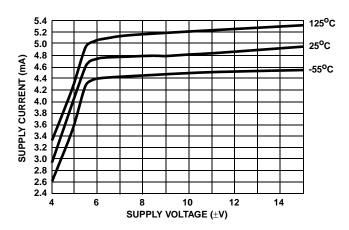

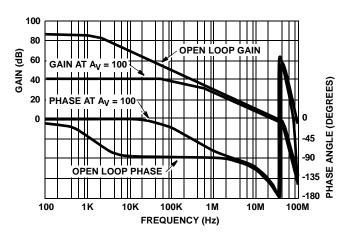

# $\textit{Typical Performance Curves} \quad \text{V}_{S} = \pm 15 \text{V}, \ \text{T}_{A} = 25^{0} \text{C}, \ \text{Unless Otherwise Specified} \quad \textit{\textbf{(Continued)}}$

FIGURE 12. OUTPUT CURRENT vs SUPPLY VOLTAGE

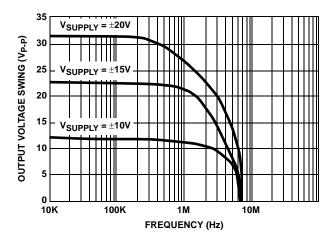

FIGURE 13. OUTPUT VOLTAGE SWING vs SUPPLY VOLTAGE

FIGURE 14. SUPPLY CURRENT vs SUPPLY VOLTAGE

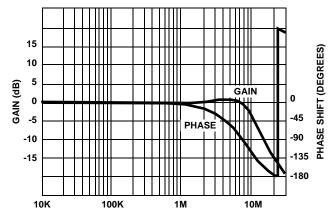

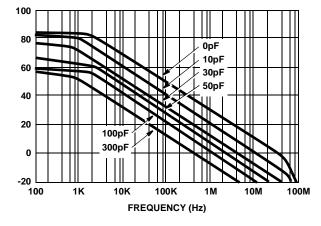

FIGURE 15. FREQUENCY RESPONSE

FIGURE 16. OPEN LOOP FREQUENCY RESPONSE FOR VARIOUS VALUES OF CAPACITORS FROM COMP PIN TO GROUND

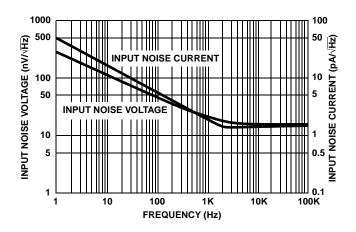

FIGURE 17. INPUT NOISE CHARACTERISTICS

intersil FN2894.6 August 1, 2005

# **Typical Performance Curves** $V_S = \pm 15 V$ , $T_A = 25^{\circ} C$ , Unless Otherwise Specified (Continued)

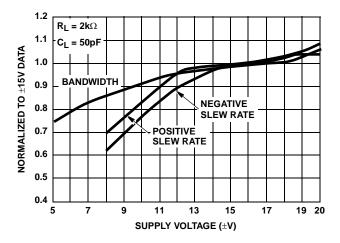

FIGURE 19. NORMALIZED AC PARAMETERS vs SUPPLY VOLTAGE

#### Die Characteristics

**METALLIZATION:**

Type: Al, 1% Cu Thickness: 16kÅ ±2kÅ

SUBSTRATE POTENTIAL:

Unbiased

PASSIVATION:

Type: Nitride (Si<sub>3</sub>N<sub>4</sub>) over Silox (SiO<sub>2</sub>, 5% Phos.)

Silox Thickness: 12kÅ ±2kÅ Nitride Thickness: 3.5kÅ ±1.5kÅ

TRANSISTOR COUNT:

40

PROCESS:

Bipolar Dielectric Isolation

V-

# Metallization Mask Layout HA-2520, HA-2525 OUT BAL 27-53-71A CD

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

-IN

+IN

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

BAL