# Kintex-7 FPGA Connectivity Targeted Reference Design

User Guide

UG927 (v1.2) November 7, 2012

#### Notice of Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

#### **Automotive Applications Disclaimer**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

#### **Fedora Information**

Xilinx obtained the Fedora Linux software from Fedora (http://fedoraproject.org/), and you may too. Xilinx made no changes to the software obtained from Fedora. If you desire to use Fedora Linux software in your product, Xilinx encourages you to obtain Fedora Linux software directly from Fedora (http://fedoraproject.org/), even though we are providing to you a copy of the corresponding source code as provided to us by Fedora. Portions of the Fedora software may be covered by the GNU General Public license as well as many other applicable open source licenses. Please review the source code in detail for further information. To the maximum extent permitted by applicable law and if not prohibited by any such third-party licenses, (1) XILINX DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE; AND (2) IN NO EVENT SHALL XILINX BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Fedora software and technical information is subject to the U.S. Export Administration Regulations and other U.S. and foreign law, and may not be exported or re-exported to certain countries (currently Cuba, Iran, Iraq, North Korea, Sudan, and Syria) or to persons or entities prohibited from receiving U.S. exports (including those (a) on the Bureau of Industry and Security Denied Parties List or Entity List, (b) on the Office of Foreign Assets Control list of Specially Designated Nationals and Blocked Persons, and (c) involved with missile technology or nuclear, chemical or biological weapons). You may not download Fedora software or technical information if you are located in one of these countries, or otherwise affected by these restrictions. You may not provide Fedora software or technical information to individuals or entities located in one of these countries or otherwise affected by these restrictions. You are also responsible for compliance with foreign law requirements applicable to the import and use of Fedora software and technical information.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                |

|----------|---------|-------------------------|

| 07/18/12 | 1.0     | Initial Xilinx release. |

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/06/12 | 1.1     | Added second sentence to third paragraph under Connectivity Targeted Reference<br>Design. Updated Figure 1-1, Figure 1-2, and Figure 1-3. Changed "FIFO" to "Virtual<br>FIFO" in third paragraph under Raw Ethernet Performance Mode. Updated resource<br>utilization usage data in Table 1-1. Updated Figure 2-17. Deleted first two rows in<br>Table 2-2. Deleted "Multiport Virtual Packet FIFO" section from Chapter 2, Getting<br>Started. Updated Figure 3-10. Changed "Multiport Packet FIFO" to "AXI Virtual FIFO"<br>in Table 3-5. Changed "DDR3 Virtual FIFO" to "AXI Virtual FIFO". Changed "virtual<br>FIFO controller" to "AXI Virtual FIFO controller" in last sentence under AXI Virtual<br>FIFO. Changed "Virtual FIFO" to "AXI Virtual FIFO" in section title Packet<br>Generator/Checker Behind AXI Virtual FIFO. Updated Figure 5-2. Updated Figure A-1.<br>Deleted "Packetized VFIFO registers" row from Table A-2. Deleted "Memory Controller<br>Registers" section from Appendix A, Register Description. |

| 11/07/12 | 1.2     | Added Implementing the Design Using the Vivado Flow to Chapter 2, Getting Started.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Table of Contents

| <b>Revision History</b>                                  |

|----------------------------------------------------------|

| Chapter 1: Introduction                                  |

| Connectivity Targeted Reference Design                   |

| Features                                                 |

| <b>Resource Utilization</b>                              |

| Chapter 2: Getting Started                               |

| <b>Requirements</b>                                      |

| Hardware Demonstration Setup 12                          |

| Ethernet Specific Features 28                            |

| <b>Rebuilding the Design</b> 29                          |

| Simulation                                               |

| Chapter 3: Functional Description                        |

| Hardware Architecture                                    |

| Software Design Description 54                           |

| Chapter 4: Performance Estimation                        |

| Theoretical Estimate75                                   |

| Measuring Performance                                    |

| Performance Observations                                 |

| Chapter 5: Designing with the TRD Platform               |

| Software-Only Modifications                              |

| Design Top-Level Only Modifications                      |

| Design Changes                                           |

| Appendix A: Register Description                         |

| DMA Registers                                            |

| User Space Registers                                     |

| Appendix B: Directory Structure and File Description     |

| Appendix C: Software Application and Network Performance |

| Compiling Traffic Generator Applications                 |

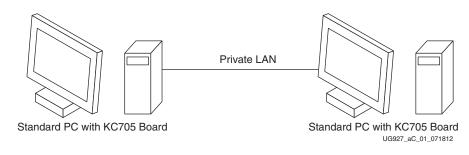

| Private Network Setup and Test 99                        |

## Appendix D: Troubleshooting

## Appendix E: Additional Resources

| Xilinx Resources | 105 |

|------------------|-----|

| References       | 105 |

## Chapter 1

## Introduction

This chapter introduces the Kintex<sup>TM</sup>-7 Connectivity Targeted Reference Design (TRD). summarizes its modes of operation, and identifies the features provided.

## **Connectivity Targeted Reference Design**

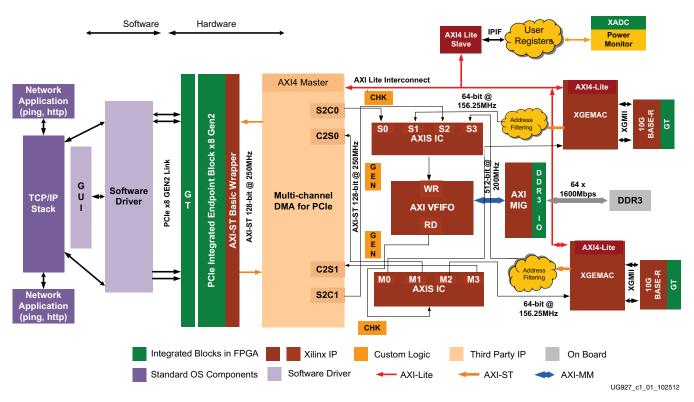

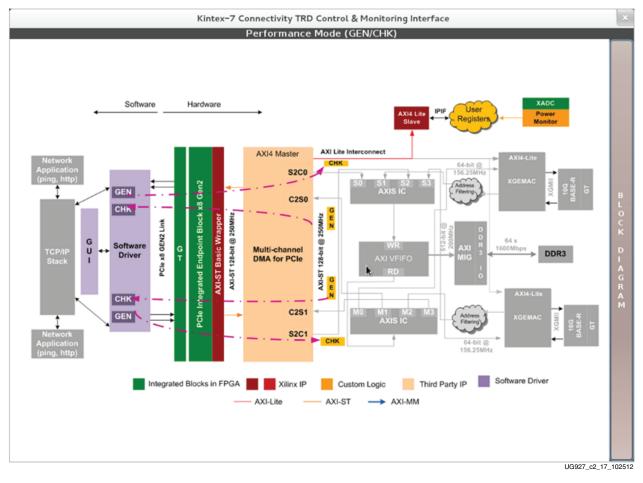

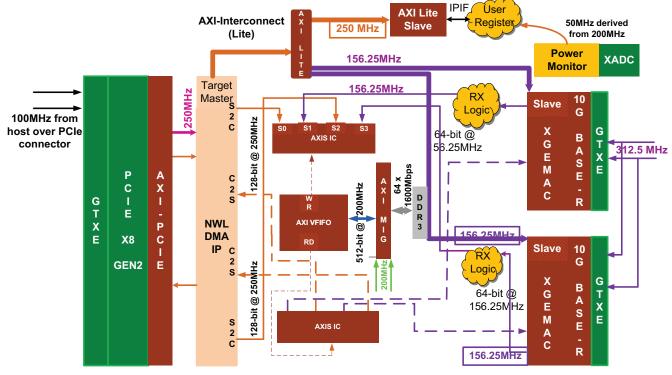

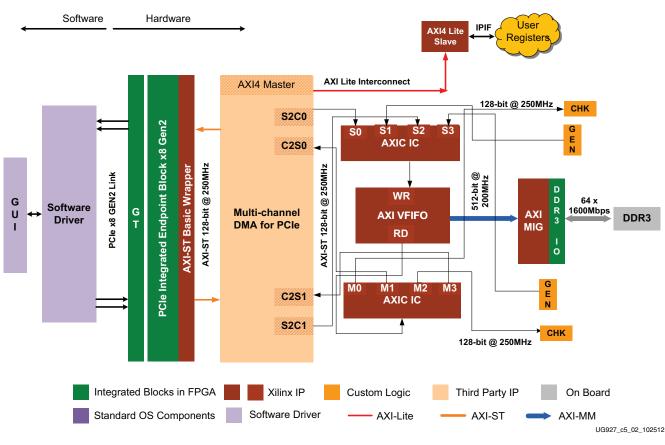

Figure 1-1 depicts the block level overview of the Kintex-7 Connectivity TRD which delivers up to 20 Gb/s of performance per direction.

The design is a dual Network Interface Card (NIC) with a GEN2 x8 PCIe endpoint, a multi-channel packet DMA from Northwest Logic, DDR3 memory for buffering, 10G Ethernet MAC, and 10GBASE-R standard compatible physical layer interface. The PCIe-DMA together is responsible for movement of data between a PC system and FPGA (S2C implies data movement from PC system to FPGA and C2S implies data movement from FPGA to PC system).

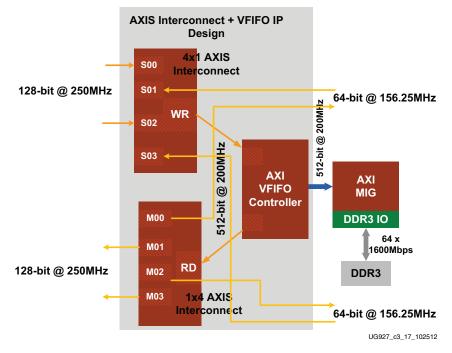

DDR3 SDRAM (64-bit, 1,600 Mb/s or 800 MHz) is used for packet buffering – a virtual FIFO layer facilitates the use of DDR3 as multiple FIFOs. The virtual FIFO layer is built using the AXI Stream interconnect and AXI Virtual FIFO controller CoreGEN IPs

Dual NIC application is built over this by use of Ten Gigabit Ethernet MAC and Ten Gigabit PCS/PMA (10GBASE-R PHY) IPs. The 10G MAC connects to the 10G BASE-R PHY over 64-bit, SDR XGMII parallel interface. Additionally, the design provides power monitoring capability based on a PicoBlaze<sup>™</sup> engine.

For software, the design provides 32-bit Linux drivers for all modes of operation listed below and a graphical user interface (GUI) which controls the tests and monitors the status.

#### Figure 1-1: Kintex-7 FPGA Connectivity TRD Block Diagram

*Note:* The arrows in Figure 1-1 indicate AXI interface directions from master to slave. They do not indicate data flow directions.

## **Operation Modes**

The design offers the following modes of operation – all available within a single design bitstream.

### PCIe-DMA Performance Mode

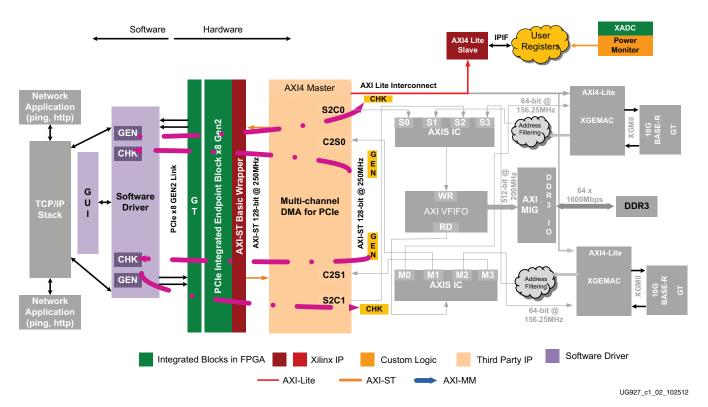

This mode demonstrates performance of the GEN2 x8 PCIe-DMA followed by a packet generator and a checker in hardware (see Figure 1-2).

Figure 1-2: PCIe-DMA Performance Mode

Capability of the PCIe-DMA system standalone is performed without involvement of any further design blocks.

PCIe-DMA Performance Mode supports:

- 1. **Loopback Mode**: Software generates packets in user space. These packets are sent to hardware over PCIe-DMA, returned back to the software driver, and are tested for integrity.

- 2. **Generator Mode**: Hardware generates packets and the software driver checks them for integrity.

- 3. **Checker Mode**: The software driver generates packets in user space. These packets are sent to hardware and then checked for integrity.

All the above modes of operation are user configurable through register programming.

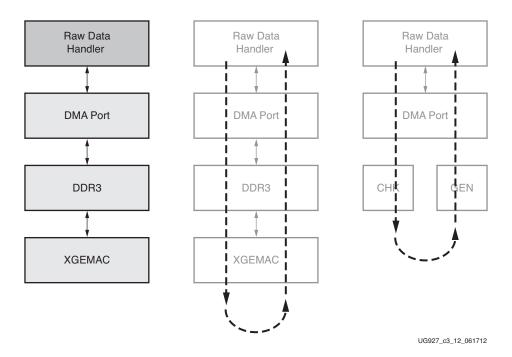

#### Raw Ethernet Performance Mode

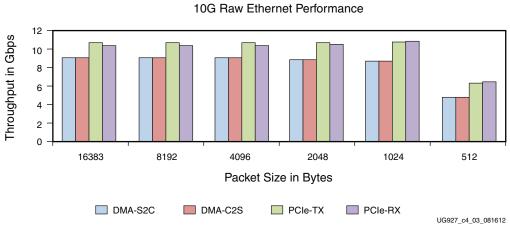

This mode demonstrates performance of the 10G Ethernet path showcasing hardware design capability for high performance (see Figure 1-3).

The software driver generates raw broadcast Ethernet frames with no connection to the networking stack.

The packet originates at the user space and moves to the FPGA through PCIe-DMA, traverses through DDR3 based Virtual FIFO, XGEMAC and 10GBASE-R PHY, where it is looped back through the other network channel and sent back to the software driver.

This only supports the loopback mode of operation.

Figure 1-3: Raw Ethernet Performance Demo

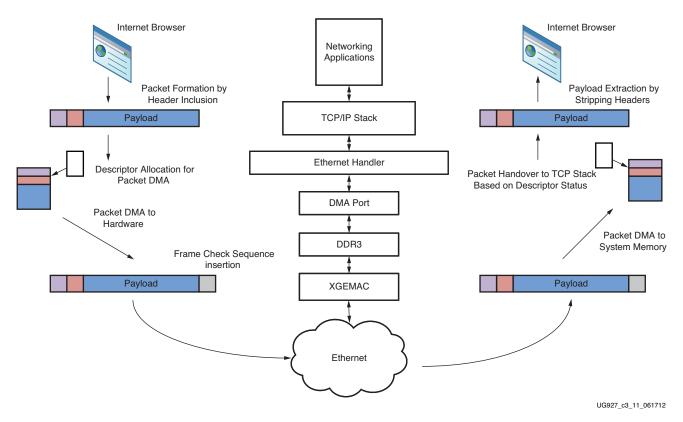

#### Application mode

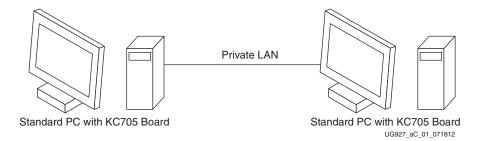

This mode demonstrates end-to-end application like a dual 10G NIC. The software driver hooks up to the networking stack and standard networking applications can be used. However, due to lack of offload engine in hardware, the performance remains low.

The packets traverse through TCP/IP stack due to invocation of various standard networking applications.

## **Features**

The Kintex-7 Connectivity TRD features are divided into base features and application features.

### **Base Features**

This section lists the features of the PCIe and DMA, which form the backbone of the design:

- PCI Express v2.1 compliant x8 Endpoint operating at 5 Gb/s/lane/direction

- PCIe transaction interface utilization engine

- MSI and legacy interrupt support

- Bus mastering scatter-gather DMA

- Multi-channel DMA

- AXI4 streaming interface for data

- AXI4 interface for register space access

- DMA performance engine

- Full duplex operation

- Independent transmit and receive channels

## **Application Features**

This section lists the features of the developed application:

- 10 Gigabit Ethernet MAC with 10G BASE-R PHY

- Address filtering

- Inter-frame gap control

- Jumbo frame support up to 16,383 bytes in size

- Ethernet statistics engine

- Management interface for configuration (MDIO)

- Picoblaze based PVT monitoring

- Engine in hardware to monitor power by reading TI's UCD9248 power controller chip on-board KC705

- Engine in hardware to monitor die temperature and voltage rails via Xilinx Analog-to-Digital Converter

- Application demand driven power management

- Option to change PCIe link width and link speed for reduced power consumption in lean traffic scenarios

## **Resource Utilization**

Resource utilization is shown in Table 1-1.

#### Table 1-1: Resource Utilization

| Resource        | Total Available | Usage         |

|-----------------|-----------------|---------------|

| Slice Registers | 407600          | 108,682 (26%) |

| Slice LUT       | 203800          | 79,091 (38%)  |

| RAMB36E1        | 445             | 127 (28%)     |

| MMCME2_ADV      | 10              | 3 (30%)       |

| PLLE2_ADV       | 10              | 1 (10%)       |

| BUFG/BUFGCTRL   | 32              | 15 (46%)      |

| XADC            | 1               | 1 (100%)      |

| IOB             | 500             | 134 (26%)     |

| GTXE2_CHANNEL   | 16              | 10 (62%)      |

| GTXE2_COMMON    | 4               | 3 (75%)       |

## Chapter 2

## **Getting Started**

This chapter is a quick-start guide enabling the user to test the Targeted Reference Design (TRD) in hardware with the software driver provided, and also simulate it. Step-by-step instructions are provided for testing the design in hardware.

## Requirements

#### Simulation Requirements

TRD simulation requires:

- 1. ModelSim Simulator v10.1a

- 2. Xilinx simulation libraries compiled for ModelSim

#### Test Setup Requirements

Testing the design in hardware requires:

- 1. KC705 Evaluation board with xc7k325t-2-ffg900 part

- 2. Design files (available on the USB media) consisting of:

- a. Design source files

- b. Device driver files

- c. FPGA programming files

- d. Documentation

- 3. ISE design Suite Logic Edition Tools v14.1

- 4. Micro USB cable

- 5. FM-S14 quad SFP+ FMC

- 6. Two SFP+ connectors with Fiber Optic cable

- 7. Fedora 16 LiveDVD

- 8. PC with PCIe v2.0 slot. Recommended PCI Express Gen2 PC system motherboards are ASUS P5E (Intel X38), ASUS Rampage II Gene (Intel X58) and Intel DX58SO (Intel X58). Note the Intel X58 chipsets tend to show higher performance. This PC could also have Fedora Core 16 Linux OS installed on it.

## Hardware Demonstration Setup

This section details the hardware setup and use of provided application and control GUI to help the user get started quickly with the hardware. It provides a step-by-step explanation on hardware bring-up, software bring-up, and use of the application GUI.

All procedures listed in the following sections require super user access on a Linux machine. When using Fedora 16 LiveDVD provided with the kit, super user access is granted by default due to the way the kernel image is built; if LiveDVD is not used contact the system administrator for super user access.

1. With the power supply turned off, ensure that switches P1 and P2 on the FM-S14 FMC card are in the ON position, as shown in Figure 2-1.

Figure 2-1: DIP Switch Position on FMC Card

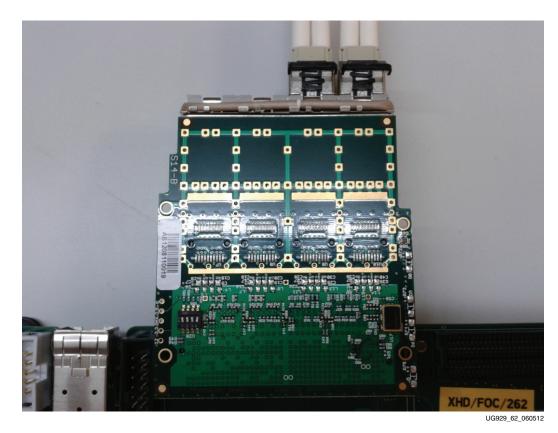

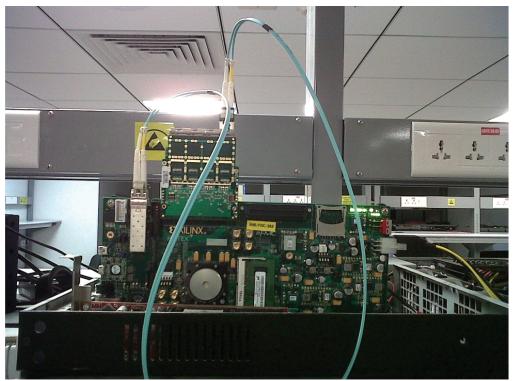

2. Insert SFP+ connectors to channel 2 and channel 3 positions as shown in Figure 2-2.

Figure 2-2: SFP+ Connector Position on FMC Card

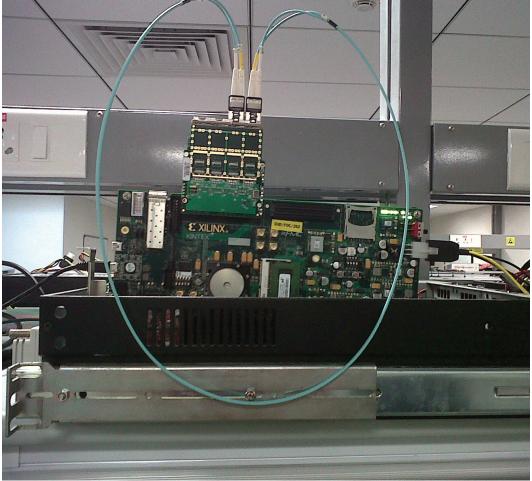

3. Insert the FM-S14 FMC card to the HPC slot of KC705 as shown in Figure 2-3. Remove the cap from the fiber optic cables and connect the fiber optic cables in a loopback fashion as shown in the figure.

UG929\_63\_060512

Figure 2-3: Setup with Fiber Optic Cable

4. Connect the 12V ATX power supply 4-pin disk drive type connector to the board. Note that the 6-pin ATX supply cannot be connected directly to the KC705 board and the 6-pin adapter is required.

*Caution!* The 6-pin ATX supply cannot be connected directly to the KC705 board and the 6-pin adapter is required.

- 5. With the host system powered off, insert the KC705 board in the PCI Express® slot through the PCI Express x8 edge connector.

- 6. Ensure that the connections are secure so as to avoid loose contact problems. Power on the KC705 board and then the system.

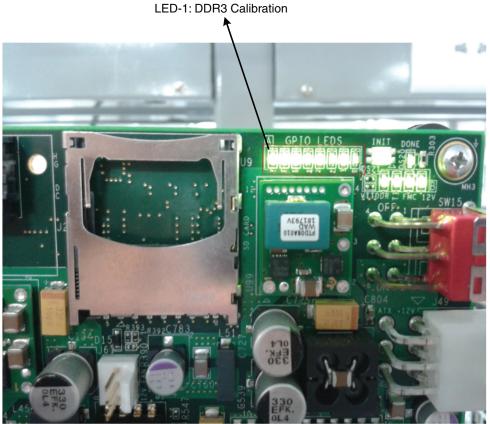

- 7. The GPIO LEDs are located in the top right corner of the KC705 board. These LED indicators illuminate to provide the following status (LED positions are marked from left to right):

LED position 1 – DDR3 link up

LED position 2 – 10GBASE-R link 1 ready

LED position 3 – 10GBASE-R link 2 ready

- LED position 4 156.25 MHz clock heart beat LED

- LED position 5 PCIe x8 link stable

- LED position 6 PCIe 250 MHz clock

- LED position 7 PCIe link up

- LED positions on the KC705 board are shown in Figure 2-4.

UG929\_64\_060512

Figure 2-4: LED Position on the FMC Card

8. The LEDs on the FMC card (note that these are on the bottom side) indicate the following status:

LED position top – FM-S14 is connected on the correct FMC connector on KC705 board

LED position bottom – indicates clock generator on FMC is programmed to generate 312.5 MHz as required by the TRD

### Installing the Device Drivers

This sections describes the steps to install the device drivers for the Kintex-7 Connectivity TRD after completion of the above hardware setup steps.

- 1. If Fedora 16 is installed on the PC system's hard disk, boot as a root-privileged user, proceed to step 3. Otherwise continue with step 2.

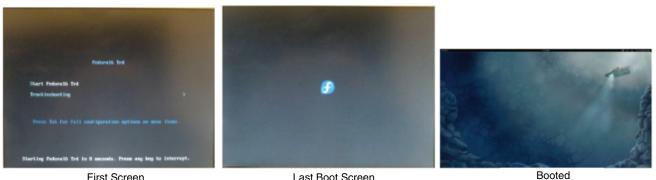

- 2. To boot from the Fedora 16 LiveDVD provided in the kit, place the DVD in the PC's CD-ROM drive. The Fedora 16 Live Media is for Intel-compatible PCs. The DVD contains a complete, bootable 32-bit Fedora 16 environment with the proper packages installed for the TRD demonstration environment. The PC boots from the CD-ROM drive and logs into a liveuser account. This account has kernel development root privileges required to install and remove device driver modules.

Note: Users might have to adjust BIOS boot order settings to enure that the CD-ROM drive is the first drive in the boot order. To enter the BIOS menu to set the boot order, press the DEL or F2 key when the system is powered on. Set the boot order and save the changes. (The DEL or F2 key is used by most PC systems to enter the BIOS setup. Some PCs might have a different way to enter the BIOS setup.)

The PC should boot from the CD-ROM drive. The images in Figure 2-5 are seen on the monitor during boot up. (Booting from Fedora 16 LiveDVD takes few minutes - wait for until Fedora 16 menu pops up on the screen as shown in Figure 2-5.)

First Screen

Last Boot Screen

929 65 061212

Figure 2-5: Fedora 16 LiveDVD Boot Sequence

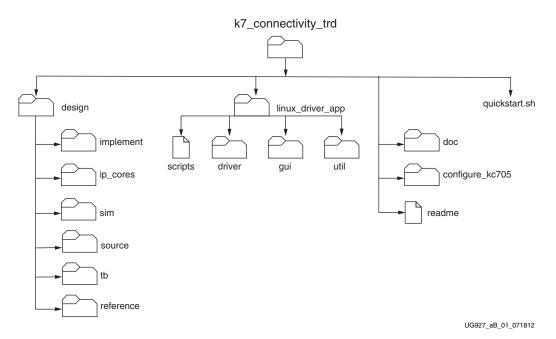

3. Copy the k7\_connectvity\_trd\_v1\_0 folder from the USB flash drive provided in the Connectivity kit to the home directory (or a folder of choice). After the folder is copied, un-mount and disconnect the USB drive. Note that the user must be a root-privileged user.

Double-click the copied k7\_connectvity\_trd\_v1\_0 folder. The screen capture in Figure 2-6 shows the content of the k7\_connectvity\_trd\_v1\_0 folder. The user needs to browse through the "Activities" tab after Fedora 16 boots up to access the "Home" directory.

| File Edit View G | o Bookmarks Help   |                          |                                       |

|------------------|--------------------|--------------------------|---------------------------------------|

| Devices          | < 🖾 Home 🔯 Desktop | k7_connectivity_trd_v1_0 | 😓 📎 🔍 Search                          |

| _Fedoral         | -                  |                          |                                       |

| 🖾 440 GB Fi      |                    |                          |                                       |

| 🖾 _Fedora1       | configure_kc705    | design do                | c linux_driver_app                    |

| 🔲 8.2 kB Fil     |                    |                          |                                       |

| 🖾 _Fedora1       | 2                  |                          |                                       |

| 🖾 712 MB F       | quickstart.sh      | readme.txt               |                                       |

| Computer         |                    |                          |                                       |

| 🗟 Home           |                    |                          |                                       |

| 🔯 Documents      |                    |                          |                                       |

| 💹 Downloads      |                    |                          |                                       |

| 🙆 Music          |                    |                          |                                       |

| Pictures         |                    |                          |                                       |

| 🛅 Videos         |                    |                          |                                       |

| 🖲 File System    |                    |                          |                                       |

| 🗑 Trash          |                    |                          |                                       |

| Network          |                    |                          | "avialatest ab" aslasted (00 to to a) |

|                  |                    |                          | "quickstart.sh" selected (85 bytes)   |

*Figure 2-6:* **Directory Structure of k7\_connectivity\_trd**

4. Ensure that the TRD package has the proper "execute" permission. Double click quickstart.sh script (see Figure 2-7). This script invokes the driver installation GUI. Click **Run in Terminal**.

| File Edit View | Go B | ookmarks    | Help      |                         |         |                |             |                 |

|----------------|------|-------------|-----------|-------------------------|---------|----------------|-------------|-----------------|

| Devices        | ^ <  | 🔊 Home      | 🐻 Desktop | k7_connectivity_trd     | _v1_0   |                | <b>∽</b> -> | <b>Q</b> Search |

| 🔲 _Fedora1     |      | _           |           |                         | _       |                |             |                 |

| 🖾 440 GB Fi    |      |             |           |                         |         |                |             | ]               |

| 🖾 _Fedora1     |      | configure_k | c705      | design                  | do      | c li           | inux_drive  | r_app           |

| 🔲 8.2 kB Fil   |      |             |           |                         |         |                |             |                 |

| 🖾 _Fedora1     |      |             |           |                         |         |                |             |                 |

| 🔲 712 MB F     |      | quickstart  | .sh       | readme.txt              |         |                |             |                 |

| Computer       |      |             |           |                         |         |                |             |                 |

| 🛅 Home         | -    |             |           |                         |         |                |             |                 |

| 🔞 Documents    | 1    |             | Do you wa | nt to run "quickst      | art.sh' | ", or display  | its cont    | ents?           |

| 🔯 Downloads    |      |             |           | " is an executable text |         |                |             |                 |

| 🐻 Music        |      |             | 4         |                         |         |                |             |                 |

| 🛅 Pictures     |      |             |           | Run in Terminal         | Displa  | ay Cancel      | R           | un              |

| 🛅 Videos       |      |             |           |                         |         |                |             |                 |

| 🖲 File System  |      |             |           |                         |         |                |             |                 |

| 🗑 Trash        |      |             |           |                         |         |                |             |                 |

| Network        |      |             |           |                         | ſ       | Produktion and | l           | (05 b) +>       |

| -              | ×    |             |           |                         |         | "quickstart.sh |             |                 |

|                |      |             |           |                         |         |                | ι           | JG929_67_061212 |

Figure 2-7: Running the Quickstart Script

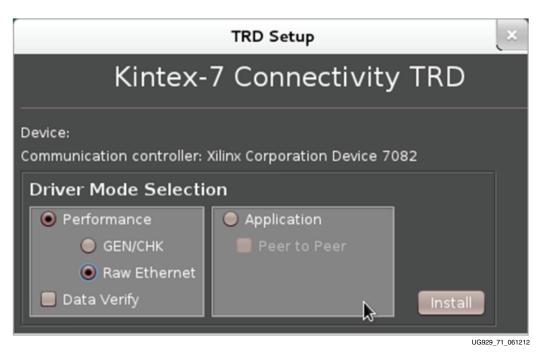

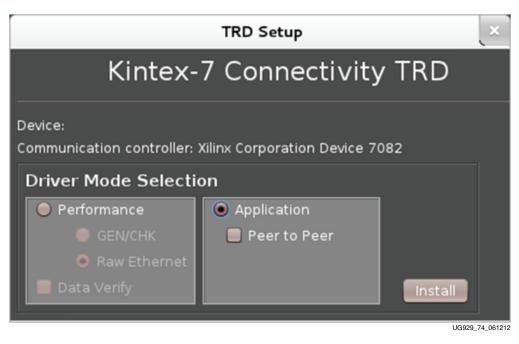

5. The GUI with driver installation option pops up as shown in Figure 2-8. The next steps demonstrate all modes of design operation by installing and un-installing various drivers.

Select **GEN/CHK** performance mode driver mode as shown in Figure 2-8 and click **Install**.

| Device:   Communication controller: Xilinx Corporation Device 7082   Driver Mode Selection <ul> <li>Performance</li> <li>GEN/CHK</li> <li>Raw Ethernet</li> <li>Data Verify</li> </ul> Install |                                                                        | TRD Setup      | ×       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|---------|

| Communication controller: Xilinx Corporation Device 7082                                                                                                                                       | Kintex-                                                                | 7 Connectivity | / TRD   |

| <ul> <li>Performance</li> <li>GEN/CHK</li> <li>Raw Ethernet</li> </ul>                                                                                                                         | Communication controller: X                                            |                | 082     |

|                                                                                                                                                                                                | <ul> <li>Performance</li> <li>GEN/CHK</li> <li>Raw Ethernet</li> </ul> | Application    | Install |

Figure 2-8: Landing Page of Kintex-7 TRD

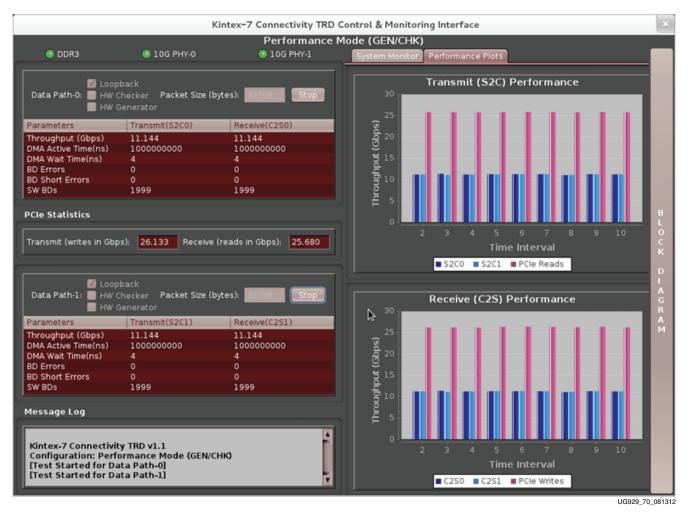

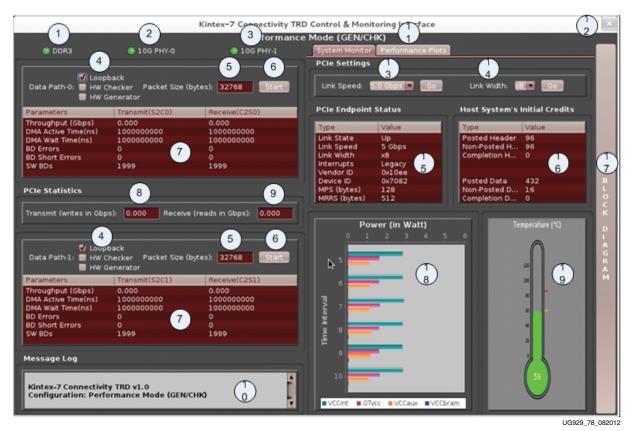

6. After installing the GEN/CHK performance mode driver, the control and monitor user interface pops up as shown in Figure 2-9. The control pane shows control parameters such as test mode (loopback, generator, or checker) and packet length. The user can select PCIe link width and speed while running a test if the host machine supports link width and speed configuration capability. The System Monitor tab in the GUI also shows system power and temperature. DDR3 ready status and 10GBASE-R link status are displayed on the top left corner of the GUI.

|                                       |                                   | Kintex-7 Connectivity TRD | Control & Monitoring Interface      |                                 | ×      |

|---------------------------------------|-----------------------------------|---------------------------|-------------------------------------|---------------------------------|--------|

|                                       |                                   | Performance               | Mode (GEN/CHK)                      |                                 |        |

| DDR3                                  | 10G PHY-0                         | 10G PHY-1                 | System Monitor Performance Pl       | lots                            |        |

|                                       |                                   |                           |                                     |                                 |        |

|                                       |                                   |                           | PCIe Settings                       |                                 |        |

| Loop                                  |                                   |                           |                                     |                                 |        |

|                                       | Checker Packet Size               | (bytes): 32768 Stop       | Link Speed: 5.0 Gbps 💌 🛛 Go         | Link Width: 🔀 🔽 🗔 Go            |        |

| I I I I I I I I I I I I I I I I I I I |                                   |                           |                                     |                                 |        |

| Parameters                            | Transmit(S2C0)                    | Receive(C2S0)             | PCIe Endpoint Status                | Host System's Initial Credits   |        |

| Throughput (Gbps)                     | 11.289                            | 11.289                    | 1                                   |                                 |        |

| DMA Active Time(ns)                   | 100000000                         | 100000000                 | Type Value                          | Type Value                      |        |

| DMA Wait Time(ns)                     | 4                                 | 4                         | Link State Up                       | Posted Header 96                |        |

| BD Errors                             |                                   |                           | Link Speed 5 Gbps                   | Non-Posted 96                   |        |

| BD Short Errors                       | 0                                 | 0                         | Link Width x8                       | Completion H 0                  |        |

| SW BDs                                | 1999                              | 1999                      | Interrupts Legacy                   |                                 |        |

|                                       |                                   |                           | Vendor ID 0x10ee                    |                                 |        |

| PCIe Statistics                       |                                   |                           | Device ID 0x7082                    | Posted Data 432                 | В      |

|                                       |                                   |                           | MPS (bytes) 128<br>MRRS (bytes) 512 | Non-Posted 16<br>Completion D 0 | ۵.     |

| Transmit (writes in Gbp               | os): 26.140 Receiv                | e (reads in Gbps): 25.689 | MRRS (bytes) 512                    | Completion D 0                  | c      |

|                                       |                                   |                           |                                     |                                 | К      |

|                                       |                                   |                           | Power (in Watt)                     | Temperature (*C)                |        |

| -                                     |                                   |                           |                                     | 5 6                             | D      |

| Loop                                  |                                   |                           |                                     |                                 | A      |

|                                       | Checker Packet Size               | (bytes): 32768 Stop       |                                     |                                 | G      |

| HW C                                  | Senerator                         |                           | 4                                   | 12                              | R      |

| Parameters                            | Transmit(S2C1)                    | Receive(C2S1)             |                                     |                                 | A<br>M |

| Throughput (Gbps)                     | 11.011                            | 11.011                    | 5                                   | 20                              | м      |

| DMA Active Time(ns)                   | 100000000                         | 100000000                 |                                     |                                 |        |

| DMA Wait Time(ns)                     | 12479860                          | 4                         |                                     | *                               |        |

| BD Errors                             | 0                                 | 0                         | 5 6                                 | a -                             |        |

| BD Short Errors                       | 0                                 | 0                         | 1 E                                 |                                 |        |

| SW BDs                                | 1999                              | 1999                      | Q 7-                                | 4                               |        |

|                                       |                                   |                           |                                     | 2                               |        |

| Message Log                           |                                   |                           |                                     |                                 |        |

|                                       |                                   |                           |                                     |                                 |        |

|                                       |                                   |                           |                                     |                                 |        |

| Kintex-7 Connectivit                  | ty TRD v1.1<br>ormance Mode (GEN/ |                           | 9-                                  | 54                              |        |

| [Test Started for Da                  |                                   | CHK                       |                                     |                                 |        |

| [Test Started for Da                  |                                   |                           |                                     |                                 |        |

|                                       |                                   | ×.                        | VCCint GTvcc VCCaux VCC             | Coram                           |        |

|                                       |                                   |                           |                                     | LIG929 69 0                     | 01212  |

Figure 2-9: GEN/CHK Performance Mode

www.xilinx.com

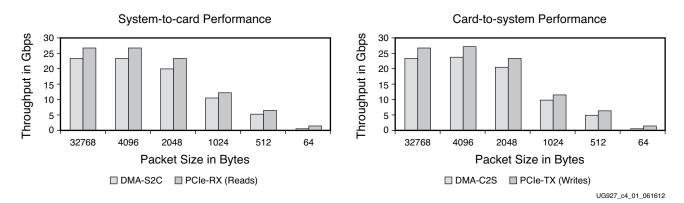

7. Click **Start** on both Data Path-0 and Data Path-1. Go to the Performance Plots tab. The Performance Plots tab shows the system-to-card and card-to-system performance numbers for a specific packet size. The user can vary packet size and see performance variation accordingly (see Figure 2-10).

Figure 2-10: GEN/CHK Performance Mode Plots

- 8. Close the GUI a pop up message asks whether you want to un-install the drivers. Click on **Yes**. This process opens the landing page of the Kintex-7 Connectivity TRD. (Driver un-installation requires the GUI to be closed first.)

- 9. Select **Raw Ethernet** performance as shown in Figure 2-11. Click **Install**.

Figure 2-11: Raw Ethernet Driver Installation

10. The GUI for raw Ethernet mode driver is invoked. The user can configure packet size in raw Ethernet mode and can control PCIe link width and speed change if the host machine supports this. The System Monitor tab monitors system power and temperature (see Figure 2-12).

| DDR3                                                                                                                                             | 10G PHY-0                                                                                          | Performance M<br>IOG PHY-1                                                 | Node (Raw Ethernet)<br>System Monitor Performance                             | e Plots                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------|

|                                                                                                                                                  |                                                                                                    |                                                                            | PCIe Settings                                                                 |                                                     |

|                                                                                                                                                  | iback<br>Checker <b>Packet Size</b> (<br>Generator                                                 | (bytes): 16383 Stop                                                        | Link Speed: 5.0 Gbps                                                          | Go Link Width: 🔀 🔽 Go                               |

| Parameters                                                                                                                                       | Transmit(S2C0)                                                                                     | Receive(C2S0)                                                              | PCIe Endpoint Status                                                          | Host System's Initial Credits                       |

| Throughput (Gbps)                                                                                                                                | 9.307                                                                                              | 9.308                                                                      |                                                                               |                                                     |

| DMA Active Time(ns)<br>DMA Wait Time(ns)                                                                                                         | 100000000                                                                                          | 100000000                                                                  | Type Value                                                                    | Type Value                                          |

| BD Errors                                                                                                                                        | 4                                                                                                  | 0                                                                          | Link State Up                                                                 | Posted Header 96                                    |

| BD Short Errors                                                                                                                                  | 0                                                                                                  | 0<br>0                                                                     | Link Speed 5 Gbps                                                             | Non-Posted 96                                       |

| SW BDs                                                                                                                                           | 1999                                                                                               | 1999                                                                       | Link Width x8<br>Interrupts Legacy                                            | Completion H 0                                      |

|                                                                                                                                                  |                                                                                                    |                                                                            | Vendor ID 0x10ee                                                              |                                                     |

|                                                                                                                                                  |                                                                                                    |                                                                            | Device ID 0x7082                                                              | Posted Data 432                                     |

| Clo Statistics                                                                                                                                   |                                                                                                    |                                                                            |                                                                               |                                                     |

| Cle Statistics                                                                                                                                   |                                                                                                    | e (reads in Gbps): 21.512                                                  | Power (in Watt)                                                               | Non-Posted 16<br>Completion D 0                     |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Hw (                                                                                             | back<br>;hecker Packet Size (<br>Senerator                                                         | (bytes): 16383 Stop                                                        | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)                        | Non-Posted 16<br>Completion D 0<br>Temperature (°C) |

| Transmit (writes in Gbp<br>Vata Path-1: Market In Goop<br>Data Path-1: Market In Market                                                          | back<br>Shecker Packet Size (                                                                      |                                                                            | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)                        | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: ■ Hw (<br>Parameters<br>Throughput (Gbps)                                                                | back<br>Checker Packet Size (<br>Senerator<br>Transmit(S2C1)<br>9.307                              | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309                              | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)                        | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)                                           | back<br>ihecker Packet Size (<br>Generator<br>Transmit(S2C1)<br>9.307<br>1000000000                | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>1000000000                | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)<br>0 1 2 3 4<br>4<br>5 | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)                                           | back<br>Checker Packet Size (<br>Generator<br>Transmit(S2C1)<br>9.307<br>1000000000<br>4           | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>1000000000<br>4           | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)<br>0 1 2 3 4<br>4<br>5 | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)<br>BMA Wait Time(ns)<br>BD Errors         | back<br>Checker Packet Size (<br>Senerator<br>Transmit(S2C1)<br>9.307<br>1000000000<br>4<br>0      | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>100000000<br>4<br>0       | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)<br>0 1 2 3 4<br>4<br>5 | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)                                           | back<br>Checker Packet Size (<br>Generator<br>Transmit(S2C1)<br>9.307<br>1000000000<br>4           | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>1000000000<br>4           | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)<br>0 1 2 3 4<br>4<br>5 | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)<br>BD Errors<br>BD Short Errors<br>SW BDs | back<br>Checker Packet Size (<br>Senerator<br>Transmit(S2C1)<br>9.307<br>1000000000<br>4<br>0<br>0 | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>1000000000<br>4<br>0<br>0 | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)                        | Non-Posted 16<br>Completion D 0                     |

| Transmit (writes in Gbp<br>Data Path-1: Hw (<br>Parameters<br>Throughput (Gbps)<br>DMA Active Time(ns)<br>BD Errors<br>BD Short Errors           | back<br>Checker Packet Size (<br>Senerator<br>Transmit(S2C1)<br>9.307<br>1000000000<br>4<br>0<br>0 | (bytes): 16383 Stop<br>Receive(C2S1)<br>9.309<br>1000000000<br>4<br>0<br>0 | MPS (bytes) 128<br>MRRS (bytes) 512<br>Power (in Watt)<br>0 1 2 3 4<br>4<br>5 | Non-Posted 16<br>Completion D 0<br>Temperature (*C) |

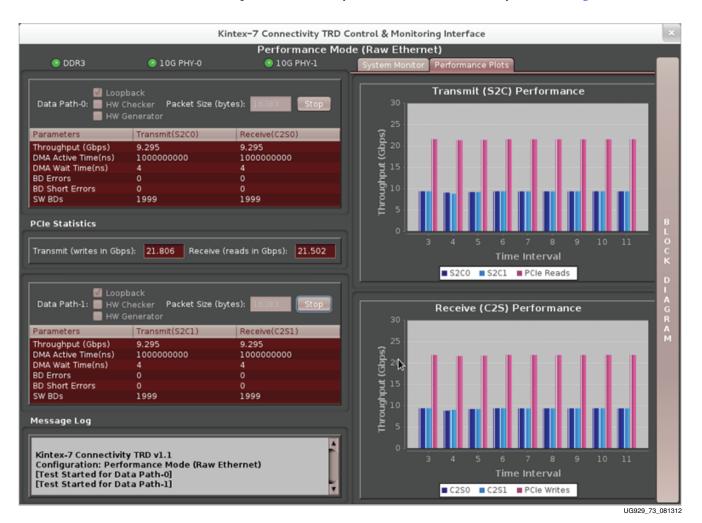

Figure 2-12: Raw Ethernet Driver GUI

11. Click **Start** on both Data Path-0 and Data Path-1. Navigate to the Performance Plots tab to see performance on system-to-card and card-to-system (see Figure 2-13).

Figure 2-13: Raw Ethernet Driver Performance Plots

- 12. Close the GUI this un-installs driver and opens the Kintex-7 Connectivity TRD landing page. Note that driver un-installation requires the GUI to be closed first.

- 13. Select the Application mode driver as shown in Figure 2-14. For using peer-peer option refer to Appendix C, Software Application and Network Performance. Click **Install**.

Figure 2-14: Application Mode Driver Installation

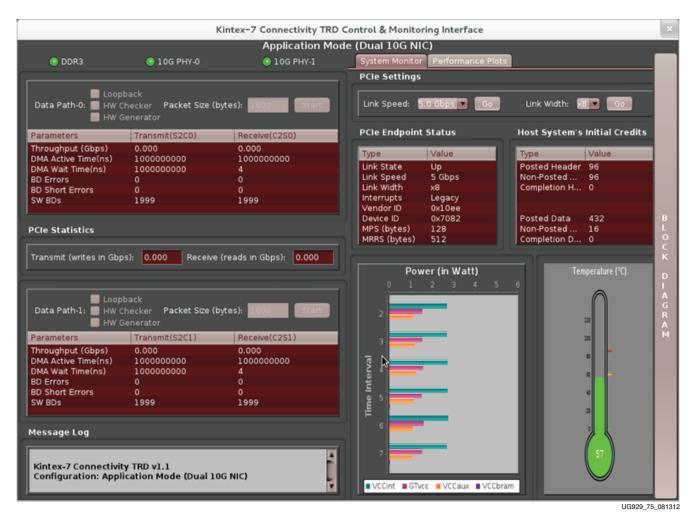

14. The GUI is invoked after the driver is installed. However, in application mode, the user cannot start or stop a test – the traffic is generated by the networking stack. The system monitor shows the system power and temperature (see Figure 2-15).

Figure 2-15: Application Mode Driver GUI

15. Open another terminal on the host machine and run ping (see Figure 2-16) using the following command:

\$ ping 10.60.0.1

\$ ping 10.60.1.1

```

liveuser@localhost:~

File Edit View Search Terminal Help

[liveuser@localhost ~]$ ping 10.60.0.1 -c 3

PING 10.60.0.1 (10.60.0.1) 56(84) bytes of data.

64 bytes from 10.60.0.1: icmp_req=1 ttl=64 time=1.64 ms

64 bytes from 10.60.0.1: icmp_req=2 ttl=64 time=1.82 ms

64 bytes from 10.60.0.1: icmp_req=3 ttl=64 time=1.83 ms

--- 10.60.0.1 ping statistics ---

3 packets transmitted, 3 received, 0% packet loss, time 2003ms

rtt min/avg/max/mdev = 1.643/1.766/1.831/0.087 ms

[liveuser@localhost ~]$ ping 10.60.1.1 -c 3

PING 10.60.1.1 (10.60.1.1) 56(84) bytes of data.

64 bytes from 10.60.1.1: icmp reg=1 ttl=64 time=1.94 ms

64 bytes from 10.60.1.1: icmp_req=2 ttl=64 time=1.85 ms

64 bytes from 10.60.1.1: icmp_req=3 ttl=64 time=1.82 ms

--- 10.60.1.1 ping statistics ---

3 packets transmitted, 3 received, 0% packet loss, time 2003ms

rtt min/avg/max/mdev = 1.823/1.873/1.947/0.072 ms

[liveuser@localhost ~]$

```

UG929\_76\_061412

Figure 2-16: Ping application on Application Mode Driver

- 16. The user can click on the Block Diagram option to view the design block diagram as shown in Figure 2-17.

- 17. Close the GUI this un-installs driver and opens the Kintex-7 Connectivity TRD landing page. Note that driver un-installation requires the GUI to be closed first.

Figure 2-17: Design Block Diagram

## **Ethernet Specific Features**

The Ethernet specific features can be exercised by using command line utilities such as **ifconfig** and **ethtool** present in Linux.

The Ethernet driver provides functions which are used by **ifconfig** and **ethtool** to report information about the NIC. The **ifconfig** utility is defined as the interface configurator and is used to configure the kernel-resident network interface and the TCP/ IP stack. It is commonly used for setting an interface's IP address and netmask and disabling or enabling a given interface apart from assigning MAC address, and changing maximum transfer unit (MTU) size. The **ethtool** utility is used to change or display Ethernet card settings. **ethtool** with a single argument specifying the device name prints the current setting of the specific device. More information about **ifconfig** and **ethtool** can be obtained from the manual (man) pages on Linux machines.

## **NIC Statistics**

The NIC statistics can be obtained using the **ethtool** command:

#### \$ethtool -S ethX

The error statistics are obtained by reading the registers provided by the Ethernet Statistics IP. PHY registers can be read using the following command:

\$ethtool -d ethX

Certain statistics can also be obtained from the **ifconfig** command:

\$ ifconfig ethX

## **Rebuilding the Design**

The design can also be re-implemented using ISE software. Before running any command line scripts, refer to the Platform Specific Instructions section in UG798, *ISE Design Suite: Installation and Licensing Guide* [Ref 2] to learn how to set the appropriate environment variables for the operating system. All scripts mentioned in this user guide assume that the XILINX environment variables have been set.

*Note:* The development machine does not have to be the hardware test machine with the PCIe slots used to run the TRD.

Copy the k7\_connectivity\_trd files to the PC with the ISE software installed.

The LogiCORE<sup>TM</sup> IP blocks required for the TRD are shipped as a part of the package. These cores and netlists are located in the k7\_connectivity\_trd/design/ip\_cores directory.

Detail of various IP cores under the <code>ip\_cores</code> directory can be obtained from <code>readme.txt</code>.

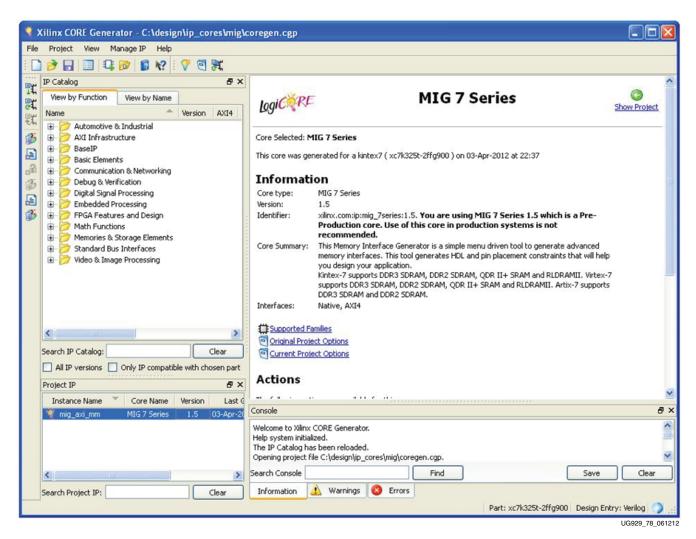

The MIG IP core is delivered through the CORE Generator<sup>™</sup> tool in the ISE software. The MIG IP core is not being delivered as a part of the TRD due to click-through license agreement with Micron for generation of DDR3 memory simulation model. This step should be completed before trying to implement or simulate the TRD.

## Generating the MIG IP Core through CORE Generator

- 1. Open a terminal window (Linux) or an ISE Design Suite command prompt (Windows).

- Navigate to k7\_connectivity\_trd/design/ip\_cores/mig. (This directory has mig\_axi\_mm.xco, mig.prj and coregen.cgp files.)

- 3. Invoke the Core Generator tool:

\$ coregen

- 4. In the Core Generator tool click File > Open project > Select coregen.cgp.

- 5. Double click instance name **mig\_axi\_mm** (as shown in Figure 2-18). This pops up the Memory Interface Generator GUI with the configuration defined by the mig\_axi\_mm.xco and mig.prj files.

Figure 2-18: MIG IP Core Generation

- Click Next to navigate to the Micron Tech Inc Simulation Model license agreement page. Select Accept and click Next. This selection generates the memory models required for simulation.

- 7. In the following page click **Next**. Then click **Generate** to create the MIG IP core.

- 8. Close the Readme Notes window and then the Core Generator GUI.

Additionally, a golden set of XCO files are also provided under the k7\_connectivity\_trd/design/reference directory so that the other cores can be regenerated, if desired.

### **Design Implementation**

Implementation scripts support command line mode and PlanAhead<sup>™</sup> design tool GUI mode for implementation on both Linux and Windows platforms.

#### Implementing the Design Using Command Line Options

Navigate to the k7\_connectivity\_trd/design/implement directory. At the command line of a terminal window (Linux) or ISE Design Suite command prompt (Windows), use one of these commands to invoke the ISE software tools and produce a BIT file and an MCS file in the results folder for download to the KC705 board:

```

$ source implement_k7_conn.sh (for Linux)

```

```

$ implement_k7_conn.bat (for Windows)

```

#### Implementing the Design Using the PlanAhead Design Tool

For PlanAhead design tool flow for Windows and Linux, navigate to design/ implement/planahead on a command window.

Run the following command to invoke the PlanAhead tool GUI with the design loaded:

\$ source launch\_pa.sh(Linux)

\$ launch\_pa.bat (Windows)

Click **Synthesize** in the Project Manager window. A window with the message *Synthesis completed successfully* appears after XST generates a design netlist. Close the message window.

Click **Implement** in the Project Manager window. A window with the message *Implementation completed successfully* appears after translate, map and par processes are done. Close the message window.

Expand Generate Bitstream in the left window. Click **Bitstream Settings**. An options window appears. In the column next to the -f field, browse to the directory design/ implement/planahead and select **bitgen\_options.ut**. Click **OK** to generate the bitstream. A window with the message *Bitstream generation successfully completed* appears at the end of this process.

Close the PlanAhead tool GUI.

Run the following command to generate an MCS file:

\$ genprom.bat (for Windows)

\$./genprom.sh (for Linux)

A promgen file is available in design/implement/planahead.

#### Implementing the Design Using the Vivado Flow

For Vivado flow for windows or Linux, open the ISE Design Suite command prompt and navigate to the design/implement/vivado folder.

To invoke the GUI mode flow:

\$ vivado -source k7\_conn\_gui.tcl

Once the GUI opens, click Generate Bitstream option in the left hand pane.

To use the batch mode flow:

\$ vivado -mode batch -source k7\_conn\_cmd.tcl

Both of these flows generate the results under the vivado\_run directory. The bitfile generated can be found under vivado\_run/k7\_connectivity\_trd.runs/impl\_1/k7\_connectivity\_trd.bit.

www.xilinx.com

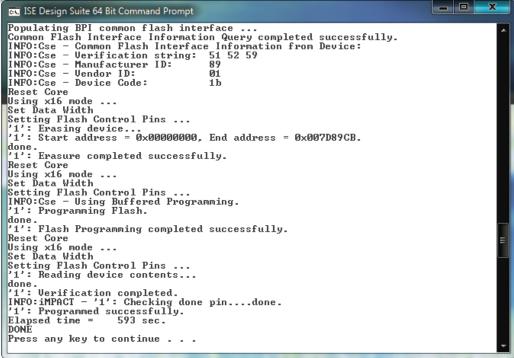

## Reprogramming the KC705

The KC705 board is shipped preprogrammed with the TRD, where the PCIe link is configured as x8 at a 5 Gb/s link rate. This procedure shows how to bring back the KC705 board to its original condition after another user has programmed it for a different operation or as a training aid for users to program their boards. The PCIe operation requires the use of the BPI flash mode of the KC705 board. This is the only configuration option that meets the strict programming time of PCI Express. Refer to UG477, 7 Series FPGA Integrated Block for PCI Express User Guide [Ref 4] for more information on PCIe configuration time requirements.

Ensure that the KC705 board switches and jumper settings are as shown in Figure 2-19. Connect the micro USB cable and use the power adapter to provide 12V power to the 6-pin connector as shown in the figure.

UG929\_79\_061212

#### Figure 2-19: Cable Installation for KC705 Board Programming

Copy the k7\_connectivity\_trd files to the PC with Xilinx programming tools or ISE Design Suite installed. Navigate to the k7\_connectivity\_trd/configuring\_kc705 directory. Execute the FPGA programming script at the command prompt:

- \$ kc705program.bat (for Windows)

- \$ impact -batch kc705program.cmd (for Linux)

This operation takes approximately 10 to 15 minutes to complete.

When complete, the *Programmed Successfully* message is displayed as shown in Figure 2-20. Remove the power connector and carefully remove the mini USB cable. The Kintex-7 Connectivity TRD is now programmed into the BPI flash and automatically configures at power up.

UG929\_80\_061212

Figure 2-20: KC705 Flash Programming on Windows

## Simulation

This section details the out-of-box simulation environment provided with the design. This simulation environment provides the user with a feel for the general functionality of the design. The simulation environment shows basic traffic movement end-to-end.

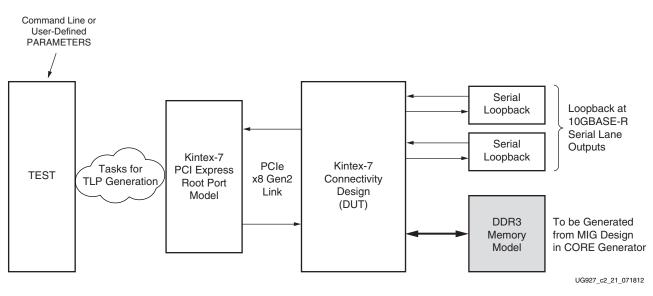

#### Overview

The out-of-box simulation environment consists of the design under test (DUT) connected to the Kintex-7 FPGA Root Port Model for PCI Express (see Figure 2-21). This simulation environment demonstrates the basic functionality of the TRD through various test cases. The out-of-box simulation environment demonstrates the end-to-end (in loopback mode) data flow for Ethernet packet.

The Root Port Model for PCI Express is a limited test bench environment that provides a test program interface. The purpose of the Root Port Model is to provide a source mechanism for generating downstream PCI Express traffic to simulate the DUT and a destination mechanism for receiving upstream PCI Express traffic from the DUT in a simulation environment.

The out-of-box simulation environment consists of:

- Root Port Model for PCI Express connected to the DUT

- Transaction Layer Packet (TLP) generation tasks for various programming operations

- Test cases to generate different traffic scenarios

Figure 2-21: Out-of-Box Simulation Overview

## Simulating the Design

To run the simulation, follow the steps outlined below.

- 1. When using ModelSim, be sure to compile the required libraries and set the environment variables as required before running the script. Refer to UG626, *Synthesis and Simulation Design Guide*, which provides information on how to run simulations with different simulators [Ref 5].

- 2. Execute the simulate\_mti.sh (on Linux) or *simulate\_mti.bat* (on Windows) under the design/sim/mti directory.

*Note:* Before running the simulation script, be sure to generate the MIG core through the CORE Generator tool, as described in Generating the MIG IP Core through CORE Generator.

#### **User-Controlled Macros**

The simulation environment allows the user to define macros that control DUT configuration. These values can be changed in the user defines.v file.

Table 2-1: User-Controlled Macro Descriptions

| Macro Name   | Default Value | Description                                         |

|--------------|---------------|-----------------------------------------------------|

| CH0          | Defined       | Enables Channel 0 initiali zation and traffic flow. |

| CH1          | Defined       | Enables Channel 1 initialization and traffic flow.  |

| DETAILED_LOG | Not Defined   | Enables a detailed log of each transaction.         |

Table 2-2: Macro Description for Design Change

| Macro Name    | Description                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------|

| DMA_LOOPBACK  | Connects the design in loopback mode at DMA user ports – no other macro should be defined.       |

| USE_DIFF_QUAD | Uses different quads for 10GBASE-R GT – either USE_DDR3_FIFO or USE_BRAM_FIFO should be defined. |

# **Test Selection**

Table 2-3 describes the various tests provided by the out-of-box simulation environment.

Table 2-3: Test Description

| Test Name        | Description                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| basic_test       | Basic Test<br>This test runs two packets for each DMA channel. One buffer<br>descriptor defines one full packet in this test.                                                                                                                                                                                   |

| packet_spanning  | Packet Spanning Multiple Descriptors<br>This test spans a packet across two buffer descriptors. It runs two<br>packets for each DMA channel.                                                                                                                                                                    |

| test_interrupts  | Interrupt Test<br>This test sets the interrupt bit in the descriptor and enables the<br>interrupt registers. This test also shows interrupt handling by<br>acknowledging relevant registers. In order to run this test, only<br>one channel (either CH0 or CH1) should be enabled in include/<br>user_defines.v |

| dma_disable      | DMA Disable Test<br>This test shows the DMA disable operation sequence on a DMA<br>channel.                                                                                                                                                                                                                     |

| pcie_link_change | PCIe Link Width & Speed Change Test<br>This test changes the PCIe link from x8 GEN2 to x4 GEN1 and<br>runs the test. This demonstrates how the demand driver power<br>management concept can be exercised by changing the PCIe link<br>configuration on the fly.                                                |

The name of the test to be run can be specified on the command line while invoking relevant simulators in the provided scripts. By default, the simulation script file specifies the basic test to be run using this syntax: **+TESTNAME=basic\_test**.

The test selection can be changed by specifying a different test case, as specified above.

# Chapter 3

# **Functional Description**

This chapter describes the hardware and software architecture in detail.

# **Hardware Architecture**

The hardware design architecture is described under the following sections:

- Base System Components: Describes PCIe-DMA and the DDR3 virtual FIFO components

- Application Components: Describes the user application design

- Utility Components: Describes the power monitor block, the PCIe link width and speed change module etc.

- Register Interface: Describes the control path of the design

- Clocking and Reset

## Base System Components

PCI Express® is a high-speed serial protocol that allows transfer of data between host system memory and Endpoint cards. To efficiently use the processor bandwidth, a bus mastering scatter-gather DMA controller is used to push and pull data from the system memory.

All data to and from the system is stored in the DDR3 memory through a multiport virtual FIFO abstraction layer before interacting with the user application.

#### PCI Express

The Kintex-7 FPGA integrated block for PCI Express provides a wrapper around the integrated block in the FPGA. The integrated block is compliant with the PCI Express v2.1 specification. It supports x1, x2, x4, x8 lane widths operating at 2.5 Gb/s (Gen1) or 5 Gb/s (Gen2) line rate per direction. The wrapper combines the Kintex-7 FPGA integrated block for PCI Express with transceivers, clocking, and reset logic to provide an industry standard AXI4-Stream interface as the user interface.

This TRD uses PCIe in x8 GEN2 configuration with credits/buffering enabled for high performance bus mastering applications.

For details on the Kintex-7 FPGA Integrated Block for PCI Express, refer to UG477, 7 Series FPGAs Integrated Block for PCI Express User Guide [Ref 4].

## Performance Monitor for PCI Express

This monitor snoops on the AXI4-Stream PCIe 128-bit interface operating at 250 MHz and provides the following measurements which are updated once every second:

- Count of active beats upstream which include the TLP headers for various transactions

- Count of active beats downstream which include the TLP headers for various transactions

- Count of payload bytes for upstream memory write transactions this includes buffer write (in C2S) and buffer descriptor updates (for both S2C and C2S)

- Count of payload bytes for downstream completion with data transactions this includes buffer fetch (in S2C) and buffer descriptor fetch (for both S2C and C2S)

These performance numbers measured are reflected in user space registers which software can read periodically and display.

| Port Name                | Туре        | Description                                                                                                                                                                                                                                       |

|--------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset                    | Input       | Synchronous reset.                                                                                                                                                                                                                                |

| clk                      | Input       | 250 MHz clock.                                                                                                                                                                                                                                    |

| Transmit Ports on the AX | I4-Stream I | nterface                                                                                                                                                                                                                                          |

| s_axis_tx_tdata[127:0]   | Input       | Data to be transmitted via PCIe link.                                                                                                                                                                                                             |

| s_axis_tx_tlast          | Input       | End of frame indicator on transmit packets. Valid only along with assertion of s_axis_tx_tvalid.                                                                                                                                                  |

| s_axis_tx_tvalid         | Input       | Source ready to provide transmit data. Indicates that the DMA is presenting valid data on s_axis_tx_tdata.                                                                                                                                        |

| s_axis_tx_tuser[3]       | Input       | Source discontinue on a transmit packet. Can be asserted any time starting on the first cycle after SOF. s_axis_tx_tlast should be asserted along with s_axis_tx_tuser[3] assertion.                                                              |

| s_axis_tx_tready         | Input       | Destination ready for transmit. Indicates that the core is ready to accept data on s_axis_tx_tdata. The simultaneous assertion of s_axis_tx_tvalid and s_axis_tx_tready marks the successful transfer of one data beat on s_axis_tx_tdata.        |

| Receive Ports on the AXI | 1-Stream In | terface                                                                                                                                                                                                                                           |

| m_axis_rx_tdata[127:0]   | Input       | Data received on the PCIe link. Valid only if m_axis_rx_tvalid is also asserted.                                                                                                                                                                  |

| m_axis_rx_tlast          | Input       | End of frame indicator for received packet. Valid only if m_axis_rx_tvalid is also asserted.                                                                                                                                                      |

| m_axis_rx_tvalid         | Input       | Source ready to provide receive data.Indicates that the core is presenting valid data on m_axis_rx_tdata.                                                                                                                                         |

| m_axis_rx_tready         | Input       | Destination ready for receive. Indicates that the DMA is ready to accept data<br>on m_axis_rx_tdata. The simultaneous assertion of m_axis_rx_tvalid and<br>m_axis_rx_tready marks the successful transfer of one data beat on<br>m_axis_rx_tdata. |

| Byte Count Ports         |             |                                                                                                                                                                                                                                                   |

| tx_byte_count[31:0]      | Output      | Raw transmit byte count.                                                                                                                                                                                                                          |

Table 3-1: Monitor Ports for PCI Express

| Port Name              | Туре   | Description                  |  |  |  |

|------------------------|--------|------------------------------|--|--|--|

| rx_byte_count[31:0]    | Output | Raw receive byte count.      |  |  |  |

| tx_payload_count[31:0] | Output | Transmit payload byte count. |  |  |  |

| rx_payload_count[31:0] | Output | Receive payload byte count.  |  |  |  |

Table 3-1: Monitor Ports for PCI Express (Cont'd)

**Note:** Start of packet is derived based on the signal values of source valid, destination ready, and end of packet indicator. The clock cycle after end of packet is deasserted and source valid is asserted indicates start of a new packet.

Four counters collect information about the transactions on the AXI4-Stream interface:

- TX Byte Count. This counter counts bytes transferred when the s\_axis\_tx\_tvalid and s\_axis\_tx\_tready signals are asserted between the packet DMA and the Kintex-7 FPGA integrated block for PCI Express. This value indicates the raw utilization of the PCIe transaction layer in the transmit direction, including overhead such as headers and non-payload data such as register access.

- RX Byte Count. This counter counts bytes transferred when the m\_axis\_rx\_tvalid and m\_axis\_rx\_tready signals are asserted between the packet DMA and the Kintex-7 FPGA integrated block for PCI Express. This value indicates the raw utilization of the PCIe transaction layer in the receive direction, including overhead such as headers and non-payload data such as register access.

- TX Payload Count. This counter counts all memory writes and completions in the transmit direction from the packet DMA to the host. This value indicates how much traffic on the PCIe transaction layer is from data, which includes the DMA buffer descriptor updates, completions for register reads, and the packet data moving from the user application to the host.

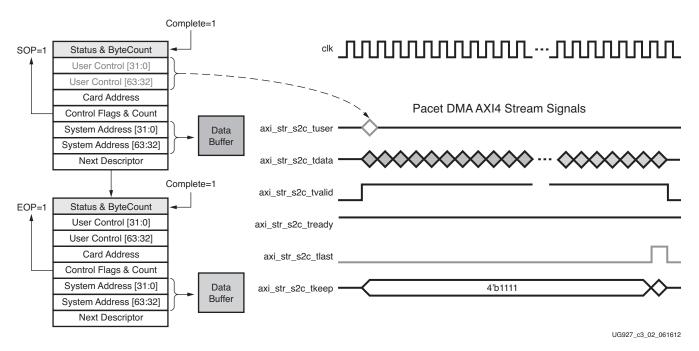

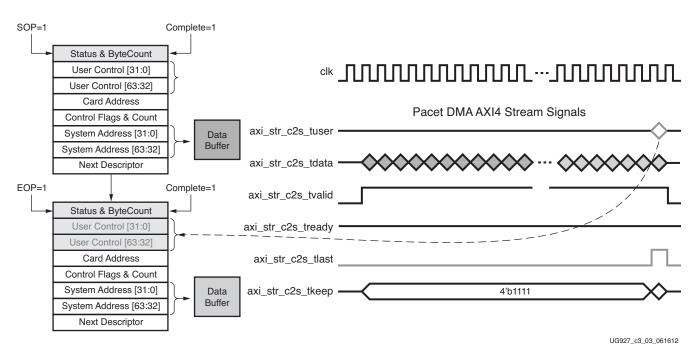

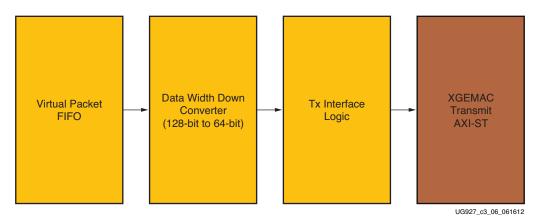

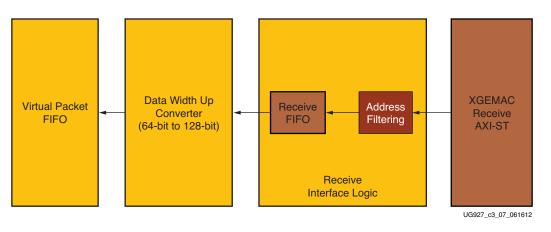

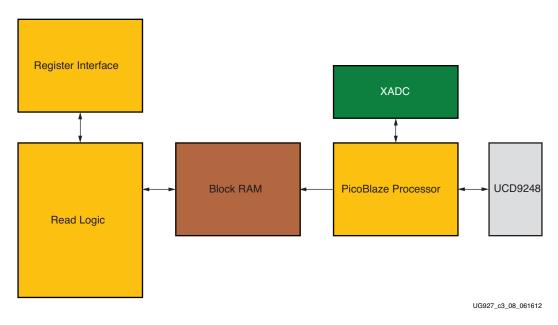

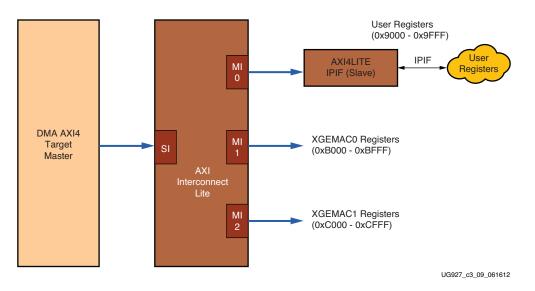

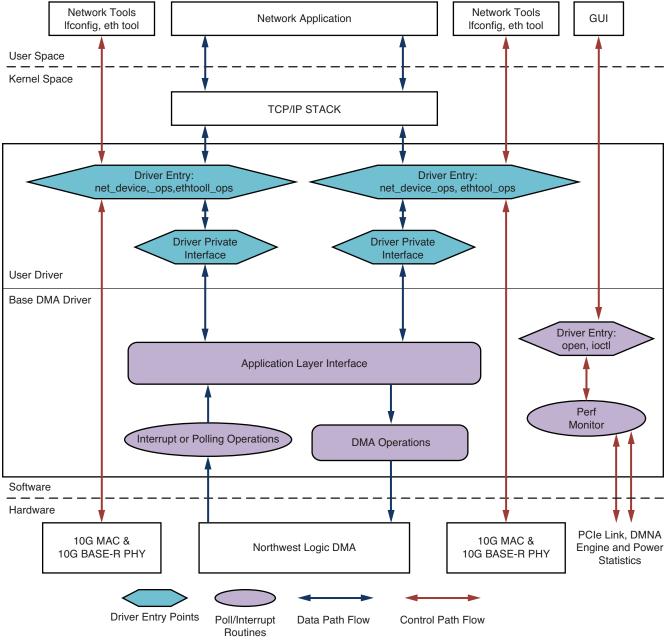

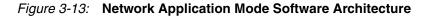

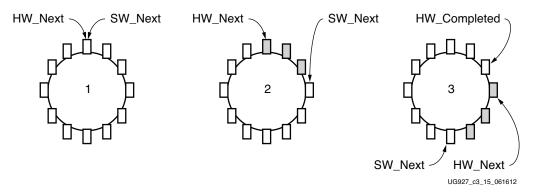

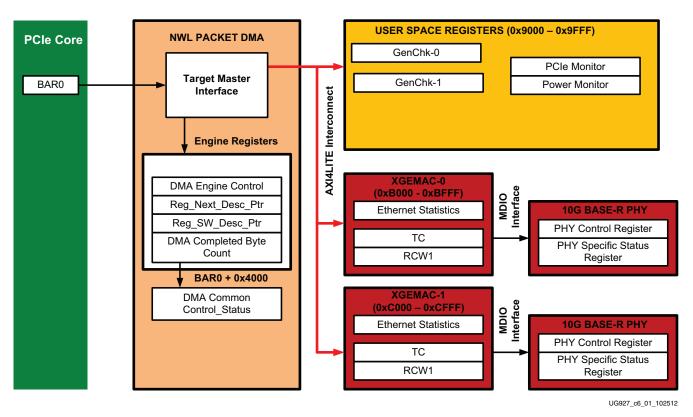

- RX Payload Count. This counter counts all memory writes and completions in the receive direction from the host to the DMA. This value indicates how much traffic on the PCIe transaction layer is from data, which includes the host writing to internal registers in the hardware design, completions for buffer description fetches, and the packet data moving from the host to user application.