# Flasher User Guide

Software Version V4.66 Manual Rev. 0

Date: April 4, 2013

**Document: UM08022**

A product of SEGGER Microconroller GmbH & Co. KG

www.segger.com

### **Disclaimer**

Specifications written in this document are believed to be accurate, but are not guaranteed to be entirely free of error. The information in this manual is subject to change for functional or performance improvements without notice. Please make sure your manual is the latest edition. While the information herein is assumed to be accurate, SEGGER Microcontroller GmbH & Co. KG (the manufacturer) assumes no responsibility for any errors or omissions. The manufacturer makes and you receive no warranties or conditions, express, implied, statutory or in any communication with you. The manufacturer specifically disclaims any implied warranty of merchantability or fitness for a particular purpose.

### Copyright notice

You may not extract portions of this manual or modify the PDF file in any way without the prior written permission of the manufacturer. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such a license.

© 2013 SEGGER Microcontroller GmbH & Co. KG, Hilden / Germany

### **Trademarks**

Names mentioned in this manual may be trademarks of their respective companies.

Brand and product names are trademarks or registered trademarks of their respective holders.

### **Contact address**

SEGGER Microcontroller GmbH & Co. KG

In den Weiden 11 D-40721 Hilden

Germany

Tel.+49 2103-2878-0 Fax.+49 2103-2878-28 Email: support@segger.com Internet: http://www.segger.com

#### Revisions

This manual describes the Flasher device.

For further information on topics or routines not yet specified, please contact us.

| Revision      | Date   | Ву | Explanation                                                                                               |

|---------------|--------|----|-----------------------------------------------------------------------------------------------------------|

| V4.64a Rev. 0 | 132602 | EL | Chapter "Working with Flasher"  * Section "LED status indicators" updated.                                |

| V4.63a Rev. 0 | 130131 | EL | Chapter "Remote Control"  * Section "ASCII command interface" Chapter "ASCII interface via Telnet" added. |

| V4.62 Rev. 0  | 130125 | EL | Flasher ARM, Flasher RX and Flasher PPC manual have been combined.                                        |

# **About this document**

This document describes the Flasher family (Flasher ARM, Flasher RX and Flasher PPC). It provides an overview about the major features of the Flasher, gives some background information about JTAG and describes Flasher related software packages available from Segger. Finally, the chapter *Support and FAQs* on page 61 helps to troubleshoot common problems.

For simplicity, we will refer to Flasher ARM/RX/PPC as Flasher in this manual.

### **Typographic conventions**

This manual uses the following typographic conventions:

| Style      | Used for                                                                                                                 |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Body       | Body text.                                                                                                               |  |  |

| Keyword    | Text that you enter at the command-prompt or that appears on the display (that is system functions, file- or pathnames). |  |  |

| Reference  | Reference to chapters, tables and figures or other documents.                                                            |  |  |

| GUIElement | Buttons, dialog boxes, menu names, menu commands.                                                                        |  |  |

Table 1.1: Typographic conventions

**SEGGER Microcontroller GmbH & Co. KG** develops and distributes software development tools and ANSI C software components (middleware) for embedded systems in several industries such as telecom, medical technology, consumer electronics, automotive industry and industrial automation.

SEGGER's intention is to cut software developmenttime for embedded applications by offering compact flexible and easy to use middleware, allowing developers to concentrate on their application.

Our most popular products are emWin, a universal graphic software package for embedded applications, and embOS, a small yet efficient real-time kernel. emWin, written entirely in ANSI C, can easily be used on any CPU and most any display. It is complemented by the available PC tools: Bitmap Converter, Font Converter, Simulator and Viewer. embOS supports most 8/16/32-bit CPUs. Its small memory footprint makes it suitable for single-chip applications.

Apart from its main focus on software tools, SEGGER develops and produces programming tools for flash microcontrollers, as well as J-Link, a JTAG emulator to assist in development, debugging and production, which has rapidly become the industry standard for debug access to ARM cores.

### **Corporate Office:**

http://www.segger.com

### **United States Office:**

http://www.segger-us.com

# EMBEDDED SOFTWARE (Middleware)

### emWin

### **Graphics software and GUI**

emWin is designed to provide an efficient, processor- and display controller-independent graphical user interface (GUI) for any application that operates with a graphical display. Starterkits, eval- and trial-versions are available.

#### embOS

### **Real Time Operating System**

embOS is an RTOS designed to offer the benefits of a complete multitasking system for hard real time applications with minimal resources. The profiling PC tool embOSView is included.

### emFile

### File system

emFile is an embedded file system with FAT12, FAT16 and FAT32 support. emFile has been optimized for minimum memory consumption in RAM and ROM while maintaining high speed. Various Device drivers, e.g. for NAND and NOR flashes, SD/MMC and CompactFlash cards, are available.

### emUSB

### **USB** device stack

A USB stack designed to work on any embedded system with a USB client controller. Bulk communication and most standard device classes are supported.

### **SEGGER TOOLS**

### **Flasher**

### Flash programmer

Flash Programming tool primarily for microcontrollers.

### **J-Link**

### JTAG emulator for ARM cores

USB driven JTAG interface for ARM cores.

#### **J-Trace**

#### JTAG emulator with trace

USB driven JTAG interface for ARM cores with Trace memory. supporting the ARM ETM (Embedded Trace Macrocell).

### J-Link / J-Trace Related Software

Add-on software to be used with SEGGER's industry standard JTAG emulator, this includes flash programming software and flash breakpoints.

# **Table of Contents**

| 1 | Introduction                                                                                                                                                                                                  | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                    |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | 1.1<br>1.1.1<br>1.1.2<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3                                                                                                                                                       | Flasher overview Features of Flasher Working environment Specifications Specifications for Flasher ARM Specifications for Flasher RX Specifications for Flasher PPC                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                    |

| 2 | Working v                                                                                                                                                                                                     | with Flasher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

|   | 2.1<br>2.1.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.5<br>2.6<br>2.6.1<br>2.7<br>2.7.1<br>2.7.2<br>2.7.3<br>2.8<br>2.8.1<br>2.8.2<br>2.8.3 | Setting up the IP interface Connecting the first time Operating modes J-Link mode Stand-alone mode MSD mode MsD mode Multiple File Support Serial number programming Serial number settings Serial number file Serial number list file Programming process Downloading serial number files to Flasher Sample setup Target interfaces Supported microcontrollers Flasher Support of external flashes Flasher ARM Flasher RX Flasher PPC Supported cores Flasher ARM Flasher ARM Flasher ARM Flasher RX Flasher ARM Flasher RX Flasher PPC | 18<br>19<br>24<br>26<br>26<br>27<br>28<br>31<br>32<br>33<br>33<br>33 |

| 3 | Remote c                                                                                                                                                                                                      | ontrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                   |

|   | 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6                                                                                                                                       | Overview Handshake control ASCII command interface Introduction General command and reply message format Settings for ASCII interface via RS232 Settings for ASCII interface via Telnet Commands to Flasher Reply from Flasher                                                                                                                                                                                                                                                                                                           | 38<br>38<br>38<br>38<br>38                                           |

| 4 | Performa                                                                                                                                                                                                      | nce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                                   |

|   | 4.1<br>4.1.1                                                                                                                                                                                                  | Performance of MCUs with internal flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

|   | 4.1.2<br>4.1.3                                                                                                 | Flasher RXFlasher PPC                                                                                                                                                                                                                                                                                             |                                                          |

|---|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 5 | Hardware                                                                                                       |                                                                                                                                                                                                                                                                                                                   | 49                                                       |

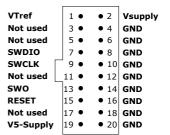

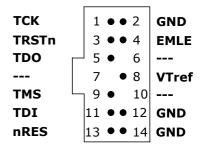

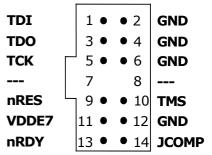

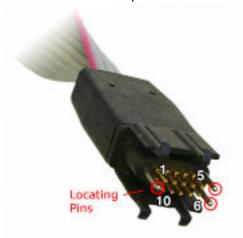

|   | 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.2.1<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.5<br>5.5.1<br>5.5.2<br>5.6 | Flasher ARM 20-pin JTAG/SWD Connector Pinout JTAG. Pinout SWD. Target power supply. Flasher RX 14-pin connector Target power supply Flasher PPC 14-pin connector. Target board design Pull-up/pull-down resistors RESET, nTRST Adapters JTAG Isolator J-Link Needle Adapter How to determine the hardware version | 50<br>51<br>53<br>53<br>55<br>56<br>56<br>56<br>57<br>57 |

| 6 | Support a                                                                                                      | nd FAQs                                                                                                                                                                                                                                                                                                           | 61                                                       |

|   | 6.1<br>6.2                                                                                                     | Contacting support  Frequently Asked Questions                                                                                                                                                                                                                                                                    | 62                                                       |

| 7 | Backgrou                                                                                                       | nd information                                                                                                                                                                                                                                                                                                    | 65                                                       |

|   | 7.1<br>7.1.1<br>7.1.2<br>7.1.3                                                                                 | Flash programming  How does flash programming via Flasher work?  Data download to RAM  Available options for flash programming                                                                                                                                                                                    | 66<br>66                                                 |

| 8 | Glossary.                                                                                                      |                                                                                                                                                                                                                                                                                                                   | 67                                                       |

| a | Literature                                                                                                     | and references                                                                                                                                                                                                                                                                                                    | 71                                                       |

# **Chapter 1**

# Introduction

This chapter gives a short overview about the different models of the Flasher family and their features.

## 1.1 Flasher overview

Flasher is a programming tool for microcontrollers with on-chip or external flash memory. Flasher is designed for programming flash targets with the J-Flash software or stand-alone. In addition to that Flasher can also be used as a regular J-Link. For more information about J-Link in general, please refer to the *J-Link / J-Trace User Guide* which can be downloaded at <a href="https://www.segger.com">http://www.segger.com</a>.

Flasher connects to a PC using the USB/Ethernet/RS232 interface, running Microsoft Windows 2000, Windows XP, Windows 2003, Windows Vista, Windows 7 or Windows 8. In stand-alone mode, Flasher can be driven by the start/stop button, or via the RS232 interface (handshake control or ASCII interface). Flasher always has a 20-pin connector, which target interfaces are supported depends on the Flasher model:

- For Flasher ARM: JTAG and SWD are supported.

- For Flasher RX: JTAG is supported. Flasher comes with additional 14-pin RX adapter

- For Flasher PPC: JTAG is supported. Flasher comes with additional 14-pin PPC adapter.

### 1.1.1 Features of Flasher

- Three boot modes: J-Link mode, stand-alone mode, MSD mode

- Stand-alone JTAG/SWD programmer (Once set up, Flasher can be controlled without the use of PC program)

- No power supply required, powered through USB

- Supports internal and external flash devices

- 64 MB memory for storage of target program

- Can be used as J-Link (emulator) with a download speed of up to 720 Kbytes/ second

- Serial in target programming supported

- Data files can updated via USB/Ethernet (using the J-Flash software), via RS232 or via the MSD functionality of Flasher

| Flasher model | Supported cores                       | Supported target interfaces | Flash programming speed (depending on target hardware) |

|---------------|---------------------------------------|-----------------------------|--------------------------------------------------------|

| Flasher ARM   | ARM7/ARM9/Cortex-M                    | JTAG, SWD                   | between 30-300 Kbytes/<br>second                       |

| Flasher RX    | Renesas RX610, RX621,<br>RX62N, RX62T | JTAG                        | between 170 and 300<br>Kbytes/second                   |

| Flasher PPC   | Power PC e200z0                       | JTAG                        | up to 138 Kbytes/second                                |

## 1.1.2 Working environment

### General

Flasher can operate from a PC with an appropriate software like J-Flash or in standalone mode.

### **Host System**

IBM PC/AT or compatible CPU: 486 (or better) with at least 128MB of RAM, running Microsoft Windows 2000, Windows XP, Windows 2003, Windows Vista, Windows 7 or Windows 8. It needs to have a USB, Ethernet or RS232 interface available for communication with Flasher.

### **Power supply**

Flasher requires 5V DC, min. 100mA via USB connector. If USB is not connected, the USB connector is used to power the device. Supply voltage is the same in this case. Please avoid excess voltage.

### **Installing Flasher PC-software J-Flash**

The latest version of the J-Flash software, which is part of the J-Link software and documentation package, can always be downloaded from our website: <a href="http://www.segger.com/download\_jlink.html">http://www.segger.com/download\_jlink.html</a>. For more information about using J-Flash please refer to <a href="http://www.segger.com/download\_jlink.html">UM08007\_FlasherARM.pdf</a> (J-Flash user guide) which is also available for download on our website.

# 1.2 Specifications

# 1.2.1 Specifications for Flasher ARM

| General                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Microsoft Windows 2000 Microsoft Windows XP Microsoft Windows XP x64 Microsoft Windows 2003 Microsoft Windows 2003 x64 Microsoft Windows Vista Microsoft Windows Vista x64 Microsoft Windows 7 Microsoft Windows 7 x64 Microsoft Windows 8 |  |  |  |  |

| Microsoft Windows 8 x64<br>+5 °C +60 °C                                                                                                                                                                                                    |  |  |  |  |

| -20 °C +60 °C                                                                                                                                                                                                                              |  |  |  |  |

| <90% rH                                                                                                                                                                                                                                    |  |  |  |  |

| anical                                                                                                                                                                                                                                     |  |  |  |  |

| 121mm x 66mm x 30mm                                                                                                                                                                                                                        |  |  |  |  |

| 119g                                                                                                                                                                                                                                       |  |  |  |  |

| interfaces                                                                                                                                                                                                                                 |  |  |  |  |

| USB 2.0, full speed                                                                                                                                                                                                                        |  |  |  |  |

| 10/100 MBit                                                                                                                                                                                                                                |  |  |  |  |

| RS232 9-pin                                                                                                                                                                                                                                |  |  |  |  |

| JTAG 20-pin (14-pin adapter available)                                                                                                                                                                                                     |  |  |  |  |

| Target interface JTAG 20-pin (14-pin adapter available)  JTAG Interface, Electrical                                                                                                                                                        |  |  |  |  |

| USB powered, 100mA for Flasher ARM.<br>500 mA if target is powered by Flasher<br>ARM                                                                                                                                                       |  |  |  |  |

| 1.2 5V                                                                                                                                                                                                                                     |  |  |  |  |

| 4.5V5V (on the 14-pin adapter the target supply voltage can be switched between 3.3V and 5V)                                                                                                                                               |  |  |  |  |

| max. 400mA                                                                                                                                                                                                                                 |  |  |  |  |

| Open drain. Can be pulled low or tristated                                                                                                                                                                                                 |  |  |  |  |

| $V_{OL} \le 10\%$ of $V_{IF}$                                                                                                                                                                                                              |  |  |  |  |

| ge range (1.8V <= V <sub>IF</sub> <= 5V)                                                                                                                                                                                                   |  |  |  |  |

| $V_{IL} <= 40\%$ of $V_{IF}$                                                                                                                                                                                                               |  |  |  |  |

| $V_{IH} >= 60\%$ of $V_{IF}$                                                                                                                                                                                                               |  |  |  |  |

| : V <sub>IF</sub> <= 3.6V                                                                                                                                                                                                                  |  |  |  |  |

| $V_{OL} \le 10\%$ of $V_{IF}$                                                                                                                                                                                                              |  |  |  |  |

| $V_{OH} >= 90\%$ of $V_{IF}$                                                                                                                                                                                                               |  |  |  |  |

| load of 10 kOhm                                                                                                                                                                                                                            |  |  |  |  |

| $V_{OL}$ <= 20% of $V_{IF}$                                                                                                                                                                                                                |  |  |  |  |

|                                                                                                                                                                                                                                            |  |  |  |  |

**Table 1.1: Flasher ARM specifications**

| HIGH level output voltage ( $V_{OH}$ ) with a load of 10 kOhm | $V_{OH} >= 80\%$ of $V_{IF}$ |

|---------------------------------------------------------------|------------------------------|

| JTAG Interf                                                   | ace, Timing                  |

| Max. JTAG speed                                               | up to 12MHz                  |

| Data input rise time (T <sub>rdi</sub> )                      | T <sub>rdi</sub> <= 20ns     |

| Data input fall time (T <sub>fdi</sub> )                      | T <sub>fdi</sub> <= 20ns     |

| Data output rise time (T <sub>rdo</sub> )                     | T <sub>rdo</sub> <= 10ns     |

| Data output fall time (T <sub>fdo</sub> )                     | T <sub>fdo</sub> <= 10ns     |

| Clock rise time (T <sub>rc</sub> )                            | T <sub>rc</sub> <= 10ns      |

| Clock fall time (T <sub>fc</sub> )                            | T <sub>fc</sub> <= 10ns      |

**Table 1.1: Flasher ARM specifications**

### 1.2.1.1 Flasher ARM download speed

The following table lists Flasher ARM performance values (Kbytes/second) for writing to memory (RAM) via the JTAG interface:

| Hardware    | ARM7 memory download      |

|-------------|---------------------------|

| Flasher ARM | 720 Kbytes/s (12MHz JTAG) |

Table 1.2: Download speed of Flasher ARM

**Note:** The actual speed depends on various factors, such as JTAG, clock speed, host CPU core etc.

# 1.2.2 Specifications for Flasher RX

| General                                             |                                                   |  |  |  |

|-----------------------------------------------------|---------------------------------------------------|--|--|--|

| Ger                                                 |                                                   |  |  |  |

|                                                     | Microsoft Windows 2000<br>Microsoft Windows XP    |  |  |  |

|                                                     | Microsoft Windows XP Microsoft Windows XP x64     |  |  |  |

|                                                     | Microsoft Windows XP X64 Microsoft Windows 2003   |  |  |  |

|                                                     | Microsoft Windows 2003 Microsoft Windows 2003 x64 |  |  |  |

| Supported OS                                        | Microsoft Windows Vista                           |  |  |  |

| Supported OS                                        | Microsoft Windows Vista x64                       |  |  |  |

|                                                     | Microsoft Windows 7                               |  |  |  |

|                                                     | Microsoft Windows 7 x64                           |  |  |  |

|                                                     | Microsoft Windows 8                               |  |  |  |

|                                                     | Microsoft Windows 8 x64                           |  |  |  |

| Operating Temperature                               | +5 °C +60 °C                                      |  |  |  |

| Storage Temperature                                 | -20 °C +60 °C                                     |  |  |  |

| Relative Humidity (non-condensing)                  | <90% rH                                           |  |  |  |

| , ,                                                 | anical                                            |  |  |  |

|                                                     | 121mm x 66mm x 30mm                               |  |  |  |

| Size (without cables)                               |                                                   |  |  |  |

| Weight (without cables)                             | 119g                                              |  |  |  |

|                                                     | interfaces                                        |  |  |  |

| USB Host interface                                  | USB 2.0, full speed                               |  |  |  |

| Ethernet Host interface                             | 10/100 MBit                                       |  |  |  |

| RS232 Host interface                                | RS232 9-pin                                       |  |  |  |

| Target interface                                    | JTAG 20-pin (shipped with 14-pin adapter          |  |  |  |

| larget interrace                                    | for Renesas RX)                                   |  |  |  |

| JTAG Interface, Electrical                          |                                                   |  |  |  |

|                                                     | USB powered, 100mA for Flasher ARM.               |  |  |  |

| Power Supply                                        | 500 mA if target is powered by Flasher            |  |  |  |

|                                                     | ARM                                               |  |  |  |

| Target interface voltage (VIF)                      | 1.2 5V                                            |  |  |  |

|                                                     | 4.5V5V (on the 14-pin adapter the tar-            |  |  |  |

| Target supply voltage                               | get supply voltage can be switched                |  |  |  |

|                                                     | between 3.3V and 5V)                              |  |  |  |

| Target supply current                               | max. 400mA                                        |  |  |  |

| Reset Type                                          | Open drain. Can be pulled low or tristated        |  |  |  |

| Reset low level output voltage (V <sub>OL</sub> )   | $V_{OL}$ <= 10% of $V_{IF}$                       |  |  |  |

| For the whole target voltage                        | ge range (1.8V <= V <sub>IF</sub> <= 5V)          |  |  |  |

| LOW level input voltage (V <sub>II</sub> )          | $V_{IL}$ <= 40% of $V_{IF}$                       |  |  |  |

| HIGH level input voltage (V <sub>IH</sub> )         | $V_{IH} >= 60\%$ of $V_{IF}$                      |  |  |  |

|                                                     |                                                   |  |  |  |

| For 1.8V <= V <sub>IF</sub> <= 3.6V                 |                                                   |  |  |  |

| LOW level output voltage ( $V_{OL}$ ) with a        | $V_{OL} \le 10\%$ of $V_{IF}$                     |  |  |  |

| load of 10 kOhm                                     | - OL                                              |  |  |  |

| HIGH level output voltage ( $V_{OH}$ ) with a       | $V_{OH} >= 90\%$ of $V_{IF}$                      |  |  |  |

| load of 10 kOhm                                     | VOH 7 - 30 /0 OF VIE                              |  |  |  |

| For 3.6 <=                                          | = V <sub>IF</sub> <= 5V                           |  |  |  |

| LOW level output voltage (V <sub>OL</sub> ) with a  | Va. <- 20% of V                                   |  |  |  |

| load of 10 kOhm                                     | $V_{OL} \le 20\%$ of $V_{IF}$                     |  |  |  |

| HIGH level output voltage (V <sub>OH</sub> ) with a | V > - 900/ of V                                   |  |  |  |

| load of 10 kOhm                                     | $V_{OH} >= 80\%$ of $V_{IF}$                      |  |  |  |

|                                                     | 1                                                 |  |  |  |

**Table 1.3: Flasher RX specifications**

| JTAG Interface, Timing                    |                          |  |

|-------------------------------------------|--------------------------|--|

| Max. JTAG speed                           | up to 12MHz              |  |

| Data input rise time (T <sub>rdi</sub> )  | T <sub>rdi</sub> <= 20ns |  |

| Data input fall time (T <sub>fdi</sub> )  | T <sub>fdi</sub> <= 20ns |  |

| Data output rise time (T <sub>rdo</sub> ) | T <sub>rdo</sub> <= 10ns |  |

| Data output fall time (T <sub>fdo</sub> ) | T <sub>fdo</sub> <= 10ns |  |

| Clock rise time (T <sub>rc</sub> )        | T <sub>rc</sub> <= 10ns  |  |

| Clock fall time (T <sub>fc</sub> )        | T <sub>fc</sub> <= 10ns  |  |

**Table 1.3: Flasher RX specifications**

### 1.2.2.1 Flasher RX download speed

The following table lists Flasher RX performance values (Kbytes/second) for writing to memory (RAM) via the JTAG interface:

| Hardware   | Flasher RX600 series memory download |  |

|------------|--------------------------------------|--|

| Flasher RX | 720 Kbytes/s (12MHz JTAG)            |  |

Table 1.4: Download speed of Flasher RX

**Note:** The actual speed depends on various factors, such as JTAG, clock speed, host CPU core etc.

# 1.2.3 Specifications for Flasher PPC

| General                                                               |                                                                                |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

|                                                                       | Microsoft Windows 2000                                                         |  |  |  |

|                                                                       | Microsoft Windows XP                                                           |  |  |  |

|                                                                       | Microsoft Windows XP x64                                                       |  |  |  |

|                                                                       | Microsoft Windows 2003                                                         |  |  |  |

|                                                                       | Microsoft Windows 2003 x64                                                     |  |  |  |

| Supported OS                                                          | Microsoft Windows Vista                                                        |  |  |  |

|                                                                       | Microsoft Windows Vista x64                                                    |  |  |  |

|                                                                       | Microsoft Windows 7 Microsoft Windows 7 x64                                    |  |  |  |

|                                                                       | Microsoft Windows 7 x64 Microsoft Windows 8                                    |  |  |  |

|                                                                       | Microsoft Windows 8 x64                                                        |  |  |  |

| Operating Temperature                                                 | +5 °C +60 °C                                                                   |  |  |  |

| Storage Temperature                                                   | -20 °C +60 °C                                                                  |  |  |  |

| Relative Humidity (non-condensing)                                    | <90% rH                                                                        |  |  |  |

|                                                                       |                                                                                |  |  |  |

|                                                                       | nanical                                                                        |  |  |  |

| Size (without cables)                                                 | 121mm x 66mm x 30mm                                                            |  |  |  |

| Weight (without cables)                                               | 119g                                                                           |  |  |  |

| Available                                                             | interfaces                                                                     |  |  |  |

| USB Host interface                                                    | USB 2.0, full speed                                                            |  |  |  |

| Ethernet Host interface                                               | 10/100 MBit                                                                    |  |  |  |

| RS232 Host interface                                                  | RS232 9-pin                                                                    |  |  |  |

| Toward intention                                                      | JTAG 20-pin (shipped with 14-pin adapter                                       |  |  |  |

| Target interface                                                      | for Renesas PPC)                                                               |  |  |  |

| JTAG Interfa                                                          | ice, Electrical                                                                |  |  |  |

| Power Supply                                                          | USB powered, 100mA for Flasher ARM. 500 mA if target is powered by Flasher ARM |  |  |  |

| Target interface voltage (VIF)                                        | 1.2 5V                                                                         |  |  |  |

| rarget interface voltage (vir)                                        | 4.5V5V (on the 14-pin adapter the tar-                                         |  |  |  |

| Target supply voltage                                                 | get supply voltage can be switched between 3.3V and 5V)                        |  |  |  |

| Target supply current                                                 | max. 400mA                                                                     |  |  |  |

| Reset Type                                                            | Open drain. Can be pulled low or tristated                                     |  |  |  |

| Reset low level output voltage (V <sub>OL</sub> )                     | $V_{OL} \le 10\%$ of $V_{IF}$                                                  |  |  |  |

| For the whole target voltage                                          | ge range (1.8V <= V <sub>IF</sub> <= 5V)                                       |  |  |  |

| LOW level input voltage (V <sub>II</sub> )                            | $V_{II} <= 40\%$ of $V_{IF}$                                                   |  |  |  |

| HIGH level input voltage (V <sub>IH</sub> )                           | $V_{IH} >= 60\%$ of $V_{IF}$                                                   |  |  |  |

| , 2117                                                                |                                                                                |  |  |  |

| For 1.8V <= V <sub>IF</sub> <= 3.6V                                   |                                                                                |  |  |  |

| LOW level output voltage (V <sub>OL</sub> ) with a<br>load of 10 kOhm | $V_{OL} \le 10\%$ of $V_{IF}$                                                  |  |  |  |

| HIGH level output voltage ( $V_{OH}$ ) with a load of 10 kOhm         | $V_{OH} >= 90\%$ of $V_{IF}$                                                   |  |  |  |

| For 3.6 <                                                             | = V <sub>IF</sub> <= 5V                                                        |  |  |  |

| LOW level output voltage (V <sub>OL</sub> ) with a load of 10 kOhm    | $V_{OL}$ <= 20% of $V_{IF}$                                                    |  |  |  |

| HIGH level output voltage ( $V_{OH}$ ) with a load of 10 kOhm         | $V_{OH} >= 80\%$ of $V_{IF}$                                                   |  |  |  |

**Table 1.5: Flasher PPC specifications**

| JTAG Interface, Timing                    |                          |  |

|-------------------------------------------|--------------------------|--|

| Max. JTAG speed                           | up to 12MHz              |  |

| Data input rise time (T <sub>rdi</sub> )  | T <sub>rdi</sub> <= 20ns |  |

| Data input fall time (T <sub>fdi</sub> )  | T <sub>fdi</sub> <= 20ns |  |

| Data output rise time (T <sub>rdo</sub> ) | T <sub>rdo</sub> <= 10ns |  |

| Data output fall time (T <sub>fdo</sub> ) | T <sub>fdo</sub> <= 10ns |  |

| Clock rise time (T <sub>rc</sub> )        | T <sub>rc</sub> <= 10ns  |  |

| Clock fall time (T <sub>fc</sub> )        | T <sub>fc</sub> <= 10ns  |  |

**Table 1.5: Flasher PPC specifications**

### 1.2.3.1 Flasher PPC download speed

The following table lists Flasher PPC performance values (Kbytes/second) for writing to memory (RAM) via the JTAG interface:

| Hardware    | Memory download           |

|-------------|---------------------------|

| Flasher PPC | 530 Kbytes/s (8 MHz JTAG) |

Table 1.6: Download speed of Flasher PPC

**Note:** The actual speed depends on various factors, such as JTAG, clock speed, host CPU core etc.

# **Chapter 2**

# **Working with Flasher**

This chapter describes functionality and how to use Flasher.

# 2.1 Setting up the IP interface

Since hardware version 3 Flasher family comes with an additional Ethernet interface to communicate with the host system. These Flashers also come with a built-in webserver which allows some basic setup of the emulator, e.g. configuring a default gateway which allows using it even in large intranets.

## 2.1.1 Connecting the first time

When connecting Flasher the first time, it attempts to acquire an IP address via DHCP. The recommended way for finding out which IP address has been assigned to Flasher is, to use the J-Link Configurator. The J-Link Configurator is a small GUI-based utility which shows a list of all emulator that are connected to the host PC via USB and Ethernet. For more information about the J-Link Configurator, please refer to UM08001\_JLinkARM.pdf (J-Link / J-Trace user guide), chapter Setup, section J-Link Configurator. The setup of the IP interface of Flasher is the same as for other emulators of the J-Link family. For more information about how to setup the IP interface of Flasher, please refer to UM08001, J-Link / J-Trace User Guide, chapter Setup, section Setting up the IP interface. For more information about how to use Flasher via Ethernet or prepare Flasher via Ethernet for stand-alone mode, please refer to Operating modes on page 19.

## 2.2 Operating modes

Flasher is able to boot in 3 different modes:

- J-Link mode

- Stand-alone mode

- MSD (Mass storage device) mode

If Flasher can establish an Ethernet uplink or can enumerate on the USB port, it boots in "J-Link mode". In this mode, Flasher can be used as a J-Link. When supply power is enabled and Flasher can not establish a connection with the host, the "stand-alone mode" is started. In this mode Flasher can be used as a stand-alone flash programmer. When the Start/Stop button is pressed when power supply is enabled, Flasher boots in "MSD mode". In this mode, Flasher boots as a mass storage device.

### 2.2.1 J-Link mode

If you want to use Flasher for the first time you need to install the J-Link software and documentation package. After installation, connect Flasher to the host PC via USB or Ethernet. For more information about how to install the J-Link software and documentation package please refer to the *J-Link / J-Trace User Guide*, chapter Setup which can be downloaded from http://www.segger.com/download\_jlink.html.

### 2.2.1.1 Connecting the target system

### Power-on sequence

In general, Flasher should be powered on before connecting it with the target device. That means you should first connect Flasher with the host system via USB / Ethernet and then connect Flasher with the target device via JTAG or SWD. Power-on the device after you connected Flasher to it. Flasher will boot in "J-Link mode".

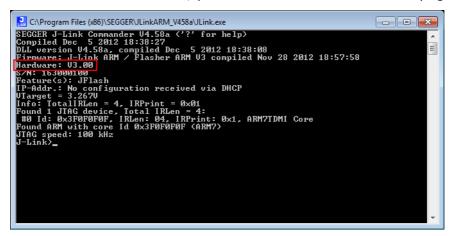

### Verifying target device connection with J-Link.exe

If the USB driver is working properly and your Flasher is connected with the host system, you may connect Flasher to your target hardware. Then start the J-Link command line tool  $\mathtt{JLink.exe}$ , which should now display the normal Flasher related information and in addition to that it should report that it found a JTAG target and the targets core ID. The screenshot below shows the output of  $\mathtt{JLink.exe}$ .

```

SEGGER J-Link Commander U4.58a ('?' for help)

Compiled Dec 5 2012 18:38:27

DLL version U4.58a, compiled Dec 5 2012 18:38:08

Firmware: J-Link ARM / Flasher ARM U3 compiled Nov 28 2012 18:57:58

Hardware: U3.00

S/N: 163000100

Feature(s): JFlash

IP-Addr.: No configuration received via DHCP

U1arget = 3.267U

Info: TotalIRLen = 4, IRPrint = 0x01

Found 1 JTAG device, Total IRLen = 4:

#0 Id: 0x3F0F0F0F, IRLen: 04, IRPrint: 0x1, ARM7TDMI Core

Found ARM with core Id 0x3F0F0F0F (ARM7)

JTAG speed: 100 kHz

J-Link>_______

```

## 2.2.1.2 Setting up Flasher for stand-alone mode

In order to set up Flasher for the stand-alone mode it needs to be configured once using the J-Flash software. For more information about J-Flash, please refer to the *J-Flash User Guide*.

After starting J-Flash, open the appropriate J-Flash project for the target Flasher shall be configured for, by selecting **File** -> **Open Project**. If J-Flash does not come with an appropriate sample project for the desired hardware, a new project needs to be created by selecting **File** -> **New Project**.

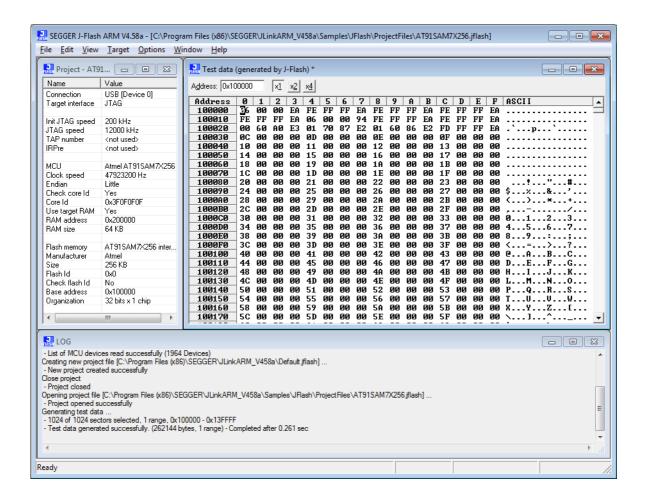

After the appropriate project has been opened / created, the data file which shall be programmed needs to be loaded, by selecting **File** -> **Open**. After this J-Flash should look like in the screenshot below.

Before downloading the configuration (project) and program data (data file) to Flasher, the connection type (USB/IP) needs to be selected in the project. These settings are also saved on a per-project basis, so this also only needs to be setup once per J-Flash project. The connection dialog is opened by clicking Options -> Project settings -> General.

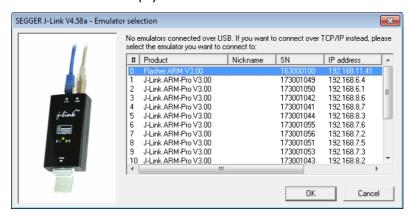

The connection dialog allows the user to select how to connect to Flasher. When connecting to a Flasher via TCP/IP it is not mandatory to enter an IP address. If the field is left blank and File->Download to programmer is selected, an emulator selection dialog pops up which shows all Flasher which have been found on the network. The user then can simply select the Flash he wants to download the configuration to.

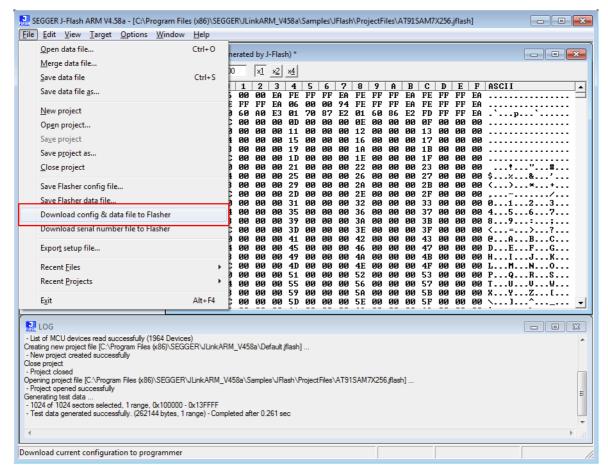

In order to download the configuration and program data to the Flasher, simply select File -> Download config & data file to Flasher.

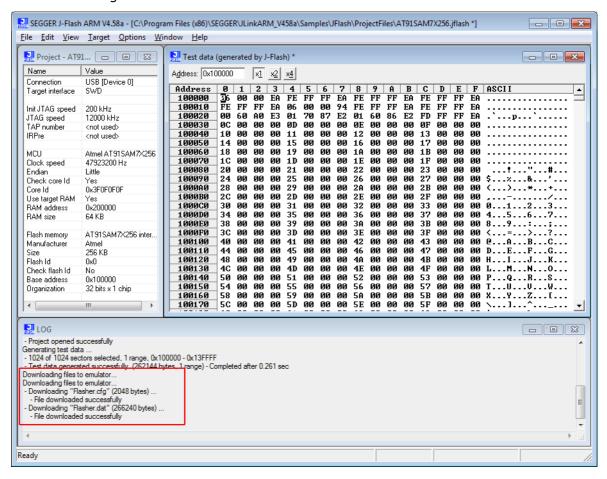

The J-Flash log window indicates that the download to the emulator was successful.

From now on, Flasher can be used in stand-alone mode (without host PC interaction) for stand-alone programming.

### 2.2.2 Stand-alone mode

In order to use Flasher in "stand-alone mode", it has to be configured first, as described in *Setting up Flasher for stand-alone mode* on page 19. To boot Flasher in the "stand-alone mode", only the power supply to Flasher has to be enabled (Flasher should not be connected to a PC). In the "stand-alone mode" Flasher can be used as a stand-alone flash programmer.

**Note:** Flasher can only program the target device it was configured for. In order to program another target device, you have to repeat the steps described in *Setting up Flasher for stand-alone mode* on page 19.

### 2.2.2.1 LED status indicators

Progress and result of an operation is indicated by Flasher's LEDs:

| # | Status of LED                                             | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0 | GREEN high frequency blinking (On/Off time: 50ms => 10Hz) | Flasher ARM is waiting for USB enumeration or ethernet link. As soon as USB has been enumerated or ethernet link has been established, the green LED stops flashing and is switched to constant green. In stand-alone-mode, Flasher remains in the high frequency blinking state until state #1 is reached. Flasher goes to state #1 as soon as a #START command has been received via the ASCII interface or the Start button has been pushed. |  |

| 1 | GREEN constant                                            | Connect to target and perform init sequence.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 2 | GREEN<br>slow blinking                                    | Flashing operation in progress:  1. Erasing (slow blinking on/off time: 80 ms => 6.25 HZ)  2. Programming (slow blinking on/off time: 300ms => ~1.67 Hz)  3. Verifying (slow blinking, on/off time: 100ms => 5 Hz)                                                                                                                                                                                                                              |  |

| 3 | GREEN constant                                            | Operation successful. Goes back to state #0 automatically.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4 | RED constant                                              | Operation failed. Goes back to state #0 automatically but red LED remains on until state #1 (next programming cycle) is entered again.                                                                                                                                                                                                                                                                                                          |  |

Table 2.1: Flasher LEDs

### 2.2.3 **MSD** mode

When pressing the Start/Stop button of Flasher while connecting it to the PC, Flasher will boot in the "MSD mode". This mode can be used to downdate a Flasher firmware version if a firmware update did not work properly and it can be used to configure Flasher for the "stand-alone mode", without using J-Flash.

If Flasher has been configured for "stand-alone mode" as described in the section above, there will be four files on the MSD, FLASHER.CFG, FLASHER.DAT, FLASHER.LOG, SERIAL.TXT.

FLASHER.CFG

FLASHER.DAT

FLASHER.LOG

SERIAL.TXT

FLASHER.CFG contains the configuration settings for programming the target device and FLASHER.DAT contains the data to be programmed. FLASHER.LOG contains all logging information about the commands, performed in stand-alone mode. The SERIAL.TXT contains the serial number, which will be programmed next. J-Flash supports to configure Flasher for automated serial number programming. For further information about how to configure

Currently, J-Flash does not support to configure Flasher for automated serial number programming.

If you want to configure multiple Flasher for the same target you do not have to use J-Flash all the time. It is also possible to copy the FLASHER.CFG and the FLASHER.DAT files from a configured Flasher to another one. To copy these files boot Flasher in "MSD mode".

# 2.3 Multiple File Support

It is also possible to have multiple data files and config files on Flasher, to make Flasher more easy to use in production environment. To choose the correct configuration file and data file pair, a FLASHER.INI file is used. This init file contains a [FILES] section which describes which configuration file and which data file should be used for programming. A sample content of a FLASHER.INI file is shown below:

```

[FILES]

DataFile = "Flasher1.dat"

ConfigFile = "Flasher1.cfg"

```

Using this method all configuration files and data files which are used in the production only have to be downloaded once. From there on a configuration file / data file pair can be switched by simply replacing the FLASHER.INI by a new one, which contains the new descriptions for the configuration file and data file. The FLASHER.INI can be replaced in two ways:

- 1. Boot Flasher in MSD mode in order to replace the FLASHER. INI

- 2. If Flasher is already integrated into the production line, runs in stand-alone mode and can not be booted in other mode: Use the file I/O commands provided by the ASCII interface of Flasher, to replace the FLASHER.INI. For more information about the file I/O commands, please refer to File I/O commands on page 42.

# 2.4 Serial number programming

Flasher supports programming of serial numbers. In order to use the serial number programming feature, the J-Flash project to be used as well as some files on the Flasher (depending on the configuration) need to be configured first.

In general, Flasher supports two ways of programming a serial number into the target:

- 1. Programming continuous serial numbers. Serial number is 1-4 bytes in size. Start serial number, increment, serial number size and address is configured in the J-Flash project.

- Programming custom serial numbers from a serial number list file. Start line into serial number list file to get next serial number bytes, line increment, serial number size and address is configured in J-Flash project. Serial number list file needs to be specified and created by user.

In the following some generic information how to setup Flasher & the J-Flash project for serial number programming are given.

**Note:** Full serial number programming support has been introduced with V4.51d of the J-Flash software and the Flasher firmware that comes with it.

**Note:** Currently, programming of serial numbers is only supported for standalone mode. Future versions of J-Flash may also support serial number programming in J-Link mode.

## 2.4.1 Serial number settings

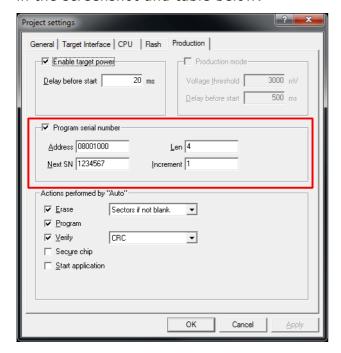

In order to enable the programming of serial numbers in stand-alone mode, the J-Flash project has to be configured to enable programming a serial number at a specific address. This is done by enabling the **Program serial number** option as shown in the screenshot and table below:

| Setting   | Meaning                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address   | The address the serial number should be programmed at.                                                                                                                                                                                                                                                          |

|           | The length of the serial number (in bytes) which should be programmed.                                                                                                                                                                                                                                          |

| Len       | If no serial number list file is given, J-Flash allows to use a 1-4 byte serial number. In case of 8 is selected as length, the serial number and its complementary is programmed at the given address.                                                                                                         |

|           | In case a serial number list file is given, Flasher will take the serial number bytes from the list file. If a serial number in the list file does not define all bytes of Len, the remaining bytes are filled with 0s. No complements etc. are added to the serial number.                                     |

|           | In case no serial number list file is given, Next SN is next serial number which should be programmed. The serial number is always stored in little endian format in the flash memory.                                                                                                                          |

| Next SN   | In case a serial number list file is given, Next SN describes the line of the serial number list file where to read the next serial number bytes from. Flasher starts counting with line 0, so in order to start serial number programming with the first line of the SNList.txt, Next SN needs to be set to 0. |

| Increment | Specifies how much Next SN is incremented.                                                                                                                                                                                                                                                                      |

Table 2.2: Flasher serial number settings

### 2.4.2 Serial number file

When selecting **File -> Download serial number file to Flasher**, J-Flash will create a Serial number file named as <JFlashProjectName>\_Serial.txt. This file is downloaded as SERIAL.TXT on Flasher. The file is generated based on the serial number settings in the J-Flash project and will contain the value defined by the Next SN option. The serial number file can also be manually edited by the user, since the serial number is written ASCII encoded in the SERIAL.TXT file.

### 2.4.3 Serial number list file

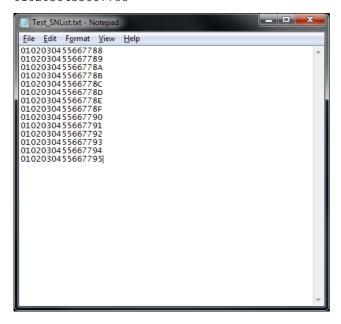

In order to program custom serial numbers which can not be covered by the standard serial number scheme provided by J-Flash (e.g. when programming non-continuous serial numbers or having gaps between the serial numbers), a so called serial number list file needs to be created by the user.

When selecting **File-> Download serial number file to Flasher**, J-Flash will look for a serial number list file named as <JFlashProjectName>\_SNList.txt in the directory where the J-Flash project is located. This file is downloaded as SNList.txt on Flasher. The serial number list file needs to be created manually by the user and has the following syntax:

- One serial number per line

- Each byte of the serial number is described by two hexadecimal digits.

### **Example**

A 8-byte serial number should be programmed at address 0x08000000.

It should be programmed as follows in the memory:

0x08000000: 0x01 0x02 0x03 0x04 0x55 0x66 0x77 0x88

The serial number list file should look as follows:

0102030455667788

The number of bytes to read per line is configured via the Len option in J-Flash. For more information, please refer to *Serial number settings* on page 26.

Which line Flasher will read at the next programming cycle, is configured via the Next SN option in J-Flash. For more information, please refer to Serial number settings on page 26. In this case Next SN needs to be set to 0, since programming should be started with the serial number bytes defined in the first line of the file.

**Note:** If the number of bytes specified in a line of the serial number list file is less than the serial number length defined in the project, the remaining bytes filled with 0s by Flasher.

**Note:** If the number of bytes specified in a line of the serial number list file is greater than the serial number length defined in the J-Flash project, the remaining bytes will be ignored by Flasher.

# 2.4.4 Programming process

Flasher will increment the serial number in SERIAL.TXT by the value defined in Increment, after each successful programming cycle.

For each programming cycle, the FLASHER.LOG on the Flasher is updated and contains the value from SERIAL.TXT that has been used for the programming cycle.

**Note:** The serial number in SERIAL.TXT will also be incremented in case if serial number programming is disabled, to make sure that for the Flasher logfile there is a reference which programming cycle passed and which not. As long as serial number programming has not been enabled in the J-Flash project, Flasher does not merge any serial number data into the image data to be programmed.

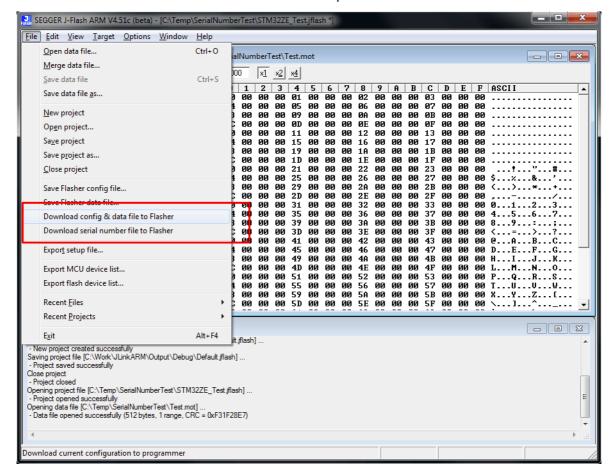

## 2.4.5 Downloading serial number files to Flasher

Downloading the serial number files needs to be done explicitly by selecting File-> Download serial number file to Flasher. Please note that the File -> Download config & data file to Flasher option does only download the configuration and data file to Flasher since usually the current serial number used for programming shall not be reset/overwritten when just updating the image Flasher shall program.

## 2.4.6 Sample setup

In the following a small sample is given how to setup Flasher for serial number programming. In the following sample, 4-byte serial numbers starting at 1234567 (0x12D687) shall be programmed at address 0x08001000.

### Defining serial number address, length and start value

In the J-Flash project the following needs to be defined:

- Address is 0x08001000

- Next SN is 1234567

- Increment is 1

- Len is 4 (bytes)

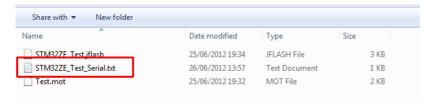

### Downloading configuration, data and serial number to Flasher.

After setting up the rest of the configuration (Target interface etc.) and selecting an appropriate data file, the configuration, data and serial number file is downloaded into Flasher via the File -> Download config & data file to Flasher and File-> Download serial number file to Flasher option.

After downloading the serial number to Flasher, J-Flash also created the <JFlashProjectName>\_Serial.txt.

Now Flasher is prepared to program the 8-byte serial number.

# 2.5 Target interfaces

The table below shows the supported target interfaces of the different Flasher models.

| Hardware    | Supported interfaces |

|-------------|----------------------|

| Flasher ARM | JTAG, SWD            |

| Flasher RX  | JTAG                 |

| Flasher PPC | JTAG                 |

Table 2.3: Supported target interfaces by Flasher

For more information about the target interfaces itself, please refer to:

- UM08001, chapter "Working with J-Link and J-Trace", section "JTAG interface"

- UM08001, chapter "Working with J-Link and J-Trace", section "SWD interface"

# 2.6 Supported microcontrollers

### 2.6.1 Flasher

Flasher supports download into the internal flash of a large number of microcontrollers. The number of supported devices is steadily growing, so you can always find the latest list of supported devices on our website:

http://www.segger.com/supported-devices.html

# 2.7 Support of external flashes

### 2.7.1 Flasher ARM

In general Flasher ARM supports programming of external flashes listed below:

- parallel NOR flash

- serial NOR flash

- NAND flash

- DataFlash

If the parallel NOR flash device which is used is not CFI-compliant you have to select the flash device in J-Flash explicitly, for a list of all parallel NOR flash devices which can be explicitly selected in J-Flash, please refer to *UM08003*, *J-Flash User Guide*, chapter *Supported Flash Devices*. For serial NOR flash, NAND flash and DataFlash devices a custom RAMCode is needed since the connection of the flash to the CPU differs from device to device. The J-Flash software comes with sample projects for custom RAMCodes. For a complete list of all custom RAMCode projects which come with the J-Flash software, please refer to: <a href="http://www.segger.com/supported-devices.html">http://www.segger.com/supported-devices.html</a>

### 2.7.2 Flasher RX

Programming of external parallel NOR flash is currently not supported by Flasher RX. This limitation will be lifted in the near future.

### 2.7.3 Flasher PPC

Programming of external parallel NOR flash is currently not supported by Flasher PPC. This limitation will be lifted in the near future.

# 2.8 Supported cores

### 2.8.1 Flasher ARM

Flasher ARM supports and has been tested with the following cores, but should work with any ARM7/9, Cortex-M0/M1/M3/M4 core. If you experience problems with a particular core, do not hesitate to contact Segger.

- ARM7TDMI (Rev 1)

- ARM7TDMI (Rev 3)

- ARM7TDMI-S (Rev 4)

- ARM920T

- ARM922T

- ARM926EJ-S

- ARM946E-S

- ARM966E-S

- Cortex-M0

- Cortex-M1

- Cortex-M3

- Cortex-M4

### 2.8.2 Flasher RX

Flasher RX supports and has been tested with the following cores. If you experience problems with a particular core, do not hesitate to contact Segger.

- RX610

- RX621

- RX62N

- RX62T

### 2.8.3 Flasher PPC

Flasher PPC supports and has been tested with the following cores. If you experience problems with a particular core, do not hesitate to contact Segger.

e200z0

# **Chapter 3**

# **Remote control**

This chapter describes how to control Flasher via the 9-pin serial interface connector.

### 3.1 Overview

There are 3 ways to control Flasher operation:

- Manual: Programming operation starts when pressing the button. The LEDs serve as visible indication.

- Via Handshake lines: 3 lines on the serial interface are used.

- 1 line is an input and can be used to start operation,

- 2 lines are outputs and serve as Busy and status output

- Terminal communication via RS232.

**Note:** All three ways to control Flasher operation are working only if Flasher is in standalone mode. In J-Link / MSD mode they have no effect.

# 3.2 Handshake control

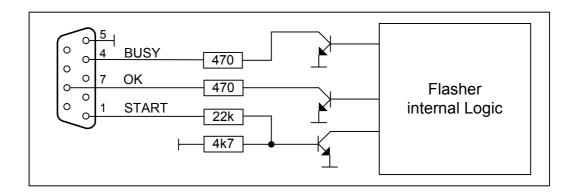

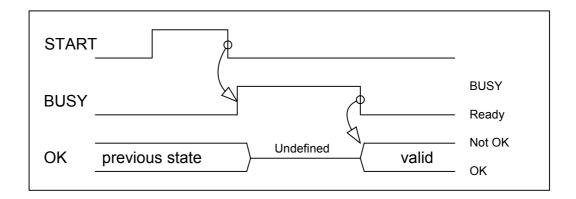

Flasher can be remote controlled by automated testers without the need of a connection to PC and Flasher's PC program. Therefore Flasher is equipped with additional hardware control functions, which are connected to the SUBD9 male connector, normally used as RS232 interface to PC.

The following diagrams show the internal remote control circuitry of Flasher:

| Pin No. | Function | Description                                                                                                                                                                                                                                                                    |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | START    | A positive pulse of any voltage between 5 and 30V with duration of min. 30 ms starts "Auto" function (Clear / Program / Verify) on falling edge of pulse. The behavior of the "Auto" function depends on the project settings, chosen in J-Flash at the <b>Production</b> tab. |

| 4       | BUSY     | As soon as the "Auto" function is started, BUSY becomes active, which means that transistor is switched OFF.                                                                                                                                                                   |

| 5       | GND      | Common Signal ground.                                                                                                                                                                                                                                                          |

| 7       | ОК       | This output reflects result of last action. It is valid after BUSY turned back to passive state. The output transistor is switched ON to reflect OK state.                                                                                                                     |

Table 3.1: Flasher LED status

# 3.3 ASCII command interface

# 3.3.1 Introduction

Once set up using J-Flash, Flasher can be driven by any application or just a simple terminal using ASCII commands.

Every known command is acknowledged by Flasher and then executed. After command execution, Flasher sends an ASCII reply message.

**Note:** Note: There are situations where the execution of a known command is rejected with #NACK:ERRxxx if Flasher is currently busy and the received command is not allowed to be sent while Flasher is busy

# 3.3.2 General command and reply message format

- Any ASCII command has to start with the start delimiter #.

- Any ASCII command has to end with simple carriage return ('\r', ASCII code 13).

- Commands can be sent upper or lower case.

# 3.3.3 Settings for ASCII interface via RS232

Flasher is driven via a RS232 serial port with the following interface settings:

- 8 data bits,

- no parity

- 1 stop bit

at 9600 baud.

# 3.3.4 Settings for ASCII interface via Telnet

A client application can connect to Flasher via Telnet on port 23. Find below a screenshot of Flasher which is remot controlled via Telnet:

```

Telnet 192.168.11.41

J-Link ARM / Flasher ARM U3 telnet-shell.

J-Link ARM / Flasher ARM U3 compiled Jan 29 2013 17:58:39

> Hauto

HACK

#STATUS: INITIALIZING

#STATUS: CONNECTING

#STATUS: UNLOCKING

#STATUS: UNLOCKING

#STATUS: PROGRAMMING

#STATUS: PROGRAMMING

#STATUS: UERIPYING

#OK (Total 7.797s, Erase 0.004s, Prog 3.949s, Verify 0.087s)

-

```

# 3.3.5 Commands to Flasher

The table below gives a overview about the commands which are supported by the current version of Flasher firmware. Click on the names for a detailed descripion:

| Commands                                                      |

|---------------------------------------------------------------|

| #AUTO                                                         |

| #AUTO NOINFO                                                  |