# **TOSHIBA**

TOSHIBA Original CMOS 32-Bit Microcontroller

TLCS-900/H1 Series

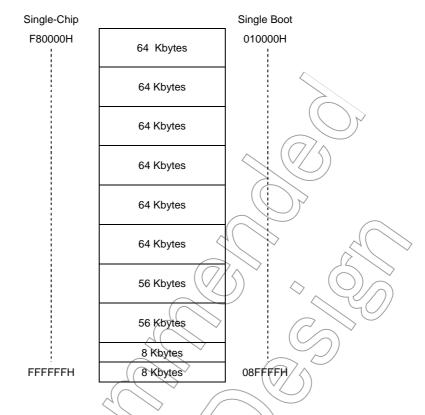

TMP92FD54AIFG

**Tentative**

# **TOSHIBA CORPORATION**

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions".

#### CMOS 32-bit Micro-controller

# TMP92FD54AIFG

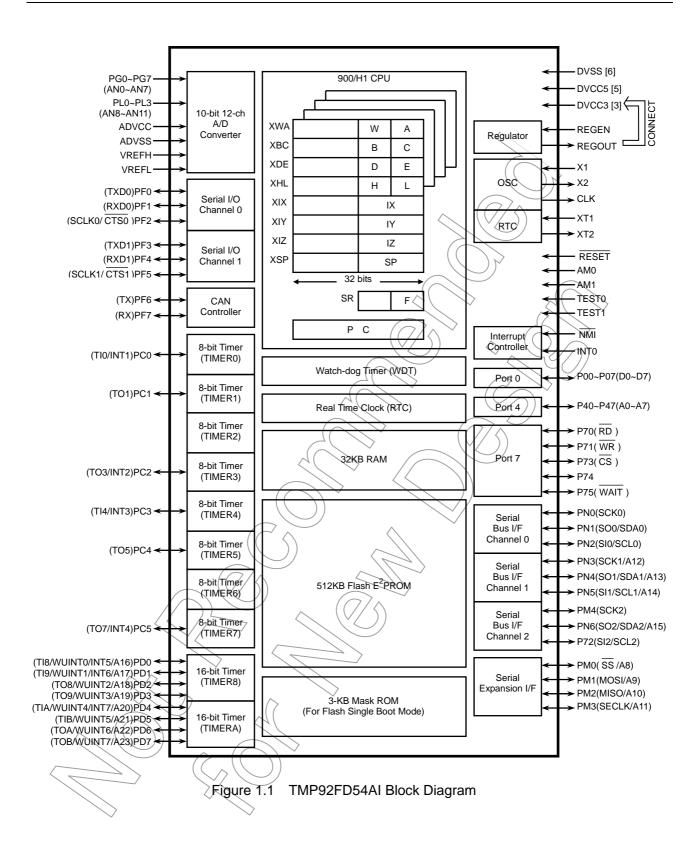

#### 1. Device Outline and Characteristics

The TMP92FD54AI is a high-performance 32-bit microcontroller incorporating a Toshiba-proprietary CPU, the TLCS-900/H1 core. The TMP92FD54AI is developed for various automotive equipments which require high-speed data processing.

Housed in a 100-pin mini-flat package, the TMP92FD54AI is best suited for high-density implementation of user systems.

The characteristics of the TMP92FD54AI are listed below:

(1) Toshiba-proprietary high-speed 32-bit CPU (TLCS-900/H1 CPU)

Fully-compatible with the instruction codes of the TLCS-900, TLCS-900/L, ELCS-900/L1,

TLCS-900/H and TLCS-900/H2

16 Mbytes of linear address space

General-purpose registers and register banks

Micro DMA: 8 channels (250 ns/4 bytes at fc = 20 MHz)

Minimum instruction execution time: 50 ns (at fc = 20 MHz)

Internal data bus: 32-bit wide

(2) Internal memory

Internal RAM : 32 Kbytes

Internal ROM : 512-Kbyte flash EEPROM

3-Kbyte masked ROM (for Single Boot mode)

(3) External memory expansion

Expandable up to 16-Mbyte (for code and data)

External data bus: 8-bit wide (The upper address bus is not available when the built-in

I/Os are selected.)

(4) Memory controller (MEMC)

Chip select output; 1 channel

(5) 8-bit timer: 8 channels

8-bit interval timer mode (8 channels)

16-bit interval timer mode (4 channels)

8-bit programmable pulse generation (PPG) output mode (4 channels)

8-bit pulse width modulation (PWM) output mode (4 channels)

(6) 16-bit timer: 2 channels

16-bit interval timer mode (2 channels)

16-bit event counter mode (2 channels)

16-bit programmable pulse generation (PPG) output mode (2 channels)

Frequency measurement mode

Pulse width measurement mode

Time difference measurement mode

(7) General-purpose serial interface (SIO): 2 channels

I/O interface mode

Universal asynchronous receiver transmitter (UART) mode

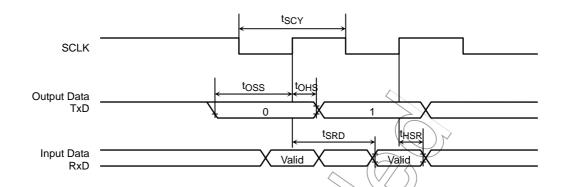

- (8) Serial expansion interface (SEI): 1 channel

- (9) Baud rate: 4 M/2 M/500 K bps at fc = 20 MHz

92FD54AI-1 2009-12-26

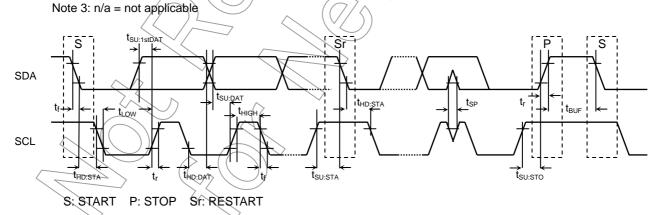

(10) Serial bus interface (SBI): 3 channels

Clock-synchronous 8-bit serial interface mode

I2C bus mode

(11) CAN controller: 1 channel

Supports CAN version 2.0B.

16 mailboxes

(12) 10-bit A/D converter (ADC): 12 channels

A/D conversion time:  $8 \mu sec$  (at fc = 20 MHz)

Total tolerance: ± 3 LSB (excluding quantization error)

Scan mode for all 12 channels

- (13) Watch dog timer (WDT)

- (14) Timer for real-time clock (RTC)

Can operate with low-frequency oscillator only.

(15) Interrupt controller (INTC): 60 interrupt sources

9 interrupts from CPU (Software interrupts and undefined instruction interrupt)

42 internal interrupt vectors

9 external interrupt vectors (INT0 to INT7, NMI)

- (16) I/O Port: 68 pins (including multi-function pins)

- (17) Standby mode

Four modes: IDLE3, IDLE2, IDLE1 and STOP

STOP mode can be released by 9 external inputs.

- (17) Internal voltage detection flag (RAMSTB)

- (18) Power supply voltage

$V_{CC5} = 4.5 \text{ V to } 5.25 \text{ V}$

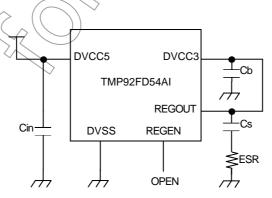

V<sub>CC3</sub> = 3.3 V (Connect REGOUT (built-in voltage regulator output) to DVCC3.)

(19) Operating temperature: -40 to 85 degree C (0 to 70 degree C when the flash memory is being rewritten.)

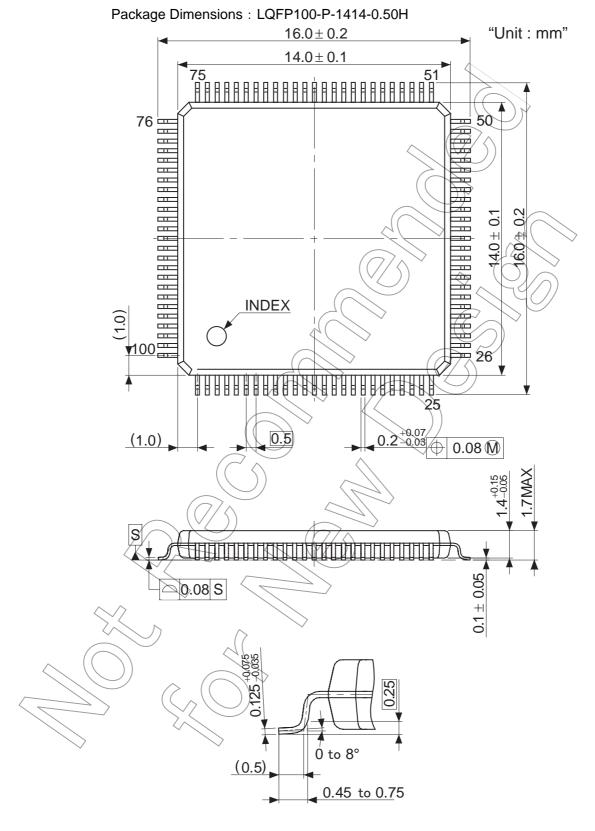

(20) Package: LQFP100-P-1414-0.50H

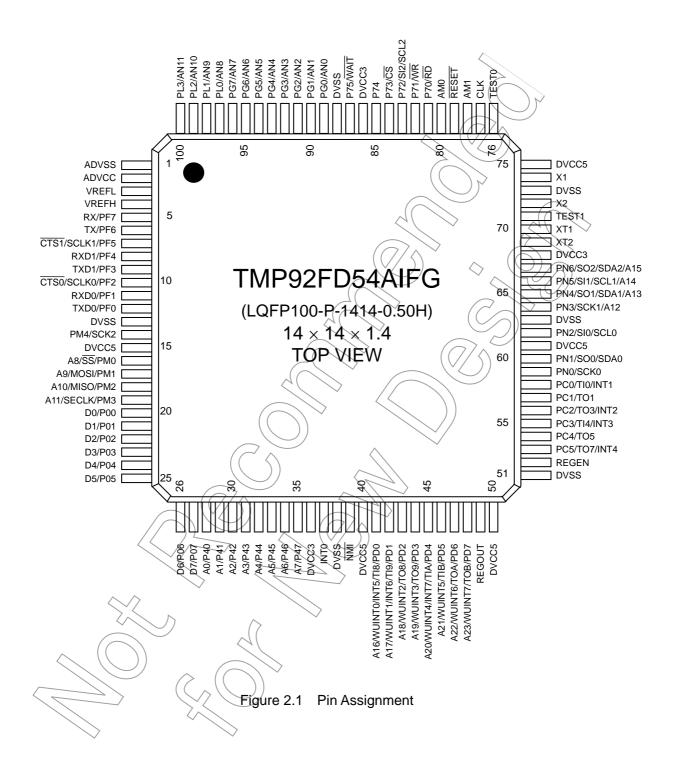

# 2. Pin Assignment and Functions

## 2.1 Pin Assignment

# 2.2 Pin Names and Functions

The names and functions of the input/output pins are described in Tables 2.2.1 to 2.2.4.

Table 2.2.1 Input/output pins (1/4)

| Pin name               | Pin<br>number | Number of pins    | In/Out              | Function                                                                                                                 |  |

|------------------------|---------------|-------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| P00 to P07<br>D0 to D7 | 20 to 27      | 8 (CMOS)<br>(TTL) | in/out<br>in/out    | Port 0: I/O port. Input or output specifiable in units of bits.  Data: Data bus 0 to 7.                                  |  |

| P40 to P47<br>A0 to A7 | 28 to 35      | 8                 | in/out<br>out       | Port4: I/O port. Input or output specifiable in units of bits. Address: Address bus 0 to 7.                              |  |

| P70<br>RD              | 81            | 1                 | in/out<br>out       | Port70: I/O port.  Read: Outputs strobe signal to read external memory.                                                  |  |

| P71<br>WR              | 82            | 1                 | in/out<br>out       | Port 71: I/O port. Write: Output strobe signal to write external memory.                                                 |  |

| P72<br>SI2<br>SCL2     | 83            | 1                 | in/out              | Port 72: I/O port.  SBI channel 2: Input data at SIO mode  SBI channel 2: Clock input/output at I/2C mode                |  |

| P73<br>CS              | 84            | 1                 | in/out<br>out       | Port 73: I/O port. Chip select: Outputs "low" if address is within specified address area.                               |  |

| P74                    | 85            | 1                 | in/out              | Port 74: I/O port.                                                                                                       |  |

| P75<br>WAIT            | 87            | 1                 | in/out<br>in        | Port 75: I/O port. Wait: Signal used to request CPU bus wait.                                                            |  |

| PC0<br>TI0<br>INT1     | 58            | 1                 | in/out<br>in<br>in  | Port C0: I/O port.  Timer input 0: Input pin for timer 0.  Interrupt request pin 1: Rising-edge interrupt request pin.   |  |

| PC1<br>TO1             | 57            | 1                 | in/out<br>out       | Port C1: I/O port.  Timer output 1: Output pin for timer 1.                                                              |  |

| PC2<br>TO3<br>INT2     | 56            | 1                 | in/out<br>out<br>in | Port C2: I/O port.  Timer output 3: Output pin for timer 3.  Interrupt request pin 2: Rising-edge interrupt request pin. |  |

| PC3<br>TI4<br>INT3     | 55            | 1                 | in/out<br>in<br>in  | Port C3: 1/O port.  Timer input 4: Input pin for timer 4.  Interrupt request pin 3: Rising-edge interrupt request pin.   |  |

| PC4<br>TO5             | 54            | 1                 | in/out<br>out       | Port C4: I/O port. Timer output 5: Output pin for timer 5.                                                               |  |

| PC5<br>TO7<br>INT4     | 53            | 1                 | in/out<br>out<br>in | Port C5: I/O port.  Timer output 7: Output pin for timer 7.  Interrupt request pin 4: Rising-edge interrupt request pin. |  |

| PD0<br>TI8<br>INT5     | ^ /           |                   | in/out<br>in<br>in  | Port D0: I/O port.  Timer input 8: Input pin for timer 8.  Interrupt request pin 5: Interrupt request pin with           |  |

| A16<br>WUINT0          | 41            | 1                 | out<br>in           | programmable rising/falling edge.  Address: Address bus 16.  Wake up input 0: Wake up request pin with                   |  |

|                        |               |                   |                     | programmable rising, falling or both falling and rising edge.                                                            |  |

| PD1<br>TI9             |               |                   | in/out<br>in        | Port D1, I/O port.  Timer input 9: Input pin for timer 9.                                                                |  |

| INT6                   | 42            | 1                 | in/                 | Interrupt request pin 6: Rising-edge interrupt request pin.                                                              |  |

| A17<br>WUINT1          |               | 4                 | out                 | Address: Address bus 17.  Wake up input 1: Wake up request pin with                                                      |  |

| DD2                    |               |                   | in/out              | programmable rising, falling or both falling and rising edge.                                                            |  |

| PD2<br>TO8             |               |                   | in/out<br>out       | Port D2: I/O port. Timer output 8: Output pin for timer 8                                                                |  |

| A18                    | 43            | 1                 | out                 | Address: Address bus 18. WUINT2 — — — —                                                                                  |  |

| WUINT2                 |               |                   | in                  | Wake up input 2: Wake up request pin with programmable rising, falling or both falling and rising edge.                  |  |

Table 2.2.2 Input/output pins (2/4)

| Pin name                            | Pin<br>number | Number of pins | In/Out                          | Function                                                                                                                                                                                                                                                                           |

|-------------------------------------|---------------|----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD3<br>TO9<br>A19<br>WUINT3         | 44            | 1              | in/out<br>out<br>out<br>in      | Port D3: I/O port.  Timer output 9: Output pin for timer 9  Address: Address bus 19.  Wake up input 3: Wake up request pin with programmable rising, falling or both falling and rising edge.                                                                                      |

| PD4<br>TIA<br>INT7<br>A20<br>WUINT4 | 45            | 1              | in/out<br>in<br>in<br>out<br>in | Port D4: I/O port.  Timer input A: Input pin for timer A  Interrupt request pin 7: Interrupt request pin with programmable rising/falling edge.  Address: Address bus 20.  Wake up input 4: Wake up request pin with programmable rising, falling or both falling and rising edge. |

| PD5<br>TIB<br>A21<br>WUINT5         | 46            | 1              | in/out<br>in<br>out<br>in       | Port D5: I/O port.  Timer input B: Input pin for timer B.  Address: Address bus 21.  Wake up input 5: Wake up request pin with programmable rising, falling or both falling and rising edge.                                                                                       |

| PD6<br>TOA<br>A22<br>WUINT6         | 47            | 1              | in/out<br>out<br>out<br>in      | Port D6: I/O port.  Timer output A: Output pin for timer A.  Address: Address bus 22:  Wake up input 6: Wake up request pin with programmable rising, falling or both falling and rising edge.                                                                                     |

| PD7<br>TOB<br>A23<br>WUINT7         | 48            | 1              | in/out<br>out<br>out<br>in      | Port D7: I/O port.  Timer output B: Output pin for timer B.  Address: Address bus 23:  Wake up input 7: Wake up request pin with programmable rising, falling or both falling and rising edge.                                                                                     |

| PF0<br>TXD0                         | 12            | 1              | in/out<br>out                   | Port F0: I/O port. Serial interface channel 0: Transmission data.                                                                                                                                                                                                                  |

| PF1<br>RXD0                         | 11            | 1              | in/out<br>in                    | Port F1: I/O port.<br>Serial interface channel 0: Receive data.                                                                                                                                                                                                                    |

| PF2<br>SCLK0<br>CTS0                | 10            | 1              | in/out<br>in/out<br>in          | Port F2; I/O port. Serial interface channel 0: Clock input/output. Serial interface channel 0: Data ready to send. (Clear-to-send)                                                                                                                                                 |

| PF3<br>TXD1                         | 9             | 1              | in/out<br>out                   | Port F3: I/O port. Serial interface channel 1: Transmission data.                                                                                                                                                                                                                  |

| PF4<br>RXD1                         | 8             | 4              | in/out<br>in                    | Port F4: (70 port. Serial interface channel 1: Receive data.                                                                                                                                                                                                                       |

| PF5<br>SCLK1<br>CTS1                | 7             | 1              | in/out<br>in/out<br>in          | Port F5: 1/O port. Serial interface channel 1: Clock input/output. Serial interface channel 1: Data ready to send. (Clear-to-send)                                                                                                                                                 |

| PF6<br>TX                           | 6             |                | in/out<br>out                   | Port F6: I/O port.<br>CAN: Transmission data.                                                                                                                                                                                                                                      |

| PF7<br>RX                           | 5             | )1)            | in/out<br>in                    | Rort F7: I/O port. CAN: Receive data.                                                                                                                                                                                                                                              |

| PG0 to PG7<br>AN0 to AN7            | 89 to 96      | 8 ((           | in in                           | Port G: Input-only port.  Analog input 0 to 7: AD converter input pins.                                                                                                                                                                                                            |

| PL0 to PL3<br>AN8 to AN11           | 97 to 100     | 4              | in                              | Port L0 to L3: Input-only port. Analog input 8 to 11: AD converter input pins.                                                                                                                                                                                                     |

| PM0<br>SS<br>A8                     | 16            | 1              | in/out<br>in<br>out             | Port M0: I/O port. SEI: Slave select input. Address: Address bus 8.                                                                                                                                                                                                                |

| PM1<br>MOSI                         | 17            | 1              | in/out<br>in/out                | Port M1: I/O port. SEI: Master output, slave input.                                                                                                                                                                                                                                |

| A8<br>PM1                           |               |                | out<br>in/out                   | Address: Address bus 8.  Port M1: I/O port.                                                                                                                                                                                                                                        |

Table 2.2.3 Input/output pins (3/4)

| Pin name | Pin<br>number | Number of pins | In/Out                                                                                         | Function                                                                                                             |

|----------|---------------|----------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| PM2      |               |                | in/out                                                                                         | Port M2: I/O port.                                                                                                   |

| MISO     | 18            | 1              | in/out                                                                                         | SEI: Master input, slave output.                                                                                     |

| A10      |               |                | out                                                                                            | Address: Address bus 10.                                                                                             |

| PM3      |               |                | in/out                                                                                         | Port M3: I/O port.                                                                                                   |

| SECLK    | 19            | 1              | in/out                                                                                         | SEI: Clock input/output.                                                                                             |

| A11      |               |                | out                                                                                            | Address: Address bus 11.                                                                                             |

| PM4      | 4.4           |                | in/out                                                                                         | Port M4: I/O port.                                                                                                   |

| SCK2     | 14            | 1              | in/out                                                                                         | SBI channel 2: Clock input/output at SIO mode.                                                                       |

| PN0      | 50            | _              | in/out                                                                                         | Port N0: I/O port.                                                                                                   |

| SCK0     | 59            | 1              | in/out                                                                                         | SBI channel 0: Clock input/output at SIO mode.                                                                       |

| PN1      |               |                | in/out                                                                                         | Port N1: I/O port.                                                                                                   |

| SO0      | 60            | 1              | out                                                                                            | SBI channel 0: Output data input/output at SIO mode                                                                  |

| SDA0     |               |                | in/out                                                                                         | SBI channel 0: Data input/output at IPC mode                                                                         |

| PN2      |               |                | in/out                                                                                         | Port N2: I/O port.                                                                                                   |

| SI0      | 62            | 1              | in                                                                                             | SBI channel 0: Input data at SIO mode                                                                                |

| SCL0     |               |                | in/out                                                                                         | SBI channel 0: Clock input/output at 12 C mode                                                                       |

| PN3      |               |                | in/out                                                                                         | Port N3: I/O port.                                                                                                   |

| SCK1     | 64            | 1              | in/out                                                                                         | SBI channel 1: Clock input/output at SIO mode                                                                        |

| A12      |               |                | out                                                                                            | Address: Address bus 12.                                                                                             |

| PN4      |               |                | in/out                                                                                         | Port N4: I/O port.                                                                                                   |

| SO1      | 0.5           |                | out                                                                                            | SBI channel 1; Output data at SIO mode                                                                               |

| SDA1     | 65            | 1              | in/out                                                                                         | SBI channel 1: Data input/output at I <sup>2</sup> C mode                                                            |

| A13      |               |                | out                                                                                            | Address: Address bus 13.                                                                                             |

| PN5      |               |                | in/out                                                                                         | Port N5: WO port.                                                                                                    |

| SI1      | 00            | _              | in                                                                                             | SBI channel 1: Input data at SIO mode                                                                                |

| SCL1     | 66            | 1              | in/out                                                                                         | SBI channel 1: Clock input/output at I <sup>2</sup> C mode                                                           |

| A14      |               |                | out                                                                                            | Address: Address bus 14                                                                                              |

| PN6      |               |                |                                                                                                | Port N6: I/O port.                                                                                                   |

| SO2      | 67            | 4              | in/out \                                                                                       | SBI channel 2: Output data at SIO mode                                                                               |

| SDA2     | 67            | 1              | out                                                                                            | SBL channel 2: data input output at I2C mode                                                                         |

| A15      |               |                | (7/                                                                                            | Address: Address bus 15.                                                                                             |

| NMI      | 39            | 1/             | \in\v                                                                                          | Non-maskable interrupt: Interrupt request pin with min — — —                                                         |

| INIVII   | 39            | // )           | in                                                                                             | programmable falling or both falling and rising edge.                                                                |

| INT0     | 37            | 1              |                                                                                                | Interrupt request pin 0: Interrupt request pin with INTO                                                             |

| INTO     | 31            | '              | in                                                                                             | programmable level or rising-edge.                                                                                   |

| ΛMO 1    | 90 70         | 2              | 3: </td <td>Address Mode selection: Connect AM0 pin to L and AM1 pin to H for Single Chip</td> | Address Mode selection: Connect AM0 pin to L and AM1 pin to H for Single Chip                                        |

| AM0,1    | 80, 78        | >2             | in                                                                                             | mode; Connect AM0 and AM1 pins to H for Single Boot mode.                                                            |

| TEST0,1  | 76, 71        | 2              | in                                                                                             | Test mode pins: Should be tied to GND.                                                                               |

| CLK      | 77            | 1              | out                                                                                            | Programmable clock output (with pull-up resistor)                                                                    |

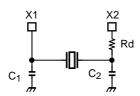

| X1/X2    | 74, 72        | 2              | in/out                                                                                         | High-trequency oscillator connecting pins: To drive these pins with an external clock, apply clock signals of 3.3 V. |

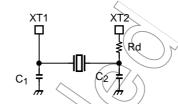

| XT1/XT2  | 70, 69        | 2              | in/out                                                                                         | Low-frequency oscillator connecting pins: To drive these pins with an external clock,                                |

|          |               | 2              | intout                                                                                         | apply clock signals of 3.3 V.                                                                                        |

| RESET    | 79>           | 1              | in \                                                                                           | Reset: Initializes LSI (with pull-up resistor).                                                                      |

| VREFH    | 4             | 1              | in                                                                                             | AD reference voltage high                                                                                            |

| VREFL    | 3             | 1              | in                                                                                             | AD reference voltage low                                                                                             |

| ADVCC    | 2             | 1              | -                                                                                              | Power supply pin for AD converter (+5V): Connect the ADVCC pin to 5-V power supply                                   |

| ADVSS    | 1             | 1              | -                                                                                              | GND pin for AD converter: Connect the ADVSS pin to GND (0V).                                                         |

Table 2.2.4 Input/output pins (4/4)

| Pin name | Pin<br>number                | Number of pins | In/Out | Function                                                                    |

|----------|------------------------------|----------------|--------|-----------------------------------------------------------------------------|

| DVCC5    | 15, 40,<br>50, 61, 75        | 5              | -      | Power supply pins (+5V): Connect all the DVCC5 pins to 5-V power supply.    |

| DVCC3    | 36, 68, 86                   | 3              | -      | Power supply pins (+3.3V): Connect all the DVCC3 pins to REGOUT pin.        |

| DVSS     | 13, 38,<br>51,<br>63, 73, 88 | 6              | -      | GND: Connect all DVSS pins to GND (0V).                                     |

| REGOUT   | 49                           | 1              | out    | Regulator output 3.3V: Connect capacitor to stabilize the regulator output. |

| REGEN    | 52                           | 1              | in     | Regulator enable pin: Should be set to H or OREN (with pull-up resistor).   |

# 3. Functional Description of Flash Memory

This chapter describes the structure and operations of the internal flash memory.

The TMP92FD54AI is a microcontroller incorporating a flash memory that is an alternative of the TMP92CD54I's internal ROM. The structural details and functions that are identical with those of the TMP92CD54I are not mentioned in this document. For those details, please refer to the TMP92CD54I datasheet.

## 3.1 Flash Memory

#### 3.1.1 Features

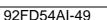

1) Memory Capacity

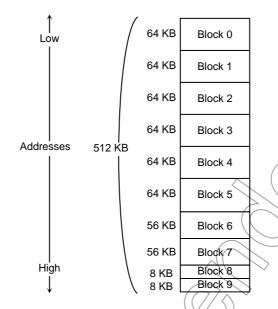

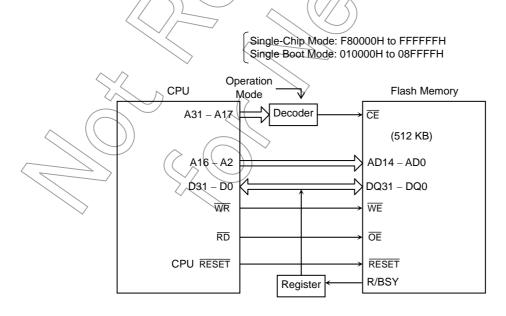

The TMP92FD54AI has a 4-Mbit (512-Kbyte) flash memory, which is divided into a total of ten blocks (64 Kbytes × 6 blocks, 56 Kbytes × 2 blocks, 8 Kbytes × 2 blocks) to allow for independent protection from program and erase for each block. When the CPU attempts to access the internal flash memory, it uses the 32-bit data bus.

2) Flash Memory Access Interleaved access (2-1-1-1 clock access)

3) Program/Erase Time

Chip programming time: 6 seconds (typ.), including program verify operations [30 µs / long word (typ.)]

Chip erase time: 12 seconds (typ.), including program verify operations

Note: These program and erase times are typical values and do not include data transfer overhead. The actual chip program and erase times depend on the programming method used.

4) Programming Procedures

The device has two on board programming modes: User Boot mode and Single Boot mode. These modes allow a flash memory to be programmed and erased via a serial communication.

• On-Board Programming Modes

1) User Boot mode (Single-Chip mode)

Supports use of a user-written programming algorithm.

2) Single Boot mode

Downloads new program code using a Toshiba-defined serial interface protocol. User-written programming algorithm is used as the subsequent reprogramming method.

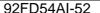

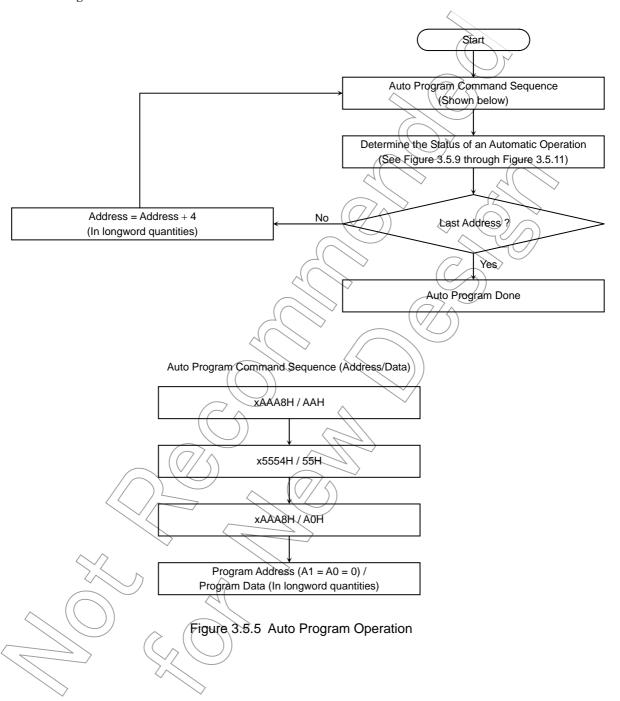

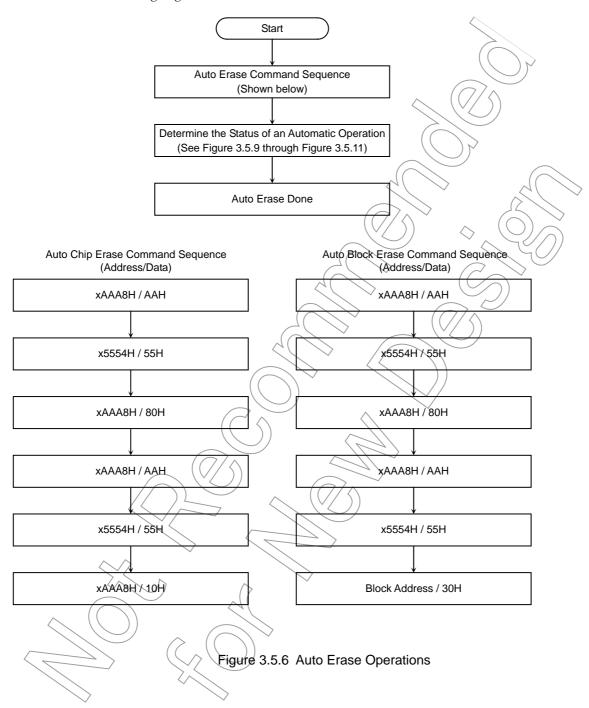

5) Program/Erase Sequence

The flash memory contained in the TMP92FD54AI is compatible with the JEDEC standards, except a few unique functions. Thus, it is easy to change from a discrete flash memory device to the TMP92FD54AI on-chip flash memory. The TMP92FD54AI contains circuitry to perform programming and erase operations automatically. This eliminates the need for the user to code complex program and erase sequences.

The TMP92FD54AI allows the user to protect individual blocks of the flash memory against program or erase through software commands; however, does not supported hardware data protection (12-V VPP).

For more details, please refer to Section 3.5, Flash Memory Program/Erase in On-Board Programming Modes.

Table 3.1.1 Functional Differences from the JEDEC Standards

| JEDEC Standards | Changes and Enhancements                                                                                               |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

| Auto Chip Frase | Changed feature: Block protection is available only under software control. Removed feature: Erase Resume/Suspend mode |

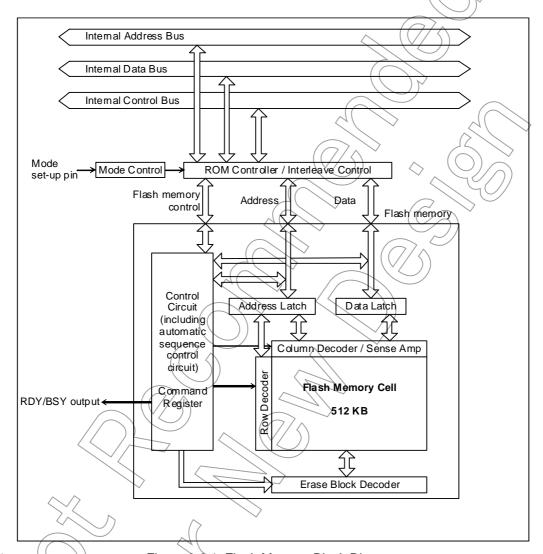

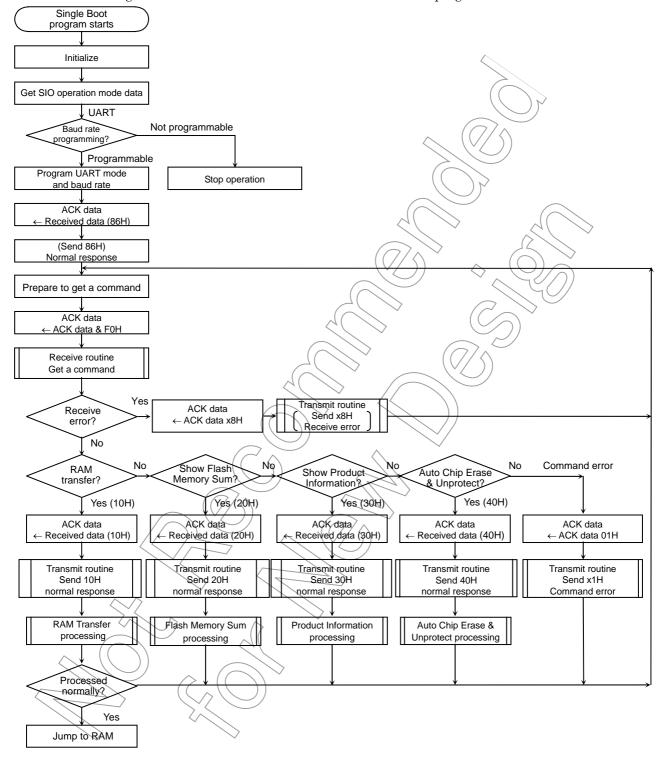

# 3.2 Block Diagram

Figure 3.2.1 Flash Memory Block Diagram

# 3.3 Operating Modes

#### 3.3.1 Overview

The TMP92FD54AI provides two operating modes.

Table 3.3.1 Operating Modes

| Operating Mode   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Chip Mode | After a reset, the TMP92FD54AI executes out of on-chip flash memory.  Single-Chip mode is further divided into Normal mode in which the user application executes and User Boot mode which allows for reprogramming of the flash memory while the TMP92FD54AI is installed on a PC board.  The means for selecting between these two modes can be set by the user as desired.  For example, the logic state on Port 00 can be used to determine whether to put the flash memory in Normal mode (when Port 00 = 1) or User Boot mode (when Port 00 = 0).  The user must include a routine in the application program to handle mode switching. |

| Normal Mode      | In this mode, the user application program in the flash memory is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| User Boot Mode   | This mode is used to rewrite the flash memory while it is installed on a PC board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Single Boot Mode | After a reset, the TMP92FD54Al executes out of the on-chip boot ROM (which is a mask ROM). The boot ROM contains an algorithm that allows users to transfer the routine for performing on board programming of the flash memory via a serial port of the TMP92FD54Al to the on-chip RAM. For program/erase operations, the CPU core can issue a command sequence to the flash memory by executing the program/erase routine in the RAM while data from an external host is being received.                                                                                                                                                    |

The on-chip flash memory can be reprogrammed in one of the following two modes: User Boot mode in Single-Chip mode and Single Boot mode. These two modes that allow the user to program and erase the flash memory in user applications are collectively referred to as on-board programming modes.

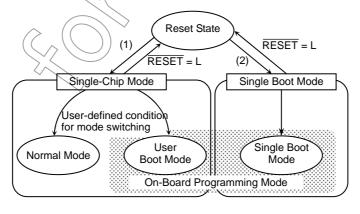

The operating modes for the flash memory, Single-Chip or Single Boot mode, is determined by the logic-states on the AMO, AM1, TESTO and TEST1 pins during a reset sequence.

The CPU starts operations in each operation mode when the Reset state is released after a level input. Do not change a mode state while the CPU is running.

The operating modes and settings, and the mode transitions are shown below.

Table 3.3.2 Operating Modes

|     | Operating Mode                          | Input Pins |     |     |       |       |  |

|-----|-----------------------------------------|------------|-----|-----|-------|-------|--|

|     | Sperating meas                          | RESET      | AM1 | AM0 | TEST1 | TEST0 |  |

| (1) | Single-Chip Mode (Normal and User Boot) | 1          | 1   | 0   | 0     | 0     |  |

| (2) | Single Boot Mode                        | /          | 1   | 1   | 0     | 0     |  |

Parenthesized numbers, (1) and (2), indicate that the relevant pins are at the logic states shown in Table 3.3.2.

Figure 3.3.1 Mode Transitions

#### 3.3.2 Reset Operation

To reset the TMP92FD54AI,  $\overline{RESET}$  must be asserted for at least 4  $\mu s$  (at fosc=10 MHz) after the internal oscillator and clock multiplier have stabilized while the supply voltage is kept within the normal operating range.

Since the clock multiplier is bypassed during reset, the system clock frequency (fc) is set to 5 MHz (when  $f_{OSC} = 10$  MHz).

For more details, refer to the TMP92CD54I datasheet, Section 3.1.2, Reset Operation.

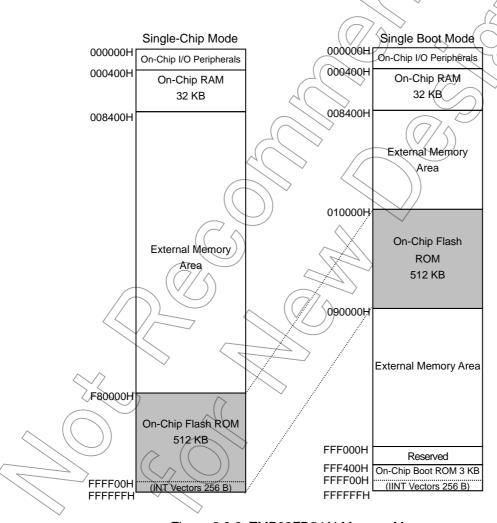

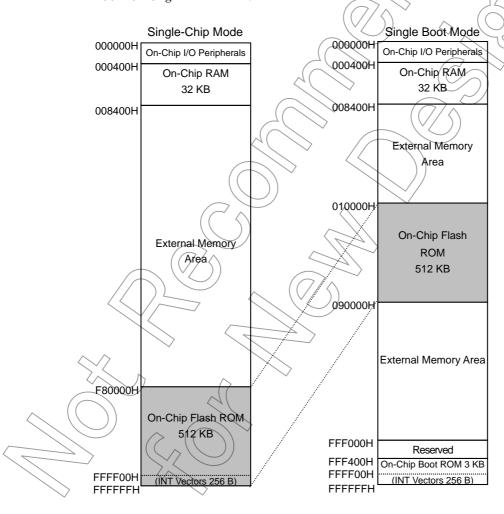

#### 3.3.3 Memory Maps in Each Operating Mode

The memory map for the TMP92FD54AI varies according to the operation mode. The memory maps, flash memory block architecture and block addresses for each operation mode are shown below.

Figure 3.3.2 TMP92FD54AI Memory Maps

Figure 3.3.3 Flash Memory Block Architecture

Table 3.3.3 Block Addresses

| В       | lock    | Single-Chip Mode    | Single Boot Mode  |

|---------|---------|---------------------|-------------------|

| Block 0 | (64 KB) | F80000H - F8FFFFH   | 010000H V01FFFFH  |

| Block 1 | (64 KB) | F90000H - F9FFFFH   | 020000H - 02EFFFH |

| Block 2 | (64 KB) | FA0000H - FAFFFFH / | 030000H - 03FFFFH |

| Block 3 | (64 KB) | FB0000H - FBFFFFH   | 040000H - 04FFFFH |

| Block 4 | (64 KB) | FC0000H - FCFFFFH   | 050000H - 05FFFFH |

| Block 5 | (64 KB) | FD0000H - FDFFFFH   | 060000H - 06FFFFH |

| Block 6 | (56 KB) | FE0000H - FEDFFFH   | 070000H - 07DFFFH |

| Block 7 | (56 KB) | FEE000H - FFBFFFH   | 07E000H - 08BFFFH |

| Block 8 | (8 KB)  | FFC000H - FFDEFFH   | 08C000H - 08DFFFH |

| Block 9 | ( 8 KB) | FFE000H - FFFFFFH   | 08E000H - 08FFFFH |

## 3.4 On-Board Programming Modes (User Boot and Single Boot Modes)

On-board programming modes allow for reprogramming of the flash memory while the TMP92FD54AI is soldered on a PC board that enables data communications with external devices.

The on-board programming modes include the following:

· User Boot Mode (Supports use of a user-written programming algorithm.)

This mode allows flash memory reprogramming by executing a user-written algorithm that is preprogrammed in the flash memory for program and erase operations. This reprogramming operation is initiated by user-defined trigger events.

· Single Boot Mode (Supports use of a Toshiba-defined boot program.)

In this mode, a user-written reprogramming routine is downloaded into the on-chip RAM via a Toshiba-specified communication pin. The boot program offers operation commands, such as RAM Transfer and Erase.

#### 3.4.1 User Boot Mode (in Single-Chip Mode)

User Boot mode allows for flash memory reprogramming by using a user-created reprogramming routine for flash memory. This mode supports situations where the reprogramming routine that is incorporated in the user application code should be used, and where the data transfer should be performed in mode other than UART mode.

This programming algorithm is executed in Single-Chip mode. To reprogram the flash memory, the mode of operation must be switched from Normal mode, in which user application programs usually run, to User Boot mode.

For example, to let the operation mode to be determined on startup, the user application code must include a mode judgment routine as part of the reset procedure so that the operating mode smoothly changes to User Boot mode.

The user must define the conditions for mode switching, based on the logic states on I/O ports of the TMF92FD54AI. Additionally, the user must incorporate a flash memory programming algorithm into the user application code that is to be executed after User Boot mode is entered.

It is impossible to read from the flash memory while it is being erased or programmed; therefore, the programming algorithm must be placed and executed in memory areas that are outside the flash memory, such as on-chip RAM.

Once reprogramming is complete, it is recommended to protect relevant flash blocks from accidental corruption during subsequent Normal mode operations.

All interrupts including the nonmaskable interrupt must be globally disabled while the flash memory is being erased or programmed in this mode. When using SIO channels, software can check interrupt request flags in interrupt priority level registers, such as INTES1<ITX1C, IRX1C>, to determine whether reception/transmission has come to an end.

The following sections describe the general procedures for two cases where the programming routine is: 1-A) stored within the TMP92FD54AI flash memory, and 1-B) loaded from an external controller. For a detailed descriptions of the erase and program sequence, refer to Section 3.5, On-Board Programming and Erasure.

#### 3.4.1.1 (1-A) Program/Erase Procedure 1

This procedure is used when the boot program for flash memory programming and erasure is previously included in the on-chip flash memory.

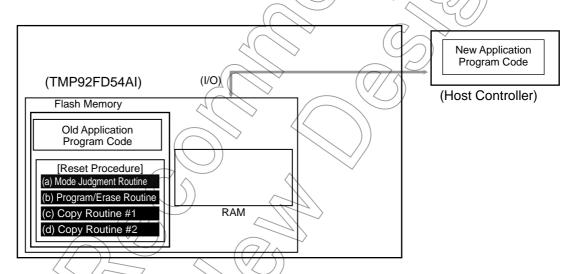

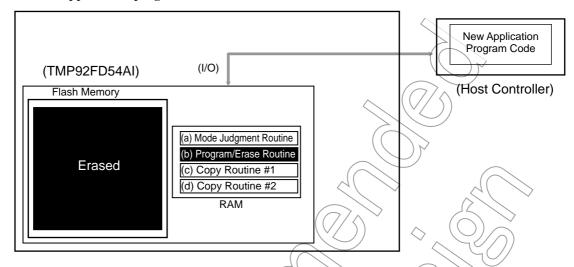

#### (Step 1) Building a programming environment

Determine the conditions (e.g., pin states) required for the flash memory to enter User Boot mode and the I/O bus to be used to transfer new program code. Create hardware and software accordingly. Before installing the TMP92FD54AI on a PC board, write the following four program routines into an arbitrary flash block in Single Boot mode.

- (a) Mode judgment routine: Code to determine whether or not to switch to User Boot mode

- (b) Program/erase routine: Code to download new program code from a host controller and reprogram the flash memory

- (c) Copy routine #1: Code to copy routines (a) to (d) to either the on-chip RAM or external memory device.

- (d) Copy routine #2: Code to copy routines (a) to (d) contained in either the on-chip RAM or external memory device to the flash memory.

Note: Routine (d) is a code to restore the reprogram routines into the flash memory. It is not necessary if routines (a) to (c) are contained in the flash memory after it is reprogrammed.

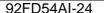

Figure 3.4.1 Building a Programming Environment

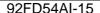

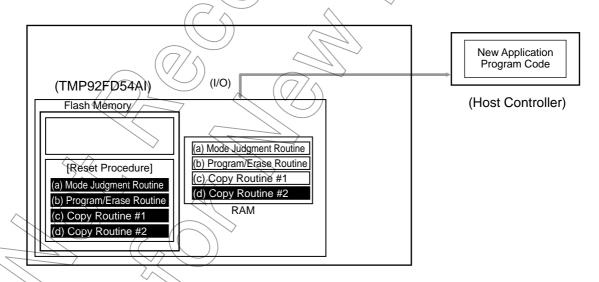

# (Step 2) Mode Transition to User Boot mode (when a mode judgment routine is included as part of the reset procedure)

Boot the TMP92FD54AI in Single-Chip mode. After a reset, the reset procedure determines whether to put the TMP92FD54AI flash memory in User Boot mode by calling a mode judgment routine. If mode switching conditions (e.g., pin states) are met, program execution jumps to user boot program for programming and erasure. (All interrupts including non-maskable interrupt must be globally disabled while in User Boot mode.)

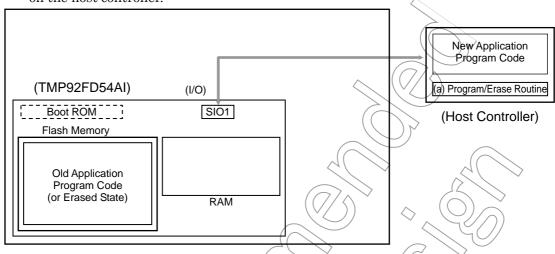

Figure 3.4.2 Mode Transition to User Boot Mode

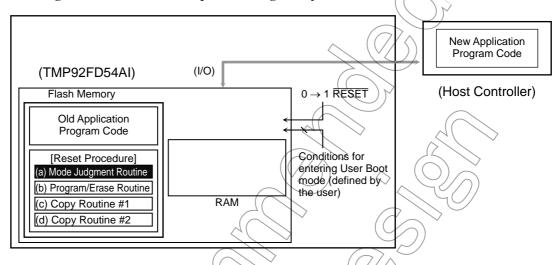

## (Step 3) Copying the user boot routines to the RAM

Execute copy routine #1 to copy the flash programming routines to either the TMP92FD54AI on-chip RAM or an external memory device. (In the following figure, the on-chip RAM is used.)

Note: If routines (a) to (d) are left unerased in the flash memory by using the Auto Block Erase command in Step 4, only the program/erase routine (routine (b)) should be copied into the RAM.

Figure 3.4.3 Copying the User Boot Routines to the RAM

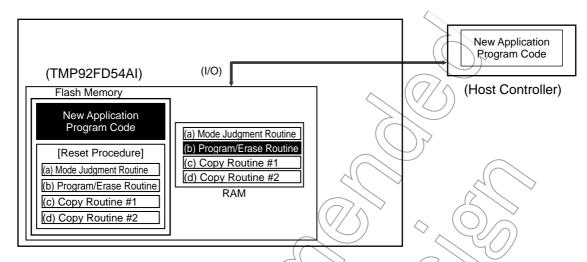

#### (Step 4) Erasing the flash memory using the program/erase routine

Jump program execution to the flash program/erase routine in the on-chip RAM to erase the flash memory (with the Auto Block Erase or Auto Chip Erase command) containing the old application program code.

Figure 3.4.4 Erasing the Flash Memory Using the Program/Erase Routine

## (Step 5) Restoring the user boot routines to the flash memory

Copy routines (a) to (d) to the flash memory by using copy routine #2 in the on-chip RAM.

Note: Step 5 is not required if routines (a) to (d) are kept in the flash memory by using the Auto Block Erase command.

Figure 3.4.5 Restoring the User Boot Routines to the Flash Memory

#### (Step 6) Writing a new application program code into the flash memory

Execute the flash program/erase routine in the on-chip RAM to download new application program code from the source (host controller) and program it into the erased flash block.

Figure 3.4.6 Writing a New Application Program Code into the Flash Memory

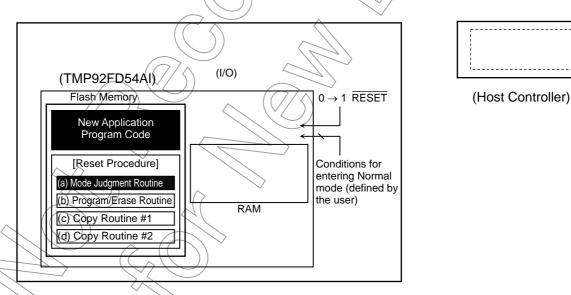

# (Step 7) Executing the new application program code

To reset the TMP92FD54AL drive the RESET pin Low. Upon reset, the on-chip flash memory is put in Normal mode. After RESET is released, the CPU will start executing the new application program code.

Figure 3.4.7 Executing the New Application Program Code

#### 3.4.1.2 (1-B) Program/Erase Procedure 2

Unlike example (1-A), only the essential part of the boot program codes should be incorporated in the flash memory for this method. Other programs are supplied from a controller as required upon reprogramming the flash memory.

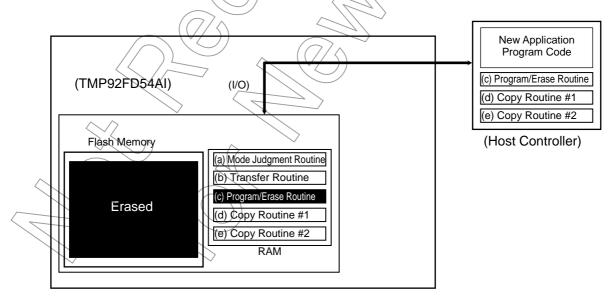

#### (Step 1) Building a programming environment

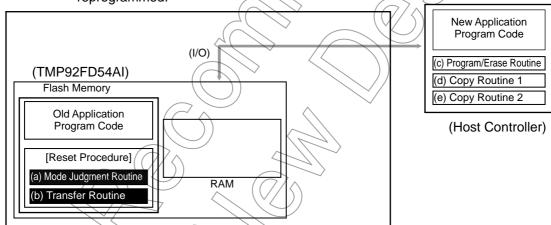

Determine the conditions (e.g. pin states) required for the flash memory to enter User Boot mode and the I/O bus to be used to transfer new program code. Create hardware and software accordingly. Before installing the TMP92FD54AI on a PC board, write the following two program routines into an arbitrary flash block in Single Boot mode.

- (a) Mode judgment routine: Code to determine whether or not to switch to User Boot mode

- (b) Transfer routine: Code to download new program/erase code from a host controller Prepare the following routines on the host controller:

- (c) Program/erase routine: Code to reprogram the flash memory

- (d) Copy routine #1: Code to copy routines (a) and (b) to the on-chip RAM or external memory device.

- (e) Copy routine #2: Code to copy routines (a) and (b) contained in either the on-chip RAM or external memory devices to the flash memory.

Note: Routines (d) and (e) are codes to restore the user boot routines into the flash memory. It is not necessary if routines (a) and (b) are contained in the flash memory after it is reprogrammed.

Figure 3.4.8 Building a Programming Environment

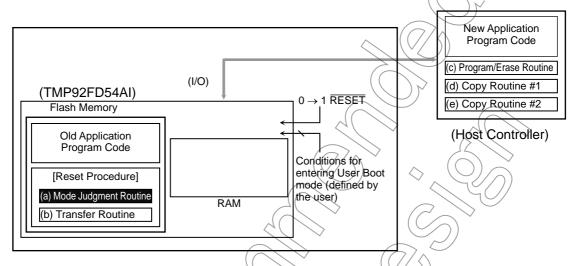

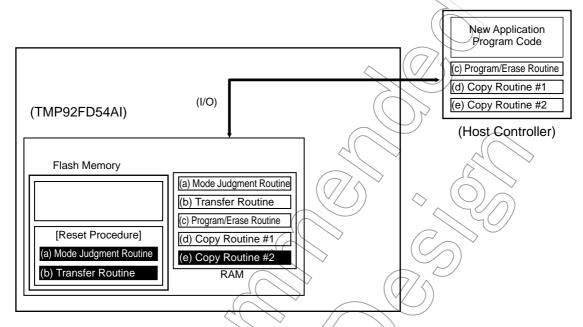

# (Step 2) Mode Transition to User Boot mode (when a mode judgment routine is included as part of the reset procedure)

Boot the TMP92FD54AI in Single-Chip mode. After a reset, the reset procedure determines whether to put the TMP92FD54AI flash memory in User Boot mode by calling a mode judgment routine. If mode switching conditions (e.g., pin states) are met, program execution jumps to user boot program for programming and erasure. (All interrupts including non-maskable interrupt must be globally disabled while in User Boot mode.)

Figure 3.4.9 Mode Transition to User Boot Mode

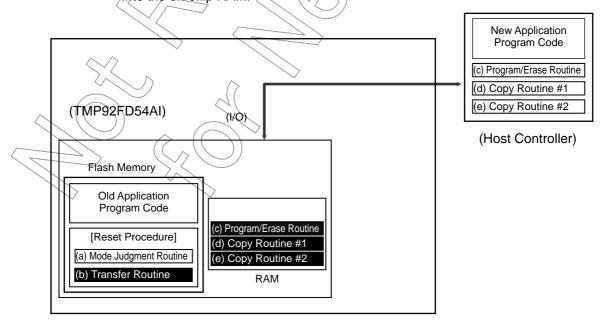

#### (Step 3) Copying the user boot routines from the host controller to the RAM

Execute the transfer routine (routine (b)) to download routines (c) to (e) from the source (host controller) to the on-chip RAM or an external memory device. (In the following figure, the on-chip RAM is used.)

Note: If routines (a) and (b) are left unerased in the flash memory by using the Auto Block Erase command in Step 5, only the program/erase routine (routine (c)) should be copied into the on-chip RAM.

Figure 3.4.10 Copying the User Boot Routines in User Boot Mode (from the Host Controller to the RAM)

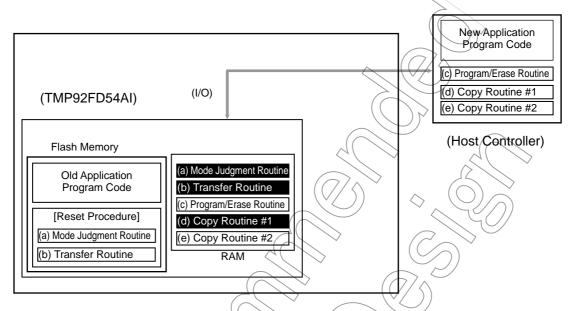

#### (Step 4) Copying the user boot routines from the flash memory to the on-chip RAM

Program execution jumps to the routine in the on-chip RAM. Execute copy routine #1 to copy routines (a) and (b) to the on-chip RAM.

Note: Step 4 is not required if routines (a) and (b) are kept in the flash memory by using the Auto Block Erase command in Step 5.

Figure 3.4.11 Copying the User Boot Routines (from the Flash Memory to the On-Chip RAM)

#### (Step 5) Erasing the flash memory using the program/erase routine

Execute the program/erase routine (routine (c)) to erase a flash block or chip containing the old application program code.

Figure 3.4.12 Erasing the Flash Memory Using the Program/Erase Routine

#### (Step 6) Restoring the user boot routines to the flash memory

Execute copy routine #2 to copy routines (a) and (b) in the on-chip RAM to the flash memory.

Note: Step 6 is not required if routines (a) and (b) are kept in the flash memory by using the Auto Block Erase command in Step 5.

Figure 3.4.13 Restoring the User Boot Routines to the Flash Memory

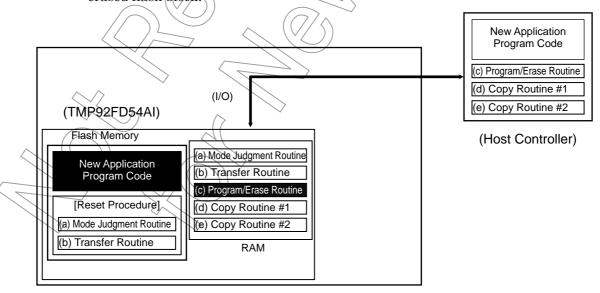

#### (Step 7) Writing a new application program code into the flash memory

Execute the flash program/erase routine (c) in the on-chip RAM to download new application program code from the source (host controller) and program it into the erased flash block.

Figure 3.4.14 Writing a New Application Program Code into the Flash Memory

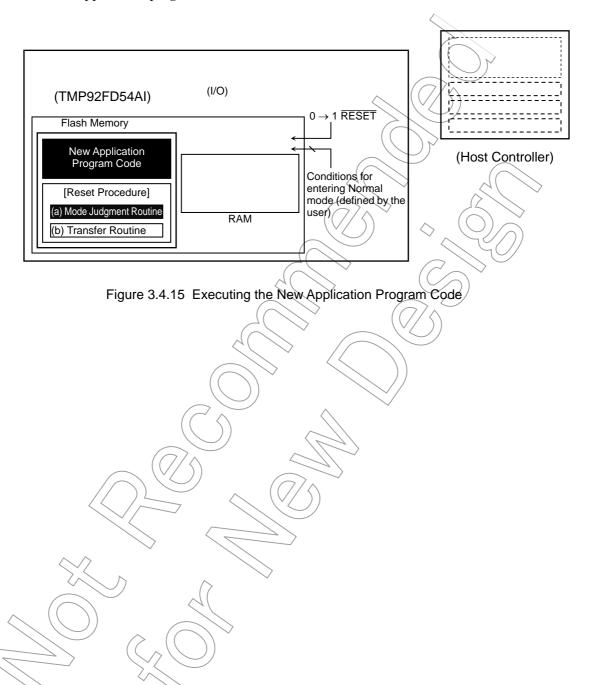

## (Step 8) Executing the new application program code

To reset the TMP92FD54AI, drive the  $\overline{RESET}$  pin Low. Upon reset, the on-chip flash memory is put in Normal mode. After  $\overline{RESET}$  is released, the CPU will start executing the new application program code.

#### 3.4.2 Single Boot Mode

In Single Boot mode, the flash memory can be programmed and erased by using a program contained in the TMP92FD54AI on chip boot ROM. This boot ROM is a masked ROM. The flash memory is programmed and erased by executing a program/erase routine (a user-created reprogramming routine) that is transferred to the RAM from an external host controller. In this mode, the on-chip boot ROM is mapped to the address area including the interrupt vector table for executing the on-chip boot ROM code. The flash memory is mapped to an address space different from the boot ROM area (refer to Figure 3.3.2).

The SIO (SIO1) of the TMP92FD54AI is connected to an external host controller. Via this serial link, a programming routine is downloaded from the host controller to the TMP92FD54AI on-chip RAM. Then, the flash memory is reprogrammed by executing the programming routine.

The host sends out both commands and programming data to reprogram the flash memory. Communications between the SIO1 and the host must follow the protocol described later. To secure the contents of the flash memory, the validity of the application's password is checked before a programming routine is downloaded into the on-chip RAM. If password matching fails, the transfer of a programming routine itself is aborted.

As in the case of User Boot (Single Chip) mode, all interrupts including nonmaskable interrupt must be globally disabled in Single Boot mode while the flash memory is being erased or programmed. When using SIO channels, software can check interrupt request flags in interrupt priority level registers, such as INTES1<ITX1C, IRX1C>, to determine whether reception/transmission has come to an end.

Once reprogramming is complete, it is recommended to protect relevant flash blocks from accidental corruption during subsequent Normal mode operations. For a detailed description of the program/erase sequence, refer to Section 3.5, Flash Memory Program/Erase in On-Board Programming Modes.

Note: Don't change the pin states of TEST0, TEST1, AM0 and AM1 during a reprogramming operation of the flash memory.

#### 3.4.2.1 Using the Program/Erase Routine in the On-Chip Boot ROM

#### (Step 1) Building a programming environment

Since a program/erase routine and programming data are transferred via the SIO1, the SIO1 must be connected to a host controller. Prepare a program/erase routine (routine (a)) on the host controller.

Figure 3.4.16 Building a Programming Environment

# (Step 2) Rebooting in Single Boot mode and the password matching (Rebooting from the on-chip ROM)

Reset the TMP92FD54AI with the mode setting pins held at appropriate logic values so that the CPU reboots from the on-chip boot ROM. To transfer the program/erase routine (routine (a)) from the source (host controller) to the on-chip RAM via the SIO, communications are made following the prescribed protocol shown in Table 3.4.4. The password transferred from the host controller is first compared to the contents of the special flash memory locations. (If the flash block has already been erased, the password is a sequence of 12 0xFF bytes.) For more details on password matching, see Section 3.4.2.14, Password.

Figure 3.4.17 Rebooting in Single Boot Mode (Rebooting from the on-chip ROM)

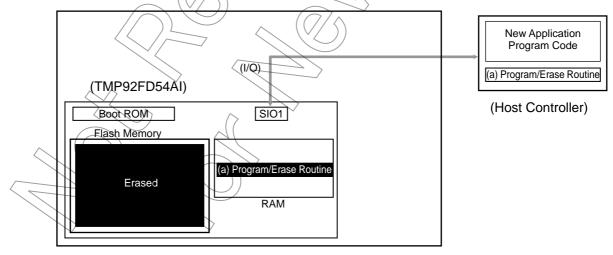

# (Step 3) Copying the program/erase routine from the host controller to the on-chip RAM

If the password was correct, the boot ROM downloads, via the serial link (SIO1), the program/erase routine (routine (a)) from the host controller into the on-chip RAM. The program/erase routine must be stored in the address range between 000400H and 006BFFH.

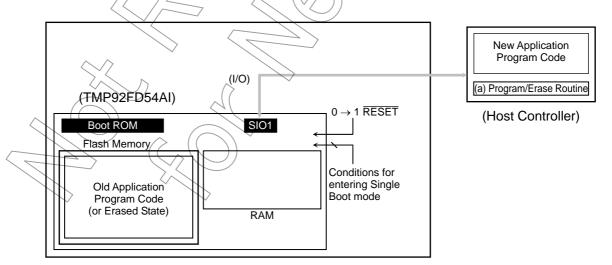

Figure 3.4.18 Copying the Program/Erase Routine from the Host Controller to the On-Chip RAM

#### (Step 4) Erasing the flash memory by executing the program/erase routine

The CPU jumps to the program/erase routine in the on-chip RAM to erase the flash block containing the old application program code as required. (The Auto Block Erase or Auto Chip Erase command should be used.)

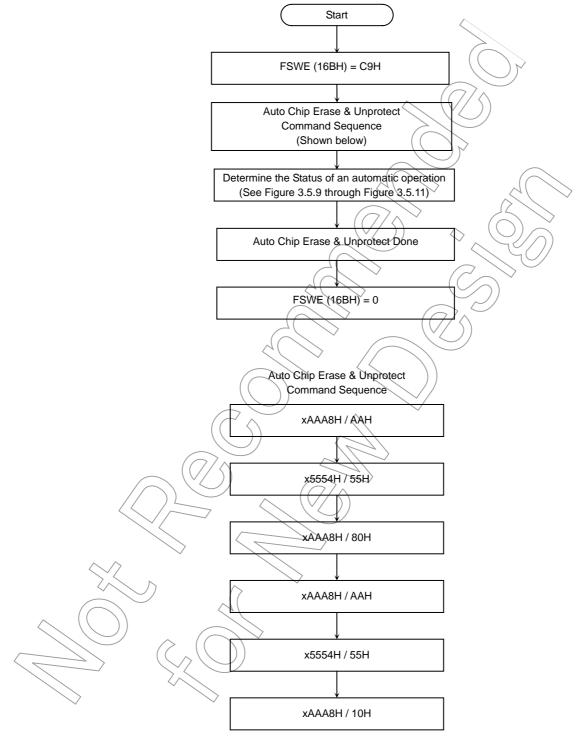

Note: Since the boot program has the Auto Chip Erase & Unprotect commands, the host controller is capable of erasing the flash chip without using the program/erase routine. To perform other operations such as the block erase and block protect operations, corresponding codes should be included in the program/erase routine.

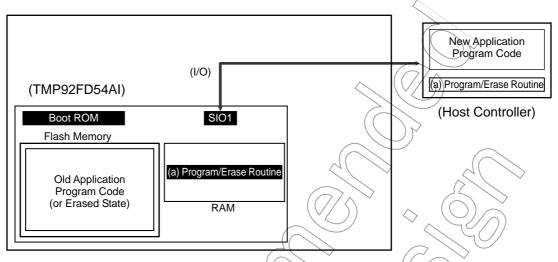

Figure 3.4.19 Erasing the Flash Memory by Executing the Program/Erase Routine

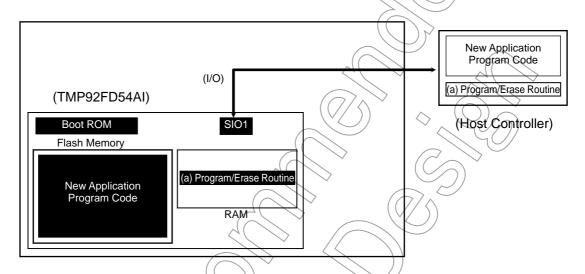

#### (Step 5) Copying a new application program code

Next, the program/erase routine (routine (a)) in the on-chip RAM downloads a new application program code from the source (host controller) and programs it into the erased flash block. Once programming is complete, protection of that flash block is turned on as required.

In the example below, a programming data transfer is performed using the same SIO communication format as for the program/erase routine. However, once the program/erase routine has been transferred, it is free to change the setting, such as the transfer path and the source of the transfer. Create board hardware and a program/erase routine to suit your particular needs.

Figure 3.4.20 Copying a New Application Program Code

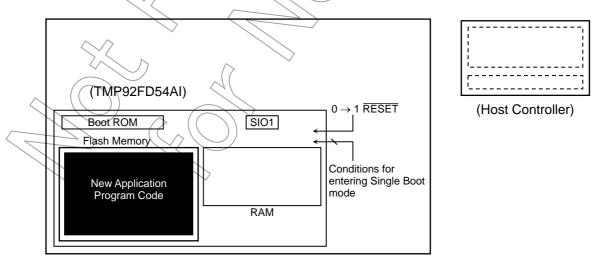

#### (Step 6) Executing the new application program

When programming of the flash memory is complete, power off the board and disconnect the cable leading from the host to the target board. Turn on the power again so that the TMP92FD54AI reboots in Single-Chip mode to execute the new program.

Figure 3.4.21 Executing the New Application Program

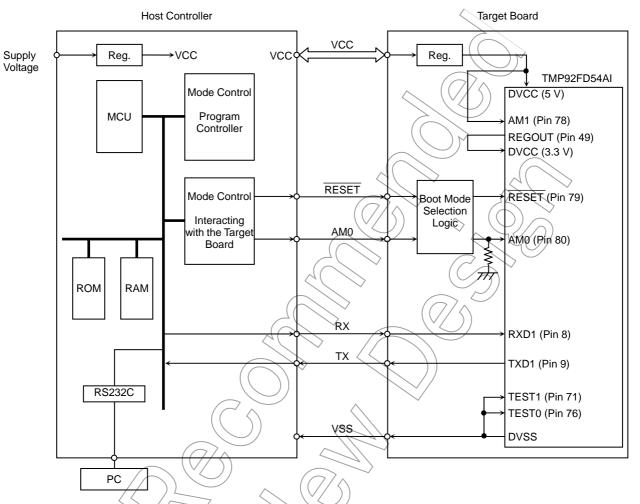

#### 3.4.2.2 Connection Example in Single Boot Mode

In Single Boot mode, serial transfer is used to reprogram the flash memory while the TMP92FD54AI is installed on the board. In this mode, SIO1 of the TMP92FD54AI is connected to a host controller, which is to issue commands to the target board. Figure 3.4.22 shows an example of host-to-target connections.

Figure 3.4.22 Example of a Connection between a Host Controller and a Target Board (When the SIO1 is Configured for UART mode in Single Boot mode)

#### 3.4.2.3 Mode Configuration

For on-board programming, boot the TMP92FD54AI in Single Boot mode as follows:

AM0, AM1 = H; TEST0, TEST1 = L;

$$\overline{\text{RESET}} = L \rightarrow H$$

Set the RESET input at logic 0, while setting the AM0, AM1, TEST0 and TEST1 inputs at the logic values shown above. Then release RESET (high) so that the TMP92FD54AI reboots in Single Boot mode.

#### 3.4.2.4 Memory Map

Figure 3.4.23 shows a comparison of the memory maps in Single-Chip and Single Boot modes. In Single Boot mode, the on-chip flash memory is mapped to the addresses 010000H through 08FFFFH; while the on-chip boot ROM (masked ROM) is mapped to the addresses FFF400H through FFFFFFH.

Figure 3.4.23 Memory Maps (for Single-Chip and Single Boot Modes)

#### 3.4.2.5 Interface Specification

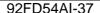

The SIO communication format in Single Boot mode is shown below. The serial transfer supports the UART (asynchronous) mode. To perform on-board programming, the host controller must also be configured to use the following communication format.

#### • UART mode

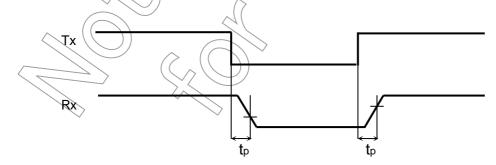

Communication channel: SIO channel 1

Serial transfer mode: UART (asynchronous) mode, full duplex

Data length: 8 bits

Parity bits: None

STOP bits: 1 bit

Baud rate: Refer to Table 3.4.1

Table 3.4.1 Selective Baud Rates

|                 |       |       | ( )  | V    |      |

|-----------------|-------|-------|------|------|------|

| Baud Rate (bps) | 38400 | 19200 | 9600 | 4800 | 2400 |

Table 3.4.2 Pin Connections Required in Single Boot Mode

| Power supply pins   | DVCC3/5 (3.3/5.0 V) |

|---------------------|---------------------|

|                     | DVSS                |

| Mode-setting pins   | AM1, AM0,           |

|                     | TEST1, TEST0        |

| Reset pin           | RESET               |

| Communications pins | TXD1 /              |

|                     | RXD1                |

|                     |                     |

#### 3.4.2.6 Data Transfer Formats

Operation commands and data transfer formats for each operation mode are shown in Table 3.4.3 through Table 3.4.7. At the same time, read the descriptions on the boot program commands described later.

Table 3.4.3 Operation Commands

|               | Code   | Command                     |  |  |

|---------------|--------|-----------------------------|--|--|

|               | 10H    | RAM Transfer                |  |  |

| $\mathcal{N}$ | 20H /> | Show Flash Memory Sum       |  |  |

| 30H           |        | Show Product Information    |  |  |

|               | 40H    | Auto Chip Erase & Unprotect |  |  |

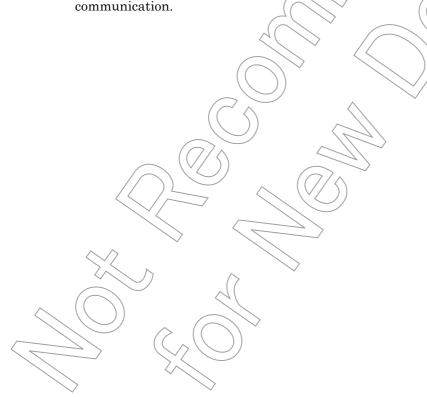

Table 3.4.4 Transfer Format for the RAM Transfer Command

|           | Byte                   | Data Transferred from the Controller to the TMP92FD54AI | Baud Rate                              | Data Transferred from the TMP92FD54AI to the Controller |

|-----------|------------------------|---------------------------------------------------------|----------------------------------------|---------------------------------------------------------|

| Boot ROM  | 1st hyte               | Serial operation mode and baud rate                     | Desired baud                           | _                                                       |

| DOOL INOW | 13t byte               | For UART mode 86H                                       | rate (Note 1)                          | _                                                       |

|           |                        | 55.                                                     |                                        |                                                         |

|           | 2nd byte               | _                                                       |                                        | ACK for the serial operation mode byte                  |

|           |                        |                                                         |                                        | For UART                                                |

|           |                        |                                                         |                                        | Normal acknowledge 86H                                  |

|           |                        |                                                         |                                        | (The boot program aborts if the baud                    |

|           |                        |                                                         |                                        | rate can not be set correctly.)                         |

|           | 3rd byte               | Command code (10H)                                      | (c                                     | _                                                       |

|           | 4th byte               | _                                                       |                                        | ACK for the command code byte (Note 2)                  |

|           |                        |                                                         |                                        | Normal acknowledge 10H                                  |

|           |                        |                                                         |                                        | Negative acknowledge x1H                                |

|           |                        |                                                         | (,)                                    | Communication error x8H                                 |

|           | 5th byte               | Password sequence (12 bytes)                            |                                        |                                                         |

|           | thru                   | (0055541145 00555511)                                   | (                                      | $\wedge$ (O) $\tilde{\wedge}$                           |

|           | 16th byte              | (08FEF4H thru 08FEFFH)                                  |                                        |                                                         |

|           | 17th byte<br>18th byte | Checksum value for bytes 5 - 16                         |                                        | ACK for the checksum byte (Note 2)                      |

|           | Tollibyle              | _                                                       | $\rightarrow$                          | Normal acknowledge 10H                                  |

|           |                        | 4( \                                                    | $\triangleright$                       | Negative acknowledge 11H                                |

|           |                        |                                                         |                                        | Communication error 18H                                 |

|           | 19th byte              | RAM storage start address (bits 31-24) (Note 3)         | (                                      | ——————————————————————————————————————                  |

|           | 20th byte              | RAM storage start address (bits/23-16) (Note 3)         |                                        | _                                                       |

|           | 21st byte              | RAM storage start address (bits 15-8) (Note 3)          |                                        | _                                                       |

|           | 22nd byte              | RAM storage start address (bits 7-0) (Note 3)           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | _                                                       |

|           | 23rd byte              | RAM storage byte count (bits 15-8) (Note 3)             |                                        | _                                                       |

|           | 24th byte              | RAM storage byte count (bits 7-0) (Note 3)              | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | _                                                       |

|           | 25th byte              | Checksum value for bytes 19-24 (Note 3)                 |                                        | _                                                       |

|           | 26th byte              |                                                         |                                        | ACK for the checksum byte (Note 2)                      |

|           |                        |                                                         |                                        | Normal acknowledge 10H                                  |

|           |                        | $(O/\land)$                                             |                                        | Negative acknowledge 11H                                |

|           |                        |                                                         | $\rightarrow$                          | Communication error 18H                                 |

|           | 27th byte              | RAM storage data                                        |                                        | _                                                       |

|           | thru <                 |                                                         |                                        |                                                         |

|           | mth byte               |                                                         |                                        |                                                         |

|           | (m + 1)th byte         | Checksum value for bytes 27-m                           |                                        | <u> </u>                                                |

|           | (m + 2)th byte         |                                                         |                                        | ACK for the checksum byte (Note 2)                      |

|           | >,<                    | $\rightarrow$                                           |                                        | Normal acknowledge 10H                                  |

|           |                        | $\triangleright$ ) $\land$                              |                                        | Negative acknowledge 11H                                |

| DAM       | (m + 2)th by th        |                                                         | 1                                      | Communication error 18H                                 |

| RAM       | (m + 3)th byte         |                                                         |                                        | Jump to RAM storage start address                       |

Note 1: For baud rate options, see Table 3.4.1.

Note 2: In case of any negative acknowledge the boot program returns to a state in which it waits for a command code (the 3rd byte).

Note 3: The 19th to 25th bytes must be within the RAM address range between 000400H and 006BFFH.

Table 3.4.5 Transfer Format for the Show Flash Memory Sum Command

|          | Byte     | Data Transferred from the Controller to the TMP92FD54AI  | Baud Rate                  | Data Transferred from the TMP92FD54AI to the Controller                                                                                     |

|----------|----------|----------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Boot ROM | 1st byte | Serial operation mode and baud rate<br>For UART mode 86H | Desired baud rate (Note 1) | _                                                                                                                                           |

|          | 2nd byte | _                                                        | _                          | ACK for the serial operation mode byte For UART Normal acknowledge 86H (The boot program aborts if the baud rate can not be set correctly.) |

|          | 3rd byte | Command code (20H)                                       |                            |                                                                                                                                             |

|          | 4th byte | _                                                        |                            | ACK for the command code byte (Note 2)  Normal acknowledge 20H  Negative acknowledge x1H  Communication error x8H                           |

|          | 5th byte | _                                                        | (1)                        | SUM (upper byte)                                                                                                                            |

|          | 6th byte | _                                                        |                            | SUM (lower byte)                                                                                                                            |

|          | 7th byte | _                                                        |                            | Checksum value for bytes 5 and 6                                                                                                            |

|          | 8th byte | (Wait for the next command code.)                        |                            |                                                                                                                                             |

Note 1: For baud rate options, see Table 3.4.1.

Note 2: In case of any negative acknowledge, the boot program returns to a state in which it waits for a command code (the 3rd byte).

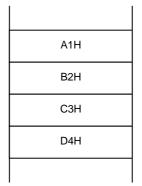

Table 3.4.6 Transfer Format for the Show Product Information Command (1 of 2)

|          | Byte                           | Data Transferred from the Controller to the TMP92FD54AI  | Baud Rate                  | Data Transferred from the TMP92FD54AI to the Controller                                                                                       |

|----------|--------------------------------|----------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Boot ROM | 1st byte                       | Serial operation mode and baud rate<br>For UART mode 86H | Desired baud rate (Note 1) | _                                                                                                                                             |

|          | 2nd byte                       | _                                                        |                            | ACK for the serial operation mode byte  For UART  Normal acknowledge 86H  (The boot program aborts if the bauc rate cannot be set correctly.) |

|          | 3rd byte                       | Command code (30H)                                       |                            |                                                                                                                                               |

|          | 4th byte                       | _                                                        |                            | ACK for the command code byte (Note 2)  Normal acknowledge 30H  Negative acknowledge x1H  Communication error x8H                             |

|          | 5th byte                       | _                                                        | 4/                         | Flash memory data (at address 08FEF0H)                                                                                                        |

|          | 6th byte                       | _                                                        |                            | Flash memory data (at address 08FEF1H)                                                                                                        |

|          | 7th byte                       | _                                                        | $((//\wedge$               | Flash memory data (at address 08FEF2H)                                                                                                        |

|          | 8th byte                       | _                                                        |                            | Flash memory data (at address 08FEF3H)                                                                                                        |

|          | 9th byte                       | _ (/                                                     |                            | Product name (12-byte ASCII code)                                                                                                             |

|          | thru<br>20th byte              |                                                          |                            | TMP92FD54AI_from the 9th byte<br>(where_denotes a space)                                                                                      |

|          | 21st byte                      |                                                          |                            | Password comparison start address (4 bytes)                                                                                                   |

|          | thru                           |                                                          | $\triangleright$           | FAH, FEH, 08H and 00H from the 21st byte                                                                                                      |

|          | 24th byte                      |                                                          | ,                          |                                                                                                                                               |

|          | 25th byte                      | - 4( \>                                                  |                            | RAM start address (4 bytes)                                                                                                                   |

|          | thru                           |                                                          |                            | 00H, 04H, 00H and 00H from the 25th byte                                                                                                      |

|          | 28th byte                      |                                                          |                            |                                                                                                                                               |

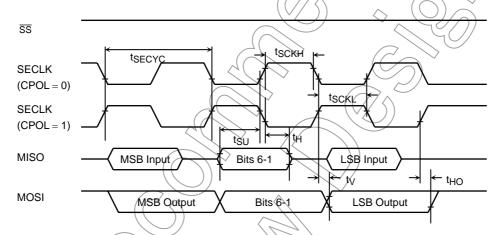

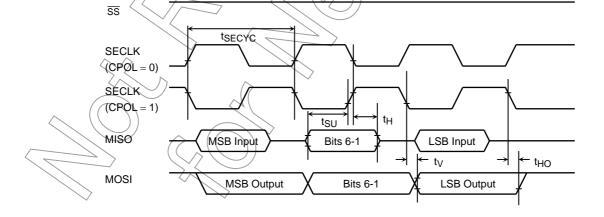

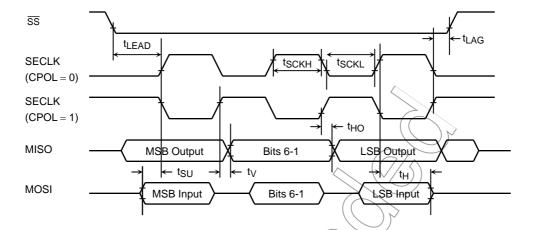

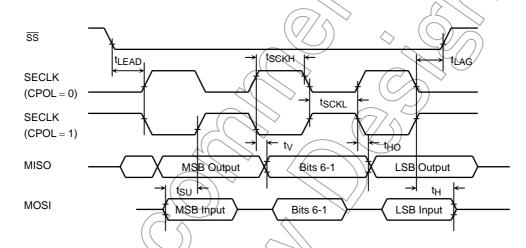

|          | 29th byte<br>thru              |                                                          |                            | Dummy data (4 bytes)<br>FEH, 6BH, 00H and 00H from the 29th byte                                                                              |