# MB86297A Carmine Hardware Manual

Revision 1.28 11th March 2009

- The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU or any third party or does FUJITSU warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite). Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

Copyright © 2009 FUJITSU LIMITED All rights reserved

#### **Trademarks**

Sun is a trademark of Sun Microsystems, Inc. in the United States.

Windows is a trademark of Microsoft Corporation in the United States and other countries

Verilog-XL is a trademark of Cadence Design Systems, Inc.

UNIX is a registered trademark, which is licensing X/Open Company Limited., in the United States and other countries.

# **Revision History**

| Rev.No | Date       | Contents                                                                                                                                                                                                                                                                                              |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01     |            | Initial Release after translation (Note: this version was updated in more than one version)                                                                                                                                                                                                           |

| 02     |            | Preliminary version                                                                                                                                                                                                                                                                                   |

| 0.1    | 2005/07/25 | First draft version after translation (Note: this version was updated in more than one version)                                                                                                                                                                                                       |

| 0.2    | 2005/08/22 | Pin table updated                                                                                                                                                                                                                                                                                     |

| 0.7    | 2005/12/08 | General update, formating not yet finished                                                                                                                                                                                                                                                            |

|        |            | Corrected "1.1 Overview".                                                                                                                                                                                                                                                                             |

|        |            | Added "1.3 Signal".                                                                                                                                                                                                                                                                                   |

|        |            | Added "1.4 Pin Assignement".                                                                                                                                                                                                                                                                          |

|        |            | Added "1.5 Pin Function".                                                                                                                                                                                                                                                                             |

|        |            | Corrected "1.6 Address Map".                                                                                                                                                                                                                                                                          |

|        |            | Added "2 DRAM Controller".                                                                                                                                                                                                                                                                            |

|        |            | Added "3 PCI Interface".                                                                                                                                                                                                                                                                              |

|        |            | Added "I2C Interface".                                                                                                                                                                                                                                                                                |

|        |            | Added and corrected "5 CARMINE CONTROL".                                                                                                                                                                                                                                                              |

|        |            | Corrected "6 KOTTOS".                                                                                                                                                                                                                                                                                 |

|        |            | Added and corrected "7 Display Controller".                                                                                                                                                                                                                                                           |

|        |            | Added and corrected "8 Video Capture".                                                                                                                                                                                                                                                                |

|        |            | Added "9 Electrical Characteristics".                                                                                                                                                                                                                                                                 |

|        |            | Overview Changed "I/O column", in Pin Assignment, for pins used as output pins at test time. Added description of processing of unused pins for when the graphics memory interface is used via a 32-bit data bus. Added "Description of Test Pin (JTAG)". Added "Description of Interrupt Registers". |

|        |            | DRAM Controller Added "DRAM CTRL DDRIF1 Register".                                                                                                                                                                                                                                                    |

|        |            | Video Capture Changed English text into Japanese. Deleted "Description of RGB555 mode".                                                                                                                                                                                                               |

|        |            | Added "Description of RGB Input function" and "Register Description".  Electrical Characteristics                                                                                                                                                                                                     |

|        |            | Corrected "Recommended Operating Conditions for Standard CMOS I/O".                                                                                                                                                                                                                                   |

|        |            | Added "Standard CMOS I/O V-I Characteristics".                                                                                                                                                                                                                                                        |

|        |            | Added "PCI I/O DC Characteristics".                                                                                                                                                                                                                                                                   |

| 0.71   | 2005/12/29 | Content is equal to 0.7, content table was included                                                                                                                                                                                                                                                   |

| 0.72   | 2006/02/06 | Basing on version 0.7                                                                                                                                                                                                                                                                                 |

|        |            | 0                                                                                                                                                                                                                                                                                                     |

|      |            | History table updated, list of modification from rev. 02 to rev. 0.7                                                                                                                                                                                                                   |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |            | Formatting finished and a few details were added after translation was finished                                                                                                                                                                                                        |

| 1.0  | 2006/07/21 | Initial Release                                                                                                                                                                                                                                                                        |

| 1.1  | 2007/03/27 | Chapter 2 is replaced with the order in Chapter 3.                                                                                                                                                                                                                                     |

|      |            | 6. KOTTOS(2D/3D Graphics)                                                                                                                                                                                                                                                              |

|      |            | ➤ Bitmap data order in explanation of DrawBitmapP had been opposite.                                                                                                                                                                                                                   |

|      |            | Added "Need setting 1 to CO field of MDR0 in BltCopyCompressedP and<br>BltCopyCompAlphaMapP".                                                                                                                                                                                          |

|      |            | Added the explanation about Z calculation of Shadow and Non-TopLeft<br>mode.                                                                                                                                                                                                           |

|      |            | > Added the EQUAL judgement isn't exact in when Z value has slope.                                                                                                                                                                                                                     |

|      |            | Added the explanation of an anti-aliasing with blend function. And added<br>the explanation of an anti-aliasing with texture.                                                                                                                                                          |

|      |            | ➤ The value of command in DrawVertex2i had been wrong.                                                                                                                                                                                                                                 |

|      |            | 7. Display Controller                                                                                                                                                                                                                                                                  |

|      |            | > VCCC register description                                                                                                                                                                                                                                                            |

|      |            | change description about software reset and add WBsr.                                                                                                                                                                                                                                  |

|      |            | > L1BLD register description: correct error description about L1AS-bit                                                                                                                                                                                                                 |

|      |            | > WBM register description: change description about functions of each bit                                                                                                                                                                                                             |

|      |            | > Add description about display layer limit                                                                                                                                                                                                                                            |

|      |            | 8. Video Capture                                                                                                                                                                                                                                                                       |

|      |            | ➤ 8.2 Selection of input port                                                                                                                                                                                                                                                          |

|      |            | describe that RGB input can be also used as 656 input                                                                                                                                                                                                                                  |

|      |            | > 8.6.1, 8.6.2: change paragraph number in them                                                                                                                                                                                                                                        |

| 1.20 | 2007/06/05 | Minor English corrections For better understanding, corrected VCCC register, removed references to POM bit (DCM3 register). Correct HSP register (15 clocks latency).                                                                                                                  |

| 1.21 | 2007/06/12 | Added short description of Field Detection bit (4) in DCM0/DCM1 register                                                                                                                                                                                                               |

| 1.22 | 2007/06/25 | Corrected DCM3 description (DCKD field) +17 to +16 PLL Clocks.                                                                                                                                                                                                                         |

|      |            | Added: DCM0/1 bit 5 description.                                                                                                                                                                                                                                                       |

| 1.23 | 2008/03/20 | Corrected Register Overview (L5 for 08C, 090, 094, 098). Corrected image positioning section 6.5.9 (text was behind image)                                                                                                                                                             |

| 1.24 | 2008/04/01 | Corrected value for CHLPF_x (11) + K3 from 10/32 to 8/32 (section 8.4.3).                                                                                                                                                                                                              |

| 1.25 | 2008/04/03 | Corrected typo in CSC (Capture SCale), corrected explanations in 7.11 'Simultaneous layer display restrictions'. Section 8.5.2 Interrupt Status, removed last sentence and changed clearing order. Corrected value of bit 16 in RGBS register. Changed description of RGBCMb register. |

| 1.26 | 2008/04/30 | Added width of SZP and DSP bitfields in section 6.4.4. (G_BitBlt).                                                                                                                                                                                                                     |

| 1.27 | 2008/05/27 | Corrected typo in description of DEVSEL timing (Status register IDSEL+06h).                                                                                                                                                                                                            |

|      |            |                                                                                                                                                                                                                                                                                        |

|      |            | Chapter 3, replaced 'disabled' with word 'prohibited'                                                                                                                                                                                                                                  |

| 1.28 | 2009/03/11 | Added description of bits 15 + 14 (FIFO size) and renamed register from 'DRAM CTRL Reserve 1' to 'DRAM CTRL FIFO Size'. |

|------|------------|-------------------------------------------------------------------------------------------------------------------------|

|      |            | Reworked descriptions in section 9.3 Precautions at Power ON                                                            |

|      |            | Corrections to description of Data Format in Display Controller                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

|      |            |                                                                                                                         |

# **CONTENTS**

| 1 8        | SPECIFICATION OF CARMINE CHIP                               | 1  |

|------------|-------------------------------------------------------------|----|

| 1.1        | 1 Overview                                                  |    |

| 1.2        |                                                             |    |

| 1.3        | 3 SIGNAL                                                    | 3  |

| Î          | 1.3.1 Signal Line                                           | 3  |

| 1.4        |                                                             |    |

|            | 1.4.1 TEBGA543 Package Pin Assignment (TOP_VIEW)            |    |

|            | 1.4.2 Package Pin Assignment Table                          |    |

| 1.5        |                                                             |    |

|            | 1.5.1 PCI Interface                                         |    |

|            | 1.5.2 Video Output Interface                                |    |

|            | 1.5.3 Video Capture Interface                               |    |

|            | 1.5.4 I <sup>2</sup> C Interface                            |    |

|            | 1.5.5 Graphics Memory Interface                             |    |

|            | 1.5.6 Clock Input                                           |    |

| 1.6        |                                                             |    |

| 1.7        |                                                             |    |

|            |                                                             |    |

| 2 I        | PCI INTERFACE                                               | 22 |

| 2.1        | 1 Features                                                  | 22 |

| 2.2        | 2 FUNCTION                                                  | 23 |

| 2          | 2.2.1 Transfer to PCI Target                                |    |

| 2          | 2.2.2 Generation of PCI Target Abort                        | 23 |

| 2.3        |                                                             |    |

|            | 2.3.1 Register Address Mapping                              |    |

|            | 2.3.2 Configuration Register                                |    |

|            | 2.3.3 Internal Register (BAR0)                              |    |

|            | 2.3.4 Configuration Register Details                        |    |

| 2          | 2.3.5 Internal Register Details (BAR0)                      |    |

| 3 I        | DRAM CONTROLLER                                             | 35 |

| 3.1        | 1 DRAM Refresh                                              | 35 |

| 3.2        |                                                             |    |

| ź          | 3.2.1 I/O Mode Setting                                      |    |

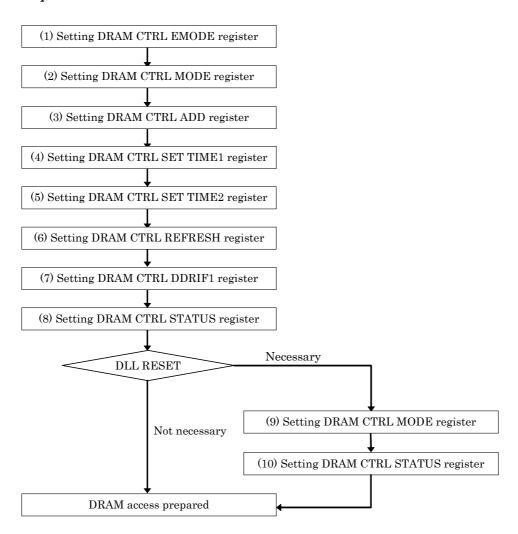

| Ĵ          | 3.2.2 Setting Procedures for DRAM Initial Sequence          |    |

| Ĵ          | 3.2.3 Internal Status of DRAM Controller and Issued Command |    |

| 3.3        | 3 DRAM CONTROLLER CONTROL REGISTERS                         | 38 |

| Ĵ          | 3.3.1 Register List                                         | 38 |

| Ĵ          | 3.3.2 Register Details                                      | 39 |

| 4 I        | I <sup>2</sup> C INTERFACE                                  | 52 |

|            |                                                             |    |

| 4.1<br>4.2 | -                                                           |    |

| 4.2        |                                                             |    |

| 4.4        |                                                             |    |

| 4.5        |                                                             |    |

|            | 4.5.1 Start Condition                                       |    |

|            | 4.5.2 Stop Condition                                        |    |

|            | 4.5.3 Addressing                                            |    |

|            | 4.5.4 Adjustment of SCL Synchronization                     |    |

|            | 4.5.5 Arbitration                                           |    |

|            | 4.5.6 Acknowledge/Negative Acknowledge                      |    |

| 4          | 4.5.7 Bus Error                                             |    |

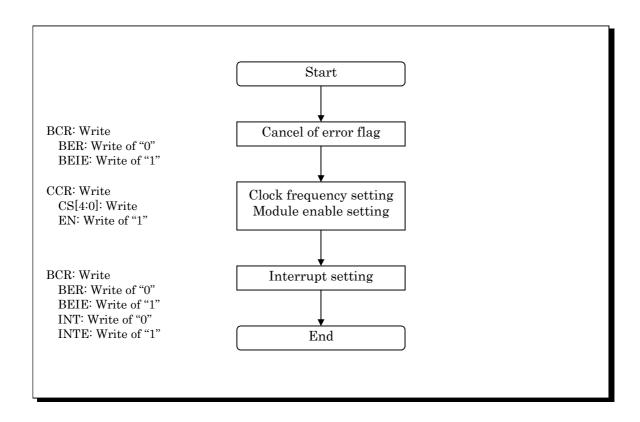

| 4          | 4.5.8 Initialization                                        |    |

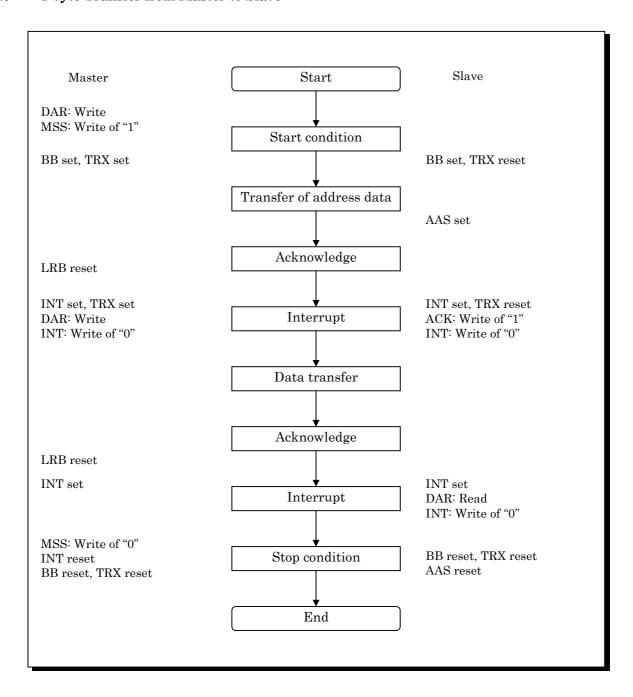

| 4          | 4.5.9 1-byte Transfer from Master to Slave                  | 64 |

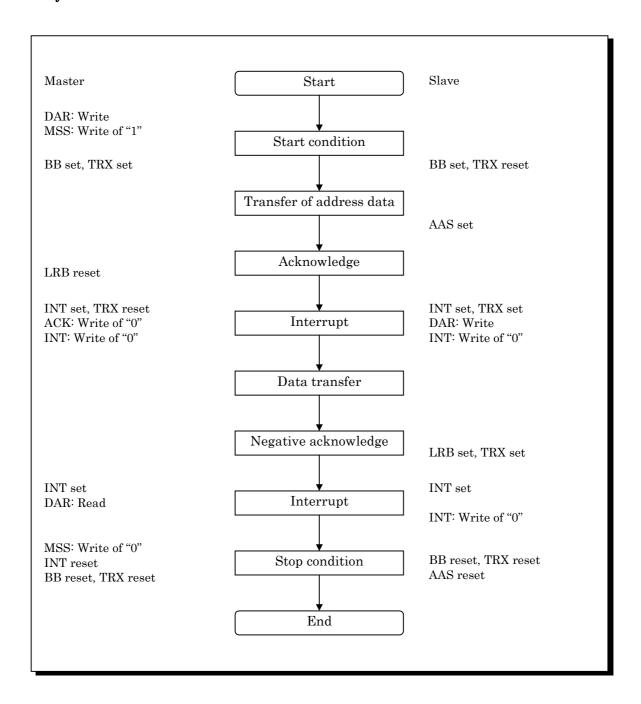

| 4.5.10         | O 1-byte Transfer from Slave to Master                       | 65  |

|----------------|--------------------------------------------------------------|-----|

| 4.5.1          | l Return after Bus Error                                     | 66  |

| 4.5.12         | 2 Interrupt Processing and Wait Request to the Master Device | 67  |

| 4.6            | Cautions                                                     | 68  |

| 4.6.1          | 10-bit Slave Address                                         | 68  |

| 4.6.2          | Conflict among SCC, MSS and INT Bits                         | 68  |

| 4.6.3          | Setting of Serial Transfer Clock                             | 68  |

| 4.6.4          | Restrictions on Multimaster                                  | 68  |

| 4.7            | REGISTER CONFIGURATION                                       | 69  |

| 4.7.1          | Register List                                                | 69  |

| 4.7.2          | Register Details                                             |     |

| 5 CAR          | MINE CONTROL                                                 | 81  |

| 5.1            | NTERRUPT                                                     |     |

| 5.1.1          | Block Diagram                                                |     |

|                | RESET SEQUENCE                                               |     |

|                | CARMINE CONTROL REGISTERS                                    |     |

| 5.3.1          | Register List                                                |     |

| 5.3.2          | Register Details                                             |     |

|                |                                                              |     |

| 6 KOT          | TOS (2D/3D GRAPHICS)                                         | 97  |

| 6.1            | Overview                                                     | 97  |

| 6.1.1          | Interface                                                    |     |

| 6.1.2          | Function                                                     |     |

|                | REGISTER LIST                                                |     |

|                | REGISTER DETAILS                                             |     |

| 6.3.1          | HOSTIF Module                                                |     |

| 6.3.2          | Rendering Engine Module                                      |     |

| 6.3.3          | Vertex Reader Module                                         |     |

| 6.3.4          | VL Engine Module                                             |     |

| 6.3.5          | Primitive Engine Module                                      |     |

|                | DISPLAY LIST                                                 |     |

| 6.4.1          | Overview                                                     |     |

| 6.4.2          | Display List Transfer Mode                                   |     |

| 6.4.3          | Header Format                                                |     |

| 6.4.4          | Geometry Display List                                        |     |

| 6.4.5          | Rendering Display List                                       |     |

|                | APPLICATION NOTE                                             |     |

| 6.5.1          | Host Interface                                               |     |

| 6.5.2          | Initialization Procedure for Hardware                        |     |

| 6.5.3          | Basic Drawing Procedure                                      |     |

| 6.5.4          | Lighting                                                     |     |

| 6.5.5          | Flat shading                                                 |     |

| 6.5.6          | Gouraud shading                                              |     |

| 6.5.7          | · · · · · · · · · · · · · · · · · · ·                        |     |

| 6.5.8          | Alpha blendingLogical operation drawing                      |     |

| 6.5.9          | • •                                                          |     |

| 6.5.10         | Depth test                                                   |     |

| 6.5.1<br>6.5.1 | 11 0                                                         |     |

|                | 8                                                            |     |

| 6.5.12         | 1 3 6                                                        |     |

| 6.5.1.         |                                                              |     |

| 6.5.14         | 7.0                                                          |     |

| 6.5.13         | 2.0 33                                                       |     |

| 6.5.10         | · · · · · · · · · · · · · · · · · · ·                        |     |

| 6.5.17         | 0 33 0                                                       |     |

| 6.5.18         | 1 2                                                          |     |

| 6.5.19         |                                                              |     |

| 6.5.20         | y y                                                          |     |

| 6.5.2          | l Debug function                                             | 338 |

|   | 6.5.22         | 2D Drawing Function                                                 | 339         |

|---|----------------|---------------------------------------------------------------------|-------------|

|   | 6.5.23         | Top-left Rule Not-applicable Primitive Drawing                      | 348         |

|   | 6.5.24         | Shadow Primitive Drawing                                            | 349         |

|   | 6.5.25         | Coral-compatible Drawing Function                                   | 349         |

|   | 6.5.26         | Processing Sequence                                                 | 350         |

|   | 6.5.26.        | Test Processing Order                                               | 350         |

|   | 6.5.26.2       | 2 Sequence of blend processing                                      | 351         |

| 7 | DISPLA         | Y CONTROLLER                                                        | 354         |

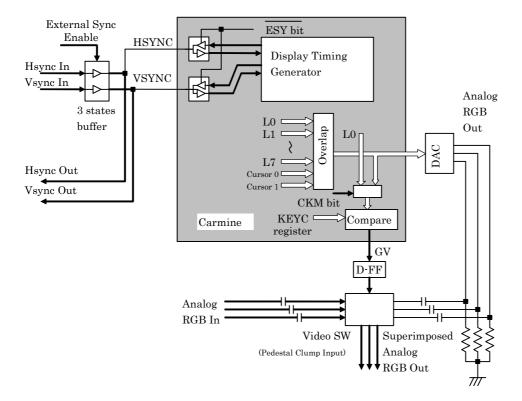

|   |                | RVIEW                                                               |             |

|   | 7.1.1          | Entire Configuration                                                |             |

|   | 7.1.2          | Individual functions of display controller                          |             |

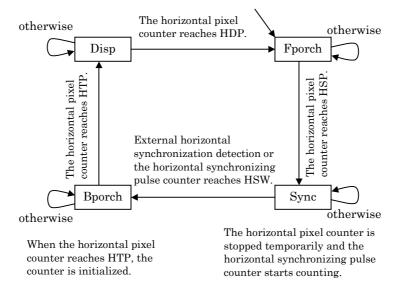

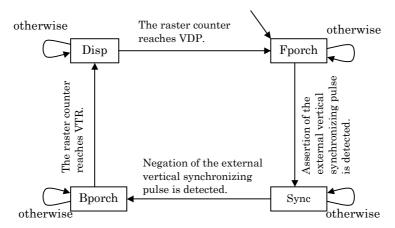

|   |                | PLAY FUNCTION                                                       |             |

|   | 7.2.1          | Screen Structure                                                    |             |

|   | 7.2.2          | Stacking                                                            |             |

|   | 7.2.2.1        | Overview                                                            |             |

|   | 7.2.2.1        | Stacking Mode                                                       |             |

|   | 7.2.2.2        | Blend Factor Layer                                                  |             |

|   | 7.2.2.3        | Control of Blend Factor Layer                                       |             |

|   | 7.2.2.4        | Display Parameter                                                   |             |

|   | 7.2.3<br>7.2.4 | Control of display position                                         |             |

|   |                | v · · · · ·                                                         |             |

|   |                | 'A FORMAT                                                           |             |

|   | 7.3.1          | Indirect Color (8 bits/pixel)                                       | •           |

|   | 7.3.2          | Direct Color (16 bits/pixel)                                        |             |

|   | 7.3.3          | Direct Color (24 bits/pixel)                                        |             |

|   | 7.3.4          | YCbCr Color (16 bits/pixel)                                         |             |

|   | 7.3.5          | Alpha Factor (8 bits/pixel)                                         |             |

|   | 7.3.6          | Layer Dependency                                                    |             |

|   |                | SOR                                                                 |             |

|   | 7.4.1          | Cursor Display Function                                             |             |

|   | 7.4.2          | Cursor Control                                                      |             |

|   |                | TROL OF DISPLAY SCAN                                                |             |

|   | 7.5.1          | Supported Display                                                   |             |

|   | 7.5.2          | Interlace Display                                                   |             |

|   |                | d Skip                                                              |             |

|   |                | ERNAL SYNCHRONIZATION                                               |             |

|   |                | IABLE PARAMETERS USED FOR CONVERSION FROM YCBCR TO RGB FOR L1 LAYER |             |

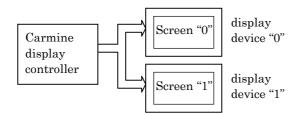

|   | 7.9 DUA        | L DISPLAY BY SINGLE DISPLAY CONTROLLER                              | 377         |

|   | 7.9.1          | Overview                                                            |             |

|   | 7.9.2          | Layer Destination Control                                           |             |

|   | 7.9.3          | Output Signal Control                                               |             |

|   | 7.9.4          | Sample Output Circuit                                               | <i>37</i> 9 |

|   | 7.9.5          | Display Clock and Timing                                            | 381         |

|   | 7.9.6          | Restrictions                                                        | 381         |

|   | 7.10 WR        | TEBACK                                                              | 382         |

|   | 7.10.1         | Overview                                                            | 382         |

|   | 7.10.2         | Source Selection                                                    | 382         |

|   | 7.10.3         | Image Area Definition                                               | 382         |

|   | 7.10.4         | Data Format                                                         | 383         |

|   | 7.10.5         | Field Selection                                                     |             |

|   | 7.10.6         | State Transition                                                    |             |

|   | 7.10.7         | Transfer Destination Selection                                      |             |

|   |                | ULTANEOUS LAYER DISPLAY RESTRICTIONS                                |             |

|   |                | ISTER                                                               |             |

|   | 7.12.1         | List of Registers                                                   |             |

|   | 7.12.2         | Common Control Register                                             |             |

|   | 7.12.3         | Writeback Register                                                  |             |

|   | 7.12.4         | Display Controller Register                                         |             |

|   |                | PLAY TIMING                                                         |             |

|   |                | =======================================                             | 170         |

|   | 7.13.1         | Noninterlace                            | 470 |

|---|----------------|-----------------------------------------|-----|

|   | 7.13.2         | Interlace Video                         |     |

|   | 7.13.3         | Composite Synchronization signal        | 472 |

| 8 | VIDEO          | CAPTURE                                 | 473 |

|   | 8.1 VII        | DEO CAPTURE FUNCTION                    | 473 |

|   | 8.1.1          | Input Data Format                       | 473 |

|   | 8.1.2          | Capture of Video Signal                 | 473 |

|   | 8.1.3          | Conversion to Non-interlace             | 473 |

|   | 8.2 SEL        | ECTION OF INPUT PORT                    | 474 |

|   | 8.3 VII        | DEO BUFFER                              | 476 |

|   | 8.3.1          | Data Format                             |     |

|   | 8.3.2          | Synchronization Control                 |     |

|   | 8.3.3          | Area Allocation                         |     |

|   | 8.3.4          | Window Display                          |     |

|   | 8.3.5          | Interlace Display                       |     |

|   |                | LLING                                   |     |

|   | 8.4.1          | Video Reduction Function                |     |

|   | 8.4.2          | Video Expansion Function                |     |

|   | 8.4.3          | Image Processing Flow                   |     |

|   | 8.5 INT 8.5.1  |                                         |     |

|   | 8.5.1<br>8.5.2 | Overview Interrupt Status               |     |

|   | 8.5.3          | Error Detection                         |     |

|   | 8.5. <i>4</i>  | Capture VSYNC interrupt                 |     |

|   |                | TERNAL VIDEO SIGNAL INPUT               |     |

|   | 8.6.1          | R.BT656YUV422 Input Format              |     |

|   | 8.6.1.1        | *                                       |     |

|   | 8.6.1.2        | -                                       |     |

|   | 8.6.1.3        |                                         |     |

|   | 8.6.1.4        |                                         |     |

|   | 8.6.1.5        |                                         |     |

|   | 8.6.1.6        |                                         |     |

|   | 8.6.1.7        |                                         |     |

|   | 8.6.2          | RGB Input Format                        | 495 |

|   | 8.6.2.1        | •                                       |     |

|   | 8.6.2.2        | Setting of capture range                | 495 |

|   | 8.6.2.3        | RGB Input Format                        | 497 |

|   | 8.6.3          | RGB Video Input Parameter Setting Chart | 500 |

|   | 8.7 REG        | GISTERS                                 | 501 |

|   | 8.7.1          | Register List                           | 501 |

|   | 8.7.2          | Video Capture Register                  | 504 |

| 9 | ELECT          | RICAL CHARACTERISTICS                   | 528 |

|   | 9.1 MA         | XIMUM RATING                            | 528 |

|   |                | COMMENDED OPERATING CONDITIONS          |     |

|   | 9.2.1          | 3.3 V Standard CMOS I/O                 |     |

|   | 9.2.2          | Graphics Memory I/O                     |     |

|   |                | CAUTIONS AT POWER ON                    |     |

|   | 9.3.1          | Recommended Power ON/OFF Sequence       |     |

|   | 9.3.2          | Power ON Reset                          |     |

|   | 9.3.3          | Reset at Normal Operation               |     |

|   |                | CHARACTERISTICS                         |     |

|   | 9.4.1          | 3.3 V Standard CMOS I/O                 |     |

|   | 9.4.2          | 3.3 V 66 MHz PCI I/O                    |     |

|   | 9.4.3          | Graphics Memory I/O                     |     |

|   | 9.4.4          | 1 <sup>2</sup> C Bus Fast Mode I/O      |     |

|   |                | TERNATE CURRENT (AC) CHARACTERISTICS    |     |

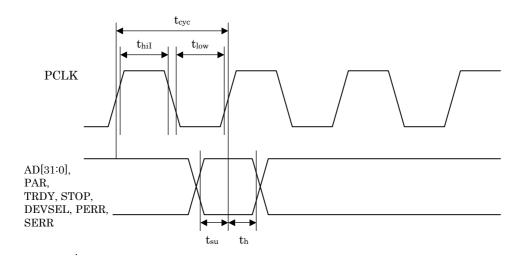

|   |                | PCI Interface                           | 546 |

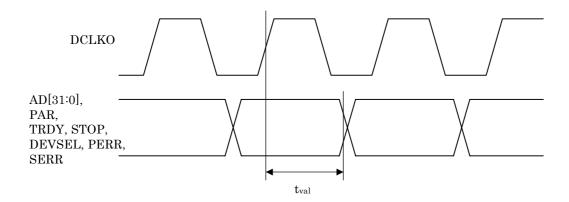

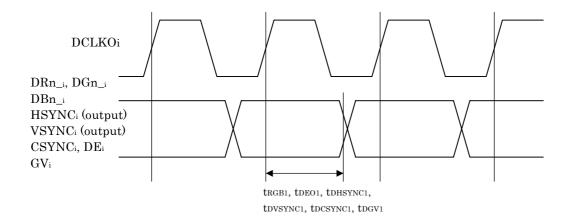

| 9.5.2 Display Interface                       | 547 |

|-----------------------------------------------|-----|

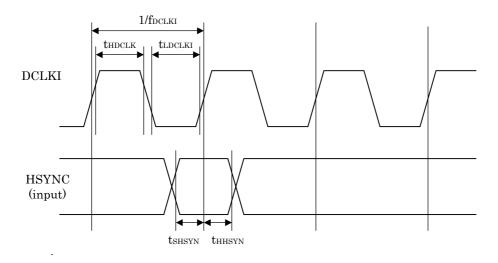

| 9.5.3 Video Capture Interface                 |     |

| 9.5.4 Graphics Memory Interface               |     |

| 9.5.5 I <sup>2</sup> C Interface              |     |

| 9.5.6 Clock Reset                             |     |

| 9.6 AC CHARACTERISTICS MEASUREMENT CONDITIONS | 555 |

| 9.7 TIMING DIAGRAM                            |     |

| 9.7.1 PLL Clock                               |     |

| 9.7.2 PCI Interface                           | 557 |

| 9.7.3 Display Interface                       |     |

| 9.7.4 Video Capture Interface                 |     |

| 9.7.5 Graphics Memory Interface               |     |

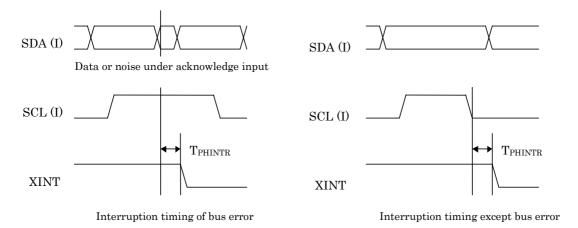

| 9.7.6 I <sup>2</sup> C Interface              |     |

# 1 Specification of Carmine Chip

#### 1.1 Overview

#### **Features**

#### Geometry engine

Carmine contains floating point operation pipelines dedicated to geometry processing for graphics processing, which allows 2D/3D graphics vertex processing including lighting at max 10M vertices/sec.

#### Rendering engine

Carmine contains a completely newly designed 2D/3D rendering engine. Carmine's multiple hardware for pixel processing improves performance of Fujitsu GDC controller Coral Series, and also supports hardware acceleration of OpenGL-ES.

#### Display controller

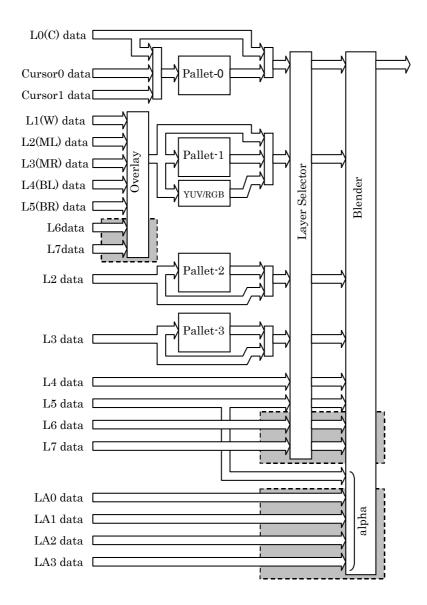

Carmine contains display controllers compatible with Fujitsu GDC controller Coral Series. The maximum resolution is  $1280 \times 1024$ , and the display controllers has two independent channels. Carmine has also two independent digital video output ports. Each digital video output port allows transparent processing, such as overlay display up to eight layers and alpha planes for four layers.

#### • Digital video capturing

Captures video images on television, etc., and displays them on the same screen as drawn images. Carmine captures video images from two independent channels.

#### CPU interface

Carmine is connected to a 32-bit PCI bus (Rev. 2.2) (the maximum operating frequency is 66 MHz).

#### • External memory interface

DDR SDRAM can be used. Selectable data bus width (64-bit/32-bit). The maximum data transfer frequency is 266 Mbps (clock frequency is 133 MHz). *Table 1.1.1* shows the available memory configuration.

Table 1.1.1 External Memory Configuration

| Memory type               | Data bus width | Number of memories used | Total capacity |  |

|---------------------------|----------------|-------------------------|----------------|--|

| DDR SDRAM 128 Mbits (x16) | 32 Bits        | 2                       | 32 Mbytes      |  |

| DDR SDRAM 256 Mbits (x16) | 32 Bits        | 2                       | 64 Mbytes      |  |

| DDR SDRAM 128 Mbits (x16) | 64 Bits        | 4                       | 64 Mbytes      |  |

| DDR SDRAM 256 Mbits (x16) | 64 Bits        | 4                       | 128 Mbytes     |  |

#### • Others

CMOS 90nm technology, 8-layer

TEBGA543 (Thermally Enhanced Ball Grid Array) package, θja =17°C/W (wind speed 0 mm)

Power supply voltage: 1.2 V (internal logic)/2.5 V (memory interface)/3.3 V (I/O)

Power consumption: 2.3 W

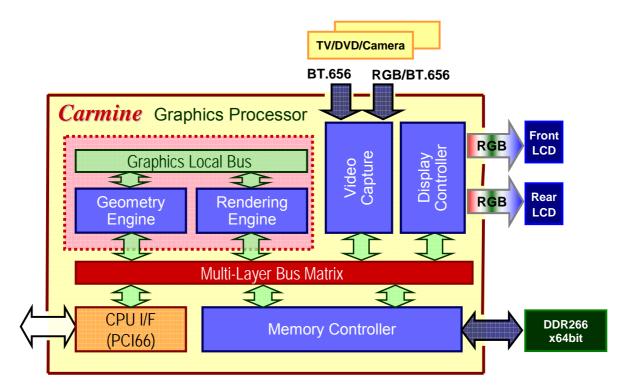

# 1.2 Entire Block Diagram

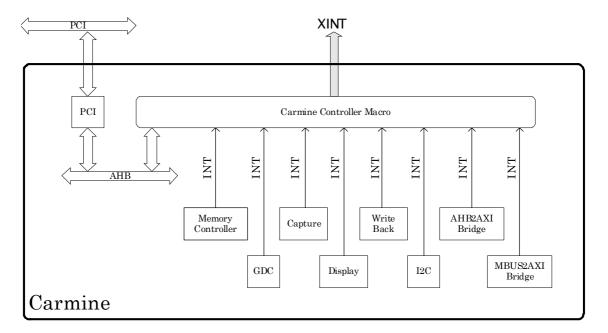

Fig. 1.1 shows the Carmine block diagram.

Fig. 1.1 Carmine Block Diagram

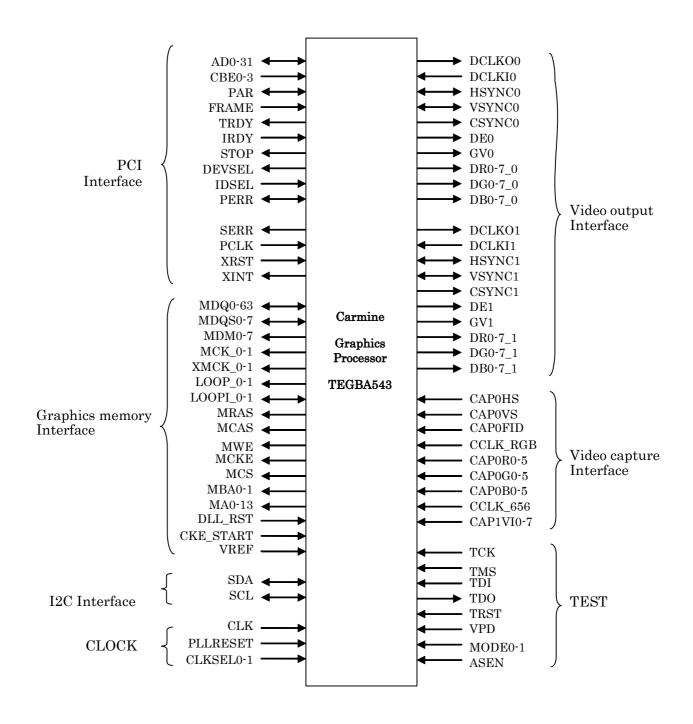

## 1.3 Signal

# 1.3.1 Signal Line

Fig. 1.2 Carmine Signal Line

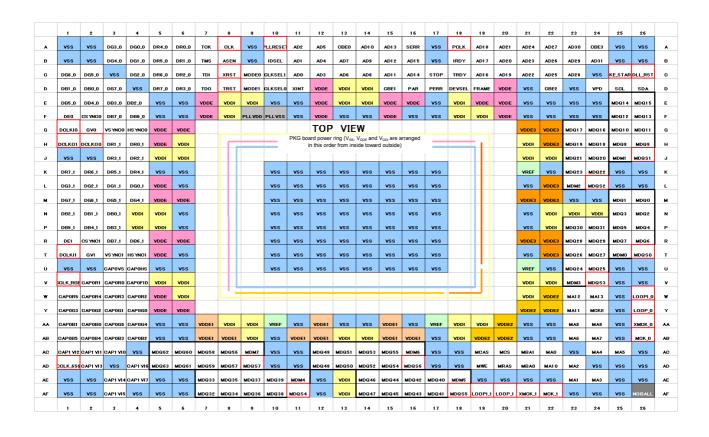

# 1.4 Pin Assignment

# 1.4.1 TEBGA543 Package Pin Assignment (TOP\_VIEW)

# 1.4.2 Package Pin Assignment Table

| JEDEC | Pin name | I/O    | JEDEC        | Pin name | I/O    | JEDEC      | Pin name | I/O    | JEDEC | Pin name      | I/O    |

|-------|----------|--------|--------------|----------|--------|------------|----------|--------|-------|---------------|--------|

| A1    | VSS      | -      | AF19         | LOOPI_1  | I/O    | A15        | AD13     | I/O    | AE8   | MDQ35         | I/O    |

| B1    | VSS      | -      | AF20         | LOOP_1   | Output | A14        | AD10     | I/O    | AE9   | MDQ37         | I/O    |

| C1    | DG6_0    | Output | AF21         | XMCK_1   | Output | A13        | CBE0     | Input  | AE10  | MDQ39         | I/O    |

| D1    | DB1_0    | Output | AF22         | MCK_1    | Output | A12        | AD5      | I/O    | AE11  | MDM4          | I/O    |

| E1    | DB5_0    | Output | AF23         | VSS      | -      | A11        | AD2      | I/O    | AE12  | VSS           | -      |

| F1    | DE0      | Output | AF24         | VSS      | -      | A10        | PLLRESET | Input  | AE13  | VDDI          | -      |

| G1    | DCLKI0   | Input  | AF25         | VSS      | -      | A9         | VSS      | -      | AE14  | MDQ46         | I/O    |

| H1    | DCLKO1   | Output | AF26         | NOBALL   | -      | A8         | CLK      | Input  | AE15  | MDQ44         | I/O    |

| J1    | VSS      | -      | AE26         | VSS      | -      | A7         | TCK      | Input  | AE16  | MDQ42         | I/O    |

| K1    | DR7_1    | Output | AD26         | VSS      | -      | A6         | DR0_0    | Output | AE17  | MDQ40         | I/O    |

| L1    | DG3_1    | Output | AC26         | VSS      | -      | A5         | DR4_0    | Output | AE18  | MDM5          | I/O    |

| M1    | DG7_1    | Output | AB26         | MCK_0    | Output | A4         | DG0_0    | Output | AE19  | VSS           | -      |

| N1    | DB2_1    | Output | AA26         | XMCK_0   | Output | A3         | DG3_0    | Output | AE20  | VSS           | -      |

| P1    | DB5_1    | Output | Y26          | LOOP_0   | Output | A2         | VSS      | -      | AE21  | VSS           | -      |

| R1    | DE1      | Output | W26          | LOOPI_0  | I/O    | B2         | VSS      | -      | AE22  | VSS           | -      |

| T1    | DCLKI1   | Input  | V26          | VSS      | -      | C2         | $DG5\_0$ | Output | AE23  | MA1           | Output |

| U1    | VSS      | -      | U26          | VSS      | -      | D2         | DB0_0    | Output | AE24  | MA3           | Output |

| V1    | CCLK_RGB | Input  | T26          | MDQS0    | I/O    | E2         | DB4_0    | Output | AE25  | VSS           | -      |

| W1    | CAP0R5   | Input  | R26          | MDQ6     | I/O    | F2         | CSYNC0   | Output | AD25  | VSS           | -      |

| Y1    | CAP0G3   | I/O    | P26          | MDQ4     | I/O    | G2         | GV0      | Output | AC25  | MA5           | Output |

| AA1   | CAP0B1   | I/O    | N26          | MDQ2     | I/O    | H2         | DCLKO0   | Output | AB25  | VSS           | -      |

| AB1   | CAP0B5   | I/O    | M26          | MDQ0     | I/O    | J2         | VSS      | -      | AA25  | VSS           | -      |

| AC1   | CAP1VI2  | Input  | L26          | VSS      | -      | K2         | DR6_1    | Output | Y25   | VSS           | -      |

| AD1   | CCLK_656 | Input  | K26          | VSS      | -      | L2         | DG2_1    | Output | W25   | VSS           | -      |

| AE1   | VSS      | -      | J26          | MDQS1    | I/O    | M2         | DG6_1    | Output | V25   | VSS           | -      |

| AF1   | VSS      | -      | H26          | MDQ9     | I/O    | N2         | DB1_1    | Output | U25   | VSS           | -      |

| AF2   | VSS      | -      | G26          | MDQ11    | I/O    | P2         | DB4_1    | Output | T25   | MDM0          | I/O    |

|       | CAP1VI5  | I/O    | F26          | MDQ13    | I/O    | R2         | CSYNC1   | Output |       | MDQ7          | I/O    |

|       | VSS      | -      | E26          | MDQ15    | I/O    | T2         | GV1      | Output |       | MDQ5          | I/O    |

|       | VSS      | -      | D26          | SDA      | I/O    | U2         | VSS      | -      |       | MDQ3          | I/O    |

|       | VSS      | -      | C26          | DLL_RST  | Input  | V2         | CAP0R1   | Input  |       | , ,           | I/O    |

|       | MDQ32    | I/O    | B26          | VSS      | -      | W2         | CAP0R4   | Input  | L25   | VSS           | -      |

|       | MDQ34    | I/O    | A26          | VSS      | -      | Y2         | CAP0G2   | Input  | K25   | VSS           | -      |

|       | MDQ36    | I/O    | A25          | VSS      | -      | AA2        | CAP0B0   | I/O    | J25   | MDM1          | I/O    |

|       | MDQ38    |        | A24          | CBE3     |        | AB2        |          | I/O    |       | · ·           | I/O    |

|       | MDQS4    | I/O    | A23          | AD30     | I/O    | AC2        | CAP1VI1  | Input  |       |               | I/O    |

|       | VSS      | -      | A22          | AD27     | I/O    | AD2        | CAP1VI3  | Input  |       | •             | I/O    |

|       | VDDI     | -      | A21          | AD24     | I/O    | AE2        | VSS      | -      |       |               | I/O    |

| AF14  | MDQ47    | I/O    | A20          | AD21     | I/O    | AE3        | CAP1VI4  | I/O    | D25   |               | I/O    |

| AF15  | MDQ45    | I/O    | A19          | AD18     | I/O    | AE4        | CAP1VI7  | Immust | C25   | CKE_<br>START | Immust |

|       | MDQ43    | I/O    | A19<br>A18   | PCLK     | Input  | AE5        | VSS      | Input  |       | VSS           | Input  |

|       | MDQ41    | I/O    | A17          | VSS      | -      | AE6        | VSS      | -      | B24   |               | I/O    |

|       | MDQS5    | I/O    | A16          | SERR     | Output | AE7        | MDQ33    | I/O    | B23   |               | I/O    |

|       | AD26     | I/O    | AD9          | MDQS7    | I/O    | C13        | AD6      | I/O    | AC22  | MA0           | Output |

| -     | AD23     | I/O    | AD10         | VSS      | -      | C13        |          | I/O    | AC23  | VSS           | -      |

| -     | AD20     | I/O    | AD10<br>AD11 | VSS      | -      | C12<br>C11 |          | I/O    | AB23  | MA6           | Output |

| -     | AD17     | I/O    | AD12         | MDQ48    | I/O    | C10        | CLKSEL1  | Input  |       | MA8           | Output |

|       | IRDY     | Input  | AD13         | MDQ50    | I/O    | C9         |          | Input  |       | MA11          | Output |

|       | VSS      | -      | AD14         |          | I/O    | C8         | XRST     | Input  |       |               | Output |

|       | AD15     | I/O    | AD15         |          | I/O    | C7         | TDI      | Input  |       |               | I/O    |

|       | AD12     | I/O    | AD16         | <b>†</b> | I/O    | C6         | DR2_0    | Output |       |               | I/O    |

| -     | AD9      | I/O    | AD17         | VSS      | -      | C5         | DR6_0    | Output |       | •             | I/O    |

| B13        | AD7            | I/O             | AD18         | VSS   | L        | C4              | DG2_0          | Output   | R23        | MDQ28          | I/O      |

|------------|----------------|-----------------|--------------|-------|----------|-----------------|----------------|----------|------------|----------------|----------|

| B13        | AD4            | I/O             | AD19         | MWE   | Output   | D4              | VSS            | - Output | P23        | MDQ30          | I/O      |

| B12<br>B11 | AD4<br>AD1     | I/O             | AD19<br>AD20 | MRAS  | Output   | E4              | DB2_0          | Output   | N23        | VDDI           | -        |

| B10        | IDSEL          | Input           | AD21         | MBA0  | Output   | F4              | DB2_0<br>DB6_0 | Output   | M23        | VSS            | -        |

| B9         | VSS            | -               | AD22         | MA10  | Output   | G4              | HSYNC0         | I/O      | L23        | MDM2           | I/O      |

| B8         | ASEN           | Input           | AD23         | MA2   | Output   | H4              | DR0_1          | Output   | K23        | MDQ23          | I/O      |

| во<br>В7   | TMS            |                 | AD23<br>AD24 | VSS   | - Output | J4              | DR0_1<br>DR2_1 | Output   | J23        | MDQ23          | I/O      |

| B6         | DR1_0          | Input<br>Output | AC24         | MA4   | Output   | K4              | DR2_1<br>DR4_1 | Output   | H23        | MDQ19          | I/O      |

| во<br>В5   | DR1_0<br>DR5_0 | Output          | AB24         | MA7   | Output   | L4              | DG0_1          | Output   | G23        | MDQ19<br>MDQ17 | I/O      |

| Бэ<br>В4   | DG1_0          |                 | AA24         | MA9   | Output   | $\frac{L4}{M4}$ | DG0_1<br>DG4_1 | +        | F23        | VSS            | 1/0      |

|            | DG1_0<br>DG4_0 | Output          |              | MCKE  |          | N4              | VDDI           | Output   | -          | VSS            |          |

| B3<br>C3   | VSS            | Output          | Y24<br>W24   | MA13  | Output   | P4              | VDDI           |          | E23<br>D23 | VSS            |          |

|            |                | 0 4 4           |              |       | Output   | 41              |                | -        | -          |                | T .      |

| D3         | DG7_0          | Output          | V24          | MDQS3 | I/O      | R4              | DB6_1          | Output   | D22        | CBE2           | Input    |

| E3         | DB3_0          | Output          | U24          | MDQ25 | I/O      | T4              | HSYNC1         | I/O      | D21        | VSS            | -        |

| F3         | DB7_0          | Output          | T24          | MDQ27 | I/O      | U4              | CAPOHS         | I/O      | D20        | VDDE           | T .      |

| G3         | VSYNC0         | I/O             | R24          | MDQ29 | I/O      | V4              | CAP0FID        | I/O      | D19        | FRAME          | Input    |

| H3         | DR1_1          | Output          | P24          | MDQ31 | I/O      | W4              | CAP0R2         | Input    | D18        | DEVSEL         | Output   |

| J3         | DR3_1          | Output          | N24          | VDDI  | -        | Y4              | CAP0G0         | Input    | D17        | PERR           | Output   |

| K3         | DR5_1          | Output          | M24          | VSS   | -        | AA4             | CAP0G4         | I/O      | D16        | PAR            | I/O      |

| L3         | DG1_1          | Output          | L24          | MDQS2 | I/O      | AB4             | CAP0B2         | I/O      | D15        | CBE1           | Input    |

| М3         | DG5_1          | Output          | K24          | MDQ22 | I/O      | AC4             | VSS            | -        | D14        | VDDI           | -        |

| N3         | DB0_1          | Output          | J24          | MDQ20 | I/O      | AC5             | MDQ62          | I/O      | D13        | VDDI           | -        |

| P3         | DB3_1          | Output          | H24          | MDQ18 | I/O      | AC6             | MDQ60          | I/O      | D12        | VDDE           | -        |

| R3         | DB7_1          | Output          | G24          | MDQ16 | I/O      | AC7             | MDQ58          | I/O      | D11        | XINT           | Output   |

| Т3         | VSYNC1         | I/O             | F24          | VSS   | -        | AC8             | MDQ56          | I/O      | D10        | CLKSEL0        | Input    |

| U3         | CAP0VS         | I/O             | E24          | VSS   | -        | AC9             | MDM7           | I/O      | D9         | MODE1          | Input    |

| V3         | CAP0R0         | Input           | D24          | VPD   | Input    | AC10            | VSS            | -        | D8         | TRST           | Input    |

| W3         | CAP0R3         | Input           | C24          | VSS   | -        | AC11            | VSS            | -        | D7         | TDO            | Output   |

| Y3         | CAP0G1         | Input           | C23          | AD28  | I/O      | AC12            | MDQ49          | I/O      | D6         | DR3_0          | Output   |

| AA3        | CAP0G5         | I/O             | C22          | AD25  | I/O      | AC13            | MDQ51          | I/O      | D5         | DR7_0          | Output   |

| AB3        | CAP0B3         | I/O             | C21          | AD22  | I/O      | AC14            | MDQ53          | I/O      | E5         | VSS            | -        |

| AC3        | CAP1VI0        | I/O             | C20          | AD19  | I/O      | AC15            | MDQ55          | I/O      | F5         | VSS            | -        |

| AD3        | VSS            | -               | C19          | AD16  | I/O      | AC16            | MDM6           | I/O      | G5         | VDDE           | -        |

| AD4        | CAP1VI6        | I/O             | C18          | TRDY  | Output   | AC17            | VSS            | -        | Н5         | VDDE           | -        |

| AD5        | MDQ63          | I/O             | C17          | STOP  | Output   | AC18            | VSS            | -        | J5         | VDDI           | -        |

| AD6        | MDQ61          | I/O             | C16          | AD14  | I/O      | AC19            | MCAS           | Output   | K5         | VSS            | -        |

| AD7        | MDQ59          | I/O             | C15          | AD11  | I/O      | AC20            | MCS            | Output   | L5         | VDDE           | -        |

| AD8        | MDQ57          | I/O             | C14          | AD8   | I/O      | AC21            | MBA1           | Output   | M5         | VDDE           | -        |

| N5         | VDDI           | -               | E18          | VDDI  | -        | U21             | VREF           | Input    | K17        | VSS            | -        |

| P5         | VDDI           | -               | E17          | VSS   | -        | T21             | VSS            | -        | K16        | VSS            | -        |

| R5         | VDDE           | -               | E16          | VDDE  | -        | R21             | VDDE3          | -        | K15        | VSS            | -        |

| Т5         | VDDE           | -               | E15          | VDDE  | -        | P21             | VSS            | -        | K14        | VSS            | -        |

| U5         | VSS            | -               | E14          | VDDI  | -        | N21             | VSS            | -        | K13        | VSS            | -        |

| V5         | VDDI           | -               | E13          | VDDI  | -        | M21             | VDDE3          | -        | K12        | VSS            | -        |

| W5         | VDDE           | -               | E12          | VDDE  | -        | L21             | VSS            | -        | K11        | VSS            | -        |

| Y5         | VDDE           | -               | E11          | VSS   | -        | K21             | VREF           | Input    | L11        | VSS            | -        |

| AA5        | VSS            | -               | E10          | VSS   | -        | J21             | VDDI           | -        | M11        | VSS            | -        |

| AB5        | VSS            | _               | E9           | VDDI  | _        | H21             | VDDI           | _        | N11        | VSS            | _        |

| AB6        | VSS            |                 | E8           | VDDI  |          | G21             | VDDE3          |          | P11        | VSS            | -        |

| AB6<br>AB7 | VDDE1          |                 | E7           | VDDI  | -        | F21             | VSS            | -        | R11        | VSS            | -        |

| AB8        | VDDE1<br>VDDE1 | _               | E6           | VSS   | _        | F21<br>F20      | VDDE           | -        | T11        | VSS            | _        |

|            | _              |                 |              | _     |          | 11              | _              |          | 11         |                |          |

| AB9        | VDDI           |                 | F6           | VSS   | -        | F19             | VDDI           | <u> </u> | T12        | VSS            | <u> </u> |

| AB10       | VSS            | -               | G6           | VDDE  | -        | F18             | VDDI           | -        | T13        | VSS            | -        |

| AB11       | VDDE1          | -               | H6           | VDDI  | -        | F17             | VSS            | +        | T14        | VSS            | -        |

| AB12       | VDDE1          | -               | J6           | VDDI  | -        | F16             | VSS            | -        | T15        | VSS            | -        |

| AB13       | VDDI           | -               | K6           | VSS   | -        | F15             | VDDE           | -        | T16        | VSS            | -        |

| AB14       | VDDI           | -               | L6           | VSS   | -        | F14             | VSS            | -        | R16        | VSS            | -        |

| AB15 | VDDE1 | M6     | VDDE  | -     | F13 | VSS    | - | P16 | VSS | - |

|------|-------|--------|-------|-------|-----|--------|---|-----|-----|---|

| AB16 | VDDE1 | - N6   | VSS   | -     | F12 | VDDE   | - | N16 | VSS | - |

| AB17 | VSS   | - P6   | VSS   | -     | F11 | VSS    | - | M16 | VSS | - |

| AB18 | VDDI  | - R6   | VDDE  | -     | F10 | PLLVSS | - | L16 | VSS | - |

| AB19 | VDDE2 | - Т6   | VSS   | -     | F9  | PLLVDD | - | L15 | VSS | - |

| AB20 | VDDE2 | - U6   | VSS   | -     | F8  | VDDI   | - | L14 | VSS | - |

| AB21 | VSS   | - V6   | VDDI  | -     | F7  | VDDE   | - | L13 | VSS | - |

| AB22 | VSS   | - W6   | VDDI  | -     | K10 | VSS    | - | L12 | VSS | - |

| AA22 | VSS   | - Y6   | VDDE  | -     | L10 | VSS    | - | M12 | VSS | - |

| Y22  | VDDE2 | - AA6  | VSS   | -     | M10 | VSS    | - | N12 | VSS | - |

| W22  | VDDE2 | - AA7  | VDDE1 | -     | N10 | VSS    | - | P12 | VSS | - |

| V22  | VDDI  | - AA8  | VDDI  | -     | P10 | VSS    | - | R12 | VSS | - |

| U22  | VSS   | - AA9  | VDDI  | -     | R10 | VSS    | - | R13 | VSS | - |

| T22  | VDDE3 | - AA10 | VREF  | Input | T10 | VSS    | - | R14 | VSS | - |

| R22  | VDDE3 | - AA11 | VSS   | -     | U10 | VSS    | - | R15 | VSS | - |

| P22  | VDDI  | - AA12 | VDDE1 | -     | U11 | VSS    | - | P15 | VSS | - |

| N22  | VDDI  | - AA13 | VSS   | -     | U12 | VSS    | - | N15 | VSS | - |

| M22  | VDDE3 | - AA14 | VSS   | -     | U13 | VSS    | - | M15 | VSS | - |

| L22  | VDDE3 | - AA15 | VDDE1 | -     | U14 | VSS    | - | M14 | VSS | - |

| K22  | VSS   | - AA16 | VSS   | -     | U15 | VSS    | - | M13 | VSS | - |

| J22  | VDDI  | - AA17 | VREF  | Input | U16 | VSS    | - | N13 | VSS | - |

| H22  | VDDE3 | - AA18 | VDDI  | -     | U17 | VSS    | - | P13 | VSS | - |

| G22  | VDDE3 | - AA19 | VDDI  | -     | T17 | VSS    | - | P14 | VSS | - |

| F22  | VSS   | - AA20 | VDDE2 | -     | R17 | VSS    | - | N14 | VSS | - |

| E22  | VSS   | - AA21 | VSS   | -     | P17 | VSS    | - |     |     |   |

| E21  | VSS   | Y21    | VDDE2 | -     | N17 | VSS    | - |     |     |   |

| E20  | VDDE  | - W21  | VDDI  | -     | M17 | VSS    | - |     |     |   |

| E19  | VDDE  | - V21  | VDDI  | -     | L17 | VSS    | - |     |     |   |

#### Notes:

$V_{SS}/PLLV_{SS}$  : Ground

$V_{DDE}$  : 3.3 V power supply

$V_{DDE1}, V_{DDE2}, V_{DDE3}$  : 2.5 V/3.3V power supply for SDRAM

$V_{DDI}$  : 1.2 V power supply

PLLV<sub>DD</sub> : PLL power supply (1.2 V)

V<sub>REF</sub> : 1/2 V<sub>DDE</sub> (1-3) for SSTL2 mode; 0 V for LVCMOS mode

- Fujitsu recommends PLLVDD be separated on the board.

- Connect a bypass capacitor of good high frequency characteristics between power pin and ground pin.

Place the capacitor as close as possible to the pins.

- The following pins are described as "I/O" in the I/O column. They are used as TEST output pins for Fujitsu shipping test of LSI, but used as input pins during normal operation:

CAP0G5 to 3, CAP0B5 to 0, CAP0VS, CAP0HS, CAP0FID, CAP1VI0, CAP1VI6 to 4

# 1.5 Pin Function

# 1.5.1 PCI Interface

Table 1.5.1 PCI Interface Pins

| Pin name | I/O    | Function                                              |  |  |

|----------|--------|-------------------------------------------------------|--|--|

| AD0-31   | In/Out | PCI address/data bus signal                           |  |  |

| CBE0-3   | Input  | PCI bus command/byte enable signal                    |  |  |

| FRAME    | Input  | PCI frame signal                                      |  |  |

| IRDY     | Input  | PCI initiator ready signal                            |  |  |

| TRDY     | Output | PCI target ready signal                               |  |  |

| DEVSEL   | Output | PCI device selection signal                           |  |  |

| IDSEL    | Input  | PCI configuration device select signal                |  |  |

| STOP     | Output | PCI stop signal                                       |  |  |

| PAR      | In/Out | PCI parity signal                                     |  |  |

| PERR     | Output | PCI parity error signal                               |  |  |

| SERR     | Output | PCI system error signal                               |  |  |

| XINT     | Output | Interrupt output signal                               |  |  |

|          |        | Note: This signal is output asynchronously with PCLK. |  |  |

| PCLK     | Input  | PCI clock signal                                      |  |  |

| XRST     | Input  | System reset input signal                             |  |  |

# 1.5.2 Video Output Interface

Table 1.5.2 Video Output Interface Pins

| Pin name | I/O    | Function                                                                   |  |  |

|----------|--------|----------------------------------------------------------------------------|--|--|

| DCLK00   | Output | Display dot clock output signal                                            |  |  |

| DCLKI0   | Input  | Dot clock input signal                                                     |  |  |

| HSYNC0   | In/Out | Horizontal synchronization signal output                                   |  |  |

|          |        | For external synchronization mode, horizontal synchronization signal input |  |  |

| VSYNC0   | In/Out | Vertical synchronization signal output                                     |  |  |

|          |        | For external synchronization mode, vertical synchronization signal input   |  |  |

| CSYNC0   | Output | Composite synchronization output signal                                    |  |  |

| DE0      | Output | Display valid period output signal                                         |  |  |

| GV0      | Output | Graphics/video switching output signal                                     |  |  |

| DR7-0_0  | Output | Digital image output signal (red)                                          |  |  |

| DG7-0_0  | Output | Digital image output signal (green)                                        |  |  |

| DB7-0_0  | Output | Digital image output signal (blue)                                         |  |  |

| DCLKO1   | Output | Display dot clock output signal                                            |  |  |

| DCLKI1   | Input  | Dot clock input signal                                                     |  |  |

| HSYNC1   | In/Out | Horizontal synchronization signal output                                   |  |  |

|          |        | For external synchronization mode, horizontal synchronization signal input |  |  |

| VSYNC1   | In/Out | Vertical synchronization signal output                                     |  |  |

|          |        | For external synchronization mode, vertical synchronization signal input   |  |  |

| CSYNC1   | Output | Composite synchronization output signal                                    |  |  |

| DE1      | Output | Display valid period output signal                                         |  |  |

| GV1      | Output | Graphics/video switching output signal                                     |  |  |

| DR7-0_1  | Output | Digital image output signal (red)                                          |  |  |

| DG7-0_1  | Output | Digital image output signal (green)                                        |  |  |

| DB7-0_1  | Output | Digital image output signal (blue)                                         |  |  |

#### (Remarks)

- Adding an external circuit generates composite video signals.

- External video can be displayed synchronously with this LSI. Select the mode synchronous with DCLKI signal or the mode synchronous with the set dot clock, as with normal display.

- HSYNC and VSYNC signals enter input immediately after reset. Pull up these signal pins outside the LSI.

- GV signal is used to switch between graphics and external video when performing chroma-key. The GV signal outputs Low level when "video" is selected.

- Correspondence between 16-bit/pixel color mode and 8-bit/pixel color mode, and 8-bit digital RGB output pin is as follows.

## (A) For 16-bit/pixel color mode:

| RGB data in graphics memory<br>R:G:B = 5:5:5 | Digital RGB output<br>R:G:B = 8:8:8   |  |

|----------------------------------------------|---------------------------------------|--|

| 00000b                                       | 00000000b                             |  |

| 00001b to 11111b                             | "111b" is added to lower 3 bits       |  |

|                                              | Calculation formula: $X \times 8 + 7$ |  |

#### (B) For 8-bit/pixel color mode:

| RGB data in color palette | Digital RGB output                    |  |

|---------------------------|---------------------------------------|--|

| R:G:B = 6:6:6             | R:G:B = 8:8:8                         |  |

| 000000Ь                   | 00000000b                             |  |

| 000001b to 111111b        | "11b" is added to lower 2 bits        |  |

|                           | Calculation formula: $X \times 4 + 3$ |  |

In video capture YCbCr mode, when images are converted to RGB, they are converted to a full 8 bits of precision and then displayed.

Table 1.5.3 Processing When No Pins Used

| Pin name | Pin state |              | Pin processing | Remarks                                                                           |  |

|----------|-----------|--------------|----------------|-----------------------------------------------------------------------------------|--|

|          | At reset  | At operation |                |                                                                                   |  |

| DCLK00   | Output    | Output       | OPEN           |                                                                                   |  |

| DCLKI0   | Input     | Input        | VDDE/GND       | Pull up the pin to VDDE or pull down the pin to GND, via a high resistance.       |  |

| HSYNC0   | Input     | In/Out       | VDDE/GND       | Pull up the pin to VDDE or pull down the pin to GND, via a high resistor.         |  |

| VSYNC0   | Input     | In/Out       | VDDE/GND       | Pull up the pin to VDDE or pull down<br>the pin to GND, via a high<br>resistance. |  |

| CSYNC0   | Output    | Output       | OPEN           |                                                                                   |  |

| DE0      | Output    | Output       | OPEN           |                                                                                   |  |

| GV0      | Output    | Output       | OPEN           |                                                                                   |  |

| DR7-0_0  | Output    | Output       | OPEN           |                                                                                   |  |

| DG7-0_0  | Output    | Output       | OPEN           |                                                                                   |  |

| DB7-0_0  | Output    | Output       | OPEN           |                                                                                   |  |

| DCLKO1   | Output    | Output       | OPEN           |                                                                                   |  |

| DCLKI1   | Input     | Input        | VDDE/GND       | Pull up the pin to VDDE or pull down the pin to GND, via a high resistance.       |  |

| HSYNC1   | Input     | In/Out       | VDDE/GND       | Pull up the pin to VDDE or pull down the pin to GND, via a high resistance.       |  |

| VSYNC1   | Input     | In/Out       | VDDE/GND       | Pull up the pin to VDDE or pull down the pin to GND, via a high resistance.       |  |

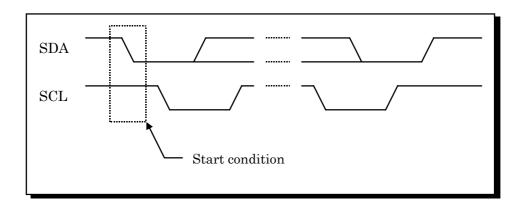

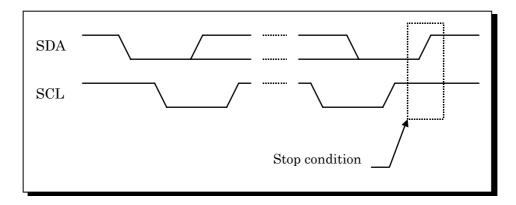

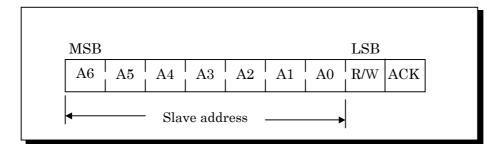

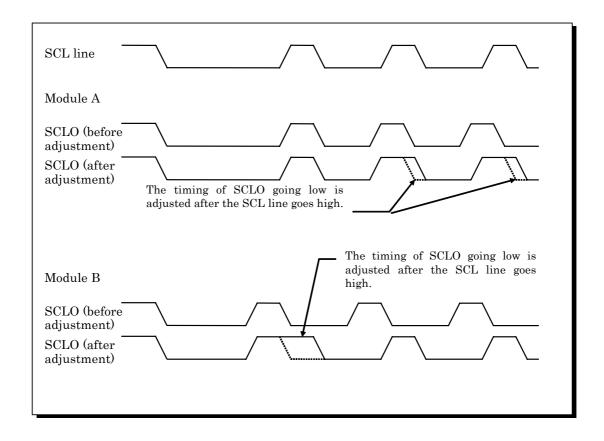

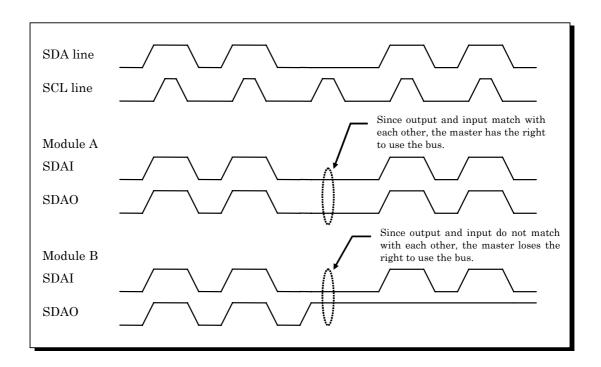

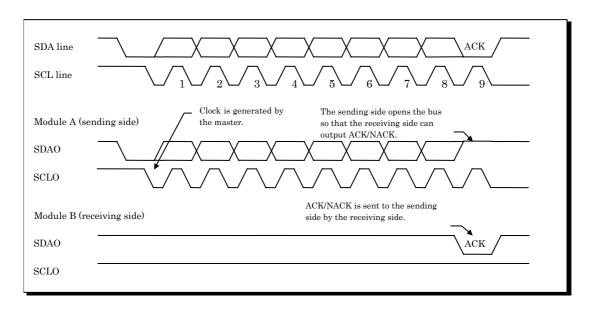

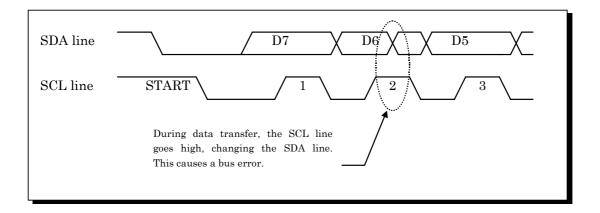

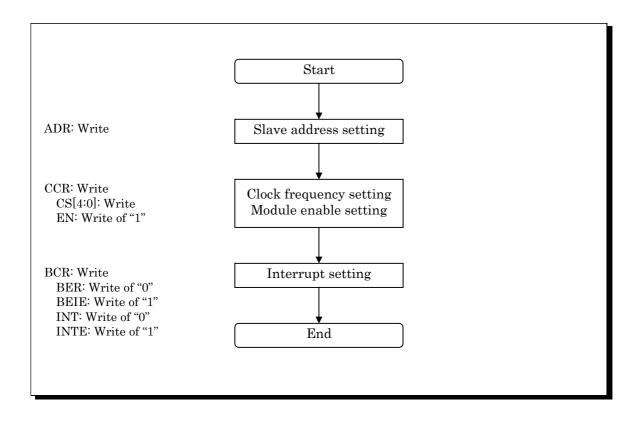

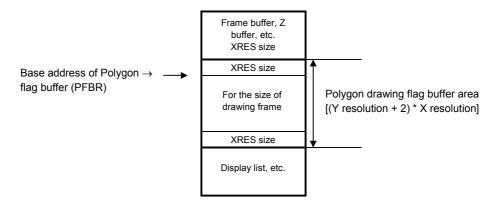

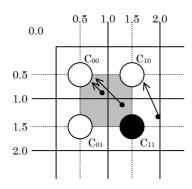

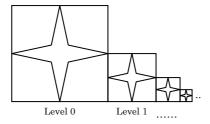

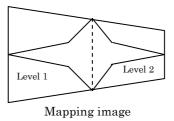

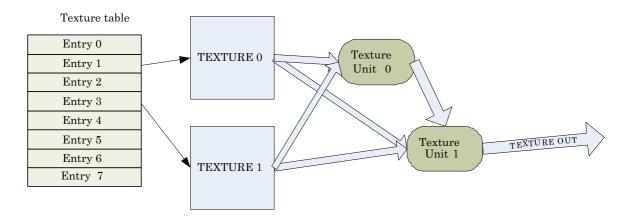

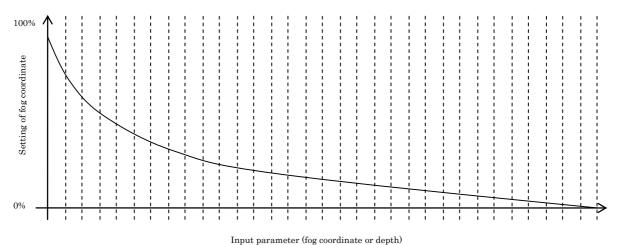

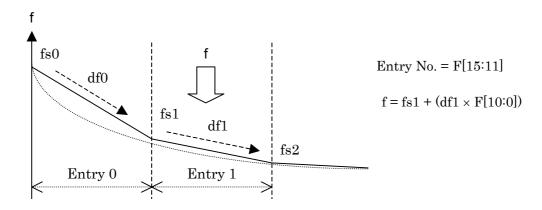

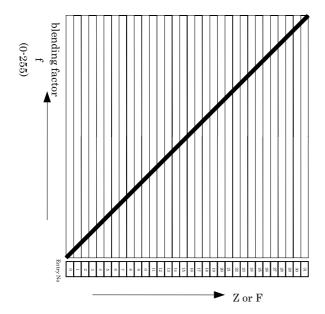

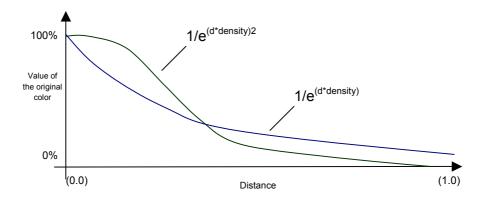

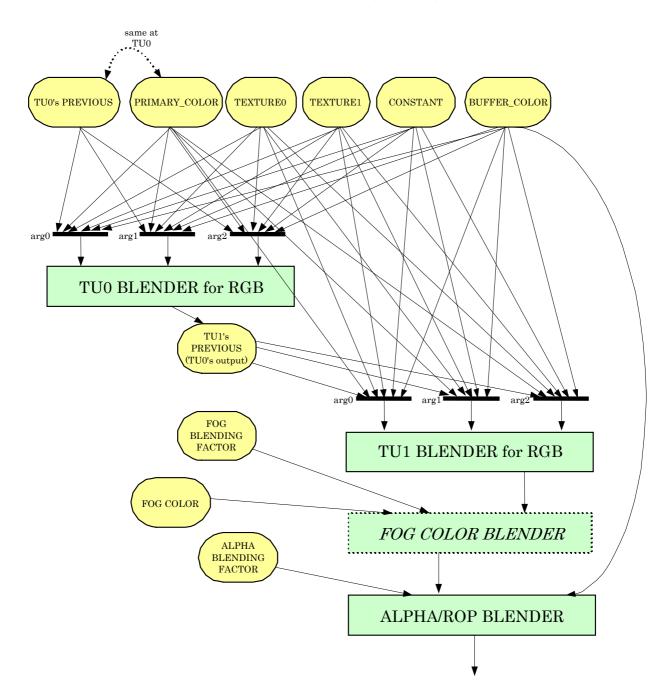

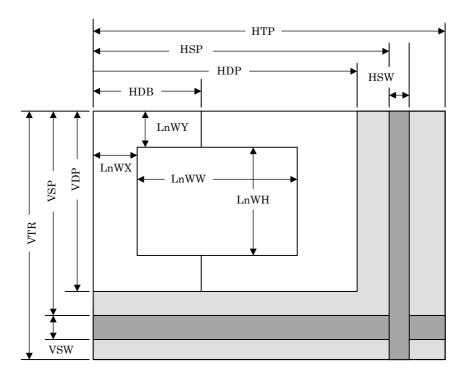

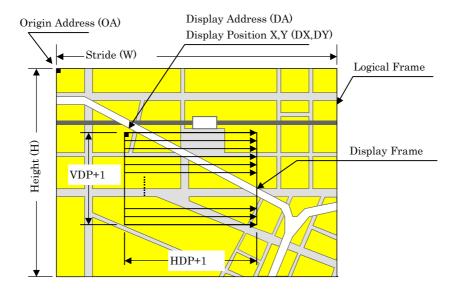

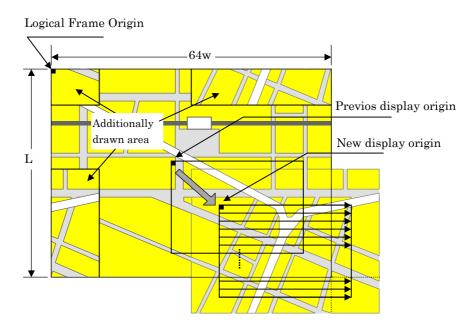

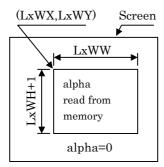

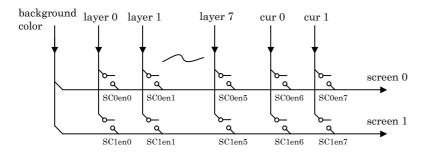

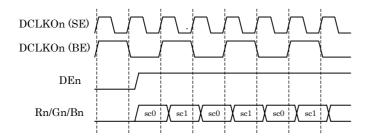

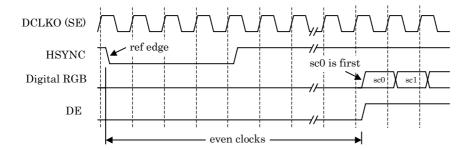

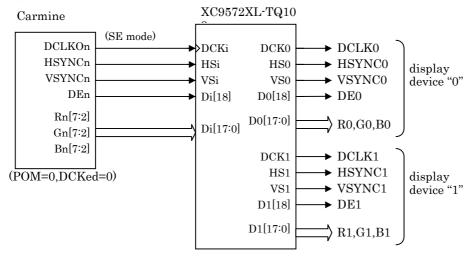

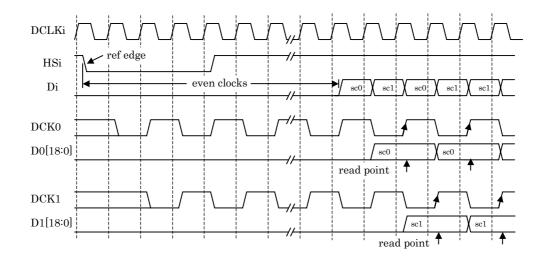

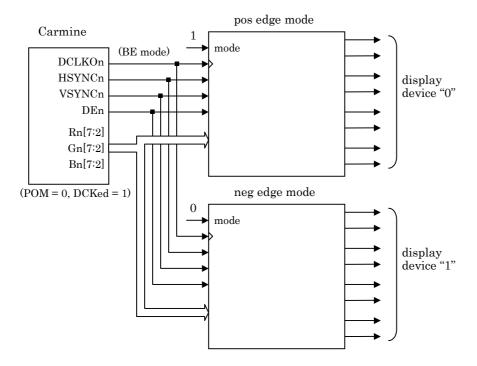

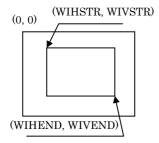

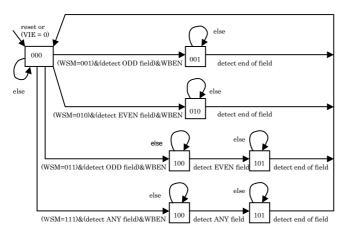

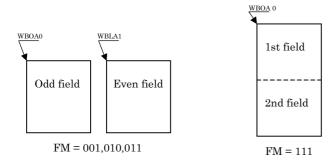

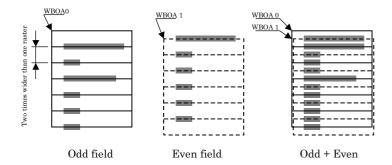

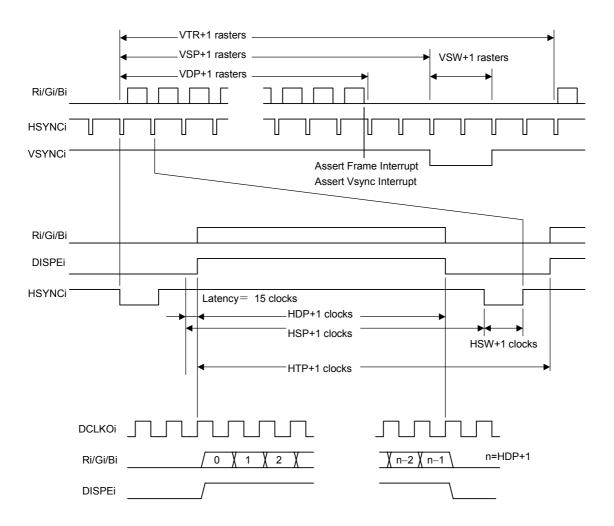

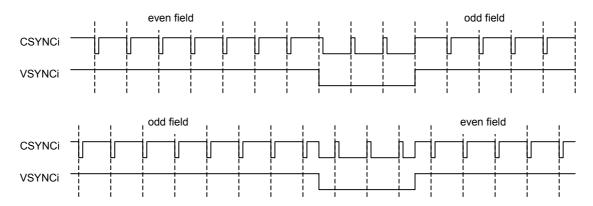

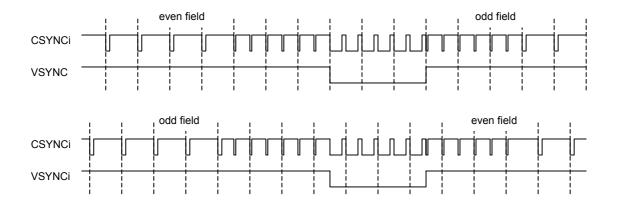

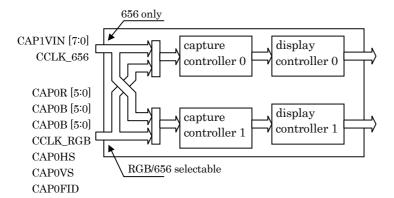

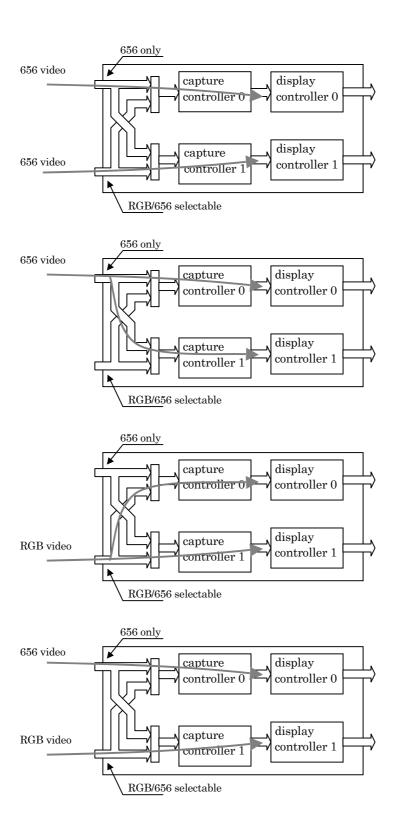

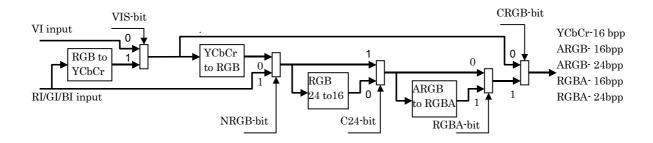

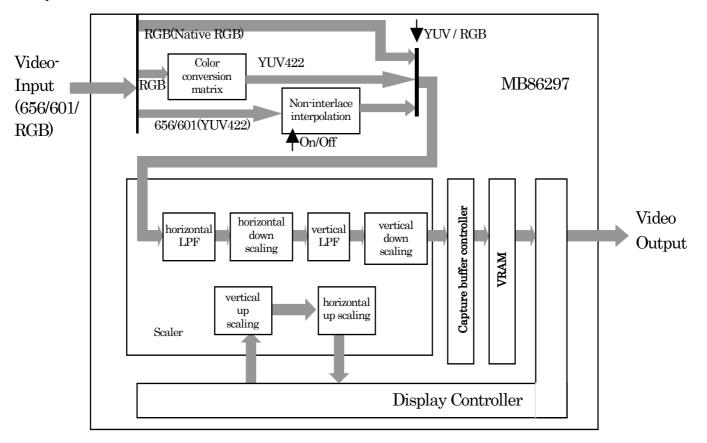

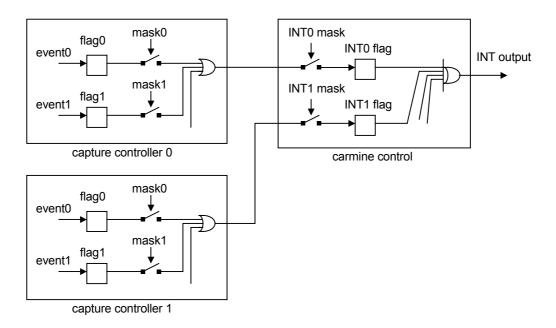

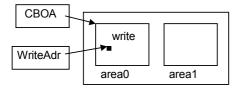

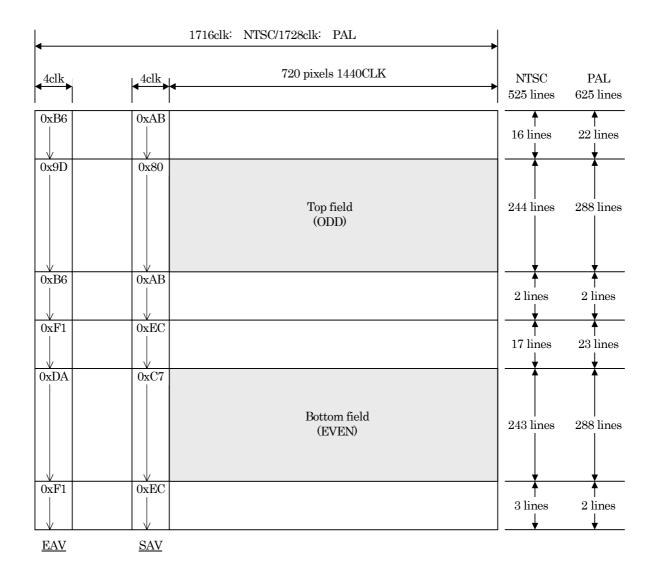

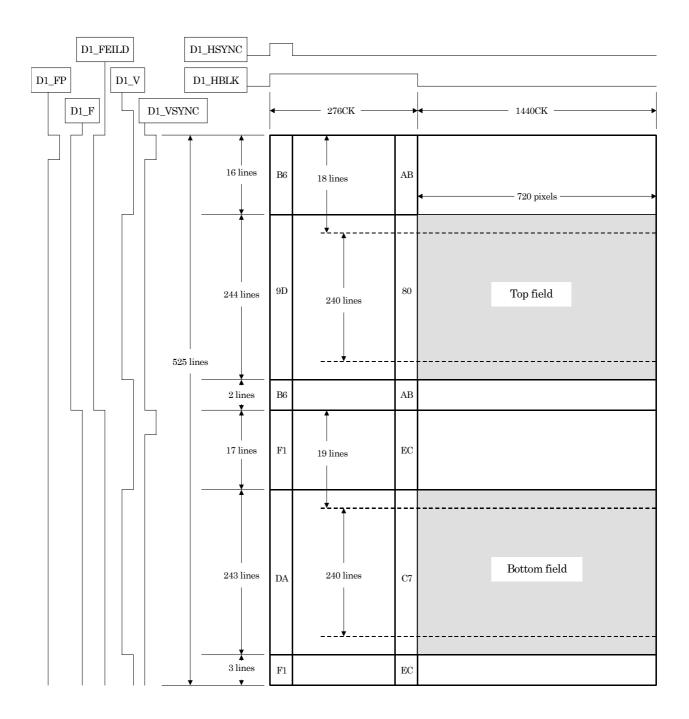

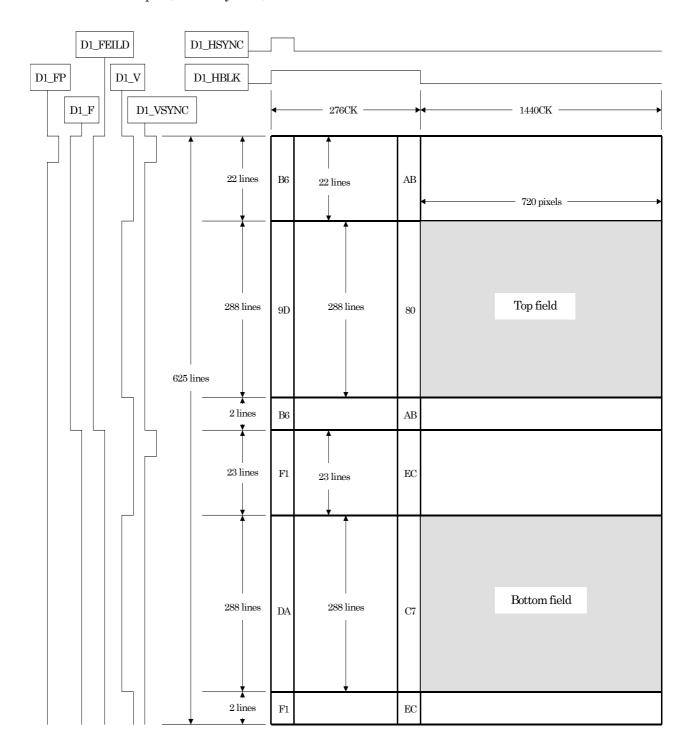

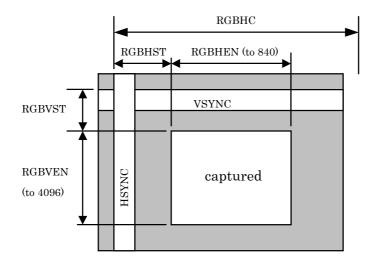

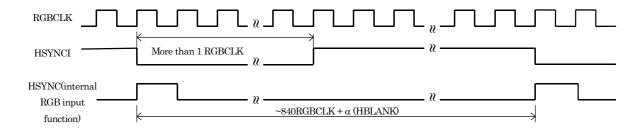

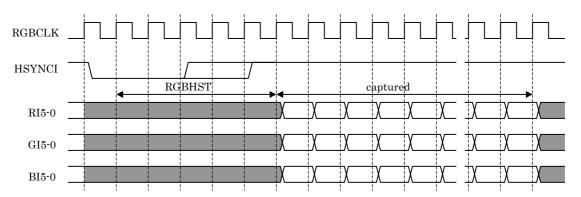

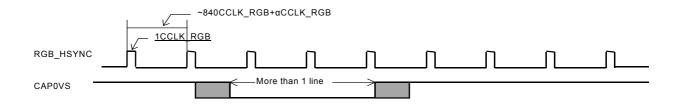

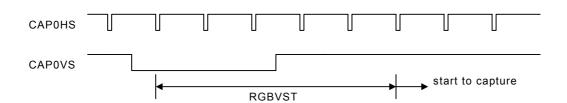

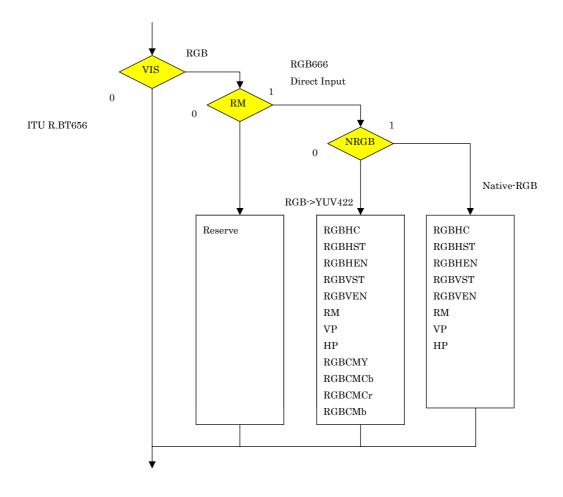

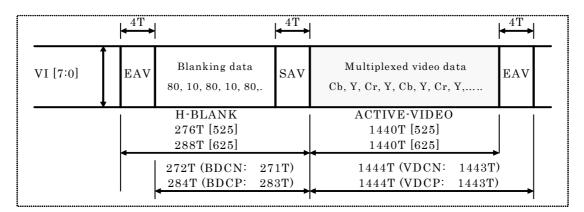

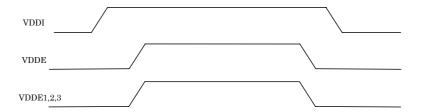

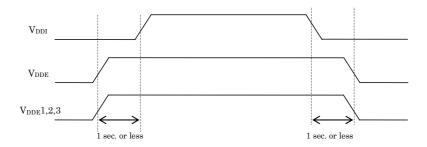

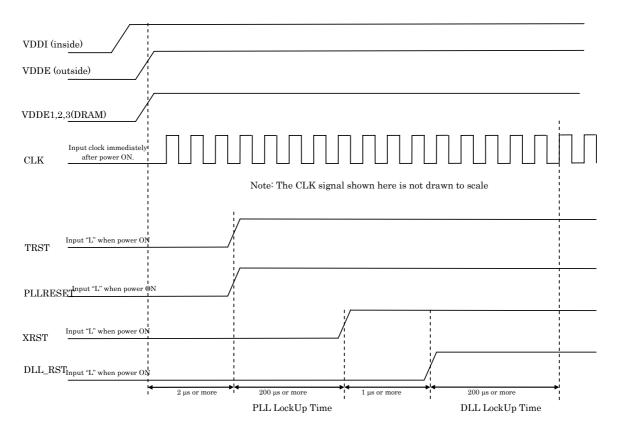

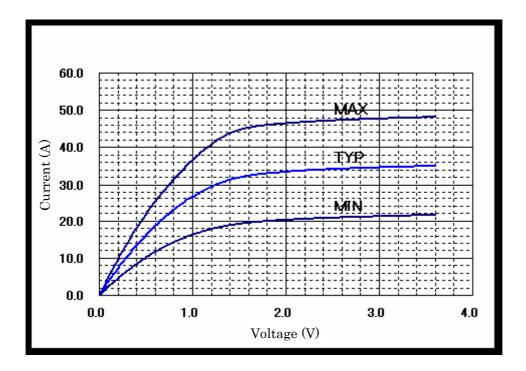

| CSYNC1   | Output    | Output       | OPEN           |                                                                                   |  |