## MAX71314/MAX71315

# **Single-Phase Electricity Meter SOC**

## **General Description**

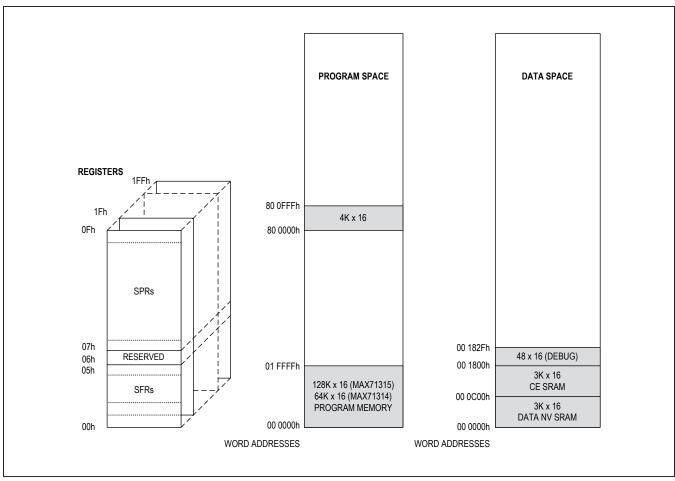

The MAX71314/MAX71315 integrate dual 32-bit processors for demanding single-phase metering applications with 256kB flash (MAX71315) or 128kB flash (MAX71314), 12kB RAM, and a single-cycle 32 x 32 + 64 multiplier. The user processor (MPU) is a 32-bit MAXQ®30 core. The metrology compute engine (CE) is a 32-bit processor dedicated to computing the metering parameters from voltage and current samples.

### **Features and Benefits**

- Four Independent Metrology Channels

- 0.1% Accuracy Over 5000:1 Current Range with Integrated Metrology ADCs

- Two Remote ADC Interfaces

- Support Current Transformers, Rogowski Coils, and Shunts

- · Four Pulse Outputs from the CE

- Digital Temperature Compensation for Metrology

- 45Hz to 65Hz Line Frequency Range with the Same Calibration

- Phase Compensation (±10°)

- 256kB Flash, 12kB SRAM (MAX71315)

- 128kB Flash, 12kB SRAM (MAX71314)

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/MAX71314.related">www.maximintegrated.com/MAX71314.related</a>.

- Single-Cycle 32 x 32 + 64 Multiply-Accumulate Unit

- Low-Power 5ksps ADC for Environmental Monitoring

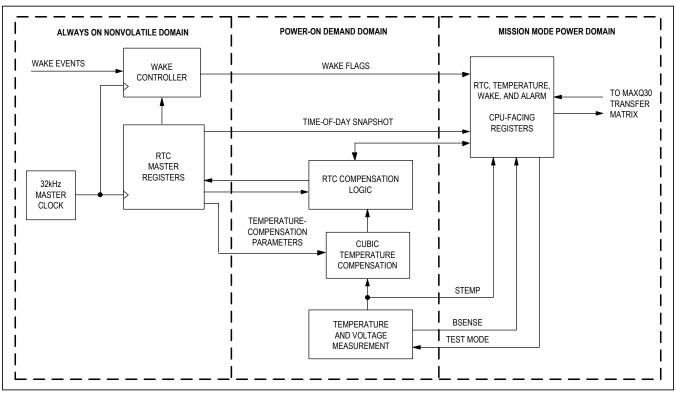

- RTC with Temperature Compensation

- On-Chip Digital Temperature Sensor

- LCD Controller Supporting Up to Eight Common Planes

- Two PWM Relay Control Channels with Programmable Frequency, Duty Cycle, and Ramp Time

- Two Touch Switch Inputs

- 12.5mA Typical Consumption at 3.3V and 10MHz in Active Mode

- 1.75µA Sleep Mode

- SPI (Master and Slave), Master I<sup>2</sup>C, 4 x UARTs

- Two Smart Card Ports

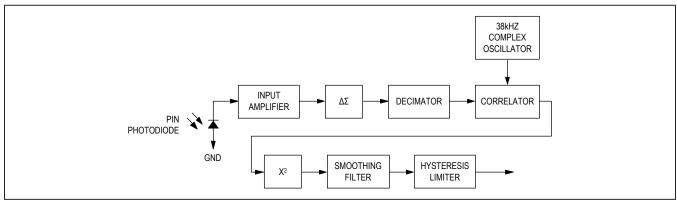

- 38kHz IR Encoder/Decoder

- Up to 10 MIPS (at 10MHz)

- 100-Pin LQFP

Ordering Information appears at end of data sheet.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

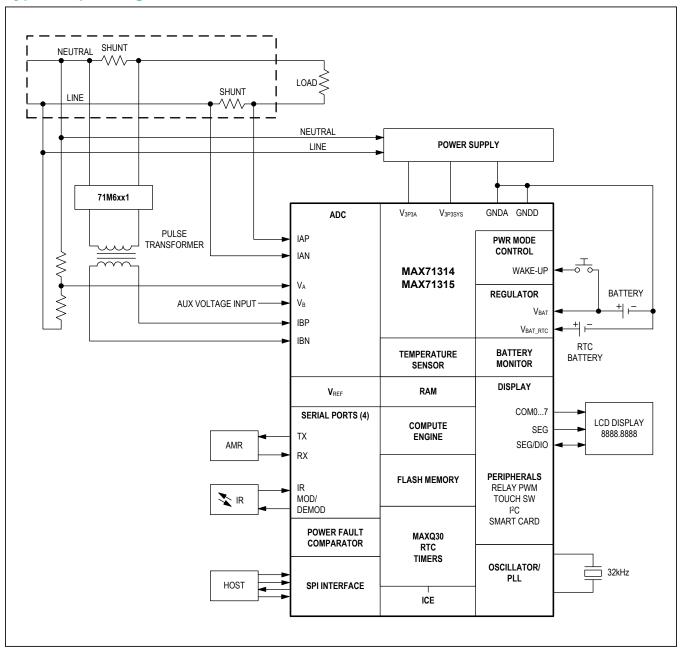

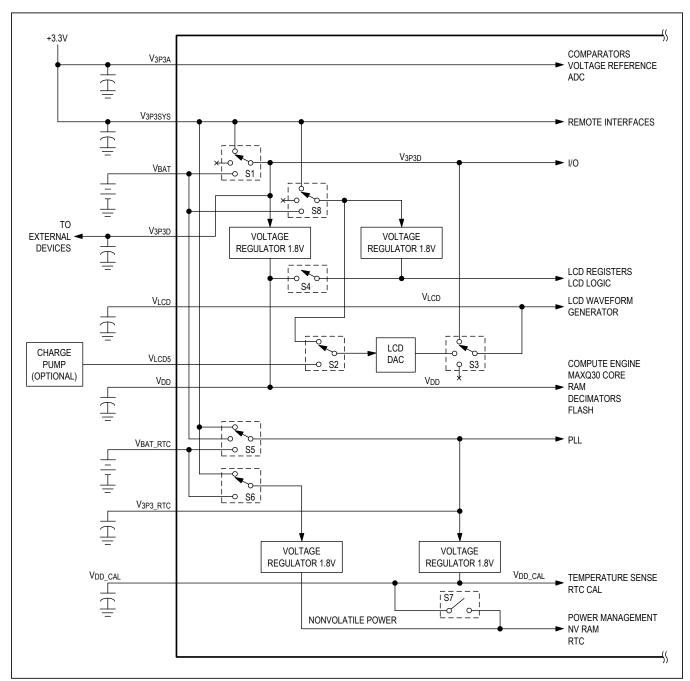

## **Typical Operating Circuit**

## **Absolute Maximum Ratings**

| Voltage, Current Supplies, and Grou | ınd Pins:                                 |

|-------------------------------------|-------------------------------------------|

| V <sub>3P3SYS</sub>                 | 0.5 to +3.6V                              |

| Crystal Pins:                       |                                           |

| XIN, XOUT(-10mA t                   | to +10mA), (-0.5V to +3.0V)               |

| Digital Pins:                       |                                           |

| Inputs (MSN/BRN Mode) (-10m.        | A to +10mA), (-0.5V to +6V)               |

| Inputs (SLP Mode)                   | (-10mA to +10mA),                         |

|                                     | $(-0.5V \text{ to } V_{3P3SYS} + 0.5V)$   |

| Outputs                             | (-8mA to +8mA),                           |

| ·                                   | $(-0.5V \text{ to } (V_{3P3SYS} + 0.5V))$ |

| Temperature and ESD Stress                   |         |

|----------------------------------------------|---------|

| Operating Junction Temperature (peak, 100ms) | +140°C  |

| Operating Junction Temperature (continuous)  | +125°C  |

| Storage Temperature Range45°C to             | +165°C  |

| ESD Stress on All Pins±4                     | kV, HBM |

| Lead Temperature (soldering, 10s)            | +300°C  |

| Soldering Temperature (reflow)               | +250°C  |

|                                              |         |

## Package Thermal Characteristics (Note 1)

**LQFP**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....47.88°C/W

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......10.90°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

$(V_{3P3SYS} = V_{3P3A} = 3.0V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                      | SYMBOL               | CONDITIONS                                                                                                                                                        | MIN  | TYP  | MAX  | UNITS      |

|--------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|

| POWER SUPPLY                   |                      |                                                                                                                                                                   |      |      |      |            |

| Supply Voltage                 | V <sub>3P3SYS</sub>  |                                                                                                                                                                   | 3.0  |      | 3.6  | V          |

| Supply Voltage, Backup Battery | $V_{BAT}$            |                                                                                                                                                                   | 2.5  |      | 3.8  | V          |

| Supply Voltage, RTC Battery    | V <sub>BAT_RTC</sub> |                                                                                                                                                                   | 2.0  |      | 3.8  | V          |

| Supply Current                 | I <sub>DD1</sub>     | (Note 3)                                                                                                                                                          |      | 12.5 | 20.0 | mA         |

| Supply Current                 | I <sub>DD2</sub>     | (Note 4)                                                                                                                                                          |      | 11.0 | 17.0 | mA         |

| Dynamic Current                |                      | V <sub>3P3SYS</sub> = V <sub>3P3A</sub> = 3.3V, metrology<br>enabled, ADC operating full speed,<br>(I <sub>CPUCLK=10MHz</sub> - I <sub>CPUCLK=1.25MHz</sub> )/4.3 |      | 356  |      | μΑ/<br>MHz |

|                                |                      | MSN mode                                                                                                                                                          | -100 |      | +600 | nA         |

| V <sub>BAT</sub> Current       | $I_{VBAT}$           | BRN mode                                                                                                                                                          |      | 8.5  | 16.0 | mA         |

|                                |                      | SLP mode                                                                                                                                                          |      | 2    | 360  | nA         |

## **Electrical Characteristics (continued)**

( $V_{3P3SYS} = V_{3P3A} = 3.0V$  to 3.6V,  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL                | CONDITIONS                                                                               | MIN                 | TYP    | MAX   | UNITS |

|--------------------------------------|-----------------------|------------------------------------------------------------------------------------------|---------------------|--------|-------|-------|

|                                      |                       | MSN mode, TEMP_PWR = 1                                                                   |                     | ±100   |       | nA    |

| V <sub>BAT_RTC</sub> Current         | I <sub>VBAT_RTC</sub> | BRN mode, TEMP_PWR = 1                                                                   |                     | 1      |       | μA    |

|                                      |                       | SLP mode                                                                                 |                     | 1.75   | 36.00 | μA    |

| CRYSTAL OSCILLATOR                   |                       |                                                                                          |                     |        |       |       |

| RTC Oscillator Frequency             | f <sub>RTC</sub>      |                                                                                          |                     | 32.768 |       | kHz   |

| Peak Output Source Current           | IXOUT                 |                                                                                          | 0.4                 |        | 3.5   | μA    |

| Maximum Output Voltage               |                       |                                                                                          |                     |        | 1.5   | V     |

| Maximum Crystal Power                |                       |                                                                                          |                     |        | 1     | μW    |

| Frequency Variation with Voltage     |                       | T <sub>A</sub> = +25°C, V <sub>3P3SYS</sub> = 0V,<br>V <sub>BAT_RTC</sub> = 2.0V to 3.8V |                     | 0.86   |       | ppm   |

| LOGIC LEVELS                         |                       |                                                                                          |                     |        |       |       |

| Digital High-Level Input Voltage     | V <sub>IH</sub>       |                                                                                          | +2.0                |        |       | V     |

| Digital Low-Level Input Voltage      | V <sub>IL</sub>       |                                                                                          |                     |        | +0.6  | V     |

| Input Leakage Current                |                       |                                                                                          | -1.3                |        | +1.3  | μA    |

| Input Pullup Current, RSTN           |                       | V <sub>IN</sub> = 0V                                                                     | 5                   |        | 160   | μA    |

| Input Pulldown Current,<br>JTAG_E    |                       | V <sub>IN</sub> = V <sub>3P3SYS</sub>                                                    | 30                  |        | 160   | μA    |

| Digital High-Level Output<br>Voltage | V <sub>OH</sub>       | I <sub>LOAD</sub> = 5mA                                                                  | V <sub>3P3D</sub> - | - 0.4  |       | V     |

| Digital Low-Level Output             | \/ - ·                | I <sub>LOAD</sub> = -1mA                                                                 |                     |        | 0.4   | V     |

| Voltage                              | VOL                   | I <sub>LOAD</sub> = -5mA                                                                 |                     |        | 0.85  | V     |

| BATTERY MONITOR                      |                       |                                                                                          | ,                   |        |       |       |

| Measurement Error                    |                       | $V_{BAT}$ = 2.0V to 3.8V, sensing either $V_{BAT}$ or $V_{BAT}$ _RTC                     |                     |        | 4     | %     |

## **Electrical Characteristics (continued)**

( $V_{3P3SYS} = V_{3P3A} = 3.0V$  to 3.6V,  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                           | SYMBOL           | CONDITIONS                                         | MIN   | TYP      | MAX   | UNITS      |  |

|-----------------------------------------------------|------------------|----------------------------------------------------|-------|----------|-------|------------|--|

| TEMPERATURE MONITOR                                 | •                |                                                    |       |          |       |            |  |

| Temperature Error                                   |                  | T <sub>A</sub> = +22°C                             |       | ±3.6     |       | °C         |  |

| Relative Temperature Error                          |                  | -40°C < T < +85°C, 3.0V < V <sub>3P3A</sub> < 3.6V | -1.75 |          | +1.75 | °C         |  |

| LCD                                                 |                  | l                                                  | 1     |          |       |            |  |

| V <sub>LCD</sub> Current                            |                  | V <sub>LCD</sub> = 3.3V                            |       |          | 4     | μA         |  |

| V <sub>REF</sub>                                    | •                |                                                    | •     |          |       |            |  |

| Nominal Reference Voltage                           | V <sub>REF</sub> | T <sub>A</sub> = +22°C                             | 1.226 | 1.228    | 1.230 | V          |  |

| Variation with Power Supply                         |                  | V <sub>3P3A</sub> = 3.0V to 3.6V                   | -1.5  |          | +1.5  | mV/V       |  |

| Deviation from Predicted Variation with Temperature |                  |                                                    | -40   |          | +40   | ppm/°C     |  |

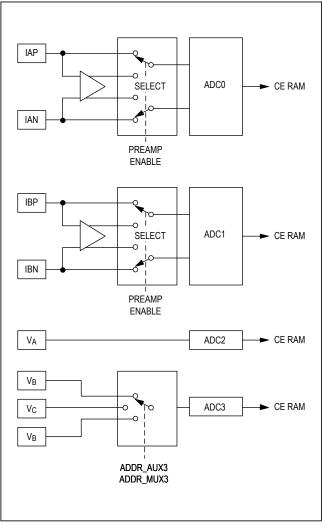

| ADC                                                 | '                |                                                    |       |          |       | '          |  |

|                                                     |                  | Preamp off                                         | -250  |          | +250  |            |  |

| Usable Input Range                                  |                  | Preamp gain = 4                                    | -26.5 |          | +26.5 | mV<br>peak |  |

| Osable input reange                                 |                  | Preamp gain = 8                                    | -13   |          | +13   |            |  |

|                                                     |                  | Preamp gain = 16                                   | -6.5  |          | +6.5  |            |  |

|                                                     |                  | f <sub>IN</sub> = 65Hz, preamp off                 | 140   |          | 450   |            |  |

| lanut lana danaa                                    |                  | f <sub>IN</sub> = 65Hz, preamp gain = 4            | 2.5   |          | 10.0  | kΩ         |  |

| Input Impedance                                     |                  | f <sub>IN</sub> = 65Hz, preamp gain = 8            | 2.5   |          | 10.0  | - K12      |  |

|                                                     |                  | f <sub>IN</sub> = 65Hz, preamp gain = 16           | 2.5   |          | 10.0  | 0.0        |  |

| LSB Size                                            |                  | FIR_LEN = 15                                       |       | 97       |       | nV/LSB     |  |

| Digital Full Scale                                  |                  | FIR_LEN = 15                                       |       | ±3375000 | )     | LSB        |  |

| Input Offset Voltage                                |                  |                                                    | -10   |          | +10   | mV         |  |

| THD, Voltage Channel                                |                  |                                                    |       | -85      |       | dB         |  |

## **Electrical Characteristics (continued)**

$(V_{3P3SYS} = V_{3P3A} = 3.0V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                 | SYMBOL | CONDITIONS                              | MIN  | TYP   | MAX  | UNITS      |

|-------------------------------------------|--------|-----------------------------------------|------|-------|------|------------|

| THD Current Channel                       |        | No preamp                               |      | -87   |      | dB         |

| THD, Current Channel                      |        | Preamp gain = 8                         |      | -85   |      | dB         |

|                                           |        | Preamp gain = 4                         | 3.9  | 4.0   | 4.1  |            |

| Current Channel Preamp Gain               |        | Preamp gain = 8                         | 7.8  | 8.0   | 8.2  | V/V        |

|                                           |        | Preamp gain = 16                        | 15.6 | 16.0  | 16.4 |            |

| Gain Variation with Supply Voltage        |        |                                         | -40  |       | +40  | ppm/%      |

| Gain Variation with Temperature           |        | (Note 5)                                | -55  |       | +55  | ppm<br>/°C |

| Current Channel Phase Shift               |        | +25°C, V <sub>3P3A</sub> = 3.0V to 3.6V |      | 6     |      | m°         |

| Phase Shift Variation with Supply         |        | (Note 5)                                | -20  |       | +20  | m°/V       |

| Phase Shift Variation with<br>Temperature |        | (Note 5)                                | -0.1 |       | +0.1 | m°/°C      |

| INTERNAL OSCILLATOR                       |        |                                         |      |       |      |            |

| Nominal Frequency                         |        |                                         |      | 24    |      | MHz        |

| Base Accuracy                             |        |                                         | -2   |       | +2   | %          |

| Frequency Variation with Supply           |        |                                         |      | -7.21 |      | kHz/V      |

- Note 2: Limits are 100% production tested at  $T_A = +22^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.

- Note 3: Supply current is the combined current into V<sub>3P3SYS</sub> and V<sub>3P3A</sub>; part is out of reset, no port activity, no flash writes, measured at V<sub>3P3SYS</sub> =V3P3A =3.3V, executing from flash, CPUCLK = 10MHz, metrology enabled, with ADC operating full speed.

- Note 4: Supply current is the combined current into V<sub>3P3SYS</sub> and V<sub>3P3A</sub>; part is out of reset, no port activity, no flash writes, measured at V<sub>3P3SYS</sub> = V<sub>3P3A</sub> = 3.3V, executing from flash, CPUCLK = 10MHz, metrology enabled, with ADC operating half speed.

- Note 5: Guaranteed by design, not production tested.

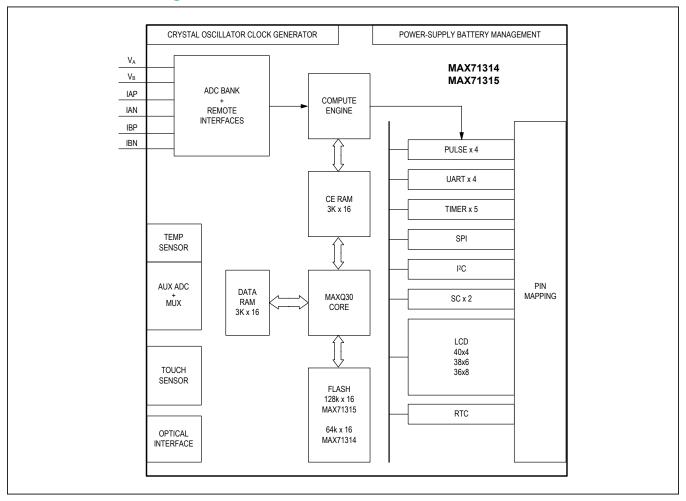

# **Functional Block Diagram**

**Table 1. Recommended External Components**

| NAME  | FROM                | то   | FUNCTION                                                                                                                                                 | VALUE       | UNITS |

|-------|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| C2    | V <sub>3P3D</sub>   | GNDD | Bypass capacitor for 3.3V output                                                                                                                         | 0.1 ± 20%   | μF    |

| CSYS  | V <sub>3P3SYS</sub> | GNDD | Bypass capacitor for V <sub>3P3SYS</sub>                                                                                                                 | ≥ 1.0 ± 30% | μF    |

| CVDD  | $V_{DD}$            | GNDD | Bypass capacitor for V <sub>DD</sub>                                                                                                                     | 0.1 ± 20%   | μF    |

| CVLCD | V <sub>LCD</sub>    | GNDD | Bypass capacitor for V <sub>LCD</sub> pin (when charge pump is used)                                                                                     | ≥ 0.1 ± 20% | μF    |

| XTAL  | XIN                 | XOUT | 32.768kHz tuning-fork crystal, electrically similar to:<br>ECS .327-12.5-17X,<br>Vishay XT26T, or<br>Suntsu SCP6-32.768kHz TR (load capacitance 12.5pF). | 32.768      | kHz   |

| CXS   | XIN                 | GNDA | Load capacitor values for crystal depends on crystal specifications                                                                                      | 22 ± 10%    | pF    |

| CXL   | XOUT                | GNDA | and board parasitics. Nominal values are based on 4pF board capacitance and include an allowance for chip capacitance.                                   | 22 ± 10%    | pF    |

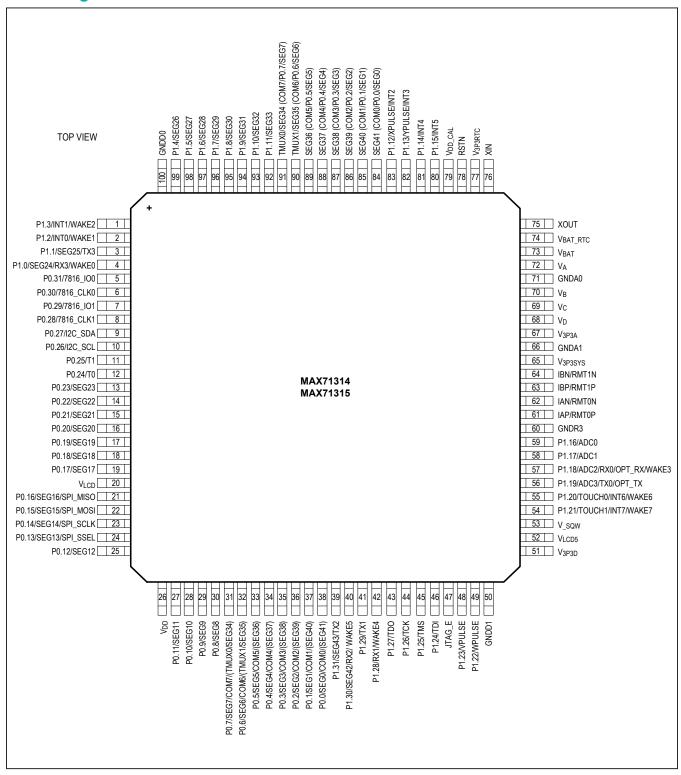

## **Pin Configuration**

# **Pin Description (Sorted by Pin Number)**

| PIN | NAME                 | FUNCTION                                                                    | PRIORITY                                                                |

|-----|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1   | P1.3/INT1/WAKE2      | GPIO Port 1 Bit 3; External Interrupt 1;<br>CPU Wake Input 2                | Dedicated GPIO bit; interrupt and wake functions independently enabled. |

| 2   | P1.2/INT0/WAKE1      | GPIO Port 1 Bit 2; External Interrupt 0; CPU Wake Input 1                   | Dedicated GPIO bit; interrupt and wake functions independently enabled. |

| 3   | P1.1/SEG25/TX3       | GPIO Port 1 Bit 1; LCD Segment 25;<br>UART 3 Transmit Data                  | LCD<br>GPIO<br>UART                                                     |

| 4   | P1.0/SEG24/RX3/WAKE0 | GPIO Port 1 Bit 0; LCD Segment 24;<br>UART 3 Receive Data; CPU Wake Input 0 | LCD<br>GPIO, UART receive                                               |

| 5   | P0.31/7816_IO0       | GPIO Port 0 Bit 31;<br>ISO UART 0 Data In/Out                               | ISO UART (if enabled) GPIO                                              |

| 6   | P0.30/7816_CLK0      | GPIO Port 0 Bit 30; ISO UART 0 Clock                                        | ISO UART (if enabled) GPIO                                              |

| 7   | PP0.29/7816_IO1      | GPIO Port 0 Bit 29;<br>ISO UART 1 Data In/Out                               | ISO UART (if enabled) GPIO                                              |

| 8   | P0.28/7816_IO_CLK1   | GPIO Port 0 Bit 28; ISO UART 1 Clock                                        | ISO UART (if enabled) GPIO                                              |

| 9   | P0.27/I2C_SDA        | GPIO Port 0 Bit 27; I <sup>2</sup> C SDA                                    | I <sup>2</sup> C port (if enabled)<br>GPIO                              |

| 10  | P0.26/I2C_SCL        | GPIO Port 0 Bit 26; I <sup>2</sup> C SCL                                    | I <sup>2</sup> C port (if enabled)<br>GPIO                              |

| 11  | P0.25/T1             | GPIO Port 0 Bit 25; Timer 1 Output                                          | PWM output function (if configured) GPIO                                |

| 12  | P0.24/T0             | GPIO Port 0 Bit 24; Timer 0 Output                                          | PWM output function (if configured) GPIO                                |

| 13  | P0.23/SEG23          | GPIO Port 0 Bit 23; LCD Segment 23                                          | LCD<br>GPIO                                                             |

| 14  | P0.22/SEG22          | GPIO Port 0 Bit 22; LCD Segment 22                                          | LCD<br>GPIO                                                             |

| 15  | P0.21/SEG21          | GPIO Port 0 Bit 21; LCD Segment 21                                          | LCD<br>GPIO                                                             |

| 16  | P0.20/SEG20          | GPIO Port 0 Bit 20; LCD Segment 20                                          | LCD<br>GPIO                                                             |

| 17  | P0.19/SEG19          | GPIO Port 0 Bit 19; LCD Segment 19                                          | LCD<br>GPIO                                                             |

| 18  | P0.18/SEG18          | GPIO Port 0 Bit 18; LCD Segment 18                                          | LCD<br>GPIO                                                             |

| 19  | P0.17/SEG17          | GPIO Port 0 Bit 17; LCD Segment 17                                          | LCD<br>GPIO                                                             |

| 20  | $V_{LCD}$            | LCD Supply Voltage                                                          |                                                                         |

| 21  | P0.16/SEG16/SPI_MISO | GPIO Port 0 Bit 16; LCD Segment 16;<br>SPI_MISO                             | LCD<br>SPI port (if enabled)<br>GPIO                                    |

| PIN | NAME                             | FUNCTION                                                                | PRIORITY                                                                |

|-----|----------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 22  | P0.15/SEG15/SPI_MOSI             | GPIO Port 0 Bit 15; LCD Segment 15;<br>SPI_MOSI                         | LCD<br>SPI port (if enabled)<br>GPIO                                    |

| 23  | P0.14/SEG14/SPI_SCLK             | GPIO Port 0 Bit 14; LCD Segment 14;<br>SPI_SCLK                         | LCD<br>SPI port (if enabled)<br>GPIO                                    |

| 24  | P0.13/SEG13/SPI_SSEL             | GPIO Port 0 Bit 13; LCD Segment 13;<br>SPI_SSEL                         | LCD<br>SPI port (if enabled)<br>GPIO                                    |

| 25  | P0.12/SEG12                      | GPIO Port 0 Bit 12; LCD Segment 12                                      | LCD<br>GPIO                                                             |

| 26  | V <sub>DD</sub>                  | _                                                                       | _                                                                       |

| 27  | P0.11/SEG11                      | GPIO Port 0 Bit 11; LCD Segment 11                                      | LCD<br>GPIO                                                             |

| 28  | P0.10/SEG10                      | GPIO Port 0 Bit 10; LCD Segment 10                                      | LCD<br>GPIO                                                             |

| 29  | P0.9/SEG9                        | GPIO Port 0 Bit 9; LCD Segment 9                                        | LCD<br>GPIO                                                             |

| 30  | P0.8/SEG8                        | GPIO Port 0 Bit 8; LCD Segment 8                                        | LCD<br>GPIO                                                             |

| 31  | P0.7/SEG7/COM7/(TMUX0/<br>SEG34) | GPIO Port 0 Bit 7; LCD Segment 7;<br>LCD Common 7 (Mirrored Segment 34) | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO |

| 32  | P0.6/SEG6/COM6/(TMUX1/<br>SEG35) | GPIO Port 0 Bit 6; LCD Segment 6;<br>LCD Common 6 (Mirrored Segment 35) | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO |

| 33  | P0.5/SEG5/COM5/(SEG36)           | GPIO Port 0 Bit 5; LCD Segment 5;<br>LCD Common 5 (Mirrored Segment 36) | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO |

| 34  | P0.4/SEG4/COM4/(SEG37)           | GPIO Port 0 Bit 4; LCD Segment 4;<br>LCD Common 4 (Mirrored Segment 37) | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO |

| 35  | P0.3/SEG3/COM3/(SEG38)           | GPIO Port 0 Bit 3; LCD Segment 3;<br>LCD Common 3 (Mirrored Segment 38) | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO |

| PIN | NAME                   | FUNCTION                                                                     | PRIORITY                                                                                                  |

|-----|------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 36  | P0.2/SEG2/COM2/(SEG39) | GPIO Port 0 Bit 2; LCD Segment 2;<br>LCD Common 2 (Mirrored Segment 39)      | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO                                   |

| 37  | P0.1/SEG1/COM1/(SEG40) | GPIO Port 0 Bit 1; LCD Segment 1;<br>LCD Common 1 (Mirrored Segment 40)      | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO                                   |

| 38  | P0.0/SEG0/COM0/(SEG41) | GPIO Port 0 Bit 0; LCD Segment 0;<br>LCD Common 0 (Mirrored Segment 41)      | Mirrored function (if enabled) LCD common (if enabled) LCD segment GPIO                                   |

| 39  | P1.31/SEG43/TX2        | GPIO Port 1 Bit 31; LCD Segment 43;<br>UART 2 Transmit Data                  | LCD segment UART (If enabled in LCD assignment register) GPIO                                             |

| 40  | P1.30/SEG42/RX2/WAKE5  | GPIO Port 1 Bit 30; LCD Segment 42;<br>UART 2 Receive Data; CPU Wake Input 5 | LCD segment GPIO UART input and CPU wake input are available in parallel with GPIO functions, if enabled. |

| 41  | P1.29/TX1              | GPIO Port 1 Bit 29; UART 1 Transmit Data                                     | UART (If enabled in LCD assignment register) GPIO                                                         |

| 42  | P1.28/RX1/WAKE4        | GPIO Port 1 Bit 28; UART 1 Receive Data;<br>CPU Wake Input 4                 | Dedicated GPIO bit; UART and wake functions independently enabled.                                        |

| 43  | P1.27/TDO              | GPIO Port 1 Bit 27; JTAG TDO                                                 | JTAG (if enabled with JTAG_E pin) GPIO                                                                    |

| 44  | P1.26/TCK              | GPIO Port 1 Bit 26; JTAG TCK                                                 | JTAG (if enabled with JTAG_E pin) GPIO                                                                    |

| 45  | P1.25/TMS              | GPIO Port 1 Bit 25; JTAG TMS                                                 | JTAG (if enabled with JTAG_E pin) GPIO                                                                    |

| 46  | P1.24/TDI              | GPIO Port 1 Bit 24; JTAG TDI                                                 | JTAG (if enabled with JTAG_E pin) GPIO                                                                    |

| 47  | JTAG_E                 | JTAG Port Enable                                                             | _                                                                                                         |

| 48  | P1/23/VPULSE           | GPIO Port 1 Bit 23                                                           | VPULSE output (if enabled) GPIO                                                                           |

| 49  | P1/22/WPULSE           | GPIO Port 1 Bit 22                                                           | WPULSE output (if enabled) GPIO                                                                           |

| 50  | GNDD                   | Digital Ground                                                               | _                                                                                                         |

| 51  | V <sub>3P3D</sub>      | Power Output for External Digital Devices                                    | _                                                                                                         |

| 52  | V <sub>LCD5</sub>      | Input from External LCD Charge Pump                                          | _                                                                                                         |

| 53  | V_SQW                  | Square-Wave Output for LCD Charge Pump                                       | _                                                                                                         |

| PIN | NAME                            | FUNCTION                                                                                          | PRIORITY                                                                                                                                                        |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54  | P1.21/TOUCH1/INT7/<br>WAKE7     | GPIO Port 1 Bit 21; Touch Input 1; External Interrupt 7; CPU Wake Input 7                         | Touch input (if enabled) GPIO; external interrupts are available when GPIO is selected.                                                                         |

| 55  | P1.20/TOUCH01/INT7/<br>WAKE6    | GPIO Port 1 Bit 20; Touch Input 0; External Interrupt 6; CPU Wake Input 6                         | Touch input (if enabled) GPIO; external interrupts are available when GPIO is selected.                                                                         |

| 56  | P1.19/ADC3/TX0/OPT_TX           | GPIO Port 1 Bit 19; AUX ADC Input 3;<br>UART 0 Transmit Data; Optical Transmit                    | AUX ADC (if selected) UART 0 (optionally modulated for optical transmission) GPIO.                                                                              |

| 57  | P1.18/ADC2/RX0/OPT_RX/<br>WAKE3 | GPIO Port 1 Bit 18; AUX ADC Input 2;<br>UART 0 Receive Data; Optical Receive/<br>CPU Wake Input 3 | AUX ADC (if selected) GPIO The optical receiver is enabled if the AUX ADC input is enabled, the demodulation filter is active and the UART receiver is enabled. |

| 58  | P1.17/ADC1                      | GPIO Port 1 Bit 17; AUX ADC Input 1                                                               | AUX ADC (if selected) GPIO                                                                                                                                      |

| 59  | P1.16/ADC0                      | GPIO Port 1 Bit 16; AUX ADC Input 0                                                               | AUX ADC (if selected) GPIO                                                                                                                                      |

| 60  | GNDR                            | Ground for Remote ADC Channels                                                                    | _                                                                                                                                                               |

| 61  | IAP/RMT0P                       | Current Input A, Noninverting input; Remote Interface 0 Positive Pole                             | RMT0P (if enabled) IAP                                                                                                                                          |

| 62  | IAN/RMT0N                       | Current input A, Inverting Input; Remote Interface 0 Negative Pole                                | RMT0N (if enabled) IAN                                                                                                                                          |

| 63  | IBP/RMT1P                       | Current input B, Noninverting Input; Remote Interface 1 Positive Pole)                            | RMT1P (if enabled) IBP                                                                                                                                          |

| 64  | IBN/RMT1N                       | Current input B, Inverting Input; Remote Interface 1 Negative Pole                                | RMT1N (if enabled)<br>IBN                                                                                                                                       |

| 65  | V <sub>3P3SYS</sub>             | Main Power Input (3.3V)                                                                           | _                                                                                                                                                               |

| 66  | GNDA                            | Analog Ground                                                                                     | _                                                                                                                                                               |

| 67  | V <sub>3P3A</sub>               | 3.3V Analog Input                                                                                 | _                                                                                                                                                               |

| 68  | V <sub>D</sub>                  | Additional Voltage Input for Metrology ADC                                                        | _                                                                                                                                                               |

| 69  | V <sub>C</sub>                  | Additional Voltage Input for Metrology ADC                                                        | _                                                                                                                                                               |

| 70  | V <sub>B</sub>                  | Additional Voltage in Input for Metrology ADC                                                     | _                                                                                                                                                               |

| 71  | GNDA                            | Analog Ground                                                                                     | _                                                                                                                                                               |

| 72  | V <sub>A</sub>                  | Voltage Sensor Input A                                                                            | _                                                                                                                                                               |

| 73  | V <sub>BAT</sub>                | Primary Backup Battery Input                                                                      | _                                                                                                                                                               |

| 74  | V <sub>BAT_RTC</sub>            | RTC Backup Battery Input                                                                          | _                                                                                                                                                               |

| 75  | XOUT                            | 32kHz Crystal Amplifier Output                                                                    | _                                                                                                                                                               |

| PIN | NAME                             | FUNCTION                                                                              | PRIORITY                                                                                                            |

|-----|----------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 76  | XIN                              | 32kHz Crystal Amplifier Input                                                         | _                                                                                                                   |

| 77  | V <sub>3P3RTC</sub>              | _                                                                                     | _                                                                                                                   |

| 78  | RSTN                             | Active-Low Reset Input                                                                | _                                                                                                                   |

| 79  | V <sub>DD_CAL</sub>              |                                                                                       | _                                                                                                                   |

| 80  | P1.15/INT5                       | GPIO Port 1 Bit 15; External Interrupt 5                                              | Dedicated GPIO bit; interrupt function independently enabled.                                                       |

| 81  | P1.14/INT4                       | GPIO Port 1 Bit 14; External Interrupt 4                                              | Dedicated GPIO bit; interrupt function independently enabled.                                                       |

| 82  | P1.13/YPULSE/INT3                | GPIO Port 1 Bit 13; YPULSE; External Interrupt 3                                      | YPULSE output (if enabled) GPIO The external interrupt function operates whether or not the pulse output is enabled |

| 83  | P1.12/XPULSE/INT2                | GPIO Port 1 Bit 12; XPULSE; External Interrupt 2                                      | XPULSE output (if enabled) GPIO The external interrupt function operates whether or not the pulse output is enabled |

| 84  | SEG41 (COM0/P0.0/SEG0)           | LCD Segment 41 (Mirrored LCD Common 0; GPIO Port 0 Bit 0; LCD Segment 0)              | Mirrored function (if enabled) LCD segment                                                                          |

| 85  | SEG40 (COM1/P0.1/SEG1)           | LCD Segment 40 (Mirrored LCD Common 1; GPIO Port 0 Bit 1; LCD Segment 1)              | Mirrored function (if enabled)<br>LCD segment                                                                       |

| 86  | SEG39 (COM2/P0.2/SEG2)           | LCD Segment 39 (Mirrored LCD Common 2; GPIO Port 0 Bit 2; LCD Segment 2)              | Mirrored function (if enabled)<br>LCD segment                                                                       |

| 87  | SEG38 (COM3/P0.1/SEG3)           | LCD Segment 38 (Mirrored LCD Common 3; GPIO Port 0 Bit 3; LCD Segment 3)              | Mirrored function (if enabled)<br>LCD segment                                                                       |

| 88  | SEG37 (COM4/P0.4/SEG4)           | LCD Segment 37 (Mirrored LCD Common 4; GPIO Port 0 Bit 4; LCD Segment 4)              | Mirrored function (if enabled)<br>LCD segment                                                                       |

| 89  | SEG36 (COM5/P0.5/SEG5)           | LCD Segment 36 (Mirrored LCD common 5;<br>GPIO Port 0 Bit 5; LCD Segment 5)           | Mirrored function (if enabled)<br>LCD segment                                                                       |

| 90  | TMUX1/SEG35/<br>(COM6/P0.6/SEG6) | TMUX1; LCD Segment 35 (Mirrored<br>LCD Common 6; GPIO Port 0 Bit 6; LCD<br>Segment 6) | Mirrored function (if enabled)<br>LCD segment<br>TMUX1                                                              |

| 91  | TMUX0/SEG34/<br>(COM7/P0.7/SEG7) | TMUX0; LCD Segment 34 (Mirrored<br>LCD Common 7; GPIO Port 0 Bit 7; LCD<br>Segment 7) | Mirrored function (if enabled) LCD segment TMUX0                                                                    |

| 92  | P1.11/SEG33                      | GPIO Port 1 Bit 11; LCD Segment 33                                                    | LCD<br>GPIO                                                                                                         |

| 93  | P1.10/SEG32                      | GPIO Port 1 Bit 10; LCD Segment 32                                                    | LCD<br>GPIO                                                                                                         |

| 94  | P1.9/SEG31                       | GPIO Port 1 Bit 9; LCD Segment 31                                                     | LCD<br>GPIO                                                                                                         |

| PIN | NAME       | FUNCTION                          | PRIORITY    |

|-----|------------|-----------------------------------|-------------|

| 95  | P1.8/SEG30 | GPIO Port 1 Bit 8; LCD Segment 30 | LCD<br>GPIO |

| 96  | P1.7/SEG29 | GPIO Port 1 Bit 7; LCD Segment 29 | LCD<br>GPIO |

| 97  | P1.6/SEG28 | GPIO Port 1 Bit 6; LCD Segment 28 | LCD<br>GPIO |

| 98  | P1.5/SEG27 | GPIO Port 1 Bit 5; LCD Segment 27 | LCD<br>GPIO |

| 99  | P1.4/SEG26 | GPIO Port 1 Bit 4; LCD Segment 26 | LCD<br>GPIO |

| 100 | GNDD       | Digital Ground                    | _           |

# **Pin Description (Sorted by Function)**

| FUNCTION             | PIN     | DESCRIPTION                                                                                                                                                                                                  |  |

|----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| POWER                | '       |                                                                                                                                                                                                              |  |

| V <sub>3P3SYS</sub>  | 65      | 3.3V Power Input for Digital Circuits                                                                                                                                                                        |  |

| V <sub>3P3A</sub>    | 67      | 3.3V Power Input for Analog Circuits                                                                                                                                                                         |  |

| V <sub>BAT</sub>     | 73      | Power Input for Primary Backup Battery. This battery supplies all digital circuits in brownout mode and LCD only mode.                                                                                       |  |

| V <sub>BAT_RTC</sub> | 74      | Power Input for RTC Backup Battery. This battery supplies the RTC block and the calibration block (temperature sensor and associated circuitry) even when primary VBAT and V3P3SYS supplies are unavailable. |  |

| V <sub>3P3D</sub>    | 51      | Provides a Bypass Point to the Internal 3.3V Bus                                                                                                                                                             |  |

| $V_{DD}$             | 26      | Provides a Bypass Point to the Internal Regulated (1.8V) Core Supply Bus                                                                                                                                     |  |

| V <sub>3P3RTC</sub>  | 77      | Provides a Bypass Point to the Real-Time clock Power Bus                                                                                                                                                     |  |

| V <sub>DD_CAL</sub>  | 79      | Provides a Bypass Point to the RTC Calibration Power Bus                                                                                                                                                     |  |

| GNDA                 | 66, 71  | Analog Ground. Should be at the same potential as digital ground. Typically, analog and digital grounds connect together at a single point.                                                                  |  |

| GNDD                 | 50, 100 | Digital Ground                                                                                                                                                                                               |  |

| GNDR                 | 60      | Remote Ground. This is the ground return for the remote sensor interfaces and is provided separately due to high currents that can flow in this circuit.                                                     |  |

| CLOCK                |         |                                                                                                                                                                                                              |  |

| XOUT                 | 75      | Crystal Amplifier Output Pin. Connect to a 32,768Hz tuning-fork crystal.                                                                                                                                     |  |

| XIN                  | 76      | Crystal Amplifier Input Pin. Connect to a 32,768Hz tuning-fork crystal.                                                                                                                                      |  |

| ANALOG               | ·       |                                                                                                                                                                                                              |  |

| IAP                  | 61      | Main Current Channel Noninverting Analog Input                                                                                                                                                               |  |

| IAN                  | 62      | Main Current Channel Inverting Analog Input                                                                                                                                                                  |  |

| IBP                  | 63      | Neutral Current Channel Noninverting Analog Input                                                                                                                                                            |  |

| IBN                  | 64      | Neutral Current Channel Inverting Analog Input                                                                                                                                                               |  |

| FUNCTION PIN   |    | DESCRIPTION                                                                                                                                                                                                                                                     |  |  |

|----------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>A</sub> | 72 | Primary Voltage Channel Analog Input (Single-Ended)                                                                                                                                                                                                             |  |  |

| V <sub>B</sub> | 70 | Secondary Voltage Channel Analog Input (Single-Ended)                                                                                                                                                                                                           |  |  |

| V <sub>C</sub> | 69 | Additional Voltage Input to Metrology Channel (Single-Ended)                                                                                                                                                                                                    |  |  |

| $V_{D}$        | 68 | Additional Voltage Input to Metrology Channel (Single-Ended)                                                                                                                                                                                                    |  |  |

| RMT0P          | 61 | Main Current Channel Remote Input, Positive Pole                                                                                                                                                                                                                |  |  |

| RMT0N          | 62 | Main Current Channel Remote Input, Negative Pole                                                                                                                                                                                                                |  |  |

| RMT1P          | 63 | Neutral Current Channel Remote Input, Positive Pole                                                                                                                                                                                                             |  |  |

| RMT1N          | 64 | Neutral Current Channel Remote Input, Negative Pole                                                                                                                                                                                                             |  |  |

| ADC0           | 59 | Auxiliary ADC Input Channel 0                                                                                                                                                                                                                                   |  |  |

| ADC1           | 58 | Auxiliary ADC Input Channel 1                                                                                                                                                                                                                                   |  |  |

| ADC2           | 57 | Auxiliary ADC Input Channel 2                                                                                                                                                                                                                                   |  |  |

| ADC3           | 56 | Auxiliary ADC Input Channel 3                                                                                                                                                                                                                                   |  |  |

| SYSTEM         |    |                                                                                                                                                                                                                                                                 |  |  |

| JTAG TDO       | 43 | JTAG Test Data Out                                                                                                                                                                                                                                              |  |  |

| JTAG TCK       | 44 | JTAG Test Clock                                                                                                                                                                                                                                                 |  |  |

| JTAG TMS       | 45 | JTAG Test Mode Select                                                                                                                                                                                                                                           |  |  |

| JTAG TDI       | 46 | JTAG Test Data In                                                                                                                                                                                                                                               |  |  |

| JTAG_E         | 47 | JTAG Port Enable. External circuitry must pull this pin high at power-up to enable the JTAG port. When not using the JTAG port (as when the product is deployed), JTAG_E should be pulled low so the JTAG pins can be used for other purposes.                  |  |  |

| RSTN           | 78 | Reset. This active-low signal resets the CPU core forcing restart to the utility ROM. If JTAG_E is not active (JTAG_E is low), most MAXQ peripherals and registers are reset to their default value. This pin must be pulled up under all operating conditions. |  |  |

| TMUX0          | 91 | Test Multiplexer 0 Output. The test multiplexer can be configured to present several internal signals to the TMUX0 pin.                                                                                                                                         |  |  |

| TMUX1          | 90 | Test Multiplexer 1 Output. The test multiplexer can be configured to present several internal signals to the TMUX1 pin.                                                                                                                                         |  |  |

| GPIO           |    |                                                                                                                                                                                                                                                                 |  |  |

| P0.0           | 38 | General-Purpose I/O Port 0 Bit 0. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.                                                                                                                   |  |  |

| P0.1           | 37 | General-Purpose I/O Port 0 Bit 1. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.                                                                                                                   |  |  |

| P0.2           | 36 | General-Purpose I/O Port 0 Bit 2. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.                                                                                                                   |  |  |

| P0.3           | 35 | General-Purpose I/O Port 0 Bit 3. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.                                                                                                                   |  |  |

| P0.4           | 34 | General-Purpose I/O Port 0 Bit 4. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.                                                                                                                   |  |  |

| FUNCTION | PIN | DESCRIPTION                                                                                                                                    |  |  |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P0.5     | 33  | General-Purpose I/O Port 0 Bit 5. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P0.6     | 32  | General-Purpose I/O Port 0 Bit 6. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P0.7     | 31  | General-Purpose I/O Port 0 Bit 7. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P0.8     | 30  | General-Purpose I/O Port 0 Bit 8. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P0.9     | 29  | General-Purpose I/O Port 0 Bit 9. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P0.10    | 28  | General-Purpose I/O Port 0 Bit 10. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.11    | 27  | General-Purpose I/O Port 0 Bit 11. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.12    | 25  | General-Purpose I/O Port 0 Bit 12. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.13    | 24  | General-Purpose I/O Port 0 Bit 13. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.14    | 23  | General-Purpose I/O Port 0 Bit 14. This pin can be configured as input, totem-pole or or open-drain output with or without a weak pullup.      |  |  |

| P0.15    | 22  | General-Purpose I/O Port 0 Bit 15. This pin can be configured as input, totem-pole ou or open-drain output with or without a weak pullup.      |  |  |

| P0.16    | 21  | General-Purpose I/O Port 0 Bit 16. This pin can be configured as input, totem-pole output or open-drain output with or without a weak pullup.  |  |  |

| P0.17    | 19  | General-Purpose I/O Port 0 Bit 17. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.18    | 18  | General-Purpose I/O Port 0 Bit 18. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.19    | 17  | General-Purpose I/O Port 0 Bit 19. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.20    | 16  | General-Purpose I/O Port 0 Bit 20. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.21    | 15  | General-Purpose I/O Port 0 Bit 21. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.22    | 14  | General-Purpose I/O Port 0 Bit 22. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.23    | 13  | General-Purpose I/O Port 0 Bit 23. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.24    | 12  | General-Purpose I/O Port 0 Bit 24. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.25    | 11  | General-Purpose I/O Port 0 Bit 25. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| FUNCTION | PIN | DESCRIPTION                                                                                                                                    |  |  |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P0.26    | 10  | General-Purpose I/O Port 0 Bit 26. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.27    | 9   | General-Purpose I/O Port 0 Bit 27. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.28    | 8   | General-Purpose I/O Port 0 Bit 28. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.29    | 7   | General-Purpose I/O Port 0 Bit 29. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.30    | 6   | General-Purpose I/O Port 0 Bit 30. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P0.31    | 5   | General-Purpose I/O Port 0 Bit 31. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P1.0     | 4   | General-Purpose I/O Port 1 Bit 0. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.1     | 3   | General-Purpose I/O Port 1 Bit 1. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.2     | 2   | General-Purpose I/O Port 1 Bit 2. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.3     | 1   | General-Purpose I/O Port 1 Bit 3. This pin can be configured as input, totem-pole out or open-drain output with or without a weak pullup.      |  |  |

| P1.4     | 99  | General-Purpose I/O Port 1 Bit 4. This pin can be configured as input, totem-pole out or open-drain output with or without a weak pullup.      |  |  |

| P1.5     | 98  | General-Purpose I/O Port 1 Bit 5. This pin can be configured as input, totem-pole output or open-drain output with or without a weak pullup.   |  |  |

| P1.6     | 97  | General-Purpose I/O Port 1 Bit 6. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.7     | 96  | General-Purpose I/O Port 1 Bit 7. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.8     | 95  | General-Purpose I/O Port 1 Bit 8. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.9     | 94  | General-Purpose I/O Port 1 Bit 9. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup.  |  |  |

| P1.10    | 93  | General-Purpose I/O Port 1 Bit 10. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P1.11    | 92  | General-Purpose I/O Port 1 Bit 11. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P1.12    | 83  | General-Purpose I/O Port 1 Bit 12. This pin can be configured as input, totem-pole output or open-drain output with or without a weak pullup.  |  |  |

| P1.13    | 82  | General-Purpose I/O Port 1 Bit 13. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| P1.14    | 81  | General-Purpose I/O Port 1 Bit 14. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |  |

| FUNCTION | FUNCTION PIN DESCRIPTION |                                                                                                                                                |  |

|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P1.15    | 80                       | General-Purpose I/O Port 1 Bit 15. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.16    | 59                       | General-Purpose I/O Port 1 Bit 16. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.17    | 58                       | General-Purpose I/O Port 1 Bit 17. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.18    | 57                       | General-Purpose I/O Port 1 Bit 18. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.19    | 56                       | General-Purpose I/O Port 1 Bit 19. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.20    | 55                       | General-Purpose I/O Port 1 Bit 20. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.21    | 54                       | General-Purpose I/O Port 1 Bit 21. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.22    | 49                       | General-Purpose I/O Port 1 Bit 22. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.23    | 48                       | General-Purpose I/O Port 1 Bit 23. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.24    | 46                       | General-Purpose I/O Port 1 Bit 24. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.25    | 45                       | General-Purpose I/O Port 1 Bit 25. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.26    | 44                       | General-Purpose I/O Port 1 Bit 26. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.27    | 43                       | General-Purpose I/O Port 1 Bit 27. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.28    | 42                       | General-Purpose I/O Port 1 Bit 28. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.29    | 41                       | General-Purpose I/O Port 1 Bit 29. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.30    | 40                       | General-Purpose I/O Port 1 Bit 30. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| P1.31    | 39                       | General-Purpose I/O Port 1 Bit 31. This pin can be configured as input, totem-pole output, or open-drain output with or without a weak pullup. |  |

| LCD      |                          |                                                                                                                                                |  |

| COM0     | 38                       | LCD Backplane Output 0                                                                                                                         |  |

| COM1     | 37                       | LCD Backplane Output 1                                                                                                                         |  |

| COM2     | 36                       | LCD Backplane Output 2                                                                                                                         |  |

| COM3     | 35                       | LCD Backplane Output 3                                                                                                                         |  |

| COM4     | 34                       | LCD Backplane Output 4                                                                                                                         |  |

| COM5     | 33                       | LCD Backplane Output 5                                                                                                                         |  |

| FUNCTION | PIN | DESCRIPTION            |  |  |

|----------|-----|------------------------|--|--|

| COM6     | 32  | LCD Backplane Output 6 |  |  |

| COM7     | 31  | LCD Backplane Output 7 |  |  |

| SEG0     | 38  | LCD Segment Output 0   |  |  |

| SEG1     | 37  | LCD Segment Output 1   |  |  |

| SEG2     | 36  | LCD Segment Output 2   |  |  |

| SEG3     | 35  | LCD Segment Output 3   |  |  |

| SEG4     | 34  | LCD Segment Output 4   |  |  |

| SEG5     | 33  | LCD Segment Output 5   |  |  |

| SEG6     | 32  | LCD Segment Output 6   |  |  |

| SEG7     | 31  | LCD Segment Output 7   |  |  |

| SEG8     | 30  | LCD Segment Output 8   |  |  |

| SEG9     | 29  | LCD Segment Output 9   |  |  |

| SEG10    | 28  | LCD Segment Output 0   |  |  |

| SEG11    | 27  | LCD Segment Output 11  |  |  |

| SEG12    | 25  | LCD Segment Output 12  |  |  |

| SEG13    | 24  | LCD Segment Output 13  |  |  |

| SEG14    | 23  | LCD Segment Output 14  |  |  |

| SEG15    | 22  | LCD Segment Output 15  |  |  |

| SEG16    | 21  | LCD Segment Output 16  |  |  |

| SEG17    | 19  | LCD Segment Output 17  |  |  |

| SEG18    | 18  | LCD Segment Output 18  |  |  |

| SEG19    | 17  | LCD Segment Output 19  |  |  |

| SEG20    | 16  | LCD Segment Output 20  |  |  |

| SEG21    | 15  | LCD Segment Output 21  |  |  |

| SEG22    | 14  | LCD Segment Output 22  |  |  |

| SEG23    | 13  | LCD Segment Output 23  |  |  |

| SEG24    | 4   | LCD Segment Output 24  |  |  |

| SEG25    | 3   | LCD Segment Output 25  |  |  |

| SEG26    | 99  | LCD Segment Output 26  |  |  |

| SEG27    | 98  | LCD Segment Output 27  |  |  |

| SEG28    | 97  | LCD Segment Output 28  |  |  |

| SEG29    | 96  | LCD Segment Output 29  |  |  |

| SEG30    | 95  | LCD Segment Output 30  |  |  |

| SEG31    | 94  | LCD Segment Output 31  |  |  |

| SEG32    | 93  | LCD Segment Output 32  |  |  |

| SEG33    | 92  | LCD Segment Output 33  |  |  |

| FUNCTION          | CTION PIN DESCRIPTION |                                                                                                     |  |  |

|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------|--|--|

| SEG34             | 91                    | LCD Segment Output 34                                                                               |  |  |

| SEG35             | 90                    | LCD Segment Output 35                                                                               |  |  |

| SEG36             | 89                    | LCD Segment Output 36                                                                               |  |  |

| SEG37             | 88                    | LCD Segment Output 37                                                                               |  |  |

| SEG38             | 87                    | LCD Segment Output 38                                                                               |  |  |

| SEG39             | 86                    | LCD Segment Output 39                                                                               |  |  |

| SEG40             | 85                    | LCD Segment Output 40                                                                               |  |  |

| SEG41             | 84                    | LCD Segment Output 41                                                                               |  |  |

| SEG42             | 40                    | LCD Segment Output 42                                                                               |  |  |

| SEG43             | 39                    | LCD Segment Output 43                                                                               |  |  |

| V <sub>LCD</sub>  | 20                    | LCD Contrast DAC Output. User should connect a 0.1µF bypass capacitor to this pin.                  |  |  |

| V <sub>LCD5</sub> | 52                    | Input for Boosted LCD Voltage. Provides an alternate input for the LCD contrast DAC.                |  |  |

| V_sqw             | 53                    | Square Wave to Drive a Charge Pump to Generate Boosted LCD Voltage. Can be disabled by software.    |  |  |

| EXTERNAL INTERF   | RUPTS                 |                                                                                                     |  |  |

| INT0              | 2                     | External Interrupt 0 Input. External interrupts can be individually enabled or masked.              |  |  |

| INT1              | 1                     | External Interrupt 1 Input. External interrupts can be individually enabled or masked.              |  |  |

| INT2              | 83                    | External Interrupt 2 Input. External interrupts can be individually enabled or masked.              |  |  |