# Superjunction MOSFET for charger applications

600 V/650 V/700 V/800 V CoolMOS™ CE

#### About this document

#### Scope and purpose

This application note will describe the fundamental differences between a Superjunction MOSFET and a standard MOSFET. Additionally, all features and benefits impacting the target applications will be described. Furthermore, these features will be illustrated from both a theoretical point of view and in hardware measurements. It will also be shown that CoolMOS<sup>™</sup> CE is a cost effective alternative compared to standard MOSFETs, which enables reaching higher efficiency levels while offering an attractive price/-performance ratio.

#### Intended audience

This document is intended for designers & engineers who wish to design chargers in price sensitive and targeted applications such as consumer, PC silverboxes and lighting where Infineon's CoolMOS<sup>™</sup> CE offers the best price-performance ratio on the market while meeting higher efficiency standards.

#### **Table of contents**

| 1     | Introduction                                            | 2  |

|-------|---------------------------------------------------------|----|

| 1.1   | Features and benefits                                   | 2  |

| 1.2   | Applications (target market)                            | 2  |

| 2     | Superjunction (SJ) principle                            | 3  |

| 2.1   | General description                                     | 3  |

| 2.2   | Superjunction benefit of CoolMOS <sup>™</sup> CE        | 4  |

| 2.2.1 | Switching speed                                         |    |

| 3     | Technology parameters                                   | 7  |

| 3.1   | Gate charge ( $Q_g$ )                                   |    |

| 3.2   | Energy stored in output capacitance (E <sub>oss</sub> ) |    |

| 4     | Measurement results                                     | 9  |

| 4.1   | Efficiency and thermal in charger                       | 9  |

| 5     | Design guidelines for CoolMOS™ CE in flyback converter  |    |

| 5.1   | Breakdown voltage (V <sub>(BR)DSS</sub> )               |    |

| 5.2   | On-state resistance (R <sub>DS(on)</sub> )              |    |

| 5.3   | C <sub>oss</sub> stored energy (E <sub>oss</sub> )      |    |

| 5.4   | Total gate charge (Q <sub>G</sub> )                     |    |

| 6     | Portfolio                                               | 14 |

| 7     | References                                              | 16 |

### 1 Introduction

The CoolMOS<sup>™</sup> CE is a technology platform of Infineon's market leading high voltage power MOSFETs designed according to the revolutionary Superjunction (SJ) principle. After launching the 500 V class in 2012, CE technology is now also available in 600 V, 650 V, 700 V and 800 V. CoolMOS<sup>™</sup> CE portfolio provides all benefits of a fast switching SJ MOSFET while keeping ease-of-use and implementation. The complete CE series of MOSFETs achieve very low conduction and switching losses, and can make applications more efficient, more compact, lighter and thermally cooler.

### 1.1 Features and benefits

The following table represents the features and benefits of CoolMOS<sup>™</sup> CE in comparison to standard MOSFETs, which will be discussed in depth in the main part of this application note.

| Features                                                        | Benefits                                                            |

|-----------------------------------------------------------------|---------------------------------------------------------------------|

| Reduced energy stored in output capacitance (E <sub>oss</sub> ) | Reduction of switching losses, improvement of light load efficiency |

| High body diode ruggedness                                      | Higher reliability in critical operating conditions                 |

| Reduced reverse recovery charge (Q <sub>rr</sub> )              | Lower possibility of hard commutation in resonant topologies        |

| Deduced acts charge (O.)                                        | Improvement in light load efficiency                                |

| Reduced gate charge (Qg)                                        | Lower gate drive capability required                                |

#### Table 1 Features and benefits

### 1.2 Applications (target market)

The following table represents the target applications and topologies for these new MOSFETs

| Table 2 Target applications and topol | ogies |

|---------------------------------------|-------|

|---------------------------------------|-------|

| Application        | PFC          | PWM     |

|--------------------|--------------|---------|

| PC silverbox       | Depart Store | TTF     |

| PC SILVERDOX       | Boost-Stage  | LLC     |

| LCD / LED / PDP TV | Boost-Stage  | LLC     |

| Coming             |              | TTF     |

| Gaming             | Boost-Stage  | LLC     |

| Adapter            | Boost-Stage  | Flyback |

| Charger            |              | Flyback |

| Lighting           | Boost Stage  | Flyback |

| Lighting           | Boost-Stage  | LLC     |

All the features and benefits of the 500 V CoolMOS<sup>™</sup> CE in connection with the target applications and topologies will be analyzed in section 4. The following section will describe the differences between SJ MOSFETs and standard MOSFETs.

Superjunction (SJ) principle

# 2 Superjunction (SJ) principle

This chapter is included to understand the difference between SJ MOSFET and standard MOSFET because the consumer market has been dominated in the past by standard MOSFETs.

### 2.1 General description

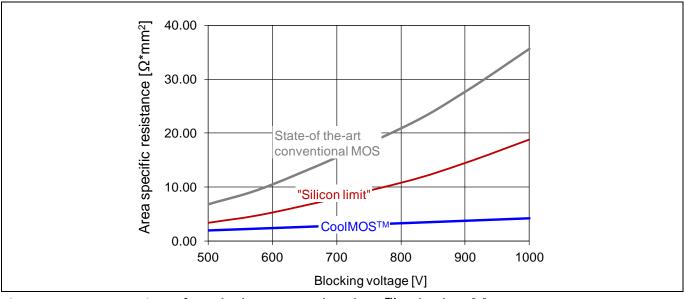

"All CoolMOS<sup>™</sup> series are based on the Superjunction principle, which is a revolutionary technology for high voltage power MOSFETs [1, 2]. Infineon Technologies has been the first company worldwide to commercialize this idea into the market [4]. Where conventional power MOSFETs just command on one degree of freedom to master both on-state resistance and blocking voltage, the superjunction principle allows two degrees of freedom for this task. Therefore conventional MOSFETs are stuck with the limit of silicon, a barrier which marks the optimum doping profile for a given voltage class. This limit line has been theoretically derived by Chen and Hu in the late 80ies [3]. No commercial product has an on-state resistance better than the limit line of silicon."

Figure 1 represents the area-specific on-resistance versus breakdown voltage of a standard MOSFET vs Infineon's SJ MOSFET CoolMOS™

Figure 1 Comparison of standard MOSFET and CoolMOS<sup>™</sup> technology [6]

"In contrast to that the superjunction principle allows to reduce the on-state resistance of a high voltage MOSFET virtually to zero, limited only by technology efforts and manufacturing capabilities." [5]

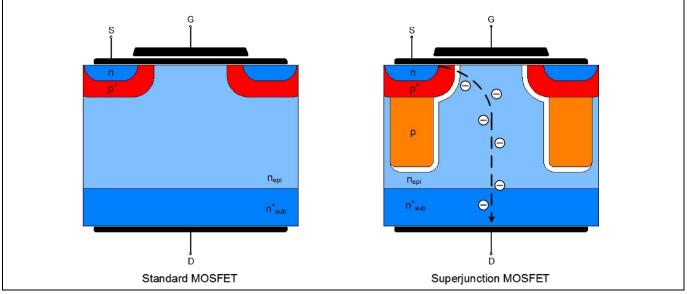

"The basic idea is simple: instead of having electrons flowing through a relatively high resistive (high voltage blocking) n-area, we allow them to flow in a very rich doped n-area, which gives naturally a very low on-state resistance. The crucial point for the SJ technology is to make the device block its full voltage, which requires a careful balancing of the additional n-charge by adjacently positioned deep p-columns, which go all the way straight through the device close to the back side n+ contact. This is where manufacturing capability comes in, as the charges within the device needs to be compensated precisely under the constraints of a mass market production line." [5]

Figure 2 shows the cross section of a standard MOSFET (left) and a SJ MOSFET (right).

#### Superjunction (SJ) principle

"The SJ principle gives us the opportunity to create best-in-class types, which have not been possible before such as a 100 m $\Omega$ /600 V part in a TO-220 package. Furthermore it allows making parts with very low capacitances for a given R<sub>DS(on)</sub> as the silicon chip is much smaller than for a conventional power MOSFET. Both input and high voltage level of the output capacitance scale directly with the chip size, whereas reverse capacitance and to some extent the low voltage level of the output capacitance is technology dependent. Characteristic of all Superjunction devices is a strong non-linearity of the output capacitance with high values at low voltage and low values at high voltage. This behavior can be easily understood if you take into account that the output capacitance is proportional to the area of the blocking pn-junction and inverse proportional to the width of the space charge layer (or the voltage sustaining area). At low voltage the p-columns are not depleted and form a very big surface, furthermore the width of the space charge layer is very narrow (the white area in" Figure 2). " At high voltage however the p-columns are fully depleted and the space charge layer has reached its full extension of roughly 45µm for a 600 V device. Important is that the non-linearity of the output capacitance allows a quasi zero-voltage-switching (ZVS) turn-off of the device, lowering turn-off losses. Superjunction devices are by nature fast in switching. Very small capacitances together with a low gate charge make rise and fall times of a few nanoseconds a reality." [5]

For more information on Superjunction devices please read the article "Mastering the Art of Slowness"; see Reference [5].

### 2.2 Superjunction benefit of CoolMOS<sup>™</sup> CE

Chapter 2.1 illustrated the general characteristics of a SJ MOSFET in comparison to a standard MOSFET. Now the question arises "What are the benefits for the CoolMOS<sup>™</sup> CE?". This application note will describe one of the most important factors which is the switching speed.

### 2.2.1 Switching speed

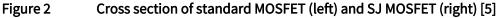

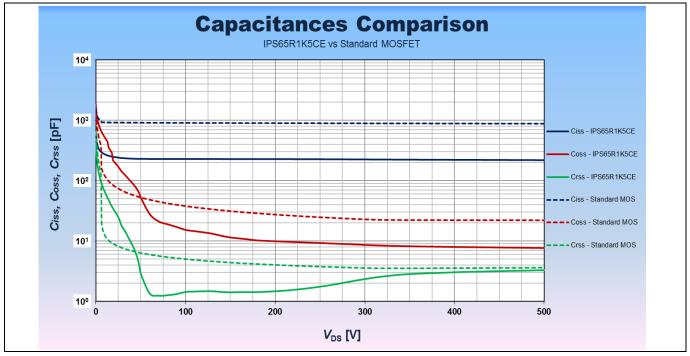

As mentioned in the general description the switching speed increases dramatically. This behavior comes from the low parasitic capacitances of a SJ MOSFET in comparison to the standard MOSFET. A SJ MOSFET has about half of the value of input and output capacitance, which brings the benefits for switching losses and driving losses. Figure 3 represents these parasitic capacitances (marked in red) in a simplified schematic.

### Superjunction MOSFET for charger applications 600 V/650 V/700 V/800 V CoolMOS™ CE

Superjunction (SJ) principle

Because of this capacitance reduction the  $E_{on}$  and  $E_{off}$  of the CoolMOS<sup>TM</sup> CE is about half in comparison to a standard MOSFET. Furthermore this reduction of capacitances results also in a reduced gate charge  $Q_g$  which gives the benefit of reduced driving losses, and the possibility to use a lower cost driver with less gate drive capability. Figure 4 represents the capacitance comparison of the 650 V CE (1500 m $\Omega$ ) vs. a comparable standard MOSFET.

Capacitance comparison 650 V CE vs. standard MOSFET

Superjunction (SJ) principle

"A fundamental characteristic of all Superjunction devices is, that both the output and reverse capacitance show a strong non-linearity. The non-linearity in Superjunction capacitance characteristics comes from the fact that at a given voltage – typically in the range of 1/10th of the rated blocking voltage – p- and n-columns deplete each other leading to a fast expansion of the space charge layer throughout the structure. This means that at a voltage beyond 50 V for 500 V rated devices both output and reverse capacitance reach minimum values of a few pF only, resulting in a dv/dt of more than 100V/ns and di/dt of several thousand A/µs if the load current is allowed to fully commute into the output capacitance during turn-off. The output capacitance is charged up to the level of the bus voltage where the voltage rise follows then the formula:

$$\frac{dv}{dt} = \frac{I_{load}}{C_{oss}}$$

[1]

The voltage rise is therefore proportional to the load current lload and inverse proportional to the value of the output capacitance C<sub>oss</sub>. Because of the decreasing C<sub>oss</sub> towards higher voltages, the highest dv/dt is reached shortly before reaching the bus voltage. The according di/dt is mainly limited by the inductances of package and PCB circuit. The highest efficiency can now be reached by turning-off the device in this manner, because the occurring switching losses can be ideally reduced down to the level of the stored energy in the output capacitance." [7]

All these benefits will be clearly visible in the efficiency results, which will be described in chapter 4. Technology parameters

Technology parameters

# 3 Technology parameters

### 3.1 Gate charge (Q<sub>g</sub>)

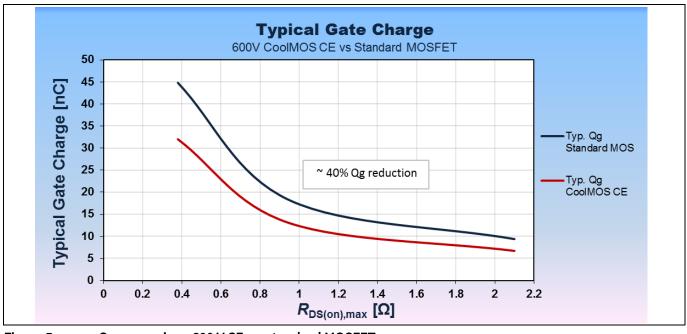

One of the most important improvements is the Qg reduction which brings benefits especially in light load conditions due to reduced driving losses. In general the CoolMOS<sup>™</sup> CE has about 40% Qg reduction in comparison to a comparable standard MOSFET over the whole R<sub>DS(on)</sub> range. Figure 5 shows the Qg in nC of the 600 V CE against a standard MOSFET over the R<sub>DS(on),max</sub> range from 400 mΩ to 2100 mΩ.

Figure 5 Q<sub>g</sub> comparison 600 V CE vs. standard MOSFET

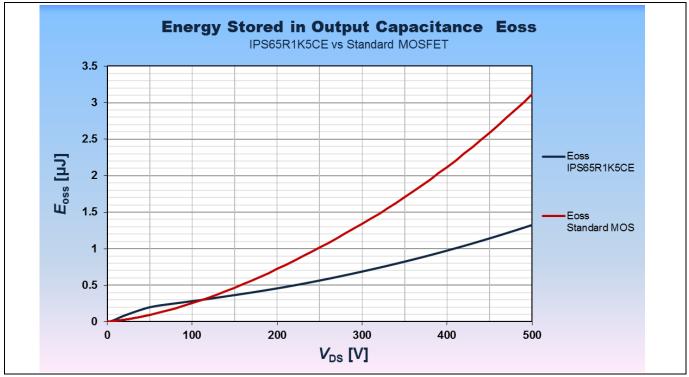

### 3.2 Energy stored in output capacitance (Eoss)

The reduced energy stored in the output capacitance brings the most important difference in hard switching topologies but nevertheless it affects also the switching losses in a resonant topology. Normally it is possible to choose between zero voltage switching (ZVS) or zero current switching (ZCS). In these two cases it is possible to eliminate the turn-on losses (ZVS) or the turn-off losses (ZCS) but it is not possible to work in these two operation modes at the same time. Normally for MOSFETs the ZVS operation is preferred due to the usual important contribution of the output capacitance to the turn-on losses (if hard switching). Therefore, one part of the switching losses is still always in action, and the reduction of  $E_{oss}$  brings a reduction of those switching losses. Figure 6 represents the  $E_{oss}$  comparison between the 650 V CE and a comparable standard MOSFET of the 1500 m $\Omega$  devices.

Technology parameters

Figure 6 E<sub>oss</sub> comparison 650 V CE vs. standard MOSFET

The  $E_{oss}$  loss is in direct proportion to the output capacitance as a function of drain to source voltage of the MOSFET. In this case the effect of a reduction of  $C_{oss}$  is very visible. One further benefit out of this is a faster  $V_{DS}$  transition time in resonant topologies, which means that it is possible to reduce the resonant inductance and circulating current loss, because it is possible to completely discharge the  $C_{oss}$  with lower currents.

### 4 Measurement results

In order to show the performance of CoolMOS<sup>™</sup> CE in charger application, two test platforms have been used. First, a slim-type 10.6 W travel charger design which is typically used in phablet or tablet segment. Next is the small form factor 15 W adapter reference board for catering the demand for fast charger market. Both power supplies are capable to accept universal input and with fixed output voltage.

#### 4.1 Efficiency and thermal in charger

In this measurement the 650 V CE is compared to a standard MOSFET in the 1.5  $\Omega$  R<sub>DS(on)</sub> range for 10.6 W charger and the efficiency and thermal performance of 1.0  $\Omega$  R<sub>DS(on)</sub> in 15 W adapter.

#### 10.6 W charger

Test setup parameters:

- Topology: Peak current controlled flyback

- V<sub>in</sub> = 90 V<sub>AC</sub> 264 V<sub>AC</sub>

- V<sub>out</sub> = 5.3 V<sub>DC</sub>

- I<sub>out</sub> = 0 A to 2 A

- Frequency = 50 kHz @ FL

- Ambient temperature = 25°C

- Plug and play scenario between 650 V CoolMOS™ CE and standard MOSFET

- High voltage MOSFET = IPS65R1K5CE

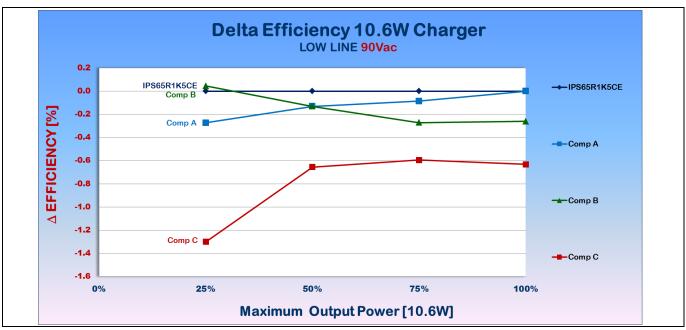

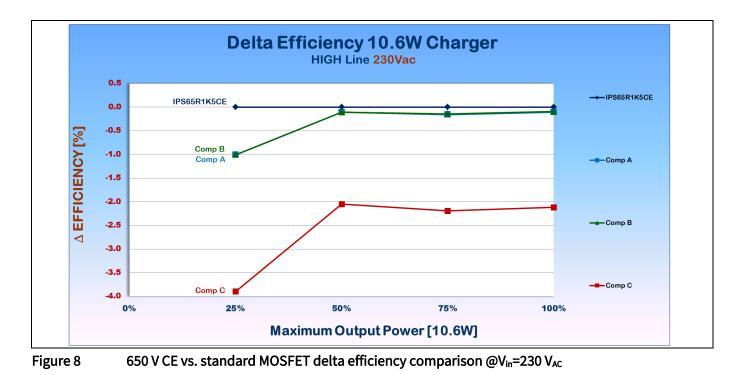

650 V CE vs. standard MOSFET delta efficiency comparison @ Vin=90 VAc

This plug and play measurement shows the benefit of a SJ MOSFET in comparison to a standard MOSFET in terms of efficiency and thermals. Due to the Q<sub>g</sub> reduction of CoolMOS<sup>™</sup> CE a minimum efficiency difference of 1% at 25% load condition, 230 V<sub>AC</sub> leads to better average efficiency as shown in Figure 7. Hence, future efficiency requirement can be easily achieved with this technology.

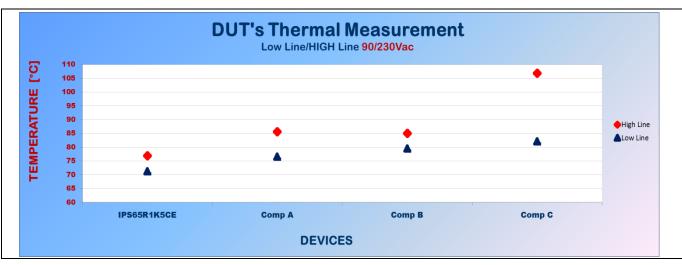

650 V CE vs. standard MOSFET thermal comparison

The thermal behavior of the power devices in charger application is very critical because the heat generated by the components will have very little way to dissipate due to very dense construction and high thermal resistance of the casing. Therefore, power mosfets with improved switching losses will help in ensuring device is below the temperature limit. As presented in Figure 8, IPS65R1K5CE offers 5°C lower than the nearest competition device at low line (worst case) which resulted to enhance design ruggedness due to increase in margin.

15 W charger

Test setup parameters:

- Topology: QR flyback

- V<sub>in</sub> = 90 V<sub>AC</sub> 264 V<sub>AC</sub>

- $V_{out} = 5 V_{DC}$

- I<sub>out</sub> = 0 A to 3 A

- Frequency = 55-110 kHz

- Ambient temperature = 25°C

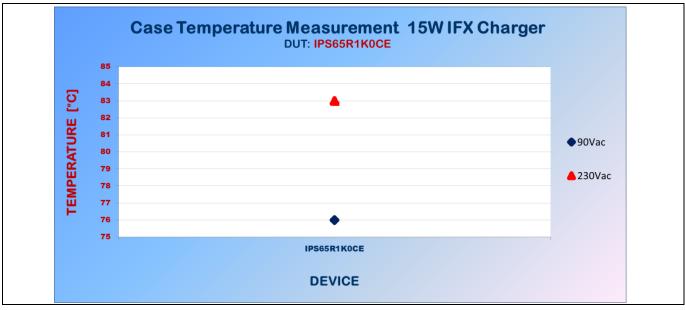

- High voltage MOSFET = IPS65R1K0CE

- •

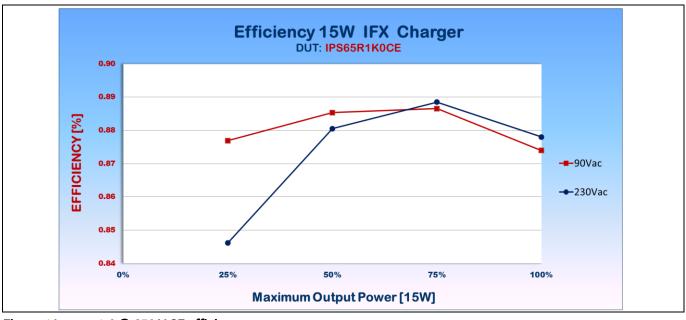

Figure 10 1.0 Ω 650 V CE efficiency

Figure 9 indicates the efficiency performance of IPS65R1K0CE. The 15 W charger can easily meet average efficiency specs of EU CoC version 5, Tier 2 and EPS of DOE USA with >5% margins in both input voltages. The solution was able reach high efficiency by reducing the switching losses in the HV switch and conduction losses in the secondary by using a SR MOSFET. Power MOSFET with low E<sub>oss</sub> and Q<sub>g</sub> contributes in minimizing the losses in the primary side.

#### Figure 11 $1.0 \Omega 650 V CE$ thermal performance

The case temperature of IPS65R1K0CE is higher at high line compared to low line (Figure 10). And theresult signifies that the converter is a switching loss dominated platform which represents the majority of the solution in the market most especially at power ≥10 W with small form factor. Thus, it is very important to consider the switching characteristic of the power mosfet which is the strongest advantage of SJ MOSFETs in comparison with standard mosfets.

# 5 Design guidelines for CoolMOS<sup>™</sup> CE in flyback converter

### 5.1 Breakdown voltage (V(BR)DSS)

Proper selection of voltage rating is necessary to ensure safe operation of the device during normal and critical conditions. Transformer's turn ratio and leakage inductance greatly influence the voltage level impressed in the device. Primary MOSFET and secondary rectifier need to be considered in choosing the optimal turn ratio because increasing or decreasing it will deliver opposite results while leakage inductance is mainly attributed to core geometry and winding construction of the transformer. Incidentally, 90% derating can be used as a rule of thumb although it some cases lower derating is required to further improved reliability.

### 5.2 On-state resistance (R<sub>DS(on)</sub>)

The primary consideration of selecting the on-state resistance is the contribution of conduction losses at full load, low input voltage because it is at its highest at this condition. However, mosfet case temperature is more critical at high input voltage which indicates the need for device that will generate lesser switching losses even to the point of choosing higher  $R_{DS(on)}$ .

### 5.3 Coss stored energy (Eoss)

To attain the demand of increasing power density in charger application, it is necessary to increase the switching frequency to lessen the increase in transformer size and output capacitors. Conversely, turn-on losses are proportional to switching frequency and E<sub>oss</sub>. Device with low E<sub>oss</sub> is beneficial in achieving high efficiency particularly at high input voltage.

### 5.4 Total gate charge (Q<sub>G</sub>)

Gate drive losses and linear losses are influenced by the total gate charge of the MOSFET. The amount of charge required to turn-on the mosfet will be the same amount of charge needed by the driver to dissipate at turn off. The duration of the linear losses is determined by Q<sub>GD</sub> which is part of switching losses. A low gate charge device is necessary to improve the efficiency and reducing the power consumption of the converter at very light load or no load condition.

# 6 Portfolio

CoolMOS<sup>™</sup> CE series follows the same naming guidelines as already established with the previous technology series e.g. IPS65R1K5CE:

| I    |     | Infineon Technologies             |

|------|-----|-----------------------------------|

| Р    | ••• | power MOSFET                      |

| S    | ••• | package type (TO-251 SL)          |

| 65   | ••• | voltage class divided by 10       |

| R1K5 |     | on-state resistance in milli Ohms |

| CE   |     | name of the series                |

#### Table 3 Portfolio 600 V CoolMOS™ CE

| R <sub>DS(on</sub> )<br>[mΩ] | TO-220<br>FullPAK | TO-252 DPAK | TO-251<br>IPAK SL | TO-251<br>IPAK | SOT-223     | TO-220 FullPAK<br>Wide Creepage |

|------------------------------|-------------------|-------------|-------------------|----------------|-------------|---------------------------------|

| 3300                         |                   | IPD60R3K4CE | IPS60R3K4CE       |                | IPN60R3K4CE |                                 |

| 2100                         |                   | IPD60R2K1CE | IPS60R2K1CE       | IPU60R2K1CE    | IPN60R2K1CE |                                 |

| 1500                         | IPA60R1K5CE       | IPD60R1K5CE | IPS60R1K5CE       | IPU60R1K5CE    | IPN60R1K5CE |                                 |

| 1000                         | IPA60R1K0CE       | IPD60R1K0CE | IPS60R1K0CE       | IPU60R1K0CE    | IPN60R1K0CE |                                 |

| 800                          | IPA60R800CE       | IPD60R800CE | IPS60R800CE       |                |             |                                 |

| 650/600                      | IPA60R650CE       | IPD60R650CE | IPS60R650CE       |                |             | IPAW60R600CE                    |

| 460                          | IPA60R460CE       | IPD60R460CE | IPS60R460CE       |                |             |                                 |

| 400/380                      | IPA60R400CE       | IPD60R400CE | IPS60R400CE       |                |             | IPAW60R380CE                    |

| 280                          |                   |             |                   |                |             | IPAW60R280CE                    |

| 190                          |                   |             |                   |                |             | IPAW60R190CE                    |

#### Table 4 Portfolio 650 V CoolMOS™ CE

| R <sub>DS(on)</sub> [mΩ] | TO-220<br>FullPAK | TO-252<br>DPAK | TO-251<br>IPAK SL | SOT-223     |

|--------------------------|-------------------|----------------|-------------------|-------------|

| 1500                     | IPA65R1K5CE       | IPD65R1K5CE    | IPS65R1K5CE       | IPN65R1K5CE |

| 1000                     | IPA65R1K0CE       | IPD65R1K0CE    | IPS65R1K0CE       |             |

| 650                      | IPA65R650CE       | IPD65R650CE    | IPS65R650CE       |             |

| 400                      | IPA65R400CE       | IPD65R400CE    | IPS65R400CE       |             |

Portfolio

#### Table 5 Portfolio 700 V CoolMOS™ CE

| R <sub>DS(on)</sub> [mΩ] | TO-262<br>IPAK | TO-252<br>DPAK | TO-251<br>IPAK SL | SOT-223     | ThinPAK 5x6  |

|--------------------------|----------------|----------------|-------------------|-------------|--------------|

| 2000/2100                |                | IPD70R2K0CE    | IPS70R2K0CE       |             | IPL70R2K1CES |

| 1400/1500                |                | IPD70R1K4CE    | IPS70R1K4CE       | IPN70R1K5CE |              |

| 950                      | IPI70R950CE    | IPD70R950CE    | IPS70R950CE       |             |              |

| 600                      |                | IPD70R600CE    | IPS70R600CE       |             |              |

#### Table 6 Portfolio 800 V CoolMOS™ CE

| R <sub>DS(on)</sub> [mΩ] | TO-220<br>FullPAK | TO-252<br>DPAK | TO-251<br>IPAK |

|--------------------------|-------------------|----------------|----------------|

| 2800                     |                   | IPD80R2K8CE    | IPU80R2K8CE    |

| 1400                     | IPA80R1K4CE       | IPD80R1K4CE    | IPU80R1K4CE    |

| 1000                     | IPA80R1K0CE       | IPD80R1K0CE    | IPU80R1K0CE    |

| 650                      | IPA80R650CE       |                |                |

| 460                      | IPA80R460CE       |                |                |

| 310                      | IPA80R310CE       |                |                |

#### References

### 7 References

- [1] T. Fujihira: "Theory of Semiconductor Superjunction Devices", Jpn. J. Appl. Phys., Vol.36, pp. 6254-6262, 1997

- [2] A.W. Ludikhuize: "A review of the RESURF technology", Proc. ISPSD 2000, pp. 11-18

- [3] X. B. Chen and C. Hu, "Optimum doping profile of power MOSFET's epitaxial Layer.", IEEE Trans. Electron Devices, vol. ED-29, pp. 985-987, 1982

- [4] G. Deboy, F. Dahlquist, T. Reiman and M. Scherf: "Latest generation of Superjunction power MOSFETs permits the use of hard-switching topologies for high power applications", Proceedings of PCIM Nürnberg, 2005, pp. 38-40

- [5] G. Deboy, L. Lin, R. Wu: "CoolMOS<sup>™</sup> C6 Mastering the Art of Slowness", Application Note revision 1.0 2009-12-21, pp. 5-6, <u>http://www.infineon.com/dgdl?folderId=5546d4694909da4801490a073396057b&fileId=db3a3043271faef</u> <u>d0127903d130171e1</u>

- [6] IFX: "CoolMOS<sup>™</sup> 900 V New 900 V class for superjunction devices A new horizon for SMPS and renewable energy applications", Application Note revision 1.0 2008-02, pp. 6, Figure 1

- [7] Dr. H. Kapels: "Superjunction MOS devices From device development towards system optimization", paper EPE 2009 Barcelona, ISBN 9789075815009, pp. 3

#### **Revision History**

#### Major changes since the last revision

| Page or Reference | Description of change |

|-------------------|-----------------------|

|                   | First Release         |

| p. 16/17          | Update of Portfolio   |

|                   |                       |

#### **Revision History**

#### Major changes since the last revision

| Page or Reference | Description of change |

|-------------------|-----------------------|

|                   |                       |

|                   |                       |

|                   |                       |

#### Trademarks of Infineon Technologies AG

µHVIC<sup>™</sup>, µIPM<sup>™</sup>, µPFC<sup>™</sup>, AU-ConvertIR<sup>™</sup>, AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CIPURSE<sup>™</sup>, CoolDP<sup>™</sup>, CoolGaN<sup>™</sup>, COOLIR<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CoolSiC<sup>™</sup>, DAVE<sup>™</sup>, DI-POL<sup>™</sup>, DirectFET<sup>™</sup>, DIBdde<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPACK<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, GaNpowIR<sup>™</sup>, HEXFET<sup>™</sup>, HIJFET<sup>™</sup>, HybridPACK<sup>™</sup>, iMOTION<sup>™</sup>, IRAM<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, LEDrivIR<sup>™</sup>, LITIX<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OPTIGA<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, PowIRaudio<sup>™</sup>, PowIRStage<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PROFET<sup>™</sup>, PRO-SIL<sup>™</sup>, RASIC<sup>™</sup>, REAL3<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, SPOC<sup>™</sup>, StrongIRFET<sup>™</sup>, SupIRBuck<sup>™</sup>, TEMPFET<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>, UHVIC<sup>™</sup>, XHP<sup>™</sup>, XMC<sup>™</sup>

Trademarks updated November 2015

#### Other Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2016-02-26 Published by Infineon Technologies AG

81726 Munich, Germany

© 2016 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference AN\_201411\_PL11\_008

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.