#### **MAX22192**

## Octal Industrial Digital Input with Diagnostics and Digital Isolation

#### **General Description**

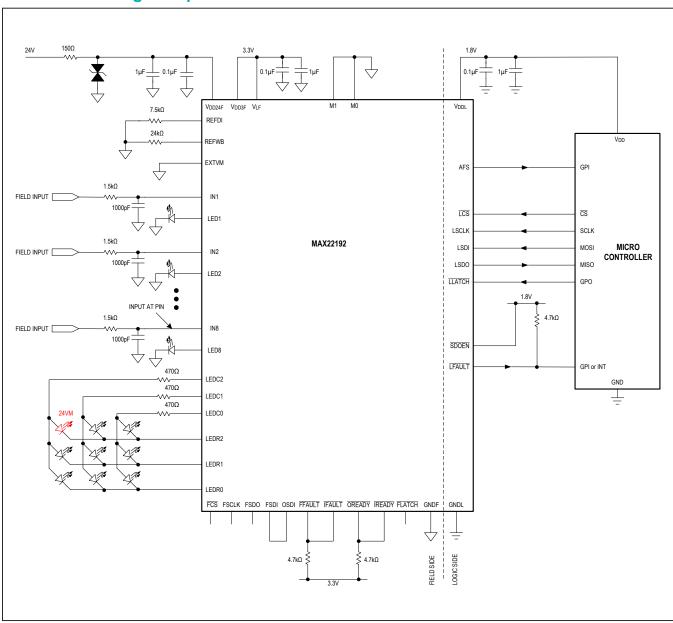

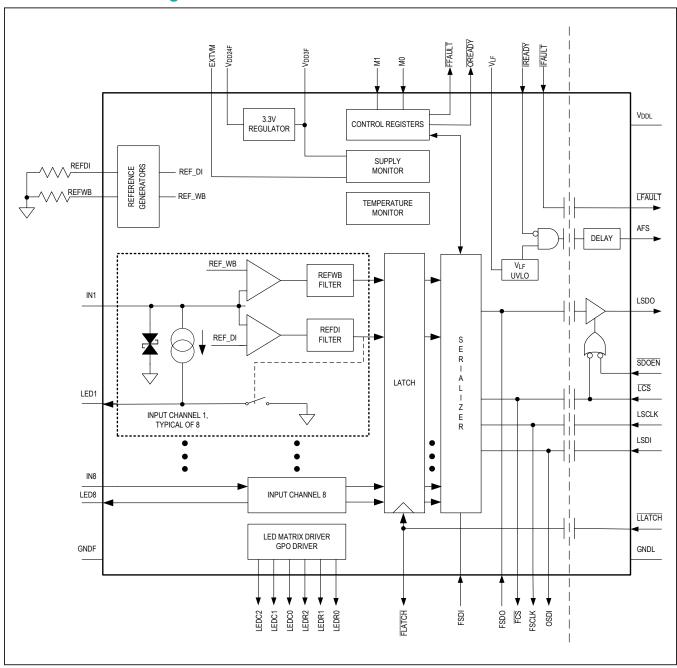

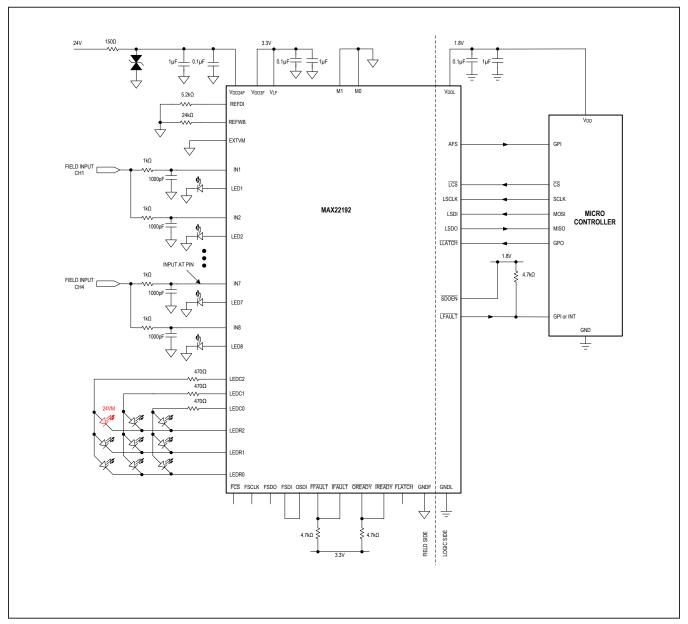

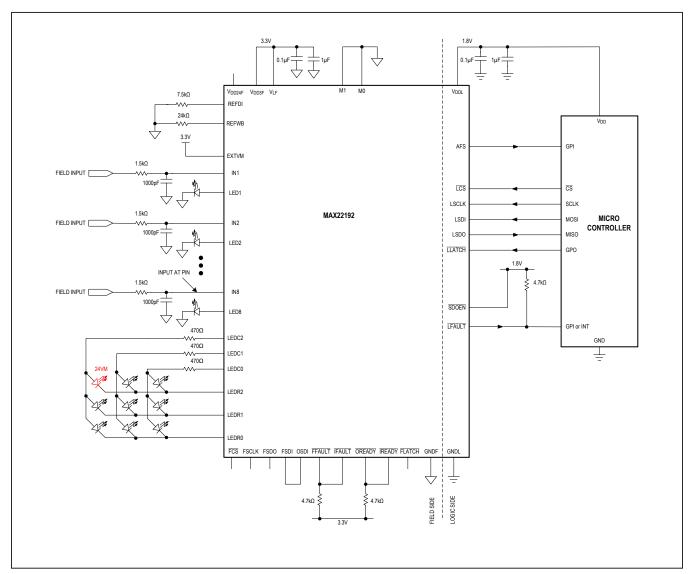

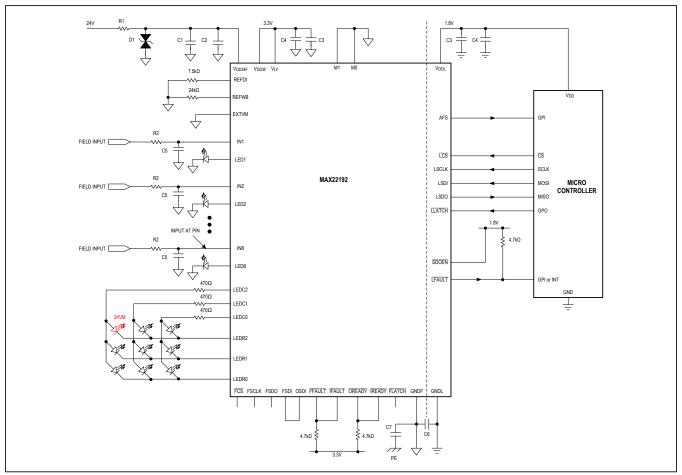

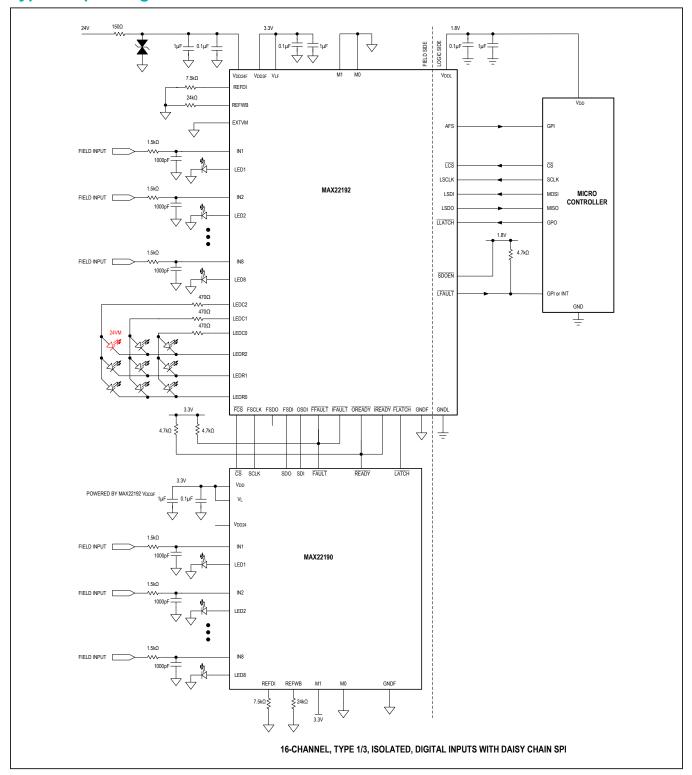

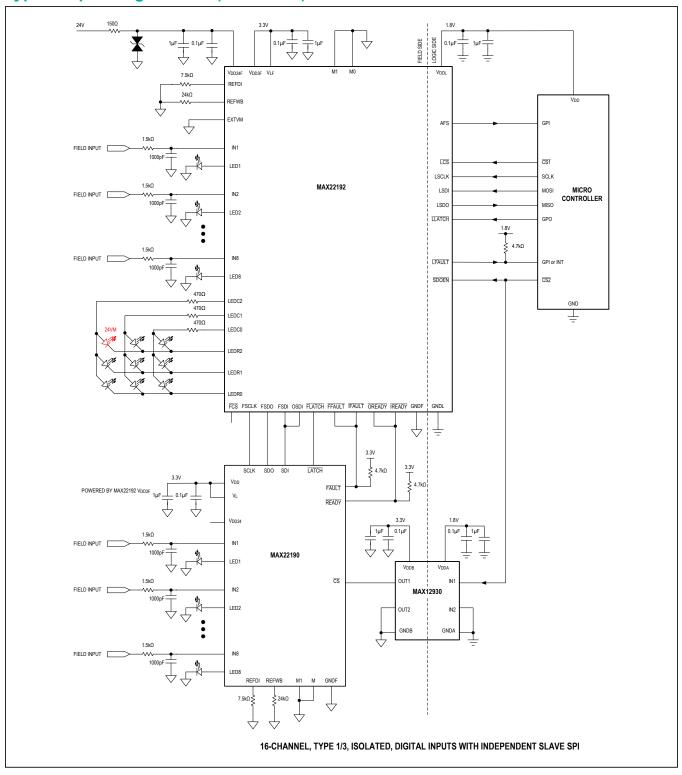

The MAX22192 is an IEC 61131-2 compliant industrial digital input device with integrated digital isolation. The MAX22192 translates eight, 24V current-sinking, industrial inputs to an isolated serialized SPI-compatible output that interfaces with 1.71V to 5.5V logic voltage. A current-setting resistor allows the MAX22192 to be configured for Type 1, Type 2, or Type 3 inputs. For proximity switches, the field-wiring is verified using the wire break feature. When wire break is enabled, the LFAULT output is asserted and a register flag set if the input current drops below the wire break threshold for more than 20ms. Additional diagnostics that assert LFAULT include: overtemperature protection, low 24V field supply, 24V field supply missing, and CRC communication error.

For robust operation in industrial environments, each input includes a programmable glitch filter. The filter delay on each channel can be independently programmed to one of eight values between 50µs and 20ms, or filter bypass.

The MAX22192 has an isolated 4-pin SPI interface, and in addition uses isolated  $\overline{\text{LLATCH}}$  input for synchronizing input data across multiple devices in parallel, and isolated  $\overline{\text{LFAULT}}$  output for instantly alerting the host of any diagnostic issues. The digital signals with a name starting with L are logic-side signals, and the digital signals with a name starting with F are field-side signals.

The MAX22192 field-side accepts a single 7V to 65V supply to the  $V_{DD24F}$  pin. When powered by the field supply, the MAX22192 generates a 3.3V output on the  $V_{DD3F}$  pin from an integrated LDO regulator, which can provide up to 25mA of current for external loads in addition to powering the MAX22192. Alternatively, the MAX22192 can be powered from a 3.0V to 5.5V supply connected to the  $V_{DD3F}$  pin. The logic-side of the MAX22192 is powered from a single 1.71V to 5.5V supply to the  $V_{DDL}$  pin to interface with 1.8V, 3.3V, or 5V logic levels.

The MAX22192 has an isolation rating of  $600V_{RMS}$  for 60 seconds and is available in a 70-pin GQFN package with 2.3mm clearance and creepage. The package material has a minimum comparative tracking index (CTI) of 600V, which gives it a group I rating in creepage tables.

#### **Benefits and Features**

- High Integration Reduces BOM Count and Board Space

- · Eight Input Channels with Serializer

- Integrated Isolation of 600V<sub>RMS</sub> for 60s (V<sub>ISO</sub>)

- Operates Directly from Field Supply (7V to 65V)

- · Compatible with 1.8V, 3.3V or 5V Logic

- 6mm x 10mm GQFN Package

- Reduced Power and Heat Dissipation

- · Accurate Input-Current Limiters

- Energyless Field-Side LED Drivers

- Fault Tolerant with Built-In Diagnostics

- Input Protection to ±40V with Low-Input Leakage Current

- · Wire-Break Detection

- · Integrated Field-Supply Voltage Monitors

- · Integrated Overtemperature Monitors

- 5-Bit CRC Code Generation for Error Detection

- Configurability Enables a Wide Range of Applications

- Configurable IEC 61131-2 Type 1, 2, 3 Inputs

- Configurable Input Current-Limiting from 0.5mA to 3.4mA

- · Selectable Input Glitch Filter

- Capable of Daisy-Chaining Other Field-Side Devices Sharing Isolated SPI

- Robust Design

- ±8kV Contact ESD and ±15kV Air-Gap ESD Using Minimum 1kΩ Resistor

- ±1kV Surge Tolerant Using Minimum 1kΩ Resistor

- -40°C to +125°C Ambient Operating Temperature

#### **Applications**

- Programmable Logic Controllers

- Industrial Automation

- Process Automation

#### **Safety Regulatory Approvals (Pending)**

- UL According to UL1577

- cUL According to CSA Bulletin 5A

<u>Ordering Information</u> and <u>Typical Operating Circuits</u> appear at end of data sheet.

#### **Isolated Octal Digital Input**

#### **Absolute Maximum Ratings**

| V <sub>DD3F</sub> , V <sub>LF</sub> to GNDF0.3V to +6V         | LSCLK, LCS, LSDI, LLATCH, SDOEN to GNDL0.3V to +6V |

|----------------------------------------------------------------|----------------------------------------------------|

| V <sub>DD24F</sub> to GNDF0.3V to +70V                         | LFAULT to GNDL0.3V to +6V                          |

| FSCLK, FCS, OSDI, FSDO to GNDF0.3V to (V <sub>LF</sub> + 0.3V) | LSDO, AFS to GNDL0.3V to (V <sub>DDL</sub> + 0.3V) |

| FLATCH to GNDF0.3V to (V <sub>LF</sub> + 0.3V)                 | Maximum Current for All Digital Output Pins20mA    |

| FSDI, IFAULT, IREADY to GNDF0.3V to +6V                        | Continuous Power Dissipation (70-GQFN)             |

| OREADY, FFAULT to GNDF0.3V to +6V                              | Multilayer Board T <sub>A</sub> = +70°C2286mW      |

| LEDC_, LEDR_ to GNDF0.3V to (V <sub>DD3F</sub> + 0.3V)         | Derate above +70°C28.6mW/°C                        |

| REFWB, REFDI to GNDF0.3V to (V <sub>DD3F</sub> + 0.3V)         | Operating Temperature Range40°C to +125°C          |

| M1, M0, EXTVM to GNDF0.3V to +6V                               | Maximum Junction Temperature+150°C                 |

| IN1 – IN8 to GNDF40V to +40V                                   | Storage Temperature Range65°C to +150°C            |

| LED1 – LED8 to GNDF0.3V to +6V                                 | Lead Temperature (soldering, 10s)+300°C            |

| V <sub>DDL</sub> to GNDL0.3V to +6V                            | Soldering (reflow)+260°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| PACKAGE TYPE: 70 GQFN                  |           |  |  |  |  |

|----------------------------------------|-----------|--|--|--|--|

| Package Code                           | R70610M+1 |  |  |  |  |

| Outline Number                         | 21-100252 |  |  |  |  |

| Land Pattern Number                    | 90-100111 |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   | )         |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 35°C/W    |  |  |  |  |

| Junction to Case $(\theta_{JC})$       | 2.9°C/W   |  |  |  |  |

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

#### **DC Electrical Characteristics**

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{DD24$

| PARAMETER                                                       | SYMBOL                 | С                                                              | ONDITIONS                                                                                             | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------------------|------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------|

| POWER SUPPLIES                                                  |                        |                                                                |                                                                                                       |      |      |      |       |

| Cumply Valtage                                                  | V <sub>DD24F</sub>     | Normal operation                                               | on                                                                                                    | 7    |      | 65   |       |

| Supply Voltage                                                  | V <sub>DD3F</sub>      | Powered from a V <sub>DD24F</sub> unconi                       | an external supply,<br>nected                                                                         | 3.0  |      | 5.5  | V     |

| Field Logic Supply Voltage                                      | V <sub>LF</sub>        | Referenced to                                                  | GNDF                                                                                                  | 3.0  |      | 5.5  | V     |

| Logic Supply Voltage                                            | $V_{\mathrm{DDL}}$     | Referenced to                                                  | GNDL                                                                                                  | 1.71 |      | 5.5  | V     |

| Field Supply Current of V <sub>DD24F</sub>                      | I <sub>DD24F</sub>     | V <sub>DD24F</sub> = 24V                                       | IN1 to IN8 = 0V, LED1<br>to LED8 = GNDF, SPI<br>static, REFDI = $7.5k\Omega$ ,<br>REFWB = $24k\Omega$ |      | 0.6  | 1.2  | mA    |

| Field Supply Current Powered<br>From V <sub>DD3F</sub>          | I <sub>DD3F</sub>      | V <sub>DD3F</sub> = 3.3V,<br>V <sub>DD24F</sub><br>unconnected | IN1 to IN8 = 0V, LED1<br>to LED8 = GNDF, SPI<br>static, REFDI = $7.5k\Omega$ ,<br>REFWB = $24k\Omega$ |      | 0.6  | 1.2  | mA    |

| Field Logic Supply Current                                      | I <sub>LF</sub>        | V <sub>LF</sub> - V <sub>GNDF</sub><br>= 5.5V                  | LCS = VDDL,         All logic pins static                                                             |      |      | 2    | mA    |

| Logic Supply Current                                            | I <sub>DDL</sub>       | V <sub>DDL</sub> -<br>V <sub>GNDL</sub> = 5.5V                 | LCS = V <sub>DDL</sub> , All logic pins static                                                        |      | 1.5  | 2    | mA    |

| V <sub>DD3F</sub> Undervoltage-Lockout<br>Threshold             | V <sub>UVLO</sub>      | V <sub>DD3F</sub> Rising                                       |                                                                                                       | 2.4  |      | 2.9  | V     |

| V <sub>DD3F</sub> Undervoltage-Lockout<br>Threshold Hysteresis  | V <sub>UVHYST</sub>    |                                                                |                                                                                                       |      | 0.07 |      | V     |

| V <sub>DD24F</sub> Undervoltage-Lockout<br>Threshold            | V <sub>UVLO24F</sub>   | V <sub>DD24F</sub> Rising                                      |                                                                                                       | 6    |      | 6.8  | V     |

| V <sub>DD24F</sub> Undervoltage-Lockout<br>Threshold Hysteresis | V <sub>UVHYST24F</sub> |                                                                |                                                                                                       |      | 0.5  |      | V     |

| V <sub>LF</sub> Undervoltage-Lockout<br>Threshold               | V <sub>UVLOVLF</sub>   | V <sub>LF</sub> Rising                                         |                                                                                                       | 0.9  |      | 1.66 | V     |

| V <sub>LF</sub> Undervoltage-Lockout<br>Threshold Hysteresis    | V <sub>UVHYSTVLF</sub> |                                                                |                                                                                                       |      | 0.07 |      | V     |

| V <sub>DDL</sub> Undervoltage-Lockout<br>Threshold              | V <sub>UVLOVL</sub>    | V <sub>DDL</sub> Rising                                        |                                                                                                       | 1.5  | 1.6  | 1.66 | V     |

| V <sub>DDL</sub> Undervoltage-Lockout<br>Threshold Hysteresis   | V <sub>UVHYSTVL</sub>  |                                                                |                                                                                                       |      | 45   |      | mV    |

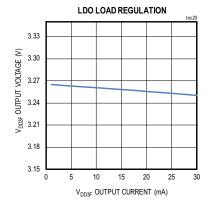

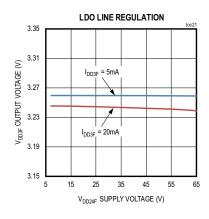

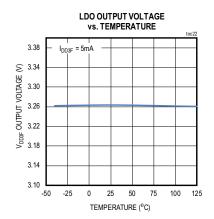

| Regulator Output Voltage                                        | V <sub>DD3F</sub>      | I <sub>LOAD</sub> = 1mA                                        |                                                                                                       | 3.0  | 3.3  | 3.6  | V     |

| Line Regulation                                                 | dV <sub>DD3FLINE</sub> | I <sub>LOAD</sub> = 1mA, \                                     | V <sub>DD24F</sub> = 12V to 24V                                                                       |      | 0    |      | mV    |

| Load Regulation                                                 | dV <sub>DD3FLOAD</sub> | I <sub>LOAD</sub> = 1mA to                                     | 10mA, V <sub>DD24F</sub> = 24V                                                                        |      | 4    |      | mV    |

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{DD24$

| PARAMETER                                        | SYMBOL                  | CONDITIONS                                                             | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------|-------------------------|------------------------------------------------------------------------|------|------|------|-------|

| Regulator Current Capability                     | I <sub>DD3F_CC</sub>    |                                                                        |      |      | 25   | mA    |

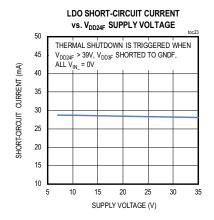

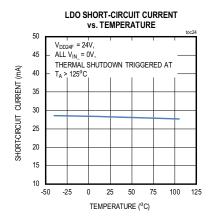

| Short-Circuit Current Limit                      | I <sub>DD24F_SC</sub>   | $V_{DD24F}$ current when $V_{DD3F}$ shorted to GNDF, $V_{DD24F}$ = 12V | 28   |      | 50   | mA    |

| Field-Side OREADY Threshold                      | VOREADY                 | V <sub>DD3F</sub> Rising, V <sub>DD24F</sub> Floating                  | 2.4  |      | 2.9  | V     |

| Field-Side OREADY Threshold Hysteresis           | VOREADY_<br>HYST        |                                                                        |      | 0.07 |      | V     |

| Field-Side OREADY Delay                          | t <sub>D_OREADY</sub>   | V <sub>DD3F</sub> valid to OREADY low                                  |      | 1    |      | ms    |

| Logic-Side AFS Delay                             | t <sub>D AFS</sub>      | IREADY low to AFS high                                                 |      | 100  |      | μs    |

| OURRLY AL ARMO                                   | _                       | IREADY high to AFS low                                                 |      | 100  |      |       |

| SUPPLY ALARMS                                    |                         |                                                                        |      |      | 47   |       |

| V <sub>DD24F</sub> UV Alarm On/Off               | V <sub>ALRMOFFUV</sub>  | V <sub>DD24F</sub> Rising, Undervoltage                                |      |      | 17   | V     |

| V <sub>DD24F</sub> UV Alarm Off/On               | V <sub>ALRMONUV</sub>   | V <sub>DD24F</sub> Falling, Undervoltage                               | 15   |      |      | V     |

| Glitch Filter for V <sub>DD24F</sub> UV          |                         |                                                                        |      | 3    |      | μs    |

| V <sub>DD24F</sub> VM Alarm On/Off               | V <sub>ALRMOFFVM</sub>  | V <sub>DD24F</sub> Rising, Missing Voltage                             |      |      | 13.9 | V     |

| V <sub>DD24F</sub> VM Alarm Off/On               | V <sub>ALRMONVM</sub>   | V <sub>DD24F</sub> Falling, Missing Voltage                            | 12.1 |      |      | V     |

| Glitch Filter for V <sub>DD24F</sub> VM          |                         |                                                                        |      | 3    |      | μs    |

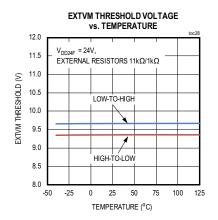

| EXTVM Threshold UV On/Off                        | V <sub>EXTOFFUV</sub>   | EXTVM Voltage Rising, Undervoltage                                     | 0.96 | 1    | 1.04 | V     |

| EXTVM Threshold UV Off/On                        | V <sub>EXTONUV</sub>    | EXTVM Voltage Falling, Undervoltage                                    | 0.93 | 0.97 | 1.01 | V     |

| EXTVM Threshold VM On/Off                        | V <sub>EXTOFFVM</sub>   | EXTVM Voltage Rising, Missing Voltage                                  | 0.77 | 0.81 | 0.84 | V     |

| EXTVM Threshold VM Off/On                        | V <sub>EXTONVM</sub>    | EXTVM Voltage Falling, Missing Voltage                                 | 0.74 | 0.79 | 0.82 | V     |

| EXTVM Selection Threshold                        | EXTVM <sub>SEL</sub>    |                                                                        |      | 0.3  |      | V     |

| EXTVM Selectable V <sub>DD24F</sub><br>Threshold | EXTVM <sub>VDD24F</sub> |                                                                        | 10   |      | 30   | V     |

| EXTVM Leakage Current                            | I <sub>L EXTVM</sub>    |                                                                        | -1   |      | +1   | μA    |

| TEMPERATURE ALARMS                               |                         |                                                                        |      |      |      |       |

| Overtemperature Alarm 1                          | T <sub>ALRM1</sub>      | ALRMT1 bit set in FAULT1 register                                      |      | 115  |      | °C    |

| Overtemperature Alarm 2                          | T <sub>ALRM2</sub>      | ALRMT2 bit set in FAULT1 register                                      |      | 140  |      | °C    |

| Overtemperature Alarm<br>Hysteresis              | T <sub>ALRM_HYS</sub>   |                                                                        |      | 10   |      | °C    |

| Thermal-Shutdown Threshold                       | T <sub>SHDN</sub>       | OTSHDN bit set in FAULT2 register                                      |      | 165  |      | °C    |

| Thermal-Shutdown Hysteresis                      | T <sub>SHDN_HYS</sub>   |                                                                        |      | 10   |      | °C    |

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{DD24$

| PARAMETER                            | SYMBOL                       | CONDITIONS                                                                     | MIN        | TYP       | MAX      | UNITS |

|--------------------------------------|------------------------------|--------------------------------------------------------------------------------|------------|-----------|----------|-------|

| WIRE-BREAK ALARMS                    | `                            |                                                                                |            |           |          |       |

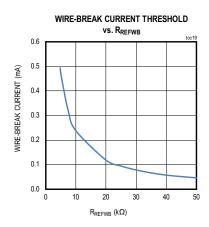

| REFWB Wire-Break Voltage             | V <sub>REFWB</sub>           | $R_{REFWB}$ = 5.2kΩ to 50kΩ                                                    |            | 0.61      |          | V     |

| REFWB Wire-Break Resistor            | R <sub>REFWB</sub>           | Nominal value                                                                  | 5.2        |           | 50       | kΩ    |

| W. D. L.O                            |                              | $R_{REFWB} = 5.2k\Omega$                                                       | 400        | 470       | 510      |       |

| Wire-Break Current Range             | I <sub>REFWB</sub>           | R <sub>REFWB</sub> = 50kΩ                                                      | 40         | 47        | 60       | μA    |

| PCB FAULT ALARMS                     | •                            |                                                                                |            |           |          |       |

| REFWB Pin Short Threshold            | I <sub>REFWBS</sub>          | RFWBS bit set in FAULT2 register                                               |            | 550       |          | μA    |

| REFWB Pin Open Threshold             | I <sub>REFWBO</sub>          | RFWBO bit set in FAULT2 register                                               |            | 6.6       |          | μA    |

| REFDI Pin Short Threshold            | I <sub>REFDIS</sub>          | RFDIS bit set in FAULT2 register                                               |            | 550       |          | μA    |

| REFDI Pin Open Threshold             | I <sub>REFDIO</sub>          | RFDIO bit set in FAULT2 register                                               |            | 6.6       |          | μA    |

| IC INPUTS (TYPES 1, 2, 3)            | •                            |                                                                                | ,          |           |          |       |

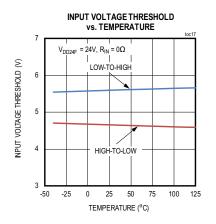

| Input Threshold Low-to-High          | V <sub>THP+</sub>            | IN1 to IN8                                                                     |            |           | 6        | V     |

| Input Threshold High-to-Low          | V <sub>THP</sub> -           | IN1 to IN8                                                                     | 4.4        |           |          | V     |

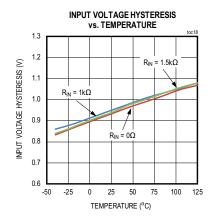

| Input Threshold Hysteresis           | VINPHYST                     | IN1 to IN8                                                                     |            | 0.8       |          | V     |

| LED On-State Current                 | I <sub>LEDON</sub>           | $R_{REFDI} = 7.5k\Omega$ , $V_{LED} = 3V$                                      | 1.5        |           |          | mA    |

| LED On-State Voltage                 | V <sub>LEDON</sub>           |                                                                                |            |           | 3        | V     |

| DI Leakage, Current Sources          |                              | IN1 to IN8 = 36V                                                               |            | 73        |          |       |

| Disabled                             | DI_LEAK                      | IN1 to IN8 = 24V                                                               |            | 42        |          | μA    |

| FIELD INPUTS                         |                              |                                                                                |            |           |          |       |

| REFDI Pin Voltage                    | V <sub>REFDI</sub>           | $R_{REFDI}$ from 5.2kΩ to 36kΩ                                                 |            | 0.61      |          | V     |

| REFDI Current-Limit Resistor         | R <sub>REFDI</sub>           | Nominal value                                                                  | 5.2        |           | 36       | kΩ    |

|                                      |                              | $R_{REFDI} = 5.2k\Omega$                                                       |            | 3.39      |          |       |

| Current-Limit Setting                | I <sub>INLIM</sub>           | $R_{REFDI} = 7.5k\Omega$                                                       |            | 2.35      |          | mA    |

|                                      |                              | R <sub>REFDI</sub> = 36kΩ                                                      |            | 0.48      |          |       |

| TYPE 1 and 3: External Series        | Resistor R <sub>IN</sub> = 1 | .5kΩ, R <sub>REFDI</sub> = 7.5kΩ, Wire-Break Detection                         | Off, unles | s otherwi | se noted |       |

| Input Current Limit                  | I <sub>INLIM</sub>           | $28V > V_{IN}$ at the pin > 5V,<br>LED on, R <sub>REFDI</sub> = 7.5kΩ (Note 2) | 2.10       | 2.35      | 2.60     | mA    |

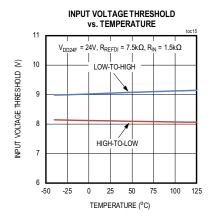

| Field Input Threshold<br>Low-to-High | V <sub>INF+</sub>            | $R_{REFDI}$ = 7.5kΩ, $R_{IN}$ = 1.5kΩ external series resistor                 |            |           | 9.9      | V     |

| Field Input Threshold<br>High-to-Low | V <sub>INF-</sub>            | $R_{REFDI}$ = 7.5kΩ, $R_{IN}$ = 1.5kΩ external series resistor                 | 7.4        |           |          | V     |

| Field Input Threshold<br>Hysteresis  | V <sub>INFHYST</sub>         | $R_{REFDI}$ = 7.5kΩ, $R_{IN}$ = 1.5kΩ external series resistor                 |            | 0.9       |          | V     |

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{DD24$

| PARAMETER                            | SYMBOL                           | COI                                                         | NDITIONS                                  | MIN                        | TYP       | MAX                      | UNITS |  |

|--------------------------------------|----------------------------------|-------------------------------------------------------------|-------------------------------------------|----------------------------|-----------|--------------------------|-------|--|

| TYPE 2: External Series Resisto      | or $R_{IN} = 1k\Omega$ , $R_{F}$ | REFDI = 5.2kΩ, Wire                                         | -Break Detection Off, unle                | ss otherw                  | ise noted |                          |       |  |

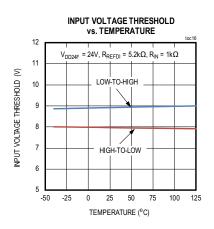

| Input Current Limit                  | I <sub>INLIM</sub>               | 28V > V <sub>IN</sub> _ at the LED on, R <sub>REFDI</sub> = | pin > 5V,<br>= 5.2kΩ (Note 2)             | 3.05                       | 3.39      | 3.71                     | mA    |  |

| Field Input Threshold<br>Low-to-High | V <sub>INF+</sub>                |                                                             | $R_{IN} = 1k\Omega$ external              |                            |           | 9.9                      | V     |  |

| Field Input Threshold<br>High-to-Low | V <sub>INF-</sub>                | $R_{REFDI}$ = 5.2kΩ, series resistor                        | $R_{IN} = 1k\Omega$ external              | 7.4                        |           |                          | V     |  |

| Field Input Threshold<br>Hysteresis  | VINFHYST                         | $R_{REFDI}$ = 5.2kΩ, series resistor                        | $R_{IN} = 1k\Omega$ external              |                            | 0.9       |                          | V     |  |

| FILTER DELAY                         |                                  |                                                             |                                           |                            |           |                          |       |  |

|                                      |                                  | FBP = 1: bypass f                                           | iltering                                  |                            | 2         |                          | μs    |  |

|                                      |                                  | FBP = 0, DELAY =                                            | = 0                                       |                            | 0.05      |                          |       |  |

|                                      |                                  | FBP = 0, DELAY =                                            | = 1                                       |                            | 0.1       |                          |       |  |

| Input Filter Delay                   |                                  | FBP = 0, DELAY =                                            | = 2                                       |                            | 0.4       |                          |       |  |

| (See DELAY[2:0] bits in FLT_         | t <sub>BOUNCE</sub>              | FBP = 0, DELAY =                                            | = 3                                       |                            | 0.8       |                          | ms    |  |

| Registers)                           | 200.102                          | FBP = 0, DELAY =                                            | = 4                                       |                            | 1.6       |                          |       |  |

|                                      |                                  | FBP = 0, DELAY =                                            | = 5                                       |                            | 3.2       |                          |       |  |

|                                      |                                  | FBP = 0, DELAY =                                            | = 6                                       |                            | 12.8      |                          |       |  |

|                                      |                                  | FBP = 0, DELAY =                                            | = 7                                       |                            | 20        |                          |       |  |

| Wire-Break Filter Delay              | t <sub>WBD</sub>                 |                                                             |                                           |                            | 20        |                          | ms    |  |

| LOGIC INTERFACE (FIELD-S             | 1                                | IC-SIDE)                                                    |                                           | Į.                         |           |                          | J     |  |

|                                      |                                  | LCS, LSCLK,<br>LSDI, LLATCH,                                | 2.25V ≤ V <sub>DDL</sub> ≤ 5.5V           | 0.7 x<br>V <sub>DDL</sub>  |           |                          |       |  |

| Input High Voltage                   | V <sub>IH</sub>                  | SDOEN, relative to GNDL                                     | 1.71V ≤ V <sub>DDL</sub> < 2.25V          | 0.75 x<br>V <sub>DDL</sub> |           |                          | V     |  |

|                                      |                                  |                                                             | AULT, IREADY, FCS, ATCH relative to GNDF  | 0.7 x<br>V <sub>LF</sub>   |           |                          |       |  |

|                                      |                                  | LCS, LSCLK,<br>LSDI, LLATCH,                                | 2.25V ≤ V <sub>DDL</sub> ≤ 5.5V           |                            |           | 0.8                      |       |  |

| Input Low Voltage                    | V <sub>IL</sub>                  | SDOEN, relative to GNDL                                     | 1.71V ≤ V <sub>DDL</sub> < 2.25V          |                            |           | 0.7                      | V     |  |

|                                      |                                  |                                                             | AULT, IREADY, FCS,  ATCH relative to GNDF |                            |           | 0.3 x<br>V <sub>LF</sub> |       |  |

| Output High Voltage (Note 3)         | V <sub>OH</sub> relative to      | FCS, FSCLK, FSI relative to GNDF,                           | OO, OSDI, FLATCH,<br>4mA source           | V <sub>LF</sub> - 0.4      |           |                          | .,,   |  |

|                                      |                                  | AFS, LSDO, relati<br>4mA source                             | ve to GNDL,                               | V <sub>DDL</sub> - 0.4     |           |                          | V     |  |

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{IN} = +24 \text{V}, C_L = 15 \text{pF} \text{ and } T_A = +25 ^{\circ}\text{C}. \text{ (Note 1)}$

| PARAMETER                                         | SYMBOL              | CONDITIONS                                                                       | MIN                      | TYP | MAX  | UNITS |

|---------------------------------------------------|---------------------|----------------------------------------------------------------------------------|--------------------------|-----|------|-------|

| Output Low Voltage (Note 3)                       | V                   | FCS, FSCLK, FSDO, OSDI, FLATCH, FFAULT, OREADY, relative to GNDF, 4mA source     |                          |     | 0.4  | V     |

|                                                   | V <sub>OL</sub>     | AFS, LSDO, LFAULT, relative to GNDL, 4mA source                                  |                          |     | 0.4  | V     |

| Input Pullup Resistance                           | R <sub>PU</sub>     | FCS, FLATCH, relative to GNDF                                                    |                          | 195 |      | kΩ    |

| Input Pulldown Resistance                         | R <sub>PD</sub>     | FSCLK, FSDI, M1, M0, relative to GNDF                                            |                          | 195 |      | K72   |

| Input Pullup Current (Note 3)                     | I <sub>PU</sub>     | IREADY pullup to V <sub>LF</sub> , LCS, LLATCH, SDOEN pullup to V <sub>DDL</sub> | -10                      | -5  | -1.5 | μA    |

| Input Pulldown Current (Note 3)                   | I <sub>PD</sub>     | FSDO, IFAULT pulldown to GNDF,<br>LSCLK, LSDI pulldown to GNDL                   | 1.5                      | 5   | 10   | μA    |

| Output High-Impedance<br>Leakage Current (Note 3) | I <sub>OL</sub>     | FFAULT, OREADY, relative to GNDF, LSDO, LFAULT, relative to GNDL                 | -1                       |     | +1   | μA    |

| LED/GPO DRIVER (LEDR_, L                          | EDC_)               |                                                                                  |                          |     |      |       |

| Output High Voltage                               | V <sub>OH_LED</sub> | LED on, I <sub>LED</sub> = 5mA                                                   | V <sub>LF</sub> -<br>0.3 |     |      | V     |

| Output Low Voltage                                | V <sub>OL_LED</sub> | LED on, I <sub>LED</sub> = 5mA                                                   |                          |     | 0.3  | V     |

| LED Driver Scan Rate                              | f <sub>LED</sub>    |                                                                                  |                          | 1   |      | kHz   |

#### **Dynamic Electrical Characteristics**

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{IN} = +24 \text{V}, C_L = 15 \text{pF} \text{ and } T_A = +25 ^{\circ}\text{C}. \text{ (Note 1)}$

| PARAMETER                                  | SYMBOL                 | CONDITIONS                                            | MIN | TYP  | MAX | UNITS |  |  |

|--------------------------------------------|------------------------|-------------------------------------------------------|-----|------|-----|-------|--|--|

| FIELD INPUT SAMPLING                       |                        |                                                       |     |      |     |       |  |  |

| Field Input Sampling Rate                  | f                      | Input Filter Bypass Mode                              |     | 1000 |     | kHz   |  |  |

|                                            | fin                    | Input Filter Delay Mode                               |     | 200  |     | KHZ   |  |  |

| Minimum Detectable Field Input Pulse Width | t <sub>PW</sub>        | No External Capacitors on Pins IN1 to IN8 (Note 2)    |     | 3    |     | μs    |  |  |

| LLATCH Delay                               | <sup>†</sup> LLATCH    | Assertion of LLATCH or LCS until input data is frozen |     | 75   |     | ns    |  |  |

| LFAULT Minimum Pulse Width                 | t <sub>PW_LFAULT</sub> | LFAULT low, pullup 4mA                                | 0.8 |      |     | μs    |  |  |

| DIGITAL ISOLATION                          |                        |                                                       |     |      |     |       |  |  |

| Common-Mode Transient<br>Immunity          | CMTI                   | I_ = GND_ (Note 4)                                    |     | 50   |     | kV/µs |  |  |

$V_{LF} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD3F} - V_{GNDF} = +3.0 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +7 \text{V to } +65 \text{V}, V_{DDL} - V_{GNDL} = +1.71 \text{V to } +5.5 \text{V}, V_{DD24F} - V_{GNDF} = +3.3 \text{V}, V_{DD3F} - V_{GNDF} = +3.3 \text{V}, V_{DD24F} - V_{GNDF} = +24 \text{V}, V_{DDL} - V_{GNDL} = +3.3 \text{V}, V_{IN} = +24 \text{V}, C_L = 15 \text{pF} \text{ and } T_A = +25 ^{\circ}\text{C}. \text{ (Note 1)}$

| PARAMETER                     | SYMBOL                    | CONDITIONS                                            | MIN | TYP | MAX | UNITS |

|-------------------------------|---------------------------|-------------------------------------------------------|-----|-----|-----|-------|

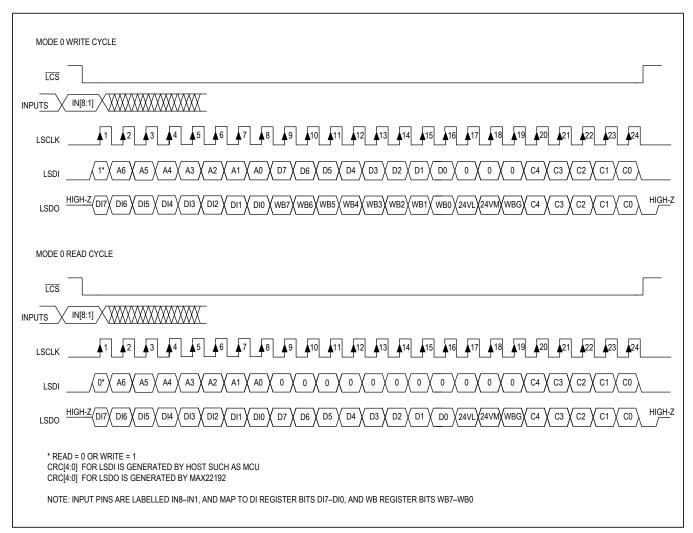

| SPI CHARACTERISTICS           |                           |                                                       |     |     |     |       |

| LSCLK Data Rate               | DR <sub>MAX</sub>         |                                                       |     |     | 5   | MHz   |

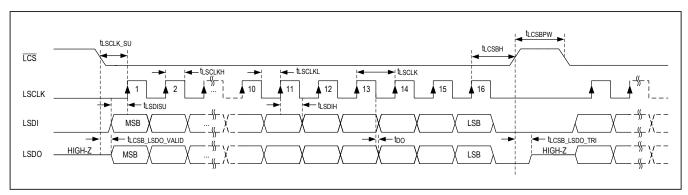

| LSCLK Pulse Width-High        | t <sub>LSCLKH</sub>       | See Figure 1                                          | 20  |     |     | ns    |

| LSCLK Pulse Width-Low         | t <sub>LSCLKL</sub>       | See Figure 1                                          | 20  |     |     | ns    |

| LSCLK Clock Period            | t <sub>LSCLK</sub>        | See Figure 1                                          | 120 |     |     | ns    |

| LCS Pulse Width               | t <sub>LCSPW</sub>        | See Figure 1                                          | 20  |     |     | ns    |

| LSDI-to-LSCLK Setup Time      | <sup>t</sup> LSDISU       | See Figure 1                                          | 5   |     |     | ns    |

| LSDI-to-LSCLK Hold Time       | t <sub>LSDIH</sub>        | See Figure 1                                          | 15  |     |     | ns    |

| LCS-Fall-to-LSCLK Rise Time   | tLSCLK_SU                 | See Figure 1                                          | 80  |     |     | ns    |

| LSCLK-Rise-to-LCS Rise Time   | <sup>t</sup> LCSH         | Rising edge of LSCLK to rising edge of LCS (Figure 1) | 40  |     |     | ns    |

| LSDO Enable Time              | tCS_LSDO_<br>VALID        | LCS falling to LSDO valid (Figure 1)                  |     |     | 70  | ns    |

| LSDO Disable Time             | t <sub>LCS_LSDO_TRI</sub> | LCS rising to LSDO High-Z (Figure 1)                  |     |     | 70  | ns    |

| Output Data Propagation Delay | t <sub>DO</sub>           | LSCLK falling to LSDO valid (Figure 1)                |     | 43  | 60  | ns    |

| LSDO Rise Time                | t <sub>R</sub>            | LSDO 10% to 90% rising                                |     | 4   |     | ns    |

| LSDO Fall Time                | t <sub>F</sub>            | LSDO 90% to 10% falling                               | ·   | 4   |     | ns    |

- Note 1: All units are production tested at T<sub>A</sub> = +25°C. Specifications over temperature are guaranteed by design.

- Note 2: External resistor REFDI is selected to set any desired current limit between 0.48mA and 3.39mA (typical values). The current limit accuracy of ±11% is guaranteed for values greater or equal to 2mA.

- **Note 3:** All currents into the device are positive. All currents out of the device are negative. All voltages are referenced to their respective ground (GNDF and GNDL), unless otherwise noted.

- Note 4: CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDF and GNDL.

Figure 1. SPI Timing Diagram

#### **Insulation Characteristics**

| PARAMETER                                     | SYMBOL           | CONDITIONS                                             | VALUE              | UNITS            |

|-----------------------------------------------|------------------|--------------------------------------------------------|--------------------|------------------|

| Maximum Withstand Isolation Voltage           | V <sub>ISO</sub> | f <sub>SW</sub> = 60Hz, duration = 60s (Note 5, 6)     | 600                | V <sub>RMS</sub> |

|                                               |                  | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C          | > 10 <sup>12</sup> |                  |

| Insulation Resistance                         | R <sub>IO</sub>  | V <sub>IO</sub> = 500V, 100°C ≤ T <sub>A</sub> ≤ 125°C | > 10 <sup>11</sup> | Ω                |

|                                               |                  | V <sub>IO</sub> = 500V at T <sub>S</sub> = 150°C       | > 109              |                  |

| Barrier Capacitance Field-Side to Logic-Side  | CIO              | f <sub>SW</sub> = 1MHz (Note 7)                        | 2                  | pF               |

| Minimum Creepage Distance                     | CPG              |                                                        | 2.3                | mm               |

| Minimum Clearance Distance                    | CLR              |                                                        | 2.3                | mm               |

| Internal Clearance                            |                  | Distance through insulation                            | 0.015              | mm               |

| Comparative Tracking Index                    | CTI              | Material Group I (IEC 60112)                           | > 600              |                  |

| Climate Category                              |                  |                                                        | 40/125/21          |                  |

| Pollution Degree<br>(Table 1 of DIN VDE 0110) |                  |                                                        | 2                  |                  |

Note 5: V<sub>ISO</sub> is defined by the IEC 60747-5-5 standard.

Note 6: Product is qualified at V<sub>ISO</sub> for 60s and 100% production tested at 120% of V<sub>ISO</sub> for 1s.

Note 7: Capacitance is measured with all logic pins on field-side and logic-side tied together.

#### **ESD Protection**

| PARAMETER | SYMBOL | CONDITIONS                                                                                       | VALUE | UNITS |

|-----------|--------|--------------------------------------------------------------------------------------------------|-------|-------|

| ESD       |        | Human Body Model, All Field-Side Pins Referenced to GNDF, All Logic-Side Pins Referenced to GNDL | ±2    | kV    |

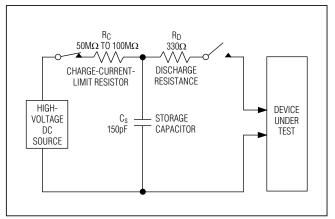

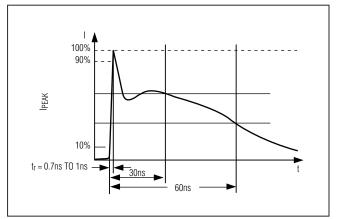

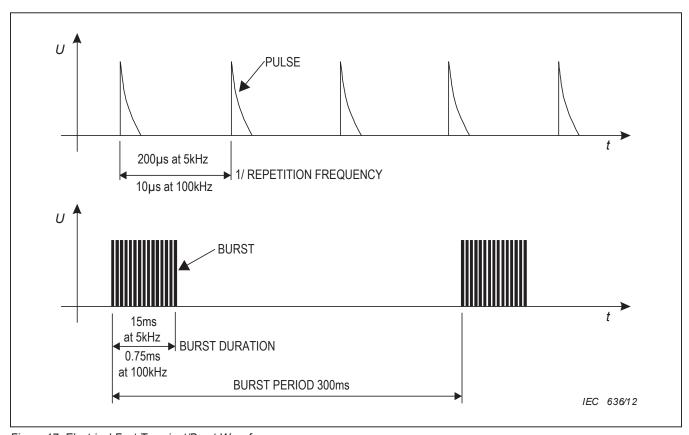

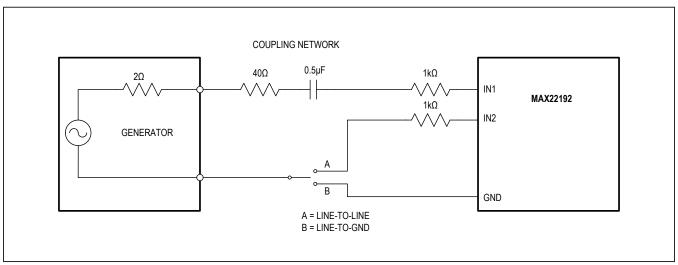

#### **ESD** and **EMC** Characteristics

| PARAMETER SYMBOL |              | CONDITIONS                                                                                                       | VALUE | UNITS |

|------------------|--------------|------------------------------------------------------------------------------------------------------------------|-------|-------|

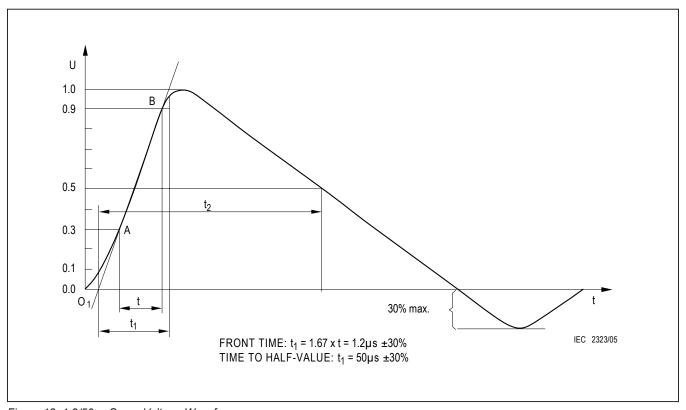

| Surge            | Line-to-Line | IEC 61000-4-5, 1.2/50 $\mu$ s pulse, minimum 1k $\Omega$ resistor in series with IN1 - IN8, with respect to GNDF | ±2    | kV    |

|                  | Line-to-GNDF | IEC 61000-4-5, 1.2/50 $\mu$ s pulse, minimum 1k $\Omega$ resistor in series with IN1 - IN8, with respect to GNDF | ±1    | KV    |

| ESD              | Contact      | IEC 61000-4-2, minimum $1k\Omega$ resistor in series with IN1- IN8, with respect to GNDF                         | ±8    | kV    |

|                  | Air-Gap      | IEC 61000-4-2, minimum $1k\Omega$ resistor in series with IN1- IN8, with respect to GNDF                         | ±15   | KV    |

Maxim Integrated | 10 www.maximintegrated.com

#### **Safety Limits**

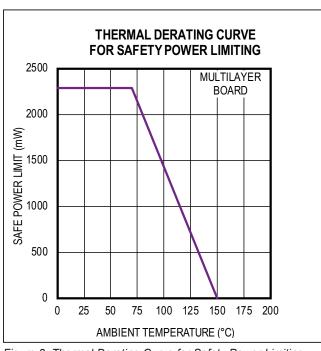

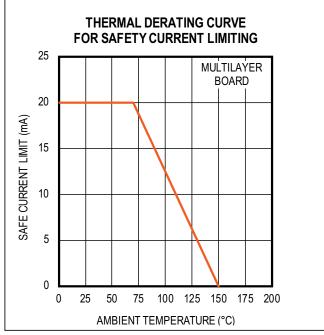

Damage to the IC can result in a low-resistance path to ground or to the supply and, without current limiting, the MAX22192 could dissipate an excessive amount of power. Excessive power dissipation can damage the die and result in damage to the isolation barrier, potentially causing downstream issues. Table 1 shows the safety limits for the MAX22192.

The maximum safety temperature (T<sub>S</sub>) for the device is the 150°C maximum junction temperature specified in the <u>Absolute Maximum Ratings</u>. The power dissipation (P<sub>D</sub>) and junction-to-ambient thermal impedance ( $\theta_{JA}$ ) determine

the junction temperature. Thermal impedance values ( $\theta_{JA}$  and  $\theta_{JC}$ ) are available in the <u>Package Information</u> section of the data sheet. The power dissipation ( $P_D$ ) can be calculated as:

$$P_D = \sum (V_{IN} \times I_{IN}) + V_{DD24F} \times I_{DD24F} + V_{LF} \times I_{LF} + V_{DDL} \times I_{DDL}$$

Calculate the junction temperature (T<sub>J</sub>) as:

$$T_J = T_A + (P_D \times \theta_{JA})$$

<u>Figure 2</u> and <u>Figure 3</u> show the thermal derating curve for safety limiting the power and the current of the device. Ensure that the junction temperature does not exceed 150°C.

Figure 2. Thermal Derating Curve for Safety Power Limiting

Figure 3. Thermal Derating Curve for Safety Current Limiting

#### Table 1. Safety Limiting Values for the MAX22192

| PARAMETER                      | SYMBOL         | TEST CONDITIONS                                                 | MAX  | UNIT |

|--------------------------------|----------------|-----------------------------------------------------------------|------|------|

| Safety Current on Any Pin      | IS             | T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C, Multilayer Board | 20   | mA   |

| Total Safety Power Dissipation | PS             | T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C, Multilayer Board | 2286 | mW   |

| Maximum Safety Temperature     | T <sub>S</sub> |                                                                 | 150  | °C   |

#### **Typical Operating Characteristics**

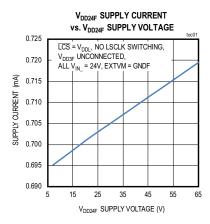

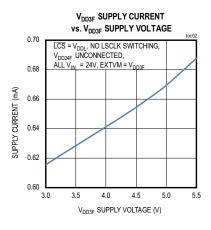

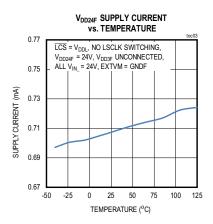

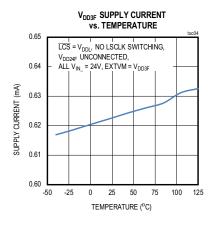

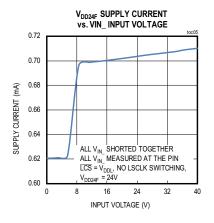

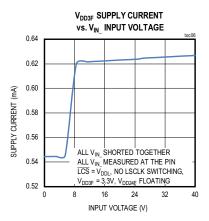

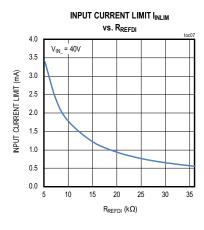

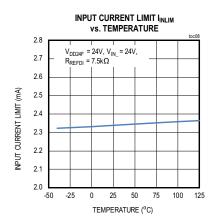

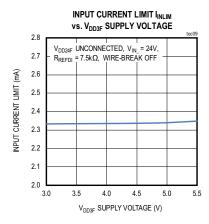

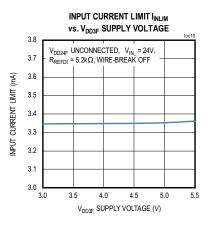

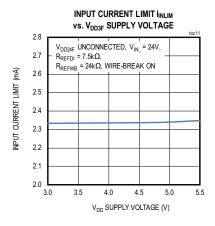

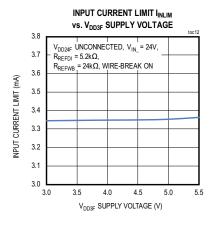

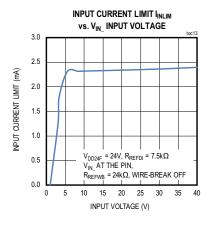

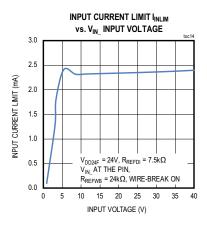

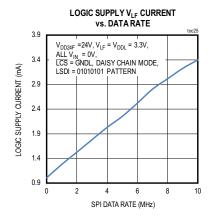

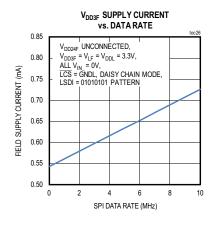

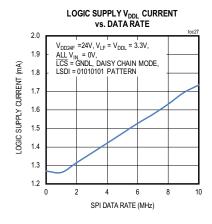

$V_{DD24F} = +24V, V_{DD3F} = V_{LF} = +3.3V, V_{DDL} = +3.3V, T_{A} = +25^{\circ}C, R_{REFDI} = 7.5k\Omega, R_{REFWB} = 24k\Omega, R_{IN} = 1.5k\Omega, unless otherwise noted$

#### **Typical Operating Characteristics (continued)**

$V_{DD24F} = +24V, \ V_{DD3F} = V_{LF} = +3.3V, \ V_{DDL} = +3.3V, \ T_{A} = +25^{\circ}C, \ R_{REFDI} = 7.5k\Omega, \ R_{REFWB} = 24k\Omega, \ R_{IN} = 1.5k\Omega, \ unless otherwise noted.$

www.maximintegrated.com

#### **Typical Operating Characteristics (continued)**

$V_{DD24F} = +24V, \ V_{DD3F} = V_{LF} = +3.3V, \ V_{DDL} = +3.3V, \ T_A = +25^{\circ}C, \ R_{REFDI} = 7.5k\Omega, \ R_{REFWB} = 24k\Omega, \ R_{IN} = 1.5k\Omega, \ unless \ otherwise noted.$

#### **Typical Operating Characteristics (continued)**

$V_{DD24F} = +24V, \ V_{DD3F} = V_{LF} = +3.3V, \ V_{DDL} = +3.3V, \ T_{A} = +25^{\circ}C, \ R_{REFDI} = 7.5k\Omega, \ R_{REFWB} = 24k\Omega, \ R_{IN} = 1.5k\Omega, \ unless \ otherwise noted.$

#### **Pin Configurations**

| TOP VIEW | Α              | В                        | С          | D                 | E          | F                 | G                         | Н              |          | J                          | K               |

|----------|----------------|--------------------------|------------|-------------------|------------|-------------------|---------------------------|----------------|----------|----------------------------|-----------------|

| 1        | +              | 0                        | $\bigcirc$ | <u> </u>          | 0          | <u></u>           | $\bigcirc$                | <u></u>        |          | 0                          | 0               |

| 2        | REFWB () LEDR0 | GNDF<br>()<br>REFDI      | IN8        | IN7<br>()<br>LED7 | IN6        | IN5<br>()<br>LED5 | V <sub>LF</sub> () FFAULT | IREADY  OREADY | MAX22192 | GNDL<br>()                 | NC<br>()<br>AFS |

| 3        | ()<br>LEDR0    | ()<br>LEDR1              | ()<br>GNDF | ()<br>GNDF        | ()<br>GNDF | ()<br>FSDO        | ()<br>IFAULT              | ()<br>GNDF     |          | V <sub>DDL</sub> () LFAULT | $\bigcirc$      |

| 4        | ()<br>LEDC0    | ()<br>LEDC1              | GNDF       | ()<br>GNDF        | $\bigcirc$ | $\bigcirc$        | ()                        | ()<br>GNDF     |          | LLATCH                     | $\bigcirc$      |

| 5        | ()<br>LEDC2    | ()<br>M1                 | ()<br>GNDF | ()<br>GNDF        | ()<br>GNDF | ()<br>FSCLK       | $\bigcirc$                | ()<br>GNDF     |          | ()<br>LSCLK                | $\bigcirc$      |

| 6        | ()<br>M0       | ()<br>V <sub>DD24F</sub> | ()<br>LED1 | ()<br>LED2        | ()<br>LED3 | ()<br>LED4        | ()<br>FCS                 | ()<br>GNDF     |          | ()<br>GNDL                 | SDOEN           |

| 7        | ()<br>VDD24F   | ()<br>VDD3F              | O<br>IN1   | ()<br>IN2         | ()<br>IN3  | ()<br>IN4         | ()<br>EXTVM               | ()<br>GNDF     |          | NC NC                      | )<br>NC         |

|          |                |                          |            |                   | (          |                   | QFN<br>x 10mr             | m)             |          |                            |                 |

#### **Pin Description**

| PIN                                | NAME               | FUNCTION                                                                                                                                                                                                   | REFERENCE |  |  |  |  |  |  |

|------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

| POWER SUPPLY                       | POWER SUPPLY       |                                                                                                                                                                                                            |           |  |  |  |  |  |  |

| J2                                 | V <sub>DDL</sub>   | Logic-Side Power Supply. Bypass with 0.1µF ceramic capacitor as close as possible to the pin. Set logic level for all logic-side signals.                                                                  | GNDL      |  |  |  |  |  |  |

| J1, J6                             | GNDL               | Power and Signal Ground for Logic-Side                                                                                                                                                                     | -         |  |  |  |  |  |  |

| A7, B6                             | V <sub>DD24F</sub> | 24V Field Supply. Bypass with 0.1 $\mu$ F capacitor in parallel with 1 $\mu$ F capacitor to GNDF. If powering the MAX22192 from V <sub>DD3F</sub> , leave V <sub>DD24F</sub> unconnected.                  | GNDF      |  |  |  |  |  |  |

| В7                                 | V <sub>DD3F</sub>  | 3.3V Field-Side Output. Internal LDO output when powered from $V_{DD24F}$ , or 3.0V–5.5V supply input when $V_{DD24F}$ is unconnected. Bypass to GNDF with 0.1µF capacitor in parallel with 1µF capacitor. | GNDF      |  |  |  |  |  |  |

| G1                                 | V <sub>LF</sub>    | Field-Side Logic Interface Supply. Bypass with 0.1µF ceramic capacitor as close as possible to the pin. Set logic level for all field-side digital signals.                                                | GNDF      |  |  |  |  |  |  |

| B1, C3-C5, D3-<br>D5, E3-E5, H3-H7 | GNDF               | Power and Signal Ground for Field-Side                                                                                                                                                                     | -         |  |  |  |  |  |  |

#### **Pin Description (continued)**

| PIN            | NAME       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             | REFERENCE |

|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| LOGIC-SIDE DIG | SITAL PINS |                                                                                                                                                                                                                                                                                                                                                                                                                      | I         |

| K5             | <u>ICS</u> | Logic-Side Chip-Select Input. Input to $\overline{\text{CS}}$ Isolation Channel. Has a weak internal pullup to $V_{DDL}$ . Drive $\overline{\text{LCS}}$ low to enable LSDO and assert $\overline{\text{FCS}}$ low, which latches input states and enable the field-side SPI interface.                                                                                                                              | GNDL      |

| J5             | LSCLK      | Logic-Side Serial Clock Input to SCLK Isolation Channel. Has a weak internal pulldown.                                                                                                                                                                                                                                                                                                                               | GNDL      |

| K4             | LSDI       | Logic-Side Serial Data Input to SDI Isolation Channel. Has a weak internal pulldown. Data is clocked into LSDI on the rising edge of LSCLK. OSDI is the output of SDI channel on the field-side.                                                                                                                                                                                                                     | GNDL      |

| КЗ             | LSDO       | Logic-Side Serial Data Output. Becomes High-Z when $\overline{\text{LCS}}$ and $\overline{\text{SDOEN}}$ are both high. LSDO is enabled when either $\overline{\text{LCS}}$ or $\overline{\text{SDOEN}}$ is low. Data is updated on the falling edge of LSCLK.                                                                                                                                                       | GNDL      |

| J4             | LLATCH     | Logic-Side Input to LATCH Isolation Channel. Has a weak internal pullup to V <sub>DDL</sub> .  Drive LLATCH low to assert FLATCH low, which latches all eight input states.                                                                                                                                                                                                                                          | GNDL      |

| J3             | LFAULT     | Logic-Side Open-Drain Output of FAULT Isolation Channel. LFAULT goes low to indicate fault conditions on the field-side. Connect a pullup resistor to V <sub>DDL</sub> .                                                                                                                                                                                                                                             | GNDL      |

| K6             | SDOEN      | LSDO Enable. Has a weak internal pullup to V <sub>DDL</sub> . Drive SDOEN low to enable LSDO when sharing the isolation with other field-side SPI devices in the independent slave configuration; drive SDOEN high and allow LCS to enable LSDO in the standalone or daisy-chain configuration.                                                                                                                      | GNDL      |

| K2             | AFS        | Field-Side Active. AFS is high to indicate field-side is operating normally and IREADY is low. When field-side is not powered, AFS is set low and all logic-side outputs are in a default state (IFAULT is low and LSDO is low when enabled). A nominal 100µs delay is added between the detection of field-side power and the assertion of AFS to ensure power supply is settled and a minimum pulse width for AFS. | GNDL      |

| K1, J7, K7     | NC         | Not Connected. Leave it unconnected, or connect to GNDL                                                                                                                                                                                                                                                                                                                                                              | -         |

| FIELD-SIDE DIG | ITAL PINS  |                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| G6             | FCS        | Output of $\overline{\text{CS}}$ Isolation Channel and Field-Side Chip-Select Input. All digital input states are latched and field-side SPI interface is active when $\overline{\text{FCS}}$ is low. Connect the $\overline{\text{CS}}$ of other field-side SPI devices to $\overline{\text{FCS}}$ when sharing the MAX22192 isolation in the daisy-chain configuration.                                            | GNDF      |

| F5             | FSCLK      | Output of SCLK Isolation Channel and Field-Side Serial Clock Input. Connect the SCLK of other field-side SPI devices to FSCLK when sharing the MAX22192 isolation.                                                                                                                                                                                                                                                   | GNDF      |

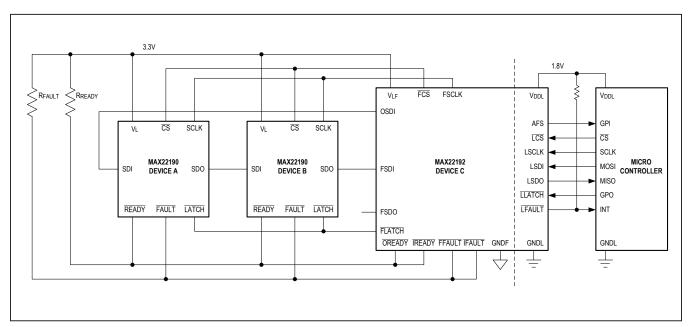

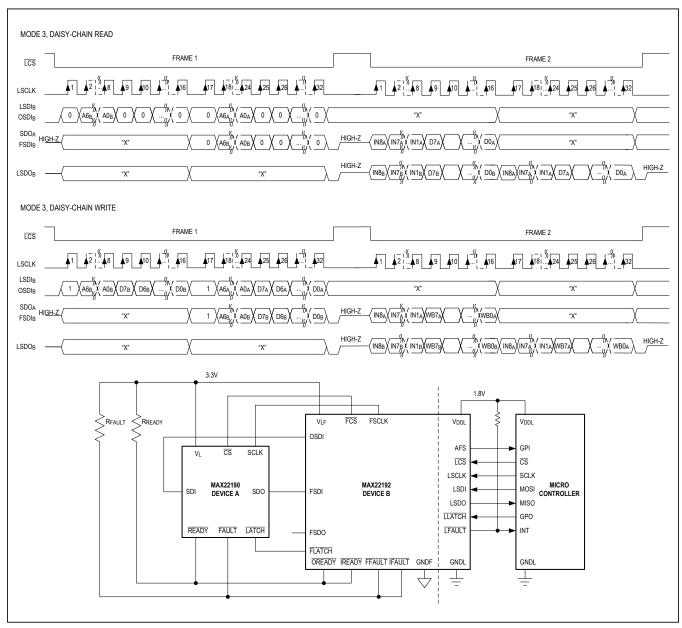

| G5             | OSDI       | Output of SDI Isolation Channel. In the standalone SPI or independent slave configuration, connect OSDI to FSDI. In the daisy-chain configuration, connect OSDI to the SDI of the first field-side SPI device. The MAX22192 is the last device in the chain. Refer to Figure 12 for details.                                                                                                                         | GNDF      |

#### **Pin Description (continued)**

| PIN      | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | REFERENCE |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| G4       | FSDI     | Field-Side Serial Data Input. Has a weak internal pulldown. Data is clocked into FSDI on the rising edge of FSCLK. In the standalone SPI or independent slave configuration, connect OSDI to FSDI. In the daisy-chain configuration, connect FSDI to the SDO of the next to last field-side SPI device. The MAX22192 is the last device in the chain. Refer to Figure 12 for details.                                                                                                                                                                                    | GNDF      |

| F3       | FSDO     | Field-Side Serial Data Output and Input to SDO Isolation Channel. Data is updated on the falling edge of FSCLK. When FCS is high, FSDO is high-impedance. In the SPI independent slave configuration, connect the SDO of other field-side SPI devices to FSDO. In the daisy-chain configuration, the MAX22192 is the last device in the chain since FSDO is internally connected to the isolation. Refer to Figure 12 for details.                                                                                                                                       | GNDF      |

| F4       | FLATCH   | Output of LATCH Isolation Channel and Field-Side LATCH Input. FLATCH and FCS control the data latch at the input of the field-side serializer. The latch is transparent when both FCS and FLATCH are high. The input data is frozen on the falling edge of either FLATCH or FCS. Connect FLATCH to the LATCH input of other field-side SPI devices when sharing the MAX22192 isolation.                                                                                                                                                                                  | GNDF      |

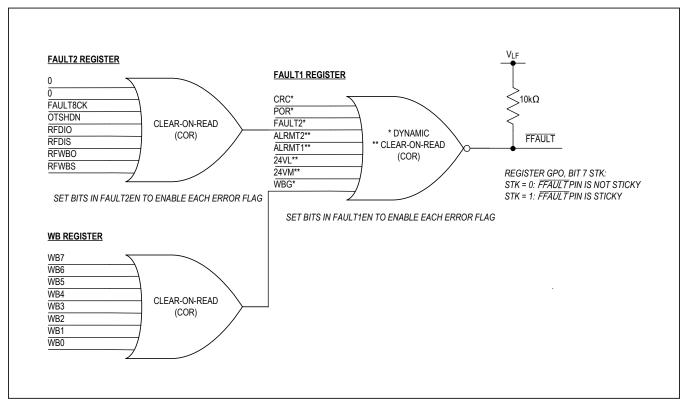

| G2       | FFAULT   | Field-Side Open-Drain Active-Low Fault Indicator. Connect a pullup resistor to $V_{LF}$ . Connect $\overline{F}\overline{F}\overline{A}\overline{U}\overline{L}\overline{T}$ to isolate $\overline{F}\overline{A}\overline{U}\overline{L}\overline{T}$ signal. $\overline{F}\overline{F}\overline{A}\overline{U}\overline{L}\overline{T}$ goes low to indicate that one or more of the flags in the FAULT registers have been set. The faults include: supply monitors, temperature monitors, CRC error, wire-break detection, and short or open at REFDI or REFWB pins. | GNDF      |

| G3       | ĪFAULT   | Field-Side Input to FAULT Isolation Channel. Has a weak internal pulldown. Connect FFAULT and FAULT of other field-side SPI devices to IFAULT when sharing the MAX22192 isolation.                                                                                                                                                                                                                                                                                                                                                                                       | GNDF      |

| H2       | OREADY   | Field-Side Open-Drain Active-Low Ready Indicator. OREADY goes low indicating the field-side is powered up and ready for operation. Connect OREADY to IREADY to isolate READY signal. Connect a pullup resistor to V <sub>LF</sub> .                                                                                                                                                                                                                                                                                                                                      | GNDF      |

| H1       | IREADY   | Field-Side Ready Input to READY Isolation Channel. Has a weak internal pullup. Assert IREADY low when field-side is ready for operation. When IREADY is high, AFS is low and logic-side outputs are in their default state (LFAULT is low and LSDO is low when enabled). When IREADY is low, AFS is high and all isolation channels operate normally. Connect OREADY and READY of other field-side SPI devices to IREADY when sharing the MAX22192 isolation.                                                                                                            | GNDF      |

| B5<br>A6 | M1<br>M0 | SPI Control Mode. See <u>Table 3</u> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GNDF      |

| Λ0       | IVIU     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

#### **Pin Description (continued)**

| PIN                               | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REFERENCE |

|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| FIELD INPUT PI                    | NS               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| C7, D7, E7, F7,<br>F1, E1, D1, C1 | IN1 - IN8        | Field Digital Inputs. For Type 1 and Type 3 inputs, place a $1.5k\Omega$ pulse withstanding resistor between the field input and IN_ pin. For Type 2 inputs, place a $1k\Omega$ pulse withstanding resistor between field input and IN_ pin.                                                                                                                                                                                                                                              | GNDF      |

| C6, D6, E6, F6,<br>F2, E2, D2, C2 | LED1 -<br>LED8   | Energyless LED Driver Outputs. Connect to GNDF if LEDs are not used.                                                                                                                                                                                                                                                                                                                                                                                                                      | GNDF      |

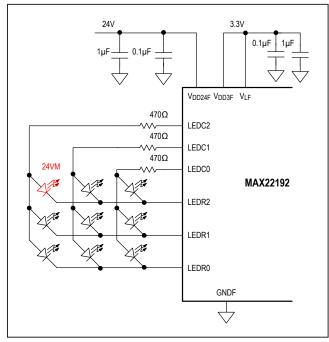

| A2, B3, A3                        | LEDR0 -<br>LEDR2 | Open-Drain Auxiliary LED Matrix Row 0–2 Output, or Push-Pull GPO Output. Connect to LED cathode when configured as LED output. Connect a resistor in series with the LED between LEDR_ and LEDC Refer to the <i>GPO Register</i> and <i>LED Register</i> for details.                                                                                                                                                                                                                     | GNDF      |

| A4, B4, A5                        | LEDC0 -<br>LEDC2 | Open-Drain Auxiliary LED Matrix Column 0–2 Output, or Push-Pull GPO Output. Connect to LED anode when configured as LED output. Connect a resistor in series with the LED between LEDR_ and LEDC Refer to the <i>GPO Register</i> and <i>LED Register</i> for details.                                                                                                                                                                                                                    | GNDF      |

| B2                                | REFDI            | Digital Input Current-Limit Reference Resistor. For Type 1 and Type 3 inputs, place a 7.5k $\Omega$ resistor from REFDI to GNDF. For Type 2 inputs, place a 5.2k $\Omega$ resistor from REFDI to GNDF.                                                                                                                                                                                                                                                                                    | GNDF      |

| A1                                | REFWB            | Wire-Break Current-Limit Reference Resistor. Connect a $5.2k\Omega$ – $50k\Omega$ resistor from REFWB to GNDF to set the wire-break threshold. See the <u>Wire-Break Detection</u> section for details.                                                                                                                                                                                                                                                                                   | GNDF      |

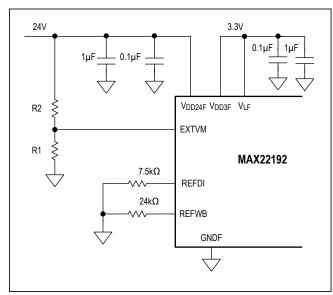

| G7                                | EXTVM            | External $V_{DD24F}$ Supply Monitoring Input. Connect EXTVM to GNDF to use internal thresholds for both $V_{DD24F}$ undervoltage and voltage missing monitoring. Connect EXTVM to external resistive divider to set the external thresholds for both $V_{DD24F}$ undervoltage and voltage missing monitoring. Connect EXTVM to $V_{DD3F}$ to disable $V_{DD24F}$ voltage monitoring, while 24VM and 24VL faults are always off. This is useful when the device is powered by $V_{DD3F}$ . | GNDF      |

#### **Functional Block Diagram**

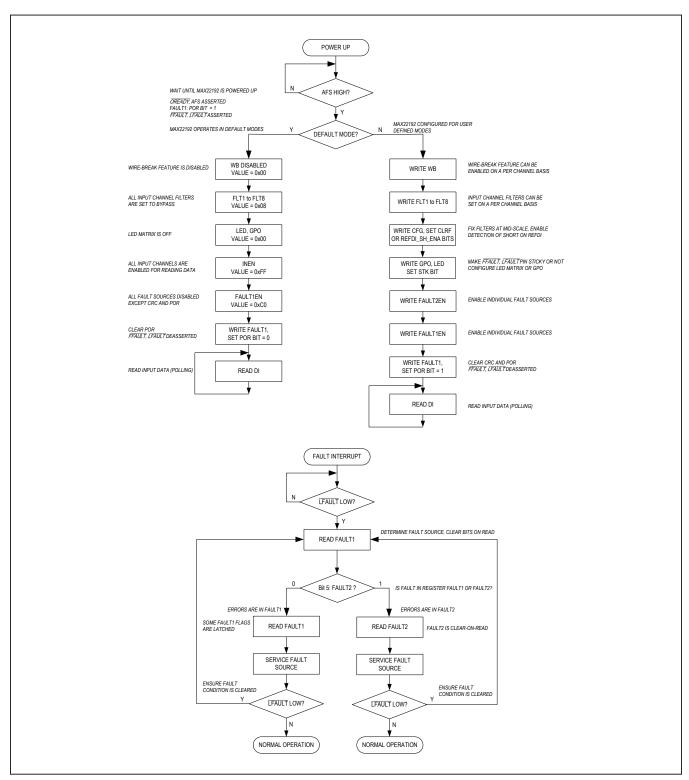

#### **Detailed Description**

The MAX22192 senses the state (on, high or off, low) of eight digital inputs. The voltages at the IN1 to IN8 input pins are compared against internal references to determine whether the sensor is ON (logic 1) or OFF (logic 0). All eight inputs are simultaneously latched by the assertion of either LLATCH or LCS, and the data made available in a serialized format using the isolated SPI interface. Placing a 7.5k $\Omega$  current-setting resistor between REFDI and GNDF, and a  $1.5k\Omega$  resistor between each field input and the corresponding IN input pin ensures that the current at the ON and OFF trip points, as well as the voltage at the trip points, satisfy the requirements of IEC 61131-2 for Type 1 and Type 3 inputs. The current sunk by each input pin rises linearly with input voltage until the level set by the current limiter is reached; any voltage increase beyond this point does not increase the input current. Limiting the input current ensures compliance with IEC 61131-2 while significantly reducing power dissipation compared to traditional resistive inputs.

The current-setting resistor R<sub>REFDI</sub> can be calculated using this equation:

#### R<sub>REFDI</sub> = 17.63V / I<sub>INLIM</sub>

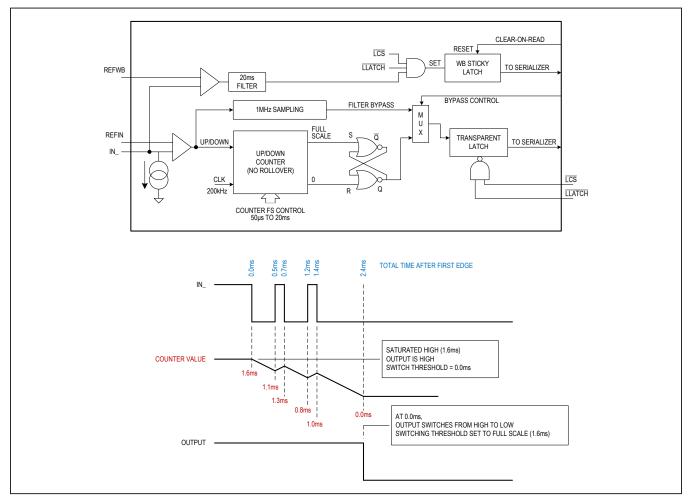

#### **Input Filters**

Each input (IN1-IN8) has a programmable filter and input data can be filtered to reduce noise, or it can be read directly for more rapid response. Bit FBP in the corresponding FLT register is used to bypass the filter or to enable the filter. One of eight filter delays (50µs, 100µs, 400µs, 800µs, 1.6ms, 3.2ms, 12.8ms, 20ms) can be independently selected for each channel. Noise rejection is accomplished through a nonrollover up-down counter where the state of the field input controls the counting direction (up or down). The filter uses an up-down counter fed by a 200kHz clock. If the input is high, it counts up; if the input is low, it counts down. The filter output is updated when the counter hits the upper or lower limit, with the upper limit depending on the selected filter delay and the lower limit being zero regardless of the filter delay. The low-to-high transition of the filter occurs when the counter reaches the upper limit. The high-to-low transition occurs when the counter reaches the lower limit. There is no rollover; counting simply stops when the upper or lower limit is hit. The filter delay is the time it takes to reach the upper/lower limit in response to a step input when the counter starts from the lower/upper limit.

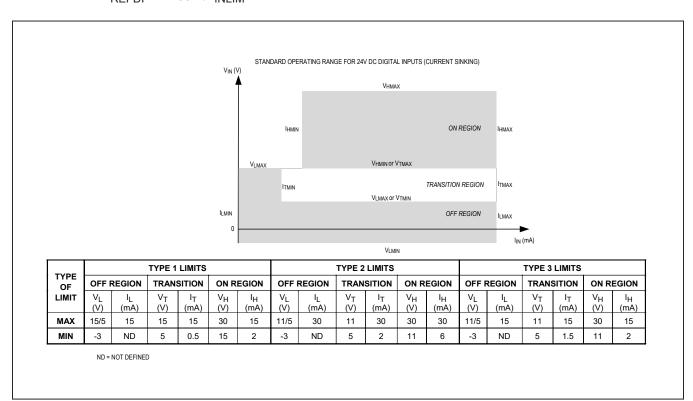

Figure 4. Switching Characteristics for IEC 61131-2 Type 1, 2, and 3 24V<sub>DC</sub> Digital Inputs

If the input is not a step function, but is bouncing, as shown in Figure 5, the output changes state after a total delay of:

Total Delay = Filter Delay + 2 x (Total Time at the Old State) In the example in Figure 5, the filter has a nominal delay of 1.6ms, and the input returns high for two 0.2ms periods after the first transition from high to low. These transitions back to the high state extend the time before the output of the filter switches. Total Delay =  $1.6ms + 2 \times (0.2ms + 0.2ms) = 2.4ms$ .

#### Wire-Break Detection