NXP Semiconductors User Guide

# S32R372141EVB User Guide

by : NXP Semiconductors

### 1. Introduction

This user guide details the setup and configuration of the NXP S32R37x Evaluation Board (hereafter referred to as the EVB). The EVB is intended to provide a mechanism for easy customer evaluation of the S32R37x 141 MAPBGA package microprocessors, and to facilitate hardware and software development.

At the time of writing this document, the S32Rxxx family form the basis of the RADAR specific 55nm devices. For the latest product information, please speak to your NXP representative or consult the NXP website at www.nxp.com and search for S32R.

The EVB is intended for bench / laboratory use and has been designed using normal temperature specified components  $(+70^{\circ}C)$ .

### 1.1. List of acronyms

Table 1 provides a list and description of acronyms used throughout this document.

### Contents

| 1. | Introduction                        | 1  |

|----|-------------------------------------|----|

| 2. | EVB Features                        |    |

| 3. | Configuration                       |    |

|    | 3.1. Power Supply Configuration     |    |

|    | 3.2. Supply Routing and Jumpers     | 7  |

| 4. | Reset Circuit                       | 8  |

| 5. | MCU External Clock Circuit          | 8  |

| 6. | JTAG                                | 9  |

| 7. | Nexus Aurora                        | 9  |

| 8. | Camera Serial Interface (MIPI-CSI2) | 10 |

|    | 8.1. Adapter Board                  |    |

| 9. | CAN FD                              | 11 |

| 10 | . Test Points                       | 12 |

| 11 | . GPIO Signal Table                 | 12 |

| 12 | . Default Jumper Summary Table      | 13 |

|    | 12.1. Default Jumper Table - EVB    | 13 |

| 13 | . User Area                         | 15 |

| 14 | . Known Issues                      | 15 |

|    |                                     |    |

| Acronym      | Description                                        |

|--------------|----------------------------------------------------|

| 1.25V_CORE   | Supply voltage from the 1.25 V switching regulator |

| 3.3V_VCCA    | Supply voltage from the 3.3 V switching regulator  |

| FRNT_END_REG | Supply voltage from the 4.2 V switching regulator  |

| 5V_AUX       | Supply voltage from the 5.0 V switching regulator  |

| ADC          | Analog-to-Digital converter                        |

| RESET_B      | External signal reset                              |

| EVB          | Evaluation board                                   |

| GND          | Ground                                             |

| HV           | High voltage (3.3V/4.2 V and/or 5 V)               |

| LED          | Light emitting diode                               |

| LV           | Low voltage (1.25 V)                               |

| MCU          | Microcontroller                                    |

| P12V         | 12 V EVB supply power domain                       |

| VREG_POR_B   | Power-on reset                                     |

| PWR          | Power                                              |

| RX           | Receive                                            |

| ТХ           | Transmit                                           |

| SBC          | System Basis Chip                                  |

#### Table 1. List of acronyms

### 1.2. Standalone concept

For maximum flexibility and simplicity, the EVB has been designed as a standalone board which provides access to the main functionality of the MCU and its interfaces and includes a GPIO breakout area for further development.

## 2. EVB features

The EVB provides the following key features:

- Support for the 141MAPBA package via a socket for simple device interchange during development

- Single 12 V external power supply input with two on-board regulators providing all of the necessary EVB and MCU voltages; Power supplied to the EVB via a 2.1 mm barrel style power jack or a 2-way level connector; 12 V operation allows in-car use if desired

- Master power switch and regulator status LEDs

- All MCU signals readily accessible at a port-ordered group of 0.1" pitch headers

- 2x CAN FD dedicated interfaces

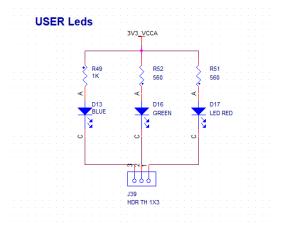

- 3x user LEDs, freely connectable

- Test points (surface mount loops) placed throughout the EVB

- MIPI-CSI2 high speed connector intended for use with Eagle MR3003 RADAR front end EVK (Evaluation Kit) or the Dolphin TEF810X front end EVK (via separate adaptor)

- Flexible MCU clocking options allow provision of an external clock from the RF front end via the MIPI-CSI2 connector or 40MHz EVB clock oscillator circuit (default). Solder pads on the EVB allow selection between these external clocks

- User reset switch with reset status LED

- Standard 14-pin JTAG debug connector and 34-pin Nexus Aurora connector

- GPIO breakout 2.54 mm headers for access to all configurable device GPIO pins

#### NOTE

To alleviate confusion between jumpers and headers, all EVB jumpers are implemented as 2mm pitch whereas headers are 0.1inch (2.54mm). This prevents inadvertently fitting a jumper to a header.

#### CAUTION

Before the EVB is used or power is applied, please fully read the following sections on how to correctly configure the board. Failure to correctly configure the board may cause irreparable component, MCU or EVB damage.

## 3. Configuration

This section details the configuration of each of the EVB functional blocks.

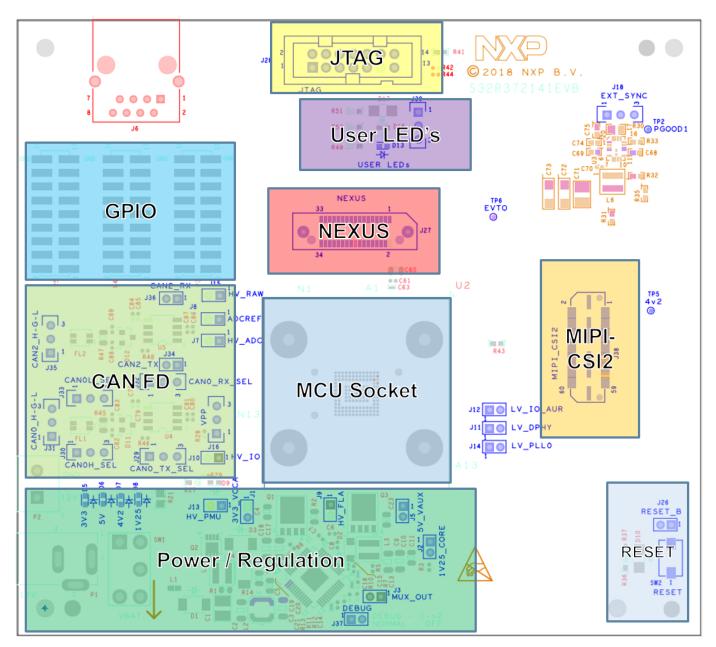

The EVB has been designed with ease of use in mind and has been segmented into functional blocks as shown below. Detailed silkscreen legend has been used throughout the board to identify all switches, jumpers and user connectors.

Configuration

Figure 1. EVB functional blocks

### 3.1. Power supply configuration

The EVB requires an external power supply voltage of 12 V DC, minimum 1.5 A. This allows the EVB to be easily used in a vehicle if required. The single input voltage is regulated on-board using an NXP system basis chip (SBC) which includes switching regulators to provide the necessary EVB and MCU operating voltages of 5.0 V, 3.3 V and 1.25 V, and also includes functional safety features such as supply monitoring and MCU reset control. A separate switching regulator provides the 4.2 V domain which is used to power the RF front end via the MIPI-CSI2 connector on board.

For flexibility, there are two different power supply input connectors on the EVB, as detailed below.

### 3.1.1. Motherboard Power Supply Connectors

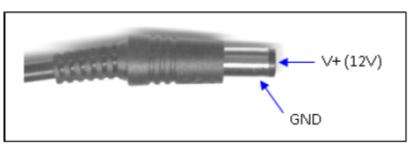

2.1 mm Barrel Connector – P1:

Figure 2. 2.1mm Power connector

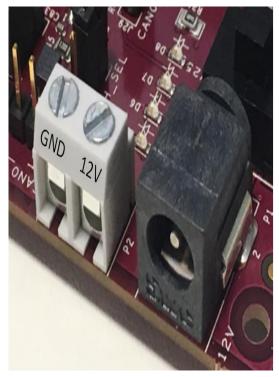

Screw Terminal Power Connector – P2:

This can be used to connect a bare wire lead to the EVB, typically from a laboratory power supply. The polarisation of the connectors is clearly marked on the EVB (Pin 1 = +12 V). Care must be taken to ensure correct connection.

Figure 3. Screw terminal power connector

### 3.1.2. Regulator power jumpers

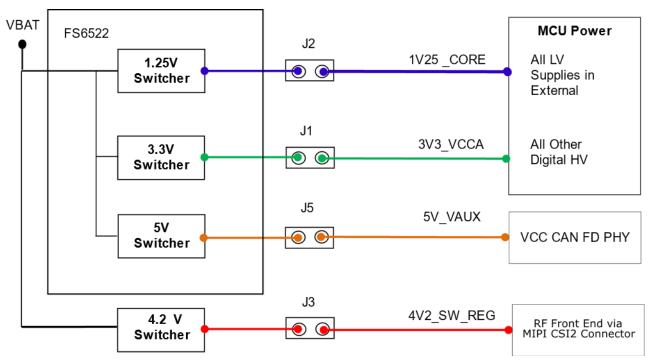

To supply the MCU and active EVB components with the required voltages, four distinct power domains are required:

- 1V25\_CORE: 1.25 V supply for the MCU core voltage

- 3V3\_VCCA: 3.3 V supply for MCU I/O

- 5V\_AUX: 5 V supply for the CAN physical interfaces

- FRNT\_END\_REG: 4.2 V supply to RF front end via MIPI-CSI2 connector

The FRNT\_END\_REG domain is provided by the LT8614 switching regulator, U3.

The 5V\_AUX, 3V3\_VCCA and 1V25\_CORE domains are provided by the FS6522 SBC, U1. The FS6522 device offers a full suite of user configurable functionality to enable functional safety applications to be developed, but detailed information of these features is outside of the scope of this document. For ease of use the FS6522 is by default in 'debug' mode, which disables some of the watchdog features and allows uninterrupted use without the need for the MCU to service any watchdogs on the FS6522 device. This is recommended for most applications unless the full functional safety features of the FS6522 are being incorporated into the application in development.

To enable the deep failsafe and watchdog timeout features of the FS6522 device a jumper is provided to switch between 'Debug' and 'Normal' operating modes. J37 can be removed to enable normal operating mode. This is only recommended if the MCU has been configured to service the FS6522 watchdog, otherwise the FS6522 will hold the MCU in reset in this mode. For more information on the FS6522 safety and watchdog features please consult the FS6522 reference manual.

All of the regulator outputs have the option of being disconnected (for example if an external supply is required). The regulators can be disconnected individually by the following jumper settings:

- Disconnecting J5 disconnects the 5 V switching regulator

- Disconnecting J1 disconnects the 3.3 V switching regulator

- Disconnecting J2 disconnects the 1.25 V switching regulator

### 3.1.3. Power switch, status LEDs

The main power switch (slide switch SW1) can be used to isolate the power supply input from the EVB voltage regulators if required.

- Moving the slide switch down (away from connector P2) will turn the EVB on

- Moving the slide switch up (towards connector P2) will turn the EVB off

When power is applied to the EVB, four blue power LEDs adjacent to the voltage regulators show the presence of the supply voltages as follows:

- LED D5 Indicates that the 3.3 V switching regulator is enabled and working correctly

- LED D6 Indicates that the 5.0 V switching regulator is enabled and working correctly

- LED D7 Indicates that the 4.2 V front end switching regulator is enabled and working correctly S32R372141EVB User Guide, Rev. 0, 08/2018

• LED D8 – Indicates that the 1.25 V switching regulator is enabled and working correctly

If no LED is illuminated when power is applied to the EVB and the regulators are correctly enabled using the appropriate jumpers, it is possible that power switch SW1 is in the "OFF" position or the power supply bias must be checked.

### 3.2. Supply routing and jumpers

The different MCU supply inputs are connected to the regulators on the motherboard through the interface connector. The following figure shows how the MCU power domains are connected to the regulators.

Figure 4. Daughter card power distribution

The connection of any power domain to a regulator has to be enabled by a dedicated jumper as described in the following table.

| Table 2. MC | J power selectior | jumpers |

|-------------|-------------------|---------|

|-------------|-------------------|---------|

| Jumper | Description                               |

|--------|-------------------------------------------|

| J1     | Connects Digital HV supplies to 3V3_VCCA  |

| J2     | Connects Digital LV supplies to 1V25_CORE |

| J3     | Connects 4V2_SW_REG via MIPI-CSI2         |

| J5     | Connects 5V_AUX supply to VCC CAN FD      |

## 4. Reset circuit

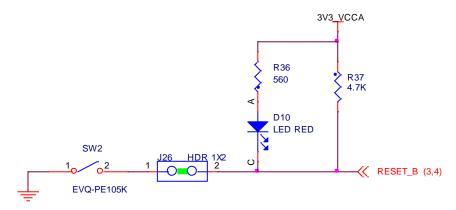

To enable standalone use the reset circuitry is placed on the EVB. It consists of a reset switch that is connected to RESET\_B via a jumper, and external voltage monitoring is handled by the FS6522 SBC which controls the MCU VREG\_POR\_B signal. A red LED (D10) is used to indicated RESET\_B reset situations, and a yellow LED (D9) indicates VREG\_POR\_B reset situations.

The EVB reset circuit provides the following functionality:

- The reset switch SW2 can be used to reset the MCU.

- The reset switch signal is connect to the MCU reset signals RESET\_B (through jumper J26) and the connection can be released by lifting the according jumper.

- For normal operation leave jumper J26 populated.

- If external control of RESET\_B is required then connection of a control signal to pin 2 of J26 can be made.

Since the S32R37X device requires external voltage monitoring the FS6522 SBC is utilised to protect the device during operation. This circuit monitors the 1.25 V (core supply) and 3.3v IO supply domain and will hold the device in reset via VREG\_POR\_B until these supplies are within the expected voltage range. For more information on the voltage monitoring and safety features of the FS6522 device please see the SBC device reference manual, available at nxp.com.

Figure 5. Voltage monitoring and reset circuit

| Jumper | Description                                 |

|--------|---------------------------------------------|

| J26    | Connect reset switch circuit to RESET_B pin |

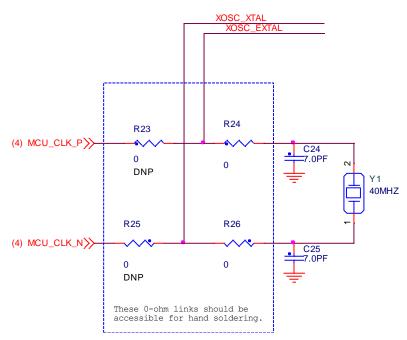

## 5. MCU external clock circuit

In addition to the internal 16 MHz oscillator, the MCU can be clocked by different external sources. The EVB system supports four possible MCU clock sources:

#### S32R372141EVB User Guide, Rev. 0, 08/2018

- 1. 40 MHz crystal Y1 (The MCU only has a 40 Mhz input)

- 2. External differential clock input to the EVB via the MIPI-CSI2 connector, for use with the Eagle MR3003 RF front end board or TEF810X Dolphin board via a separate adaptor.

The clock circuitry for the EVB is shown in Figure 6. Each source is selectable via the 0-ohm links as shown, with crystal Y1 being the default factory option.

Figure 6. 40MHz crystal circuit

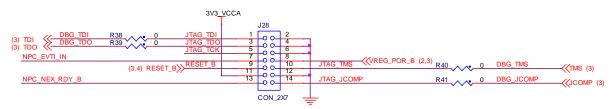

## 6. JTAG

The EVB is fitted with 14-pin JTAG debug connector. The following diagram shows the 14-pin JTAG connector pinout (0.1" keyed header).

Figure 7. JTAG connector pinout

### 7. Nexus Aurora

Table 4 shows the pinout of the 34-pin Samtec connector for the S32R37.

| Table 4. Aurora | Trace connector | pinout |

|-----------------|-----------------|--------|

|-----------------|-----------------|--------|

| Pin No | Function | Pin No | Function       |

|--------|----------|--------|----------------|

| 1      | TX0+     | 2      | VREF           |

| 3      | TX0-     | 4      | TCK/TCKC/DRCLK |

| 5   | VSS               | 6   | TMS/TMSC/TxDataP |

|-----|-------------------|-----|------------------|

| 7   | TX1+              | 8   | TDI/TxDataN      |

| 9   | TX1-              | 10  | TDO/RxDataP      |

| 11  | VSS               | 12  | JCOMP/RxDataN    |

| 13  | TX2+              | 14  | EVTI1            |

| 15  | TX2-              | 16  | EVTI0            |

| 17  | VSS               | 18  | EVTO0            |

| 19  | TX3+              | 20  | VREG_POR_B       |

| 21  | TX3-              | 22  | RESET_B          |

| 23  | VSS               | 24  | VSS              |

| 25  | TX4+ <sup>1</sup> | 26  | CLK+             |

| 27  | TX4+ <sup>1</sup> | 28  | CLK-             |

| 29  | VSS               | 30  | VSS              |

| 31  | TX5+ <sup>1</sup> | 32  | EVTO1/RDY        |

| 33  | TX5+ <sup>1</sup> | 34  | N/C              |

| GND | VSS               | GND | VSS              |

## 8. Camera Serial Interface (MIPI-CSI2)

A dedicated MIPI-CSI2 interface is provided on the EVB, and is designed to provide compatibility with the Eagle MR3003 Radar front end EVK, or the Dolphin TEF810X Radar front end EVK via a separate adaptor.

A 60 pin Samtec connector (QTH-030-01-L-D-A-K-TR) is used for the MIPI-CSI2 interface. The pinout of the connector is shown in Figure 8.

| MIPI-CSI2 Connector | J38<br>QTH-030-01-L-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D-A-K-TR |                                                                     |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|--|

| ETIMER_ETC5 >>      | 12     SI       2     1       4     3       6     5       8     7       9     7       12     1       14     13       16     17       16     17       18     17       18     17       20     19       22     19       22     19       22     21       24     21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | FRNT_END_REG                                                        |  |

| ERROR_N >>          | 25         4         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3         3 |          | CSI_LANEOP<br>CSI_LANEON<br>CSI_LANEON<br>T<br>CSI_CLKN<br>CSI_CLKP |  |

| ETIMER_ETC2 >>      | 50 49<br>52 9 51<br>54 9 53<br>56 9 55<br>58 9 55<br>58 9 55<br>50 9 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×        | CSI_LANE1P<br>CSI_LANE1N                                            |  |

Figure 8. MIPI-CSI2 connector pinout

### 8.1. Adapter board

In order to utilize the EVB with the Dolphin TEF810X RADAR front end EVK, an adapter board must be connected for compatibility.

Please consult the website at www.nxp.com or speak to your NXP representative for more details on the availability of adapter boards.

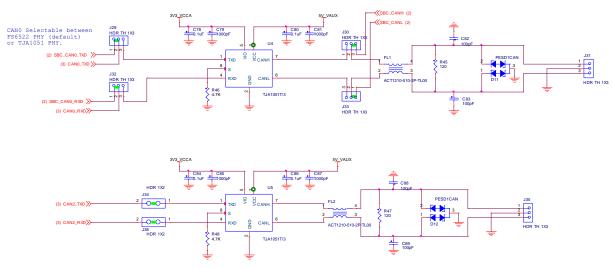

## 9. CAN FD

The EVB supports 2x CAN FD capable interfaces. The FS6522 SBC device has an on-board CAN physical interface, and 2x NXP TJA1051T/3 CAN FD (Flexible Data) compliant physical interfaces are provided (U4 and U5) on the EVB for higher speed applications.

Since the CAN module pads have multiplexable functions these can be configured as follows:

By default CAN0 signals will go straight to the onboard phy of the FS6522 SBC (U1), but if CAN FD speeds are required from CAN0 then the following jumpers can be changed to enable the CAN FD physical interface U4:

- Change J29 and J32 to pins 2-3 to re-route CAN0\_TX and CAN0\_RX to U4.

- Change J30 and J33 to pins 1-2 to reroute CANH and CANL on J31 to come from U4.

#### **GPIO** signal table

CAN2 signals are routed to the on-board CAN-FD phy U5 via J34 and J36, with CANH and CANL output on J35.

Figure 9. CAN FD Physical Interfaces

## **10. Test points**

EVB test points are listed and detailed in Table 5.

| Table 5 | Test | points - | daughter | card |

|---------|------|----------|----------|------|

|---------|------|----------|----------|------|

| Signal     | TP<br>name | Shape Description |                                                         |

|------------|------------|-------------------|---------------------------------------------------------|

| PGOOD1     | TP2        | Surface Pad       | Power good signal from FRNT_END_REG switching regulator |

| 4v2        | TP5        | Surface Pad       | 4.2V Switching regulator output                         |

| NPC_EVTO_B | TP6        | Test Loop         | PI9 (Pad G14)                                           |

## 11. GPIO signal table

The assignable pin outputs from the MCU signals from headers P3, P4 and P5 on the top left-hand side of the board are summarized in Table 6, Table 7 and Table 8, respectively. For further information on available pin functionality consult the device Reference Manual.

| Pin No | Port | Function | Pin No | Port | Function |

|--------|------|----------|--------|------|----------|

| 1      | PA0  | GPIO[0]  | 2      | PA1  | GPIO[1]  |

| 3      | PA2  | GPIO[2]  | 4      | PA3  | GPIO[3]  |

| 5      | PA4  | GPIO[4]  | 6      | PA5  | GPIO[5]  |

| 7      | PA6  | GPIO[6]  | 8      | PA7  | GPIO[7]  |

| 9      | PA8  | GPIO[8]  | 10     | PA9  | GPIO[9]  |

| 11     | PA10 | GPIO[10] | 12     | PA11 | GPIO[11] |

Table 6. P3 GPIO Breakout Table

| 13 | PA12 | GPIO[12] | 14 | PA13 | GPIO[13] |

|----|------|----------|----|------|----------|

| 15 | PA14 | GPIO[14] | 16 | PA15 | GPIO[15] |

| 17 |      | GND      | 18 |      | GND      |

| Pin No | Port | Function      |

|--------|------|---------------|

| 1      | PB0  | GPIO[16]      |

| 3      | PB2  | GPIO[18]      |

| 5      | PB4  | GPIO[20]      |

| 7      | PB6  | GPIO[22]_CLKO |

|        |      | UT            |

| 9      | PB15 | GPIO[31]      |

| 11     | PC12 | GPIO[44]      |

| 13     | PD1  | GPIO[49]      |

| 15     | PD6  | GPIO[54]      |

| 17     |      | GND           |

|        |      |               |

#### Table 7. P4 GPIO Breakout Table

| Pin No | Port | Function |

|--------|------|----------|

| 2      | PB1  | GPIO[17] |

| 4      | PB3  | GPIO[19] |

| 6      | PB5  | GPIO[21] |

| 8      | PB13 | GPIO[29] |

| 10     | PC0  | GPIO[32] |

| 12     | PC15 | GPIO[47] |

| 14     | PD3  | GPIO[51] |

| 16     | PD14 | GPIO[62] |

| 18     |      | GND      |

#### Table 8. P5 GPIO Breakout Table

| Pin No | Port         | Function            | Pin No | Port     | Function      |

|--------|--------------|---------------------|--------|----------|---------------|

| 1      | PE2          | GPIO[66]            | 2      | PE4      | GPIO[68]      |

| 3      | PE6          | GPIO[70]            | 4      | PE13     | GPIO[77]      |

| 5      | PE15         | GPIO[79]_CLKO<br>UT | 6      | PF0      | GPIO[80]      |

| 7      | PF15         | GPIO[95]            | 8      | PG8      | GPIO[10<br>4] |

| 9      | PH7          | GPIO[119]           | 10     | PI4      | GPIO[13<br>2] |

| 11     | PI5          | GPIO[133]           | 12     | NMI      | NMI           |

| 13     | FCCU[F<br>0] | FCCU_0              | 14     | FCCU[F1] | FCCU_1        |

| 15     |              | NC                  | 16     |          | NC            |

| 17     |              | GND                 | 18     |          | GND           |

### 12. Default jumper summary table

### 12.1. Default jumper table - EVB

On delivery, the EVB comes with a default jumper configuration. Table 9 lists and describes briefly the jumpers on the S32R37X and indicates which jumpers are on/off on delivery of the board.

| Table | 9.  | Default | iumper  | table |

|-------|-----|---------|---------|-------|

| IUNIO | ••• | Donaunt | Janipor | LUNIO |

| Jumper | Default Pos | PCB Legend  | Description                              |

|--------|-------------|-------------|------------------------------------------|

| J1     | On          | 3.3 V       | 3.3 V supply for the FS6520 regulator    |

| J2     | On          | 1.25 V      | 1.25 V supply                            |

| J3     | On          | MUX_OUT     | FS6520 multiplexed output                |

| J5     | On          | 5V_AUX      | Output from transistor                   |

| J7     | On          | HV_ADC      | 3.3 V ADC supply                         |

| J8     | On          | ADCREF      | 3.3 V ADC reference voltage              |

| J9     | On          | HV_FLA      | 3.3 V Flash supply                       |

| J10    | On          | 1.25 V      | 3.3 V IO                                 |

| J11    | On          | LV_DPHY     | 1.25V MIPI-CSI2 DPHY                     |

| J12    | On          | LV_IO_AUR   | VDD_LV_IO_AURORA                         |

| J13    | On          | HV_PMU      | 3.3 V PMU supply                         |

| J14    | On          | LV_PLLO     | 1.25 V PLL supply                        |

| J15    | On          | HV_RAW      | ADC reference voltage                    |

| J16    | 2-3         | EXT_SYNC    | VPP Test (always GND)                    |

| J18    | 1-2         | EXT_SYNC    | LT8614 internal voltage synchronisation  |

| J26    | On          | RESET_B     | Reset switch                             |

| J29    | 1-2         | CAN0_TX_SEL | CAN0 transmitter select between U1 or U4 |

| J30    | 1-2         | CAN0H_SEL   | CAN0 High select between U1 or U4        |

| J31    | Off         | CAN0_H-G-L  | CAN0 connections                         |

| J32    | 1-2         | CAN0_RX_SEL | CAN0 receiver select between U1 or U4    |

| J33    | 1-2         | CAN0L_SEL   | CAN0 Low select between U1 or U4         |

| J34    | On          | CAN2_TX     | U5 Transmitter connection                |

| J35    | Off         | CAN2_H-G-L  | CAN2 connections                         |

| J36    | On          | CAN2_RX     | U5 Receiver connection                   |

| J37    | On          | DEBUG       | FS6522 in Debug Mode                     |

| J39    | Off         | 3V3_VCCA    | User LEDs                                |

S32R372141EVB User Guide, Rev. 0, 08/2018

### 13. User area

There are three active low user LEDs D13 (blue), D14 (green) and D15 (red). These are enabled by connecting a logic 0 signal to the corresponding pin on 0.1" header J39 (USER LEDS).

## 14. Known issues

No known issues.

How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

> Document Number: S32R372141EVBUG Rev. 0 08/2018