## Product Change Notification - SYST-04GTSK003

## Date:

06 Jun 2019

**Product Category:**

Ethernet Controllers

### Affected CPNs:

**7**

## Notification subject:

ERRATA - ENC424J600/624J600 Silicon/Data Sheet Errata

## Notification text:

SYST-04GTSK003 Microchip has released a new DeviceDoc for the ENC424J600/624J600 Silicon/Data Sheet Errata of devices. If you are using one of these devices please read the document located at <u>ENC424J600/624J600 Silicon/Data Sheet Errata</u>.

## Notification Status: Final

## **Description of Change:**

- 1) Section/Figure/Entry: Module 6 Added new Module

- 2) Section/Figure/Entry: All Converted to Microchip format

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 06 Jun 2019

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

## Markings to Distinguish Revised from Unrevised Devices: N/A Attachment(s):

ENC424J600/624J600 Silicon/Data Sheet Errata

Please contact your local <u>Microchip sales office</u> with questions or concerns regarding this notification.

## **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN home page</u> select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. If you wish to <u>change your PCN profile</u>, including opt out, please go to the <u>PCN home page</u> select

If you wish to <u>change your PCN profile, including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

Affected Catalog Part Numbers (CPN)

ENC424J600-I/ML ENC424J600-I/PT ENC424J600T-I/ML ENC424J600T-I/PT ENC624J600-I/PT ENC624J600T-I/PT

# ENC424J600/624J600

## ENC424J600/624J600 Silicon Errata and Data Sheet Clarification

The ENC424J600/624J600 devices that you have received conform functionally to the current Device Data Sheet (DS39935B), except for the anomalies described in this document. This document describes known silicon errata for the ENC424J600/624J600 family of devices, which includes the following:

- ENC424J600

- ENC624J600

The silicon issues discussed in the following pages are for silicon revisions with the combined Device/Revision IDs listed in Table 1. A summary of ENC424J600/624J600 silicon errata is provided in Table 2.

**Note:** This document summarizes all silicon errata issues from all revision of silicon, previous as well as current. Only the issues in the last column of Table 2 apply to the current silicon revision (A2).

The silicon revision level can be retrieved by querying the read-only EIDLEDL register (when using one of the 8-bit interfaces) or the lower byte of the EIDLED register (when using a 16-bit interface). Please refer to the Device Data Sheet for detailed information on accessing these registers. The values for the various ENC424J600/624J600 silicon revisions are shown in Table 1.

#### TABLE 1:AFFECTED SILICON REVISIONS

| Dort Numbero | Value of EIDLEDL or EIDLED<7:0> |  |

|--------------|---------------------------------|--|

| Part Numbers | A2                              |  |

| ENC424J600   | 215                             |  |

| ENC624J600   | 21h                             |  |

#### TABLE 2: SILICON ISSUE SUMMARY

| Module | Feature  | ltem<br>Number | Silicon Issue Summary                                                                              | Affected<br>Revisions <sup>(1)</sup> |

|--------|----------|----------------|----------------------------------------------------------------------------------------------------|--------------------------------------|

|        |          |                |                                                                                                    | A2                                   |

| PHY    | Receive  | 1.             | Rare packet loss following collisions, 10BASE-T Half-Duplex mode (PHY Receive)                     |                                      |

| PHY    | Transmit | 2.             | Deviations from MAU eye pattern in 10BASE-T mode (PHY Trans-<br>mit)                               | ×                                    |

| PHY    | Transmit | 3.             | Rise time/fall time asymmetry in MLT2 signal (PHY Transmit)                                        | Х                                    |

| Memory | SFR      | 4.             | CRYPTEN bit cannot be changed by BFC/BFS/BFCU/BFSU opcodes or EIRSET/EIRCLR registers (SFR Memory) | Х                                    |

| AES    | -        | 5.             | AES module produces incorrect results                                                              | Х                                    |

| MAC    | -        | 6.             | Errant MAC Address                                                                                 | Х                                    |

Note 1: Only those issues indicated in the last column apply to the current silicon revision.

#### Silicon Errata Issues

**Note:** This document summarizes all silicon errata issues from all revision of silicon, previous as well as current. Table 2 details which errata apply to each silicon revision.

#### Module 1: Rare packet loss following collisions, 10BASE-T Half-Duplex mode (PHY Receive)

#### DESCRIPTION

On rare occasions, in 10BASE-T Half-Duplex mode, a collision will cause the immediately following packet to be received incorrectly. This causes the packet to be dropped. This condition may occur on an average of one to four times per 10,000 collisions.

#### END USER IMPLICATIONS

Full-Duplex mode and 100Base-TX modes are unaffected by this issue. Typical modern networks are deployed using Ethernet switching technology and will not experience any collisions or packet loss due to this issue. In the uncommon case that an affected network infrastructure is used, upper layer communications protocols, such as TCP, will normally perform automatic retransmission to ensure that no application data is lost.

#### Work around

None.

PLAN

This erratum will not be corrected in a future revision.

#### Module 2: Deviations from MAU eye pattern in 10BASE-T mode (PHY Transmit)

#### DESCRIPTION

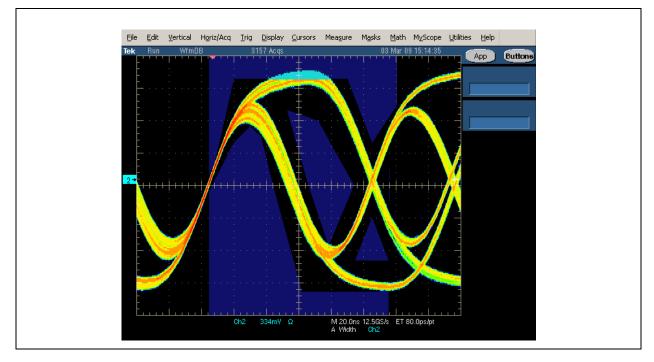

When transmitting random data in 10BASE-T mode, the PHY transmit waveform slightly violates the MAU eye diagram keep-out zones specified in the IEEE 802.3<sup>™</sup> Std. 2005, Section 14.3.1.2.1. Specifically, the waveform amplitude is slightly too high for '0' to '1' and '1' to '0' bit transitions when tested against the twisted-pair model, as shown in Figure 1.

#### FIGURE 1: 10BASE-T MAU EYE DIAGRAM

#### END USER IMPLICATIONS

This issue applies only to 10 Mbps speed and is unlikely to cause compatibility problems in real networks. When terminated with a 100W resistor without the twisted-pair model, the transmit waveform stays within the amplitude limits of +2.2V to +2.8V and -2.2V to -2.8V required by the standard.

#### Work around

None.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 3: Rise time/fall time asymmetry in MLT2 signal (PHY Transmit)

#### DESCRIPTION

For 100BASE-TX operation, the IEEE 802.3 specification requires the rise and fall times of the MLT3 signal to match within 0.5 ns, measured over 10 different intervals. The actual rise/fall time symmetry measurements may occasionally be slightly above this level.

#### END USER IMPLICATIONS

This issue has no substantial impact on the quality of the transmitted signal and will not impact applications operating in real networks.

#### Work around

None.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 4: CRYPTEN bit cannot be changed by BFC/BFS/BFCU/BFSU opcodes or EIRSET/ EIRCLR registers (SFR Memory)

#### DESCRIPTION

The CRYPTEN bit (EIR<15>) cannot be changed using the Bit Field Set (BFS), Bit Field Clear (BFC), Bit Field Set Unbanked (BFSU) or Bit Field Clear Unbanked (BFCU) SPI opcodes. Similarly, when the PSP interface is being used, CRYPTEN cannot be changed by writing to the EIRSET or EIRCLR registers.

#### END USER IMPLICATIONS

In order to change the CRYPTEN bit, a workaround procedure must be used.

#### Work around

Set or clear the CRYPTEN bit using the Write Control Register (WCR) or Write Control Register Unbanked (WCRU) SPI opcodes, or a direct PSP write to the EIR register.

If the application is not constrained by power consumption, it is possible to set the CRYPTEN bit at device initialization and leave it set.

If the application must change CRYPTEN at run time, care must be taken to ensure that no required interrupt flag bits in EIR are corrupted in the process. For example, if the Link Change Interrupt Flag, LINKIF (EIR<11>), is used by the software, writing to EIR will cause potential loss of information. This can be avoided by sampling the interrupt source (PHYLNK bit in ESTAT) before and after changing CRYPTEN. If the PHYLNK bit has changed, the LINKIF bit can be manually set through a safe BFS operation or write to EIRSET. Any intermediate spurious interrupts on the INT pin can be suppressed by appropriately controlling the EIE interrupt enable bits.

Ideally, if using the SPI interface or using a PSP interface with byte write capability, write only to EIRH and avoid writing to EIRL.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 5: AES module produces incorrect results

#### DESCRIPTION

At room temperature, the AES module may compute valid results. However, across voltage, temperature, and ordinary part-to-part device variation, the AES engine will compute incorrect results or fail to finish computations.

#### END USER IMPLICATIONS

To implement AES, a work around software solution must be used.

#### Work around

Use a software implementation of AES. For applications based on Microchip PIC® microcontrollers or dsPIC® digital signal controllers, consider using the libraries documented in the Microchip Application Notes AN953, "Data Encryption Routines for the PIC18" or AN1044, "Data Encryption Routines for PIC24 and dsPIC® Devices". The source code for these libraries is available on the Data Encryption Libraries CD, Microchip part number SW300052.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 6: Errant MAC Address

#### DESCRIPTION

A very few of the ENC424J600/624J600 devices have been programmed with either duplicate MAC addresses or MAC addresses that fall outside Microchip's range of allocated range. Microchip has identified and corrected this problem. Therefore, future devices are not affected. Less than 0.08% of devices were affected by this erratum.

#### END USER IMPLICATIONS

There is a possibility that these devices can be on the same network with another device with the same MAC address. This could cause communication failures.

#### Work around

Microchip will RMA the ENC424J600/624J600 parts with invalid MAC addresses. Please contact your local sales office to initiate the RMA process.

#### PLAN

This erratum has been corrected in the newer products.

## APPENDIX A: DOCUMENT REVISION HISTORY

| Revision Level & Date   | Section/Figure/Entry | Correction                     |

|-------------------------|----------------------|--------------------------------|

| DS80000477B (05-29-19)  | Module 6.            | Added new module.              |

|                         | All                  | Converted to Microchip format. |

| DS80000477A (June 2009) | All                  | Initial release                |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

#### Technical support is available through the web site at: http://microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet Iogo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified Iogo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 9781522445616

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Netherlands - Drunen Tel: 31-416-690399

Italy - Padova

Italy - Milan

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4450-2828

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820