# ICM7217

# 4-Digit LED Display Programmable Up/Down Counter

December 1993

#### Features

- Four Decade, Presettable Up-Down Counter with Parallel Zero Detect

- Settable Register with Contents Continuously Compared to Counter

- Directly Drives Multiplexed 7 Segment Common Anode or Common Cathode LED Displays

- On-Board Multiplex Scan Oscillator

- Schmitt Trigger On Count Input

- TTL Compatible BCD I/O Port, Carry/ Borrow, Equal, and Zero Outputs

- Display Blank Control for Lower Power Operation; Quiescent Power Dissipation <5mW</li>

- All Terminals Fully Protected Against Static Discharge

- Single 5V Supply Operation

# Description

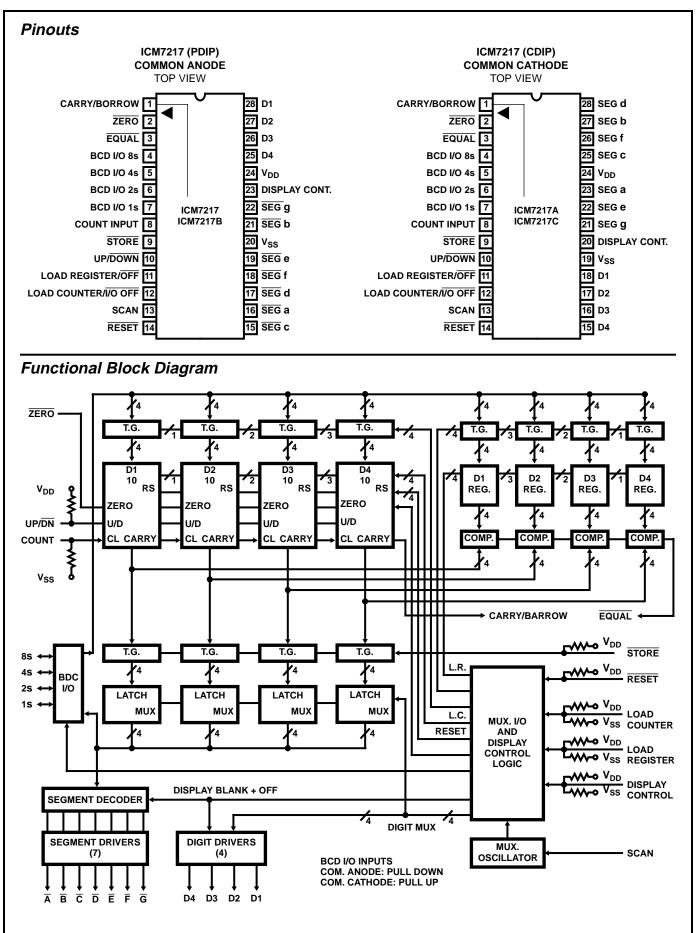

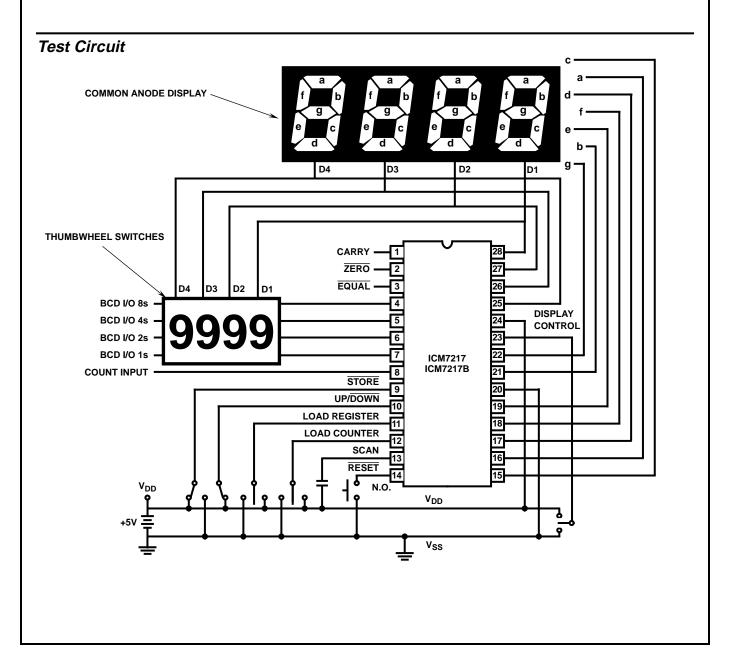

The ICM7217 is a four digit, presettable up/down counter with an onboard presettable register continuously compared to the counter. The ICM7217 is intended for use in hard-wired applications where thumbwheel switches are used for loading data, and simple SPDT switches are used for chip control.

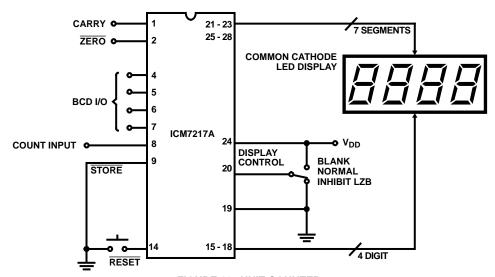

This circuit provides multiplexed 7 segment LED display outputs, with common anode or common cathode configurations available. Digit and segment drivers are provided to directly drive displays of up to 0.8 inch character height (common anode) at a 25% duty cycle. The frequency of the onboard multiplex oscillator may be controlled with a single capacitor, or the oscillator may be allowed to free run. Leading zeros can be blanked. The data appearing at the 7 segment and BCD outputs is latched; the content of the counter is transferred into the latches under external control by means of the Store pin.

The ICM7217 (common anode) and ICM7217A (common cathode) versions are decade counters, providing a maximum count of 9999, while the ICM7217B (common anode) and ICM7217C (common cathode) are intended for timing purposes, providing a maximum count of 5959.

This circuit provides 3 main outputs; a CARRY/BORROW output, which allows for direct cascading of counters, a  $\overline{\text{ZERO}}$  output, which indicates when the count is zero, and an  $\overline{\text{EQUAL}}$  output, which indicates when the count is equal to the value contained in the register. Data is multiplexed to and from the device by means of a tri-state BCD I/O port. The CARRY/BORROW,  $\overline{\text{EQUAL}}$ ,  $\overline{\text{ZERO}}$  outputs, and the BCD port will each drive one standard TTL load.

To permit operation in noisy environments and to prevent multiple triggering with slowly changing inputs, the count input is provided with a Schmitt trigger.

Input frequency is guaranteed to 2MHz, although the device will typically run with  $f_{\text{IN}}$  as high as 5MHz. Counting and comparing ( $\overline{\text{EQUAL}}$  output) will typically run 750kHz maximum.

# **Ordering Information**

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE             | DISPLAY DRIVER<br>TYPE | COUNT OPTION/<br>MAX COUNT |

|----------------|----------------------|---------------------|------------------------|----------------------------|

| ICM7217AIPI    | -25°C to +85°C       | 28 Lead Plastic DIP | Common Cathode         | Decade/9999                |

| ICM7217CIPI    | -25°C to +85°C       | 28 Lead Plastic DIP | Common Cathode         | Timing/5959                |

| ICM7217IJI     | -25°C to +85°C       | 28 Lead Ceramic DIP | Common Anode           | Decade/9999                |

| ICM7217BIJI    | -25°C to +85°C       | 28 Lead Ceramic DIP | Common Anode           | Timing/5959                |

# Specifications ICM7217

## Absolute Maximum Ratings Thermal Information

$\begin{array}{cccc} Thermal \ Resistance & \theta_{JA} & \theta_{JC} \\ Ceramic \ DIP \ Package & 55^{\circ}C/W & 20^{\circ}C/W \\ Plastic \ DIP \ Package & 55^{\circ}C/W & - \\ Junction \ Temperature & & & \end{array}$

Operating Temperature Range ... -25°0 to +85°C Storage Temperature Range ... -65°0 to +150°C Plasti Lead Temperature (Soldering, 10s) ... +300°C Cerai

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **Electrical Specifications** $V_{DD} = 5V$ , $V_{SS} = 0V$ , $T_A = +25^{\circ}C$ , Display Diode Drop 1 .7V, Unless Otherwise Specified

| PARAMETER                                                                                   | TEST CONDITIONS                                                                        | MIN  | TYP   | MAX  | UNIT    |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-------|------|---------|

| Supply Current<br>(Lowest Power Mode), IDD (7217)                                           | Display Off, LC, DC, UP/DN,<br>ST, RS, BCD I/O Floating or at V <sub>DD</sub> (Note 3) | -    | 350   | 500  | μΑ      |

| Supply Current, OPERATING, I <sub>OP</sub>                                                  | Common Anode, Display On, all "8's"                                                    | 140  | 200   | -    | mA      |

| Supply Current, OPERATING, I <sub>OP</sub>                                                  | Common Cathode, Display On, all "8's"                                                  | 50   | 100   | -    | mA      |

| V <sub>SUPPLY,</sub> VDD                                                                    |                                                                                        | 4.5  | 5     | 5.5  | V       |

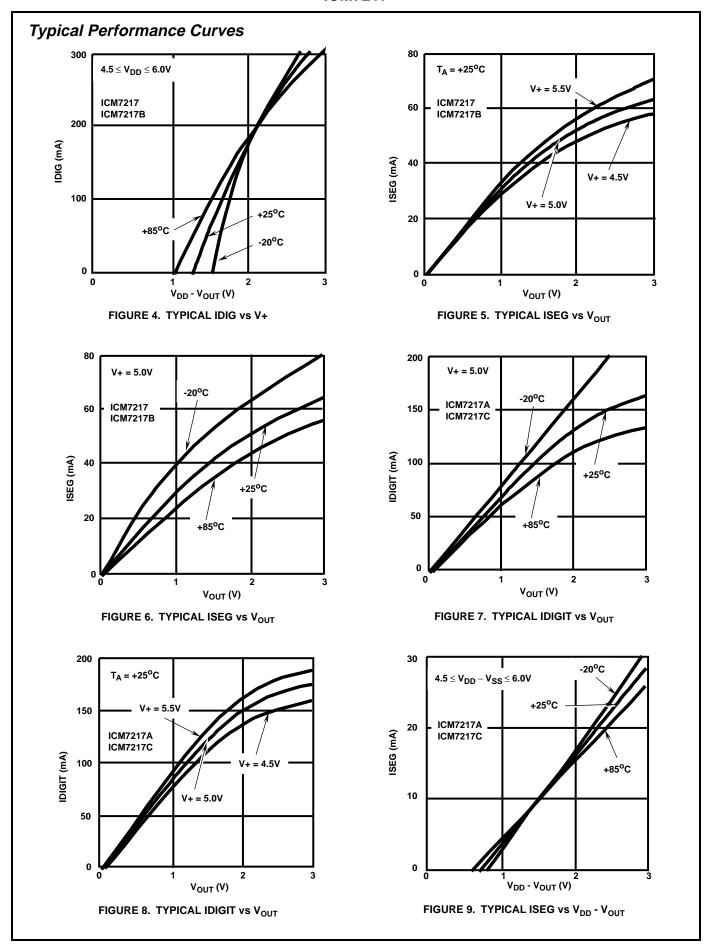

| Digit Driver Output Current, IDIG                                                           | Common Anode, V <sub>OUT</sub> = V <sub>DD</sub> - 2.0V                                | 140  | 200   | -    | mA peak |

| SEGment Driver<br>Output Current, ISEG                                                      | Common Anode, V <sub>OUT</sub> = +1.5V                                                 | 20   | 35    | -    | mA peak |

| Digit Driver, Output Current, I <sub>DIG</sub>                                              | Common Cathode, V <sub>OUT</sub> = +1.0V                                               | -50  | -75   | -    | mA peak |

| SEGment Driver<br>Output Current, ISEG                                                      | Common Cathode V <sub>OUT</sub> = V <sub>DD</sub> - 2V                                 | -9   | -12.5 | -    | mA peak |

| ST, RS, UP/DN Input<br>Pullup Current, IP                                                   | V <sub>IN</sub> = V <sub>DD</sub> - 2V (Note 3)                                        | 5    | 25    | -    | μΑ      |

| 3 Level Input Impendance, ZIN                                                               |                                                                                        | 40   | -     | 350  | kΩ      |

| BCD I/O Input, High Voltage                                                                 | ICM7217 Common Anode (Note 4)                                                          | 1.5  | -     | -    | V       |

| VBIH                                                                                        | ICM7217 Common Cathode (Note 4)                                                        | 4.40 | -     | -    | V       |

| BCD I/O Input, Low Voltage                                                                  | ICM7217 Common Anode (Note 4)                                                          | -    | -     | 0.60 | V       |

| VBIL                                                                                        | ICM7217 Common Cathode (Note 4)                                                        | -    | -     | 3.2V | V       |

| BCD I/O Input, Pullup Current IBPU                                                          | ICM7217 Common Cathode $V_{IN} = V_{DD} - 2V$ (Note 3)                                 | 5    | 25    | -    | μΑ      |

| BCD I/O Input<br>Pulldown Current, IBPD                                                     | ICM7217 Common Anode V <sub>IN</sub> = +2V (Note 3)                                    | 5    | 25    | -    | μΑ      |

| BCD I/O, ZERO, EQUAL Outputs<br>Output High Voltage, VOH                                    | . 011                                                                                  |      | -     | -    | V       |

| BCD I/O, CARRY/BORROW ZERO, EQUAL Outputs Output Low Voltage, VOL                           |                                                                                        |      | -     | 0.4  | V       |

| Count Input Frequency, f <sub>IN</sub>                                                      | -20°C < T <sub>A</sub> < +70°C                                                         | -    | 5     | -    | MHz     |

|                                                                                             | Guaranteed                                                                             | 0    | -     | 2    | MHz     |

| Count Input Threshold, VTH                                                                  | (Note 5)                                                                               | -    | 2     | -    | V       |

| Count Input Hysteresis, VHYS                                                                | (Note 5)                                                                               | -    | 0.5   | -    | V       |

| Count Input LO, VCIL                                                                        |                                                                                        |      | -     | 0.40 | V       |

| Count Input HI, VCIH                                                                        |                                                                                        | 3.5  | -     | -    | V       |

| Display Scan Oscillator Frequency, F <sub>DS</sub> Free-running (SCAN Terminal Open Circuit |                                                                                        | -    | 2.5   | 10   | kHz     |

# Specifications ICM7217

**Switching Specifications**  $V_{DD} = 5V$ ,  $V_{SS} = 0V$ ,  $T_A = +25^{\circ}C$

| PARAMETER                                    | MIN  | TYP | MAX | UNIT |

|----------------------------------------------|------|-----|-----|------|

| UP/DOWN Setup Time, t <sub>UCS</sub>         | 300  | -   | -   | ns   |

| UP/DOWN Hold Time, t <sub>UCH</sub>          | 1500 | 750 | -   | ns   |

| COUNT Pulse Width High, t <sub>CWH</sub>     | 250  | 100 | -   | ns   |

| COUNT Pulse Width Low, t <sub>CWI</sub>      | 250  | 100 | -   | ns   |

| COUNT to CARRY/BORROW Delay, t <sub>CB</sub> | -    | 750 | -   | ns   |

| CARRY/BORROW Pulse Width t <sub>BW</sub>     | -    | 100 | -   | ns   |

| COUNT to EQUAL Delay, t <sub>CE</sub>        | -    | 500 | -   | ns   |

| COUNT to ZERO Delay, t <sub>CZ</sub>         | -    | 300 | -   | ns   |

| RESET Pulse Width, t <sub>RST</sub>          | 1000 | 500 | -   | ns   |

#### NOTES:

- Due to the SCR structure inherent in the CMOS process used to fabricate these devices, connecting any terminal to a voltage greater than V<sub>DD</sub> or less than V<sub>SS</sub> may cause destructive device latchup. For this reason it is recommended that the power supply to the device be established before any inputs are applied and that in multiple systems the supply to the ICM7217 be turned on first.

- 2. In the ICM7217 the UP/DOWN, STORE, RESET and the BCD I/O as inputs have pullup or pulldown devices which consume power when connected to the opposite supply. Under these conditions, with the display off, the device will consume typically 750µA.

- 3. These voltages are adjusted to allow the use of thumbwheel switches for the ICM7217. Note that a high level is taken as an input logic zero for ICM7217 common-cathode versions.

- 4. Parameters not tested (Guaranteed by Design).

# **Detailed Description**

## **Control Outputs**

The CARRY/BORROW output is a positive going pulse occurring typically 500ns after the positive going edge of the COUNT INPUT. It occurs when the counter is clocked from 9999 to 0000 when counting up and from 0000 to 9999 when counting down. This output allows direct cascading of counters. The CARRY/BORROW output is not valid during load counter and reset operation. When the count is 6000 or higher, a reset generates a CARRY/BORROW pulse.

The EQUAL output assumes a negative level when the contents of the counter and register are equal.

The  $\overline{\text{ZERO}}$  output assumes a negative level when the content of the counter is 0000.

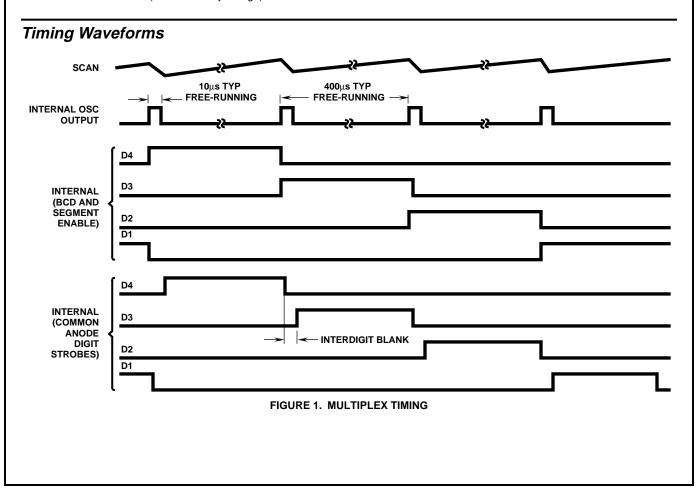

The CARRY/BORROW,  $\overline{\text{EQUAL}}$  and  $\overline{\text{ZERO}}$  outputs will drive a single TTL load over the full range of supply voltage and ambient temperature; for a logic zero, these outputs will sink 1.6mA at 0.4V and for a logic one, the outputs will source  $>60\mu\text{A}$ . A  $10\text{k}\Omega$  pull-up resistor to  $V_{DD}$  on the  $\overline{\text{EQUAL}}$  or  $\overline{\text{ZERO}}$  outputs is recommended for highest speed operation, and on the CARRY/BORROW output when it is being used for cascading. Figure 2 shows control outputs timing diagram.

#### **Display Outputs and Control**

The Digit and SEGment drivers provide a decoded 7 segment display system, capable of directly driving common anode LED displays at typical peak currents of 35mA/seg. This corresponds to average currents of 8mA/seg at 25% multiplex duty cycle. For the common cathode versions, peak segment currents are 12.5mA, corresponding to average segment currents of 3.1mA. Figure 1 shows the multiplex timing. The DISPLAY pin controls the display output using three level logic. The pin is self-biased to a voltage approximately <sup>1</sup>/<sub>2</sub> (V<sub>DD</sub>); this corresponds to normal operation. When this pin is connected to  $V_{\mbox{\scriptsize DD}},$  the segments are disabled and when connected to V<sub>SS</sub>, the leading zero blanking feature is inhibited. For normal operation (display on with leading zero blanking) the pin should be left open. The display may be controlled with a 3 position SPDT switch; see Test Circuit.

## **Multiplex SCAN Oscillator**

The on-board multiplex scan oscillator has a nominal freerunning frequency of 2.5kHz. This may be reduced by the addition of a single capacitor between the SCAN pin and the positive supply. Capacitor values and corresponding nominal oscillator frequencies, digit repetition rates, and loading times are shown in Table 1.

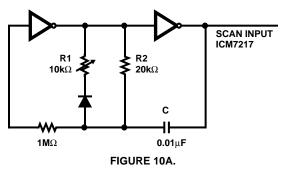

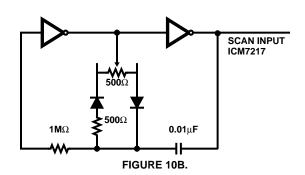

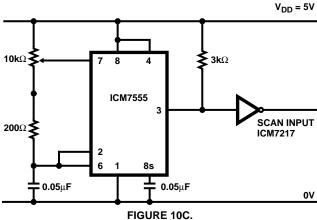

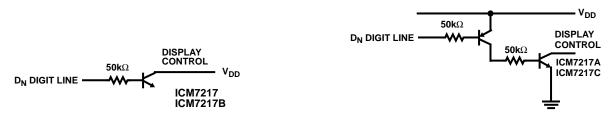

FIGURE 10. BRIGHTNESS CONTROL CIRCUITS

TABLE 1. ICM7217 MULTIPLEXED RATE CONTROL

| SCAN<br>CAPACITOR | NOMINAL<br>OSCILLATOR<br>FREQUENCY | DIGIT<br>REPETITION<br>RATE | SCAN<br>CYCLE<br>TIME<br>(4 DIGITS) |

|-------------------|------------------------------------|-----------------------------|-------------------------------------|

| None              | 2.5kHz                             | 625Hz                       | 1.6ms                               |

| 20pF              | 1.25kHz                            | 300Hz                       | 3.2ms                               |

| 90pF              | 600Hz                              | 150Hz                       | 8ms                                 |

The internal oscillator output has a duty cycle of approximately 25:1, providing a short pulse occurring at the oscillator frequency. This pulse clocks the four-state counter which provides the four multiplex phases. The short pulse width is used to delay the digit driver outputs, thereby providing interdigit blanking which prevents ghosting. The digits are scanned from MSD (D4) to LSD (D1). See Figure 1 for the display digit multiplex timing.

During load counter and load register operations, the multiplex oscillator is disconnected from the SCAN input and is allowed to free-run. In all other conditions, the oscillator may be directly overdriven to about 20kHz, however the external oscillator signal should have the same duty cycle as the internal signal, since the digits are blanked during the time the external signal is at a positive level (see Figure 1). To insure proper leading zero blanking, the interdigit blanking time should not be less than about  $2\mu s$ . Overdriving the oscillator at less than 200Hz may cause display flickering.

The display brightness may be altered by varying the duty cycle. Figure 10 shows several variable-duty-cycle oscillators suitable for brightness control at the ICM7217 SCAN input. The inverters should be CMOS CD4000 series and the diodes may be any inexpensive device such as IN914.

#### Counting Control, STORE, RESET

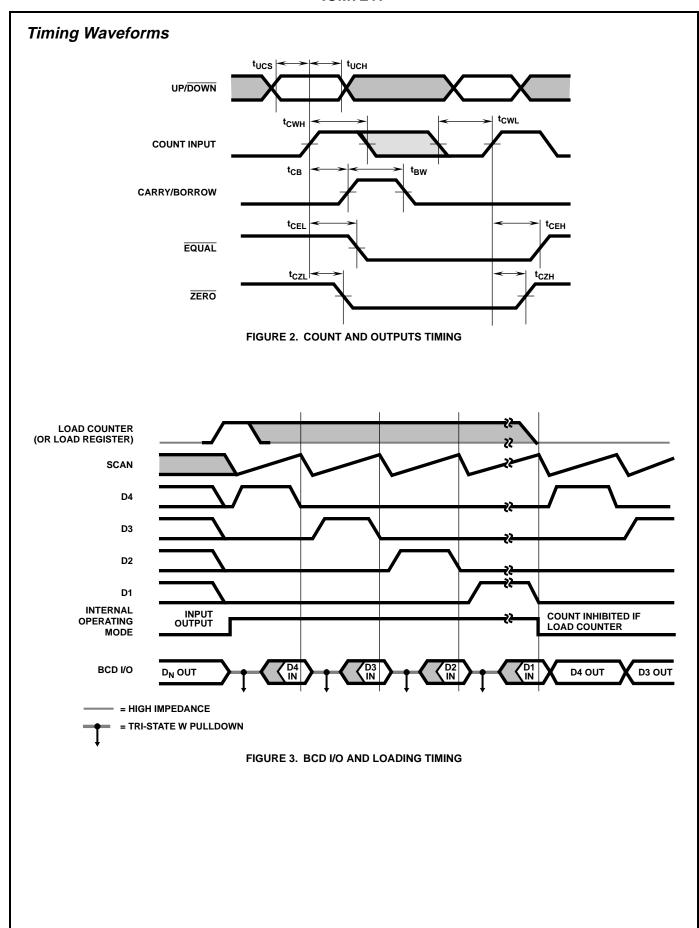

As shown in Figure 2, the counter is incremented by the rising edge of the COUNT INPUT signal when UP/DOWN is high. It is decremented when UP/DOWN is low. A Schmitt trigger on the COUNT INPUT provides hysteresis to prevent double triggering on slow rising edges and permits operation in noisy environments. The COUNT INPUT is inhibited during reset and load counter operations.

The STORE pin controls the internal latches and consequently the signals appearing at the 7-Segment and BCD outputs. Bringing the STORE pin low transfers the contents of the counter into the latches.

The counter is asynchronously reset to 0000 by bringing the  $\overline{\text{RESET}}$  pin low. The circuit performs the reset operation by forcing the BCD input lines to zero, and "presetting" all four decades of counter in parallel. This affects register loading; if LOAD REGISTER is activated when the  $\overline{\text{RESET}}$  input is low, the register will also be set to zero. The  $\overline{\text{STORE}}$ ,  $\overline{\text{RESET}}$  and UP/DOWN pins are provided with pullup resistors of approximately  $75k\Omega$ .

## **BCD I/O Pins**

The BCD I/O port provides a means of transferring data to and from the device. The ICM7217 versions can multiplex data into the counter or register via thumbwheel switches, depending on inputs to the LOAD COUNTER or LOAD REG-

ISTER pins; (see below). When functioning as outputs, the BCD I/O pins will drive one standard TTL load. Common anode versions have internal pull down resistors and common cathode versions have internal pull up resistors on the four BCD I/O lines when used as inputs.

#### LOADing the COUNTER and REGISTER

The BCD I/O pins, the LOAD COUNTER (LC), and LOAD REGISTER (LR) pins combine to provide presetting and compare functions. LC and LR are 3-level inputs, being self-biased at approximately  $^{1}/_{2}V_{DD}$  for normal operation. With both LC and LR open, the BCD I/O pins provide a multiplexed BCD output of the latch contents, scanned from MSD to LSD by the display multiplex.

When either the LOAD COUNTER (Pin 12) or LOAD REGISTER (Pin 11) is taken low, the drivers are turned off and the BCD pins become high-impedance inputs. When LC is connected to  $V_{DD}$ , the count input is inhibited and the levels at the BCD pins are multiplexed into the counter. When LR is connected to  $V_{DD}$ , the levels at the BCD pins are multiplexed into the register without disturbing the counter. When both are connected to  $V_{DD}$ , the count is inhibited and both register and counter will be loaded.

The LOAD COUNTER and LOAD REGISTER inputs are edge-triggered, and pulsing them high for 500ns at room temperature will initiate a full sequence of data entry cycle operations (see Figure 3). When the circuit recognizes that either or both of the LC or LR pins input is high, the multiplex oscillator and counter are reset (to D4). The internal oscillator is then disconnected from the SCAN pin and the preset circuitry is enabled. The oscillator starts and runs with a frequency determined by its internal capacitor, (which may vary from chip to chip). When the chip finishes a full 4 digit multiplex cycle (loading each digit from D4 to D3 to D2 to D1 in turn), it again samples the LOAD REGISTER and LOAD COUNTER inputs. If either or both is still high, it repeats the load cycle, if both are floating or low, the oscillator is reconnected to the SCAN pin and the chip returns to normal operation. Total load time is digit "on" time multiplied by 4. If the Digit outputs are used to strobe the BCD data into the BCD I/ O inputs, the input must be synchronized to the appropriate digit (Figure 3). Input data must be valid at the trailing edge of the digit output.

When LR is connected to GROUND, the oscillator is inhibited, the BCD I/O pins go to the high impedance state, and the segment and digit drivers are turned off. This allows the display to be used for other purposes and minimizes power consumption. In this display off condition, the circuit will continue to count, and the CARRY/BORROW, EQUAL, ZERO, UP/DOWN, RESET and STORE functions operate as normal. When LC is connected to ground, the BCD I/O pins are forced to the high impedance state without disturbing the counter or register. See "Control Input Definitions" (Table 2) for a list of the pins that function as tri-state self-biased inputs and their respective operations.

Note that the ICM7217 and ICM7217B have been designed to drive common anode displays. The BCD inputs are high true, as are the BCD outputs.

|         | CD4502B |        |

|---------|---------|--------|

| INPUT A | N       | OUTPUT |

|         | K       |        |

| INPUT B |         |        |

|         |         |        |

| INPUT B | INPUT A | OUTPUT       |

|---------|---------|--------------|

| High    | High    | Low          |

| High    | Low     | Disconnected |

| Low     | High    | Disconnected |

| Low     | Low     | Disconnected |

**INPUT B INPUT A** OUTPUT High High Disconnected High Low Disconnected High Low High Low Low Low FIGURE 11D. CMOS TRI-STATE BUFFER

FIGURE 11C. CMOS OPEN DRAIN

..\_\_ .\_....

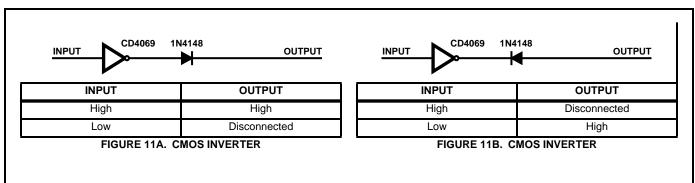

FIGURE 11. DRIVING 3-LEVEL INPUTS OF ICM7217

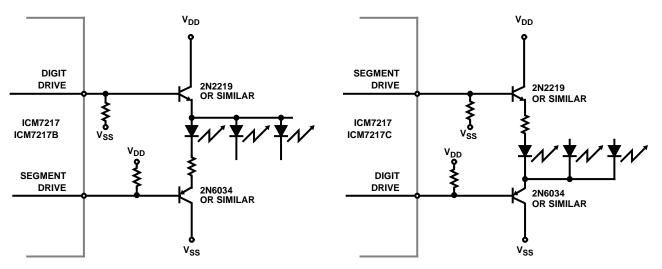

FIGURE 12A. COMMON ANODE

FIGURE 12B. COMMON CATHODE

FIGURE 12. FORCING LEADING ZERO DISPLAY

FIGURE 13A. COMMON ANODE DISPLAY

FIGURE 13B. COMMON CATHODE DISPLAY

FIGURE 13. DRIVING HIGH CURRENT DISPLAYS

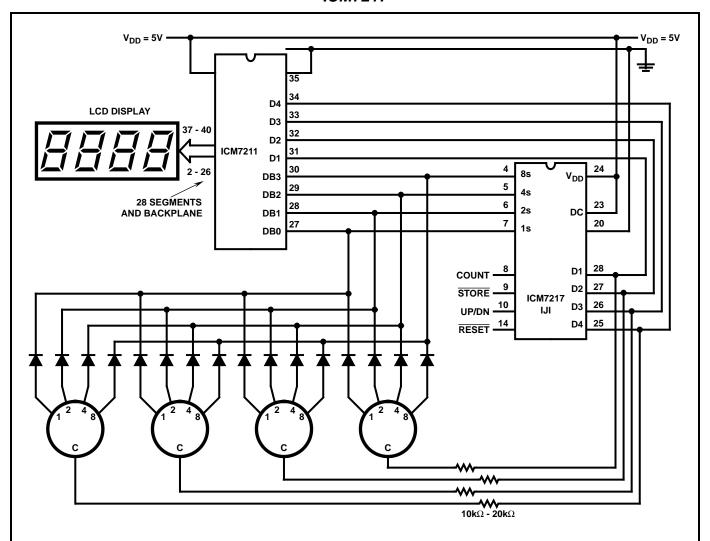

FIGURE 14. LCD DISPLAY INTERFACE (WITH THUMBWHEEL SWITCHES

The ICM7217A and the ICM7217C are used to drive common cathode displays, and the BCD inputs are low true. BCD outputs are high true.

#### **Notes on Thumbwheel Switches & Multiplexing**

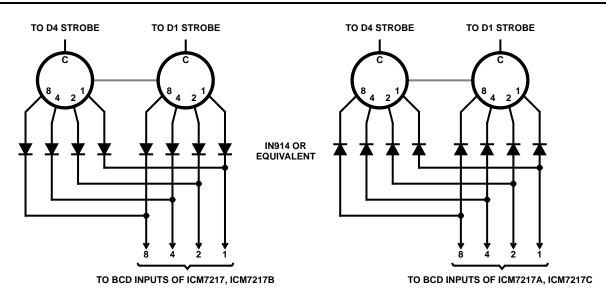

As it was mentioned, the ICM7217 is basically designed to be used with thumbwheel switches for loading the data to the device. See Figure 14 and Figure 17.

The thumbwheel switches used with these circuits (both common anode and common cathode) are TRUE BCD coded; i.e. all switches open corresponds to 0000. Since the thumbwheel switches are connected in parallel, diodes must be provided to prevent crosstalk between digits. In order to maintain reasonable noise margins, these diodes should be specified with low forward voltage drops (IN914). Similarly, if the BCD outputs are to be used, resistors should be inserted in the Digit lines to avoid loading problems.

## **Output and Input Restrictions**

LOAD COUNTER and LOAD REGISTER operations take 1.6ms typical (5ms maximum) after LC or LR are released. During this load period the EQUAL and ZERO outputs are

not valid (see Figure 3). Since the Counter and register are compared by XOR gates, loading the counter or register can cause erroneous glitches on the  $\overline{\text{EQUAL}}$  and  $\overline{\text{ZERO}}$  outputs when codes cross.

LOAD COUNTER or LOAD REGISTER, and RESET input can not be activated at the same time or within a short period of each other. Operation of each input must be delayed 1.6ms typical (5ms for guaranteed proper operation) relating to the preceding one.

Counter and register can be loaded together with the same value if LC and LR inputs become activated exactly at the same time.

Notice the setup and hold time of UP/DOWN input when it is changing during counting operation. Violation of UP/ $\overline{\text{DOWN}}$  hold time will result in incrementing or decrementing the counter by 1000, 100 or 10 where the preceding digit is transitioning from 5 to 6 or 6 to 5.

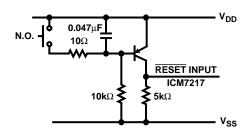

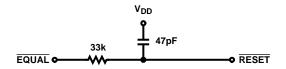

The RESET input may be susceptible to noise if its input rise time is greater than about 500µs This will present no problems when this input is driven by active devices (i.e., TTL or CMOS logic) but in hardwired systems adding virtually any

capacitance to the RESET input can cause trouble. A simple circuit which provides a reliable power-up reset and a fast rise time on the RESET input is shown on Figure 11.

When using the circuit as a programmable divider ( $\div$  by n with equal outputs) a short time delay (about 1 $\mu$ s) is needed from the  $\overline{\text{EQUAL}}$  output to the  $\overline{\text{RESET}}$  input to establish a pulse of adequate duration. (See Figure 16).

When the circuit is configured to reload the counter or register with a new value from the BCD lines (upon reaching EQUAL), loading time will be digit "on" time multiplied by four. If this load time is longer than one period of the input count, a count can be lost. Since the circuit will retain data in the register, the register need only be updated when a new value is to be entered. RESET will not clear the register.

FIGURE 15. POWER ON RESET

FIGURE 16. EQUAL TO RESET DELAY

# **Applications**

#### 3-level Inputs

ICM7217 has three inputs with 3-level logic states; High, Low and Disconnected. These inputs are: LOAD REGISTER/OFF, LOAD COUNTER/I/O OFF and DISPLAY CONT.

The circuits illustrated on Figure 11 can be used to drive these inputs in different applications.

#### **Fixed Decimal Point**

In the common anode versions, a fixed decimal point may be activated by connecting the DP segment lead from the appropriate digit (with separate digit displays) through a  $39\Omega$  series resistor to Ground. With common cathode devices, the DP segment lead should be connected through a  $75\Omega$  series resistor to  $V_{DD}$ .

To force the device to display leading zeroes after a fixed decimal point, use a bipolar transistor and base resistor in a configuration like that shown in Figure 12 with the resistor connected to the digit output driving the DP for left hand DP displays, and to the next least significant digit output for right hand DP display.

#### **Driving Larger Displays**

For displays requiring more current than the ICM7217 can provide, the circuits of Figure 13 can be used.

## **LCD Display Interface**

The low-power operation of the ICM7217 makes an LCD interface desirable. The Harris ICM7211 4 digit BCD to LCD display driver easily interfaces to the ICM7217 as shown in Figure 14. Total system power consumption is less than 5mW. System timing margins can be improved by using capacitance to ground to slow down the BCD lines.

The  $10k\Omega$  -  $20k\Omega$  resistors on the switch BCD lines serve to isolate the switches during BCD output.

#### **Unit Counter with BCD Output**

The simplest application of the ICM7217 is a 4 digit unit counter (Figure 18). All that is required is an ICM7217, a power supply and a 4 digit display. Add a momentary switch for reset, an SPDT center-off switch to blank the display or view leading zeroes, and one more SPDT switch for up/down control. Using an ICM7217A with a common-cathode calculator-type display results in the least expensive digital counter/display system available.

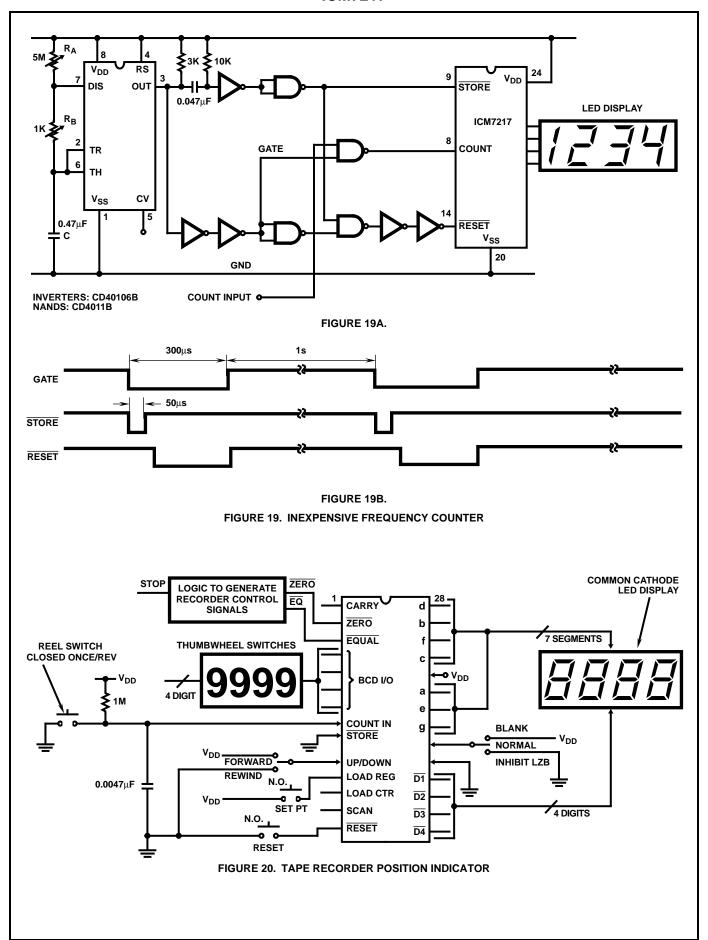

# **Inexpensive Frequency Counter/ Tachometer**

This circuit uses the <u>low power ICM7555</u> (CMOS 555) to generate the gating, <u>STORE</u> and <u>RESET</u> signals as shown in Figure 19. To provide the gating signal, the timer is configured as an a stable multivibrator, using R<sub>A</sub>, R<sub>B</sub> and C to provide an output that is positive for approximately one second and negative for approximately 300 $\mu$ s - 500 $\mu$ s. The positive waveform time is given by t<sub>WP</sub> = 0.693 (R<sub>A</sub> + R<sub>B</sub>)C while the negative waveform is given by two = 0.693 R<sub>B</sub>C. The system is calibrated by using a 5M $\Omega$  potentiometer for R<sub>A</sub> as a "coarse" control and a 1k $\Omega$  potentiometer for R<sub>B</sub> as a "fine" control. CD40106Bs are used as a monostable multivibrator and reset time delay.

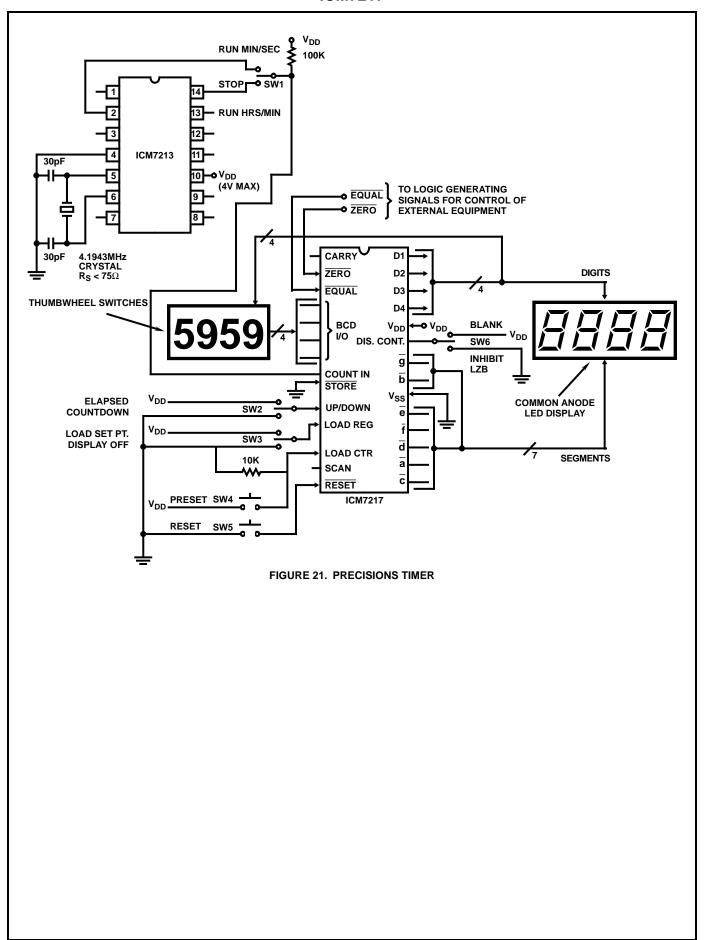

#### Tape Recorder Position Indicator/controller

The circuit in Figure 20 shows an application which uses the up/down counting feature of the ICM7217 to keep track of tape position. This circuit is representative of the many applications of up/down counting in monitoring dimensional position

In the tape recorder application, the LOAD REGISTER,  $\overline{\text{EQUAL}}$  and  $\overline{\text{ZERO}}$  outputs are used to control the recorder. To make the recorder stop at a particular point on the tape, the register can be set with the stop point and the  $\overline{\text{EQUAL}}$  output used to stop the recorder either on fast forward, play or rewind.

To make the recorder stop before the tape comes free of the reel on rewind, a leader should be used. Resetting the counter at the starting point of the tape, a few feet from the end of the leader, allows the  $\overline{\text{ZERO}}$  output to be used to stop the recorder on rewind, leaving the leader on the reel.

The  $1M\Omega$  resistor and  $0.0047\mu F$  capacitor on the COUNT INPUT provide a time constant of about 5ms to debounce the reel switch. The Schmitt trigger on the COUNT INPUT of the ICM7217 squares up the signal before applying it to the counter. This technique may be used to debounce switch-closure inputs in other applications.

#### **Precision Elapsed Time/Countdown Timer**

The circuit in Figure 21 uses an ICM7213 precision one minute/one second timebase generator using a 4.1943MHz crystal for generating pulses counted by an ICM7217B. The thumbwheel switches allow a starting time to be entered into the counter for a preset-countdown type timer, and allow the register to be set for compare functions. For instance, to make a 24-hour clock with BCD output the register can be preset with 2400 and the EQUAL output used to reset the counter. Note the 10k resistor connected between the LOAD COUNTER terminal and Ground. This resistor pulls the LOAD COUNTER input low when not loading, thereby inhibiting the BCD output drivers. This resistor should be eliminated and SW4 replaced with an SPDT center-off switch if the BCD outputs are to be used.

This technique may be used on any 3-level input. The  $100k\Omega$  pullup resistor on the count input is used to ensure proper logic voltage swing from the ICM7213. For a less expensive (and less accurate) timebase, an ICM7555 timer may be used in a configuration like that shown in Figure 19 to generate a 1Hz reference.

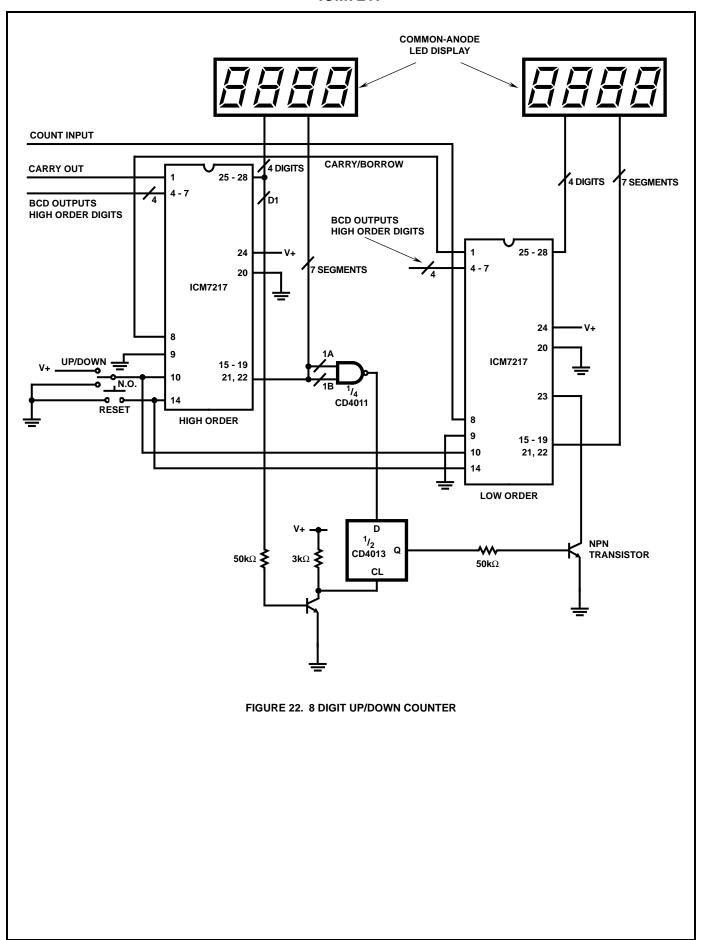

#### 8-Digit Up/down Counter

This circuit (Figure 22) shows how to cascade counters and retain correct leading zero blanking. The NAND gate detects whether a digit is active since one of the two segments  $\bar{a}$  or  $\bar{b}$  is active on any unblanked number. The flip flop is clocked by the least significant digit of the high order counter, and if this digit is not blanked, the Q output of the flip flop goes high and turns on the NPN transistor, thereby inhibiting leading zero blanking on the low order counter.

It is possible to use separate thumbwheel switches for presetting, but since the devices load data with the oscillator free-running, the multiplexing of the two devices is difficult to synchronize.

#### ICM7217

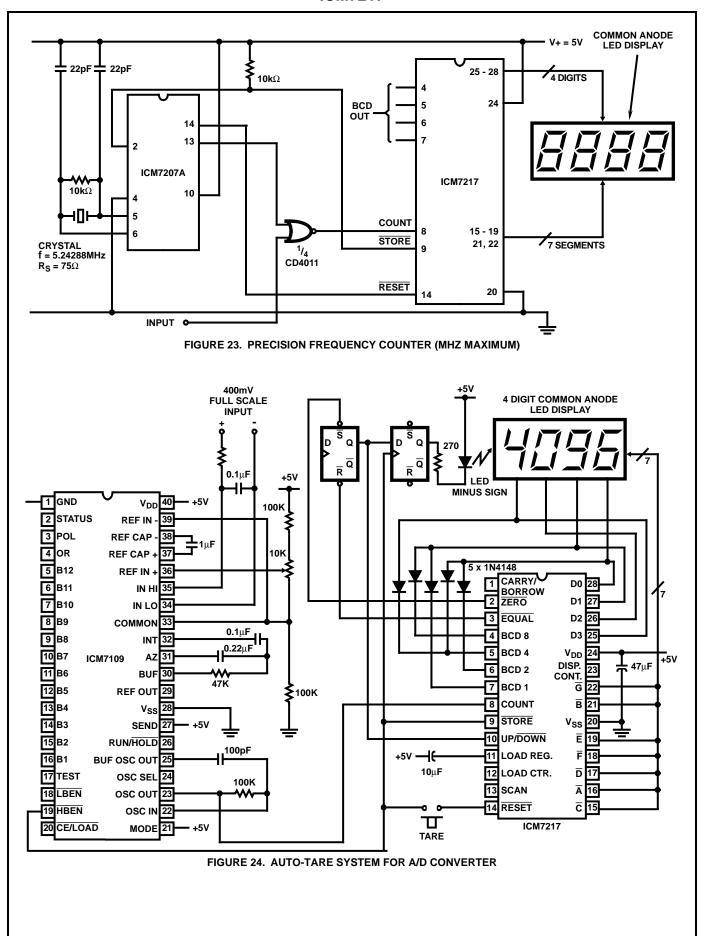

#### **Precision Frequency Counter/Tachometer**

The circuit shown in Figure 23 is a simple implementation of a four digit frequency counter, using an ICM7207A to provide the one second gating window and the  $\overline{\text{STORE}}$  and  $\overline{\text{RESET}}$  signals. In this configuration, the display reads hertz directly. With Pin 11 of the ICM7027A connected to  $V_{DD}$ , the gating time will be 0.1s; this will display tens of hertz at the least significant digit. For shorter gating times, an ICM7207 may be used (with a 6.5536MHz crystal), giving a 0.01s gating with Pin 11 connected to  $V_{DD}$ , and a 0.1s gating with Pin 11 open.

To implement a four digit tachometer, the ICM7207A with one second gating should be used. To get the display to read directly in RPM, the rotational frequency of the object to be measured must be multiplied by 60. This can be done electronically using a phase-locked loop, or mechanically by

using a disc rotating with the object with the appropriate number of holes drilled around its edge to interrupt the light from an LED to a photo-dector. For faster updating, use 0.1s gating, and multiply the rotational frequency by 600.

#### **Auto-tare System**

This circuit uses the count-up and count-down functions of the ICM7217, controlled via the EQUAL and ZERO outputs, to count in SYNC with an ICL7109A and ICL7109D Converter as shown in Figure 24. By RESETing the ICM7217 on a "tare" value conversion, and STORE-ing the result of a true value conversion, an automatic fare subtraction occurs in the result.

The ICM7217 stays in step with the ICL7109 by counting up and down between 0 and 4095, for 8192 total counts, the same number as the ICL7109 cycle. See applications note No. A047 for more details.

**TABLE 2. CONTROL INPUT DEFINITIONS ICM7217**

| INPUT                    | TERMINAL                             | VOLTAGE                                          | FUNCTION                                                                                                                                                      |

|--------------------------|--------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STORE                    | 9                                    | V <sub>DD</sub> (or floating)<br>V <sub>SS</sub> | Output Latches Not Updated<br>Output Latches Updated                                                                                                          |

| UP/DOWN                  | 10                                   | V <sub>DD</sub> (or floating)<br>V <sub>SS</sub> | Counter Counts Up<br>Counter Counts Down                                                                                                                      |

| RESET                    | 14                                   | V <sub>DD</sub> (or floating)<br>V <sub>SS</sub> | Normal Operation<br>Counter Reset                                                                                                                             |

| LOAD COUNTER/<br>I/O OFF | 12                                   | Unconnected V <sub>DD</sub> V <sub>SS</sub>      | Normal Operation Counter Loaded with BCD data BCD Port Forced to Hi Z Condition                                                                               |

| LOAD REGISTER/<br>OFF    | 11                                   | Unconnected V <sub>DD</sub> V <sub>SS</sub>      | Normal Operation Register Loaded with BCD Data Display Drivers Disabled; BCD Port Forced to Hi Z Condition, mpx Counter Reset to D4; mpx Oscillator Inhibited |

| DISPLAY CONTrol          | 23 Common Anode<br>20 Common Cathode | Unconnected  V <sub>DD</sub> V <sub>SS</sub>     | Normal Operation<br>Segment Drivers Disabled<br>Leading Zero Blanking Inhibited                                                                               |

FIGURE 17. THUMBWHEEL SWITCH/DIODE CONNECTIONS

FIGURE 18. UNIT COUNTER