### NAT9914

- Available as RoHS-compliant

- Pin compatible with TI TMS9914A

- Software compatible with NEC µPD7210 or TI TMS9914A controller chips

- Low power consumption

- Meets all IEEE 488.2 requirements

- Bus line monitoring

- Preferred implementation of requesting service

- Will not send messages when there are no Listeners

- Performs all IEEE 488.1 interface functions

- Programmable data transfer rate (T1 delays of 350 ns, 500 ns, 1.1 μs, and 2 μs)

- Automatic EOS and/or NL message detection

- Direct memory access (DMA)

- Automatically processes IEEE 488 commands and reads undered commands

- TTL-compatible CMOS device

- Programmable clock rate

20 MHz maximum

- Reduces driver overhead

- Does not lose a data byte if ATN is asserted while transmitting data

## Description

The NAT9914 IEEE 488.2 controller chip can perform all the interface functions dened by the IEEE Standard 488.1-1987, and also meets the additional requirements and recommendations of the IEEE Standard 488.2-1987. Connected between the processor and the IEEE 488 bus, the NAT9914 provides high-level management of the IEEE 488 bus, signicantly increases the throughput of driver software, and simplifies both the hardware and software design. The NAT9914 performs complete IEEE 488 Talker, Listener, and Controller functions. In addition to its numerous improvements, the NAT9914 is also completely pin compatible with the TI TMS 9914A and software compatible with the NEC  $\mu$ PD7210 and TI TMS9914A controller chips.

## IEEE 488.2 Overview

The IEEE 488.2 standard removes the ambiguities of IEEE 488.1 by standardizing the way instruments and controllers operate. It defines data formats, status reporting, error handling, and common configuration commands to which all IEEE 488.2 instruments must respond in a precise manner. It also denes a set of controller requirements. With IEEE 488.2, you gain the benets of reduced development time and cost because systems are more compatible and reliable. The NAT9914 brings the full power of IEEE 488.2 to the design engineer along with numerous other design and performance benefits, while retaining the 40-pin and 44-pin hardware congurations of the TI TMS 9914A.

## General

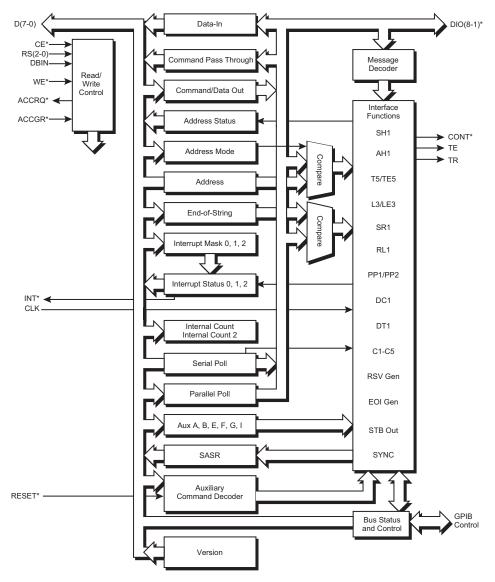

The NAT9914 manages the IEEE 488 bus. You program the IEEE 488 bus by writing control words into the appropriate registers. CPU-readable status registers supply operational feedback. The NAT9914 mode determines the function of these registers. On power up or reset, the NAT9914 registers resemble those of the TMS9914A set, with additional registers that supply extra functionality and IEEE 488.2 compatibility. In this mode, the NAT9914 is completely pin compatible with the TI TMS9914A. If you enable the 7210 mode, the registers resemble those of the NEC  $\mu$ PD7210 set, with additional registers that supply extra functionality and IEEE 488.2 compatibility. In this mode, the NAT9914 is completely pin compatible with the TI TMS9914A. If you enable the 7210 mode, the registers resemble those of the NEC  $\mu$ PD7210 set, with additional registers that supply extra functionality and IEEE 488.2 compatibility. This mode is not pin compatible with the NEC  $\mu$ PD7210. Figure 4 shows the key components of the NAT9914.

## **RoHS Compliance**

The NAT9914 is currently available from NI both in a standard package and as a RoHS-compliant chip. The chips can be ordered using the part numbers shown in the Ordering Information box below. The RoHS-compliant parts are identified through the added "F" at the end of the part number and the chip itself is marked with an e3 inside an ellipse to indicate a matte pure tin finish on the leads, in accordance with the marking recommendations defined in JEDEC JESD97.

The RoHS-compliant NAT9914 meets industry requirements for baking and maximum solder reflow temperature. The baking requirements are outlined in JEDEC J-STD-033, and

NI recommends using the solder reflow profile as shown in IPC/JEDEC J-STD-020C with a peak temperature of 260 °C, the maximum temperature they can withstand. The Moisture Sensitivity Level (MSL) for the RoHS-compliant surface mount NAT9914 ASICs is 3 (the MSL is not applicable to the NAT9914BPDF through-hole device).

#### **Ordering Information**

| NI NAT9914BPD (40-pin DIP package)<br>RoHS-compliant<br>Non RoHS-compliant<br>Sample kit (RoHS-compliant, 2 ASICs)   | NAT9914BPD-9    |

|----------------------------------------------------------------------------------------------------------------------|-----------------|

| NI NAT9914BPL (44-pin PLCC package)<br>RoHS-compliantI<br>Non RoHS-compliant<br>Sample kit (RoHS-compliant, 2 ASICs) | . NAT9914BPL-27 |

| NI NAT9914BPQ (44-pin QFP package)<br>RoHS-compliant<br>Non RoHS-compliant<br>Sample kit (RoHS-compliant, 4 ASICs)   | .NAT9914BPQ-84  |

Visit ni.com for a detailed reference manual & specifications.

#### BUY NOW!

For complete product specifications, pricing, and accessory information, call (800) 813 3693 (U.S.) or go to **ni.com/gpib**.

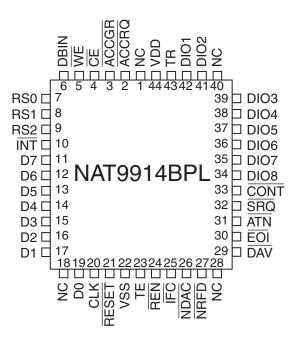

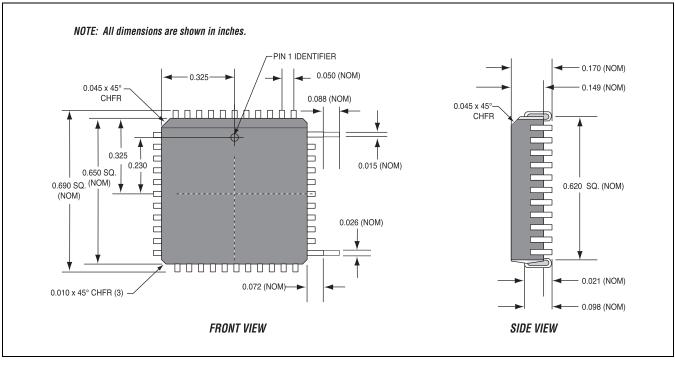

Figure 2. NAT9914BPL Pin Conguration

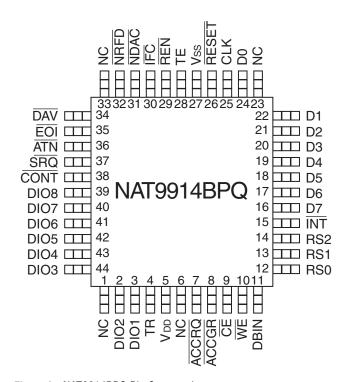

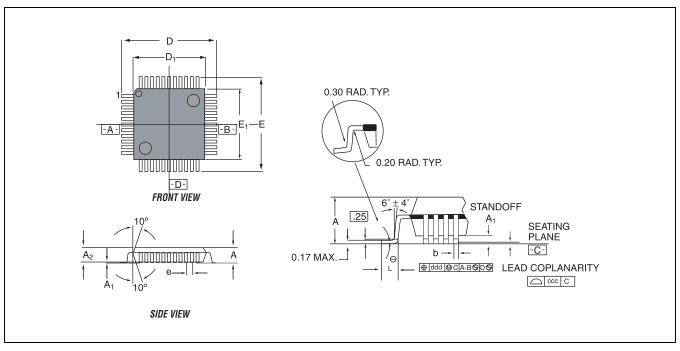

Figure 3. NAT9914BPQ Pin Conguration

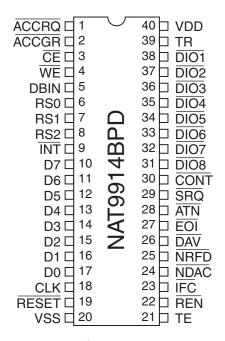

Figure 1. NAT9914BPD Pin Conguration

## **Pin Identication**

| Pin Number  |             |             |           |                            |                                                    |

|-------------|-------------|-------------|-----------|----------------------------|----------------------------------------------------|

| PLCC        | DIP         | QFP         | Mnemonic  | Туре                       | Description                                        |

| 11, 12, 13, | 10, 11, 12, | 16, 17, 18, | D(7-0)    | I/O <sup>†</sup>           | Bidirectional 3-state data bus transfers           |

| 14, 15, 16, | 13, 14, 15, | 19, 20, 21, |           |                            | commands, data, and status between the             |

| 17, 19      | 16, 17      | 22, 24      |           |                            | NAT9914 and the CPU.                               |

|             |             |             |           |                            | D0 is the most significant bit.                    |

| 4           | 3           | 9           | CE*       | 1                          | Chip Enable gives access to the register           |

|             |             |             |           |                            | selected by a read or write operation, and the     |

|             |             |             |           |                            | register selects RS(2-0).                          |

| 6           | 5           | 11          | DBIN      | I† I                       | With the Data Bus Input, you can place the         |

|             |             |             |           |                            | contents of the register selected by RS(2-0)       |

|             |             |             |           |                            | and CE* onto the data bus D(7-0). The polarity     |

|             |             |             |           |                            | of DBIN is reversed for DMA operation.             |

| 5           | 4           | 10          | WE*       | 1                          | The Write input latches the contents of the        |

|             |             |             |           |                            | data bus D(7-0) into the register selected by      |

|             |             |             |           |                            | RS(2-0).                                           |

| 3           | 2           | 8           | ACCGR*    | I.                         | The Access Grant signal selects the DIR or         |

|             |             |             |           |                            | CDOR for the current read or write cycle.          |

| 2           | 1           | 7           | ACCRQ*    | 0                          | The Access Request output asserts to request       |

|             |             |             |           |                            | a DMA Acknowledge cycle.                           |

| 20          | 18          | 25          | CLK       | I <sup>†</sup>             | The CLK input can be up to 20 MHz.                 |

| 21          | 19          | 26          | RESET*    | ľ                          | Asserting the RESET* input places the              |

|             |             |             |           |                            | NAT9914 in an initial, idle state.                 |

| 10          | 9           | 15          | INT*      | 0                          | The Interrupt output asserts when one of the       |

|             |             | -           | (OC)      |                            | unmasked interrupt conditions is true. The         |

|             |             |             | ()        |                            | NAT9914 does not drive INT* high. The INT*         |

|             |             |             |           |                            | pin must be pulled up by an external resistor.     |

| 9, 8, 7     | 8, 7, 6     | 14, 13, 12  | RS(2-0)   |                            | The Register Selects determine which register      |

| -, -, -     | -, - , -    | ,,          |           |                            | to access during a read or write operation.        |

| 25          | 23          | 30          | IFC*      | I/0 <sup>†,††</sup>        | Bidirectional control line initializes the         |

|             |             |             |           | (00)                       | IEEE 488 interface functions.                      |

| 24          | 22          | 29          | REN*      | I/O <sup>†</sup>           | Bidirectional control line selects either remote   |

|             |             |             |           | (00)                       | or local control of devices.                       |

| 31          | 28          | 36          | ATN*      | ( <i>I</i> /0 <sup>†</sup> | Bidirectional control line indicates whether       |

|             |             |             |           |                            | data on the DIO lines is an interface or device-   |

|             |             |             |           |                            | dependent message.                                 |

| 32          | 29          | 37          | SRQ*      | I/0 <sup>†</sup>           | Bidirectional control line requests service from   |

| 02          | 20          | 0.          | 0.10      | ., 0                       | the controller.                                    |

| 34, 35, 36, | 31, 32, 33, | 39, 40, 41, | DIO(8-1)* | I/0 <sup>†</sup>           | 8-bit bidirectional IEEE 488 data bus              |

| 37, 38, 39, | 34, 35, 36  | 42, 43, 44, | 2.0(0.1)  |                            |                                                    |

| 41, 42      | 37, 38      | 2, 3        |           |                            |                                                    |

| 29          | 26          | 34          | DAV*      | I/0 <sup>†</sup>           | Handshake line indicates that the data on the      |

| 20          | 20          | 01          | Britt     |                            | DIO(8-1)* lines is valid.                          |

| 27          | 25          | 32          | NRFD*     | I/0 <sup>†</sup>           | Handshake line indicates that the device is        |

|             |             | 52          |           |                            | ready for data.                                    |

| 26          | 24          | 31          | NDAC*     | I/0 <sup>†</sup>           | Handshake line indicates the completion of a       |

|             | - '         |             |           |                            | message reception.                                 |

| 30          | 27          | 35          | E01*      | I/0 <sup>†</sup>           | Bidirectional control line indicates the last byte |

| 00          | £1          | 00          | LUI       |                            | of a data message or executes a parallel poll.     |

| 23          | 21          | 28          | TE        | 0 <sup>†</sup>             | Talk Enable controls the direction of the          |

| 20          | 21          | 20          | 12        |                            | IEEE 488 data transceiver.                         |

|             |             |             |           |                            | 1222 400 data transcolver.                         |

|        | Pin Number |        |          |      |                                                                  |

|--------|------------|--------|----------|------|------------------------------------------------------------------|

| PLCC   | DIP        | QFP    | Mnemonic | Туре | Description                                                      |

| 43     | 39         | 4      | TR       | 0†   | Trigger asserts when one of the trigger conditions is satisfied. |

| 33     | 30         | 38     | CONT*    | 0†   | Controller asserts when the NAT9914 is Controller-In-Charge.     |

| 44     | 40         | 5      | VDD      | -    | Power pin - +5 V (±5%)                                           |

| 22     | 20         | 27     | VSS      | -    | Ground pin – 0 V                                                 |

| 1, 18, | -          | 1, 6,  | NC       | -    | No connect                                                       |

| 28,40  |            | 23, 33 |          |      |                                                                  |

OC= Open collector.

$^{\dagger}$  The pin contains an internal pull-up resistor of 25 k $\Omega$  to 100 k $\Omega$

\* Active low.

$^{\dagger\dagger}$  In controller applications where the CLK signal frequency is > 8 MHz, IFC\* should be pulled up with a 4.7 k $\Omega$  resistor.

<sup>+++</sup> RS0 and RS1 contain an internal pull-up resistor of 25 kΩ to 100 kΩ. RS2 does not contain an internal pull-up or pull-down resistor.

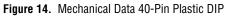

Figure 4. NAT9914 Block Diagram

### 9914 Mode Registers

In 9914 mode, the NAT9914 registers consist of all the TI TMS9914A registers and two types of additional registers – newly dened registers and paged-in registers. The NAT9914 maps the newly dened registers into the unused portion of the 9914 address space. Each paged-in register appears at Offset 2 immediately after you issue an auxiliary page-in command, and it remains there until you page another register into the same space or you issue a reset. The table below lists all the registers in the 9914 register set. See the NAT9914 Reference Manual available at ni.com for more information.

### 9914 Register Set

| Register                        | PAGE-IN | R | S(2-0 | I) | WE* | DBIN | CE* | ACCGR* |

|---------------------------------|---------|---|-------|----|-----|------|-----|--------|

| Interrupt Status 0              | U       | 0 | 0     | 0  | 1   | 1    | 0   | 1      |

| Interrupt Mask 0                | U       | 0 | 0     | 0  | 0   | 0    | 0   | 1      |

| Interrupt Status 1              | U       | 0 | 0     | 1  | 1   | 1    | 0   | 1      |

| Interrupt Mask 1                | U       | 0 | 0     | 1  | 0   | 0    | 0   | 1      |

| Address Status                  | U       | 0 | 1     | 0  | 1   | 1    | 0   | 1      |

| Interrupt Mask 2 <sup>+</sup>   | Р       | 0 | 1     | 0  | 0   | 0    | 0   | 1      |

| End-of-String <sup>+</sup>      | Р       | 0 | 1     | 0  | 0   | 0    | 0   | 1      |

| Bus Control                     | Р       | 0 | 1     | 0  | 0   | 0    | 0   | 1      |

| Accessory                       | Р       | 0 | 1     | 0  | 0   | 0    | 0   | 1      |

| Bus Status                      | U       | 0 | 1     | 1  | 1   | 1    | 0   | 1      |

| Auxiliary Command               | U       | 0 | 1     | 1  | 0   | 0    | 0   | 1      |

| Interrupt Status 2 <sup>+</sup> | Р       | 1 | 0     | 0  | 1   | 1    | 0   | 1      |

| Address                         | U       | 1 | 0     | 0  | 0   | 0    | 0   | 1      |

| Serial Poll Status <sup>+</sup> | Р       | 1 | 0     | 1  | 1   | 1    | 0   | 1      |

| Serial Poll Mode                | U       | 1 | 0     | 1  | 0   | 0    | 0   | 1      |

| Command Pass Through            | U       | 1 | 1     | 0  | 1   | 1    | 0   | 1      |

| Parallel Poll                   | U       | 1 | 1     | 0  | 0   | 0    | 0   | 1      |

| Data-In                         | U       | 1 | 1     | 1  | 1   | 1    | 0   | 1      |

| Data-In                         | U       | Х | Х     | Х  | Х   | 0    | Х   | 0      |

| Command/Data Out                | U       | 1 | 1     | 1  | 0   | 0    | 0   | 1      |

| Command/Data Out                | U       | Х | Х     | Х  | 0   | 1    | Х   | 0      |

The  $^{\dagger}$  symbol denotes features (such as registers and auxiliary commands) that are not available in the TMS9914A.

Notes for the PAGE-IN column:

- $\label{eq:U} U = \mbox{ Page-in auxiliary commands do not affect the register offset.}$

- P = The register offset is valid only after a page-in auxiliary command.

## 7210 Mode Registers

The NAT9914 registers include all the NEC  $\mu$ PD7210 registers plus two types of additional registers – extra auxiliary registers and paged-in registers. You write the extra auxiliary registers the same as standard  $\mu$ PD7210 auxiliary registers. On issuing an auxiliary page-in command, the paged-in registers appear at the same offsets as existing  $\mu$ PD7210 registers. At the end of the next CPU access, the chip pages out the paged-in registers. The following table lists all the registers in the 7210 mode register set. See the *NAT9914 Reference Manual* available at ni.com for more information.

### 7210 Register Set

| Register                            | PAGE-IN | I | A(2-0 | ) | WE* | DBIN | CE* | ACCGR* |

|-------------------------------------|---------|---|-------|---|-----|------|-----|--------|

| Data-In                             | U       | 0 | 0     | 0 | 1   | 1    | 0   | 1      |

| Data-In                             | Х       | Х | Х     | Х | Х   | 0    | Х   | 0      |

| Command/Data Out                    | U       | 0 | 0     | 0 | 0   | 0    | 0   | 1      |

| Command/Data Out                    | Х       | Х | Х     | Х | 0   | 1    | Х   | 0      |

| Interrupt Status 1                  | U       | 0 | 0     | 1 | 1   | 1    | 0   | 1      |

| Interrupt Mask 1                    | U       | 0 | 0     | 1 | 0   | 0    | 0   | 1      |

| Interrupt Status 2                  | U       | 0 | 1     | 0 | 1   | 1    | 0   | 1      |

| Interrupt Mask 2                    | U       | 0 | 1     | 0 | 0   | 0    | 0   | 1      |

| Serial Poll Status                  | N       | 0 | 1     | 1 | 1   | 1    | 0   | 1      |

| Serial Poll Mode                    | N       | 0 | 1     | 1 | 0   | 0    | 0   | 1      |

| Version                             | Р       | 0 | 1     | 1 | 1   | 1    | 0   | 1      |

| Internal Counter 2                  | Р       | 0 | 1     | 1 | 0   | 0    | 0   | 1      |

| Address Status                      | U       | 1 | 0     | 0 | 1   | 1    | 0   | 1      |

| Address Mode                        | U       | 1 | 0     | 0 | 0   | 0    | 0   | 1      |

| Command Pass Through                | N       | 1 | 0     | 1 | 1   | 1    | 0   | 1      |

| Auxiliary Mode                      | U       | 1 | 0     | 1 | 0   | 0    | 0   | 1      |

| Source/Acceptor Status <sup>+</sup> | Р       | 1 | 0     | 1 | 1   | 1    | 0   | 1      |

| Address 0                           | N       | 1 | 1     | 0 | 1   | 1    | 0   | 1      |

| Address                             | N       | 1 | 1     | 0 | 0   | 0    | 0   | 1      |

| Interrupt Status 0 <sup>+</sup>     | Р       | 1 | 1     | 0 | 1   | 1    | 0   | 1      |

| Interrupt Mask 0 <sup>+</sup>       | Р       | 1 | 1     | 0 | 0   | 0    | 0   | 1      |

| Address 1                           | N       | 1 | 1     | 1 | 1   | 1    | 0   | 1      |

| End-of-String                       | N       | 1 | 1     | 1 | 0   | 0    | 0   | 1      |

| Bus Status <sup>+</sup>             | Р       | 1 | 1     | 1 | 1   | 1    | 0   | 1      |

| Bus Control <sup>+</sup>            | Р       | 1 | 1     | 1 | 0   | 0    | 0   | 1      |

The  $^{\rm t}$  symbol denotes features (such as registers and auxiliary commands) that are not available in the NEC7210.

Notes for the PAGE-IN column:

- U = The page-in auxiliary command does not affect the register.

- N = The register offset is always valid except for immediately after a page-in auxiliary command.

- P = The register is valid only immediately after a page-in auxiliary command.

### **Preliminary DC Characteristics**

$T_A 0$  to 70 °C;  $V_{CC} = 5 V \pm 5\%$

|                       |                 | Limits |                 |      | Test                    |

|-----------------------|-----------------|--------|-----------------|------|-------------------------|

| Parameter             | Symbol          | Min    | Max             | Unit | Condition               |

| Voltage input low     | V <sub>IL</sub> | -0.5   | +0.8            | V    | -                       |

| Voltage input high    | V <sub>IH</sub> | +2.0   | V <sub>CC</sub> | V    | -                       |

| Voltage output low    | V <sub>OL</sub> | 0      | 0.4             | V    | -                       |

| Voltage output high   | V <sub>OH</sub> | +2.4   | VCC             | V    | -                       |

| Input/output          | -               | -10    | +10             | μA   | without                 |

| Leakage current       |                 |        |                 |      | internal pull-up        |

| Input/output          | -               | -200   | +200            | μA   | with internal           |

| Leakage current       |                 |        |                 |      | pull-up                 |

| Supply current        | -               | -      | 45              | mA   | -                       |

| Output current low    |                 |        |                 |      |                         |

| All pins except ACCRQ | I <sub>OL</sub> | 2      | -               | mA   | 0.4 V @ I <sub>OL</sub> |

| ACCRQ                 | I <sub>OL</sub> | 4      | -               | mA   | 0.4 V @ I <sub>OL</sub> |

| Input current low     | I <sub>IL</sub> | -      | - 0.5           | mA   | -                       |

| Supply voltage        | V <sub>DD</sub> | 4.75   | 5.25            | V    | _                       |

### Capacitance

| T₄ ( | ) to | 70 | °C; | V <sub>CC</sub> | = 5 | ٧ | ±5% |

|------|------|----|-----|-----------------|-----|---|-----|

|------|------|----|-----|-----------------|-----|---|-----|

|                       |                  | Lim | its |      | Test      |

|-----------------------|------------------|-----|-----|------|-----------|

| Parameter             | Symbol           | Min | Max | Unit | Condition |

| Input<br>capacitance  | C <sub>IN</sub>  | -   | 10  | pF   | -         |

| Output<br>capacitance | C <sub>OUT</sub> | -   | 10  | pF   | -         |

| I/O capacitance       | C <sub>I/O</sub> | -   | 10  | pF   | -         |

### **Absolute Maximum Ratings**

| Property                                    | Range                                                                                                               |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Supply voltage, V <sub>DD</sub>             | -0.5 to +7.0 V                                                                                                      |

| Input voltage, V <sub>I</sub>               | -0.5 to V <sub>DD</sub> +0.5 V                                                                                      |

| Operating temperature, T <sub>OPR</sub>     | 0 to +70° C                                                                                                         |

| Storage temperature, T <sub>STG</sub>       | -40 to +125° C                                                                                                      |

| Comment: Exposing the device to stresses al | bove those listed could cause permanent damage. The                                                                 |

|                                             | nditions outside the limits described in the operational ng conditions for extended periods may affect reliability. |

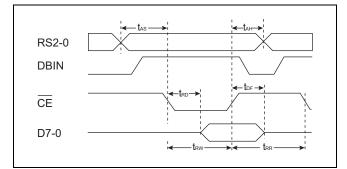

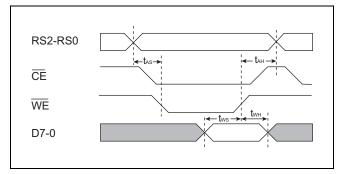

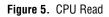

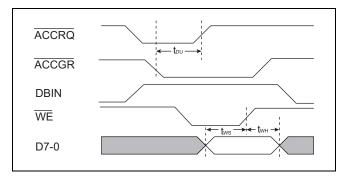

### **AC Characteristics**

T<sub>A</sub> 0 to 70 °C; V<sub>CC</sub> = 5 V ±5%

|                                                                             |                 | Lin | nits |      | Test      |

|-----------------------------------------------------------------------------|-----------------|-----|------|------|-----------|

| Parameter                                                                   | Symbol          | Min | Max  | Unit | Condition |

| Address hold from CE, WE,and DBIN                                           | t <sub>AH</sub> | 0   | -    | ns   | -         |

| Address setup to $\overline{\text{CE}}$ , $\overline{\text{WE}}$ , and DBIN | t <sub>AS</sub> | 0   | -    | ns   | -         |

| Data float from CE or DBIN                                                  | t <sub>DF</sub> | -   | 20   | ns   | -         |

| Data delay from $DBIN{\downarrow}$                                          | t <sub>DR</sub> | -   | 75   | ns   | ACCGR=0   |

| ACCRQ unassertion                                                           | t <sub>DU</sub> | -   | 20   | ns   | -         |

| Data delay from $\overline{CE}\downarrow$                                   | t <sub>RD</sub> | -   | 80   | ns   | ACCGR=1   |

| CE recovery width                                                           | t <sub>RR</sub> | 80  | -    | ns   | -         |

| CE pulse width                                                              | t <sub>RW</sub> | 80  | -    | ns   | -         |

| Data hold from WE↑                                                          | t <sub>WH</sub> | 0   | -    | ns   | -         |

| Data setup to WE↑                                                           | t <sub>WS</sub> | 60  | -    | ns   | -         |

#### Notes

•  $t_{AS}$  is the setup time to  $\overline{CE}\downarrow$  or  $\overline{WE}\downarrow$ , whichever is later.

$\bullet \qquad t_{AH} \text{ is the hold time from } \overline{W} E \uparrow \text{ or } \overline{CE} \uparrow, \text{ whichever is earlier}.$

## **Timing Waveforms**

Figure 6. DMA Read

Figure 7. CPU Write

Figure 8. DMA Write

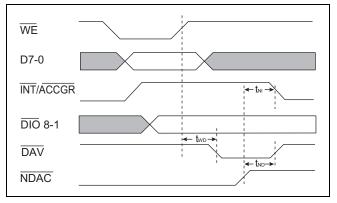

### **Source Handshake**

|                                                                                                      |                 | Limits (ns) |      | Test               |

|------------------------------------------------------------------------------------------------------|-----------------|-------------|------|--------------------|

| Parameter                                                                                            | Symbol          | Min         | Max  | Condition          |

| NDAC↑ to DAV↑                                                                                        | t <sub>ND</sub> | -           | 40   | -                  |

| $\overline{\text{NDAC}}$ to $\overline{\text{INT}}\downarrow$ or $\overline{\text{ACCRQ}}\downarrow$ | t <sub>NI</sub> | -           | 40   | INT(DOIE Bit=1)    |

|                                                                                                      |                 |             |      | ACCGR (DMA0 Bit=1) |

| WE ↑ to DAV↓                                                                                         | t <sub>WD</sub> | 2000        | 2180 | 2 µs T1, 5MHz      |

| $\overline{WE}$ $\uparrow$ to $\overline{DAV}$ $\downarrow$                                          | t <sub>WD</sub> | 1200        | 1380 | 1.1 μs T1, 5MHz    |

| WE ↑ to DAV↓                                                                                         | t <sub>WD</sub> | 600         | 780  | 500 ns T1, 5MHz    |

| $\overline{WE}$ $\uparrow$ to $\overline{DAV}$ $\downarrow$                                          | t <sub>WD</sub> | 400         | 580  | 350 ns T1, 5MHz    |

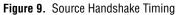

### **Acceptor Handshake**

|                                                                                                               |                 | Limits (ns) |       | Test                                   |

|---------------------------------------------------------------------------------------------------------------|-----------------|-------------|-------|----------------------------------------|

| Parameter                                                                                                     | Symbol          | Min         | Max   | Condition                              |

| DAV↓ to NDAC↑                                                                                                 | t <sub>DD</sub> |             | 35+3T |                                        |

| DAV↑ to NDAC↓                                                                                                 | t <sub>DF</sub> |             | 25    |                                        |

| $\overline{\text{DAV}}\downarrow$ to $\overline{\text{INT}}\downarrow$ or $\overline{\text{ACCRQ}}\downarrow$ | t <sub>DI</sub> |             | 50+2T | INT(DIIE Bit=1),<br>ACCGR (DMAI Bit=1) |

| $\overline{\text{DAV}}\downarrow$ to $\overline{\text{NRFD}}\downarrow$                                       | t <sub>DR</sub> |             | 20    |                                        |

| DBIN↑ to NRFD↑                                                                                                | t <sub>NR</sub> |             | 35    | Read of DIR, not in<br>Holdoff state   |

Note: T = one clock period

Figure 10. Acceptor Handshake Timing

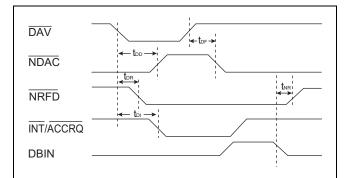

### **Response to ATN**

|                                                                         |                 | Limits (ns) |     | Test                             |

|-------------------------------------------------------------------------|-----------------|-------------|-----|----------------------------------|

| Parameter                                                               | Symbol          | Min         | Max | Condition                        |

| ATN↑ to NRFD↓                                                           | t <sub>AF</sub> |             | 35  | Acceptor handshake holdoff       |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{NDAC}}\downarrow$ | t <sub>AN</sub> |             | 35  | $AIDS \mathop{\rightarrow} ANRS$ |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{TE}}\downarrow$   | t <sub>AT</sub> |             | 30  | $TACS \to TADS$                  |

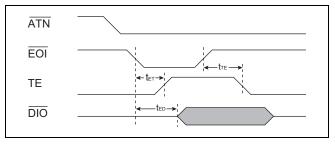

Figure 11. ATN Response Timing

### Parallel Poll

|                                                                              |                 | Limits (ns) |     | Test                    |

|------------------------------------------------------------------------------|-----------------|-------------|-----|-------------------------|

| Parameter                                                                    | Symbol          | Min         | Max | Condition               |

| $\overline{\text{EOI}}\downarrow$ to $\overline{\text{DIO}}\downarrow$ valid | t <sub>ED</sub> |             | 90  | $PPSS \rightarrow PPAS$ |

| EOI↓ to TE↑                                                                  | t <sub>ET</sub> |             | 30  | $PPSS \to PPAS$         |

| EOI↑ to TE↓                                                                  | t <sub>TE</sub> |             | 30  | $PPAS\toPPSS$           |

Figure 12. Parallel Poll Response Timing

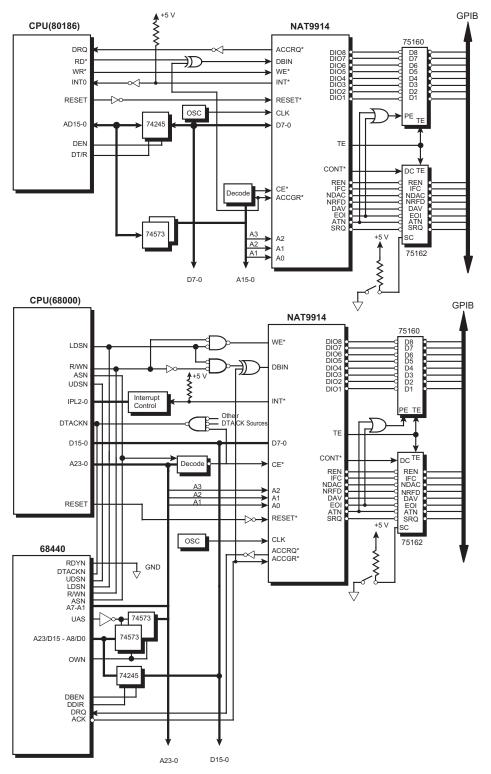

Figure 13. Typical CPU Systems with NAT9914

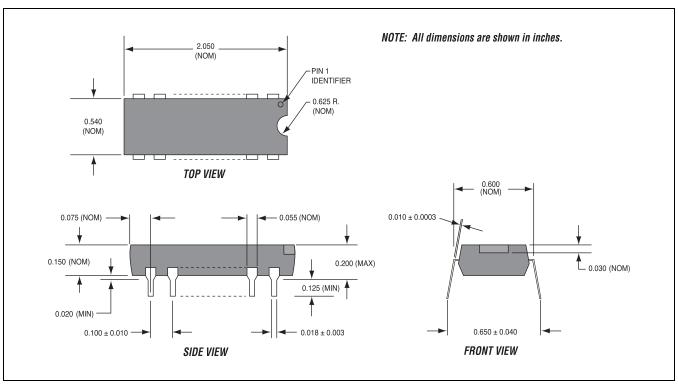

Figure 15. Mechanical Data 44-Pin PLCC

Figure 16. Mechanical 44-Pin QFP

| Dimensions     | Tolerance     | Value (in mm) |

|----------------|---------------|---------------|

| A              | max.          | 2.35          |

| A <sub>1</sub> | -             | 0.25 max.     |

| A <sub>2</sub> | + 0.10/-0.05  | 2.00          |

| D              | ± 0.25        | 17.20         |

| D <sub>1</sub> | ± 0.10        | 14.00         |

| E              | ± 0.25        | 17.20         |

| E <sub>1</sub> | ± 0.10        | 14.00         |

| L              | + 0.15/- 0.10 | 0.88          |

| e              | basic         | 1.00          |

| b              | ± 0.05        | 0.35          |

| θ              | -             | 0 to 7°       |

| ddd            | -             | 0.20 nom.     |

| CCC            | max.          | 0.10          |

# **NI Services and Support**

NI has the services and support to meet your needs around the globe and through the application life cycle – from planning and development through deployment and ongoing maintenance. We offer services and service levels to meet customer requirements in research, design, validation, and manufacturing. Visit ni.com/services.

## **Training and Certification**

NI training is the fastest, most certain route to productivity with our products. NI training can shorten your learning curve, save development time, and reduce maintenance costs over the application life cycle. We schedule instructor-led courses in cities worldwide, or we can hold a course at your facility. We also offer a professional certification program that identifies individuals who have high levels of skill and knowledge on using NI products. Visit ni.com/training.

## **Professional Services**

Our Professional Services Team is comprised of NI applications engineers, NI Consulting Services, and a worldwide National Instruments Alliance Partner program of more than 600 independent consultants and integrators.

Services range from start-up assistance to turnkey system integration. Visit ni.com/alliance.

## **OEM Support**

We offer design-in consulting and product integration assistance if you want to use our products for OEM applications. For information about special pricing and services for OEM customers, visit ni.com/oem.

## **Local Sales and Technical Support**

In offices worldwide, our staff is local to the country, giving you access to engineers who speak your language. NI delivers industry-leading technical support through online knowledge bases, our applications engineers, and access to 14,000 measurement and automation professionals within NI Developer Exchange forums. Find immediate answers to your questions at ni.com/support.

We also offer service programs that provide automatic upgrades to your application development environment and higher levels of technical support. Visit ni.com/ssp.

## **Hardware Services**

### **NI Factory Installation Services**

NI Factory Installation Services (FIS) is the fastest and easiest way to use your PXI or PXI/SCXI combination systems right out of the box. Trained NI technicians install the software and hardware and configure the system to your specifications. NI extends the standard warranty by one year on hardware components (controllers, chassis, modules) purchased with FIS. To use FIS, simply configure your system online with ni.com/pxiadvisor.

### **Calibration Services**

NI recognizes the need to maintain properly calibrated devices for high-accuracy measurements. We provide manual calibration procedures, services to recalibrate your products, and automated calibration software specifically designed for use by metrology laboratories. Visit ni.com/calibration.

### **Repair and Extended Warranty**

NI provides complete repair services for our products. Express repair and advance replacement services are also available. We offer extended warranties to help you meet project life-cycle requirements. Visit ni.com/services.

National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the *Terms of Use* section on ni.com/legal for more information about National Instruments trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. A National Instruments Alliance Partner is a business entity independent from NI and has no agency, partnership, or joint-venture relationship with NI.