Data brief

#### L9963E single node in a distributed BMS System

#### **Features**

- Single node L9963E board for distributed multi-cell BMS

- To be used with EVAL-L9963E-MCU or EVAL-L9963E as second stage or stacked with additional EVAL-L9963E-NDS

- Measures from 4 to 14 cells in series, with 0 us desynchronization delay between samples. Supports also busbar connection without altering cell results

- Coulomb counter supporting pack overcurrent detection in both ignition on and off states

- Fully synchronized current and voltage samples

- 16-bit voltage measurement

- Communication between nodes through a 2.66 Mbps isolated serial communication with regenerative buffer, supporting dual access ring

- · Transformer based isolation

- Up to 4 analog inputs for NTC sensing, plus PCB temperature sensing

- · Hot-plug protection circuit

#### **Description**

The EVAL-L9963E-NDS is a hardware tool for L9963E for Li-ION battery management application. The board is intended to be used as a single node in a distributed BMS. EVAL-L9963E-NDS is needed when the total number of battery cells to be managed exceeds 14. The number of nodes to be stacked depends on total battery voltage, additional nodes can be added via additional EVAL-L9963E-NDS. A maximum of 31 total nodes beyond the base node EVAL-L9963E-MCU can be stacked. It has to be used in conjunction with EVAL-L9963E-MCU as second stage or stacked with additional EVAL-L9963E-NDS.

EVAL-L9963E-NDS allows the user to manage up to 14 channels for cell voltage sensing, one channel for current sensing, and up to 4 analog input for temperature sensing (plus an additional on-board NTC to sense PCB temperature). The board provides additional protection for hot plug.

EVAL-L9963E-NDS is not intended to be used as a standalone evaluation board but with EVAL-L9963E-MCU.

# Product status link EVAL-L9963E-NDS

| Product summary |                 |  |

|-----------------|-----------------|--|

| Order code      | EVAL-L9963E-NDS |  |

Reference EVAL-L9963E-NDS Evaluation board

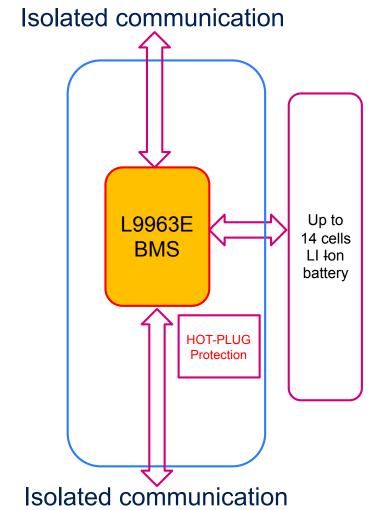

## 1 Block diagram

EVAL-L9963E-NDS provides a single L9963E device with the external connectors for battery and isolated communication.

Figure 1. EVAL-L9963E-NDS block diagram

DB4439 - Rev 1 page 2/14

## 2 Featured components

The EVAL-L9963E-NDS can be considered as an additional node in a distributed BMS system, the first stage should be implemented with an EVAL-L9963E-MCU or an EVAL-L9963E-NDS. In the following table there is a short description of all ST featured components.

**Table 1. Featured components**

| Name   | Description                                         |

|--------|-----------------------------------------------------|

| L9963E | Automotive chip for battery management applications |

DB4439 - Rev 1 page 3/14

## 3 Minimum system requirements

- EVAL-L9963E-MCU as first stage of a distributed BMS system

- Power supply:

- at least 3 output 0 30 V (if possible 60 V):

- 1 output to power L9963E (0:60 V)

- 1 output to simulate Cells common mode voltage (0:60 V)

- 1 output to simulate Cell voltage (0:5 V)

DB4439 - Rev 1 page 4/14

### 4 Connectors

Table 2. EVAL-L9963E-NDS connectors

| Name | Description                                                                   | Configuration        |

|------|-------------------------------------------------------------------------------|----------------------|

|      | Isolated serial communication port:                                           |                      |

|      | 1. Fault Line supply                                                          |                      |

| ISOL | 2. ISOLm                                                                      | USB Type A connector |

|      | 3. ISOLp                                                                      |                      |

|      | 4. FaultL                                                                     |                      |

|      | Isolated serial communication port:                                           |                      |

|      | 1. Fault Line supply                                                          |                      |

| ISOH | 2. ISOHm                                                                      | USB Type A connector |

|      | 3. ISOHp                                                                      |                      |

|      | 4. FaultH                                                                     |                      |

|      | Battery connector:                                                            |                      |

|      | 1. Cell 14                                                                    |                      |

|      | 2. Cell 12                                                                    |                      |

|      | 3. Cell 10                                                                    |                      |

|      | 4. Cell 8                                                                     |                      |

|      | 5. Cell 6                                                                     |                      |

|      | 6. Cell 4                                                                     |                      |

|      | 7. Cell 2                                                                     |                      |

|      | 8. Cell 0                                                                     |                      |

|      | 9. Ground                                                                     |                      |

|      | 10. Current sensor resistor negative pin                                      |                      |

|      | 11. NTC 1-                                                                    |                      |

|      | 12. NTC 2-                                                                    |                      |

|      | 13. NTC3 -                                                                    |                      |

| P2   | 14. NTC4 –                                                                    | Multi pin connector  |

|      | 15. VBAT                                                                      |                      |

|      | 16. Cell 13                                                                   |                      |

|      | 17. Cell 11                                                                   |                      |

|      | 18. Cell 9                                                                    |                      |

|      | 19. Cell 7                                                                    |                      |

|      | 20. Cell 5                                                                    |                      |

|      | 21. Cell 3<br>22. Cell 1                                                      |                      |

|      |                                                                               |                      |

|      |                                                                               |                      |

|      | <ul><li>24. Current sensor resistor positive pin</li><li>25. NTC 1+</li></ul> |                      |

|      | 26. NTC 2+                                                                    |                      |

|      | 27. NTC3 +                                                                    |                      |

|      | 28. NTC4 +                                                                    |                      |

|      | ZU. INTO+ T                                                                   |                      |

DB4439 - Rev 1 page 5/14

#### 5 Hot plug protection

RHOT 47 GND 3

VREG

100k 10K 3

RPD RG 4

STS8N6LF6AG

CGS

47nF

Figure 2. Hot plug protection circuit

The structure in Figure 2 on the GND path will help with standing the hot plug by limiting the in rush current incoming from any L9963E pin connected to the centralized clamp.

Working principle is the following:

- When L9963E is OFF and no cell is connected, the VREG regulator is shut down and MHOT is safely kept off by the RPD pull down resistor.

- Upon the first hot plug event, inrush current incoming from the centralized clamp is forced to flow into RHOT resistor, which offers proper limiting.

- Any VDS voltage spike on MOSFET during hot plug could be coupled to the gate via the parasitic Miller capacitance. Unwanted turn-on is safely filtered by CGS, that helps keeping VGS below the threshold voltage. Hence the MOSFET will stay OFF during hot plug.

- If the hot plug voltage is enough to guarantee L9963E powerup the MOSFET will be turned on by VREG regulator with a proper delay, obtained through RG gate resistor.

- Finally, during L9963E normal operation the MOSFET will be ON, thus guaranteeing a very low impedance path (few  $m\Omega$ ) on the AGND line.

- Such a small shift between L9963E GND and battery pack GND will not alter cell measurement at all, since cell ADCs are fully differential. Hence, both cell and sum of cells measurements will be accurate.

- Moreover, since L9963E only drains few mA from the battery pack, error introduced on the VBAT stack measurement via internal voltage divider will be negligible.

- Also the CSA used for Coulomb Counting features a fully differential architecture, thus being immune to such a small common mode shift.

DB4439 - Rev 1 page 6/14

### **Distributed BMS topology**

EVAL-L9963E-NDS is intended to be used in combination with EVAL-L9963E-MCU as an additional node of a distributed BMS system. EVAL-L9963E-MCU are needed as first stage and up to 31 EVAL-L9963E-NDS can be connected as additional nodes. In Figure 3 a possible layout for a distributed BMS using multiple EVAL-L9963E-NDS together with EVAL-L9963E-MCU.

(optional) dual ring configuration 14x Cells Isolated communication line EVAL-L9963E-ND\$ Multi Cell LI-ION battery Max 31x Nodes EVAL-L9963E MCU 14x Cells EVAL-L9963E-NDS 14x Cells

Figure 3. Distributed BMS architecture

DB4439 - Rev 1

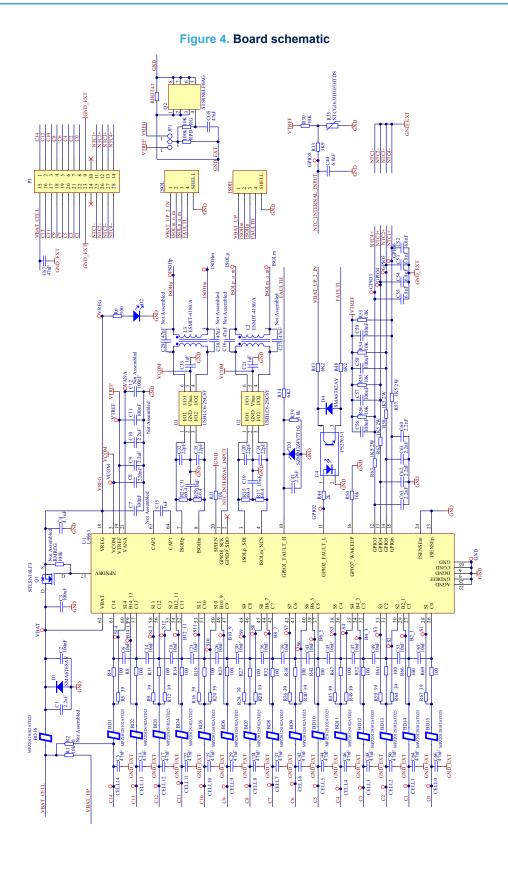

### EVAL-L9963E-NDS Evaluation board schematic

DB4439 - Rev 1 page 8/14

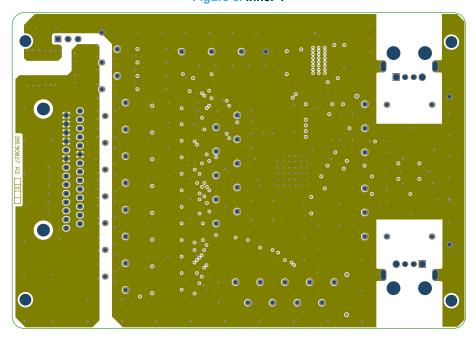

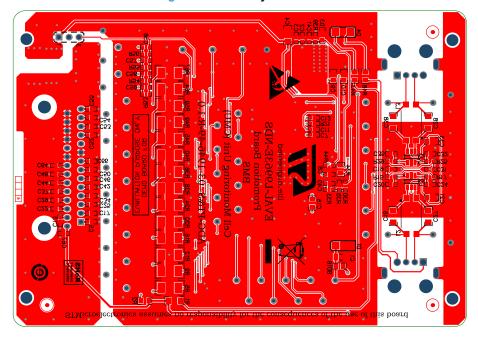

## 8 Board layout

STMicroelectronics assumes no responsibility for the consequences of the use of this board

STMicroelectronics assumes no responsibility for the consequences of the use of this board

STMicroelectronics assumes no responsibility for the consequences of the use of this board

STMICROELECTRONICS ASSUMENT OF THE CONSTRUCTION OF

Figure 5. Assembly TOP

DB4439 - Rev 1 page 9/14

Figure 7. Inner 2

Figure 8. Assembly BOTTOM

DB4439 - Rev 1 page 10/14

## **Revision history**

**Table 3. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 03-Mar-2021 | 1       | Initial release. |

DB4439 - Rev 1 page 11/14

#### **Contents**

| 1   | Block diagram                              | 2  |

|-----|--------------------------------------------|----|

| 2   | Featured components                        | 3  |

| 3   | Minimum system requirements                | 4  |

| 4   | Connectors                                 | 5  |

| 5   | Hot plug protection                        | 6  |

| 6   | Distributed BMS topology                   | 7  |

| 7   | EVAL-L9963E-NDS Evaluation board schematic | 8  |

| 8   | Board layout                               | 9  |

| Rev | vision history                             | 11 |

# **List of figures**

| Figure 1. | EVAL-L9963E-NDS block diagram | . 2 |

|-----------|-------------------------------|-----|

| Figure 2. | Hot plug protection circuit   | . 6 |

| Figure 3. | Distributed BMS architecture  | . 7 |

| Figure 4. | Board schematic               | . 8 |

| Figure 5. | Assembly TOP                  | . 9 |

| Figure 6. | Inner 1                       | . 9 |

| Figure 7. | Inner 2                       | 10  |

| Figure 8. | Assembly BOTTOM               | 10  |

DB4439 - Rev 1

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DB4439 - Rev 1 page 14/14