#### Product Change Notification / SYST-19GWSQ227

|   | _ | • | _ | _ |

|---|---|---|---|---|

|   | 2 | T | 0 | • |

| _ | а |   | C | • |

22-Mar-2021

#### **Product Category:**

32-bit Microcontrollers

### **PCN Type:**

**Document Change**

#### **Notification Subject:**

ERRATA - SAM D10 Series Family Silicon Errata and Data Sheet Clarifications

#### **Affected CPNs:**

SYST-19GWSQ227\_Affected\_CPN\_03222021.pdf SYST-19GWSQ227\_Affected\_CPN\_03222021.csv

#### **Notification Text:**

SYST-19GWSQ227

Microchip has released a new Product Documents for the SAM D10 Series Family Silicon Errata and Data Sheet Clarifications of devices. If you are using one of these devices please read the document located at SAM D10 Series Family Silicon Errata and Data Sheet Clarifications.

**Notification Status: Final**

**Description of Change:** This revision includes numerous typographical updates, along with the following new information: The I2C standard uses the terminology "master" and "slave". The equivalent Microchip terminology used in this document is "Host" and "Client" respectively.

The following Errata were added:

- 2. Module: "SERCOM I2C STATUS.CLKHOLD bit"

- 3. Module: "Device Standby Wakeup"

Updated the following Data Sheet Clarifications with new images and descriptions:

- 2. Module: "OSC32K and XOSC32K EN1K bit"

- 4. Module: "Brown-Out Detectors (BOD) Characteristics"

- 5. Module: "ADC Power Management"

- 9. Module: "NVMCTRL NVM User Configuration"

The following Data Sheet Clarifications were added:

• 14. Module: "SERCOM I2C INTFLAG.DRDY bit"

- 15. Module: "NVMCTRL AUX1 Device Configuration Register"

- 16. Module: "DMAC SRCADDR and DSTADDR Registers' Descriptions"

- 17. Module: "RTC and TC READREQ.RCONT bit fields"

- 18. Module: "DMAC BASEADDR, WRBADDR and DESCADDR registers alignment"

- 19. Module: "DAC Maximum Input Clock Frequency"

- 20. Module: "DAC Start Conversion Event"

- 21. Module: "DAC Electrical Characteristics"

- 22. Module: "ADC Electrical Characteristics at 85°C"

- 23. Module: "Bandgap Electrical Characteristics at 85°C"

- 24. Module: "ADC Electrical Characteristics at 105°C"

- 25. Module: "Bandgap Electrical Characteristics at 105°C"

The following Data Sheet Clarifications were removed:

• Module: 32 kHz Ultra-Low Power Internal Oscillator (OSCULP32K) Operation

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

**Change Implementation Status:** Complete

**Date Document Changes Effective:** 22 Mar 2021

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

#### **Attachments:**

SAM D10 Series Family Silicon Errata and Data Sheet Clarifications

Please contact your local Microchip sales office with questions or concerns regarding this notification.

#### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

#### Affected Catalog Part Numbers (CPN)

ATSAMD10-XMINI

ATSAMD10C13A-SSNT

ATSAMD10C13A-SSUT

ATSAMD10C14A-SSNT

ATSAMD10C14A-SSUT

ATSAMD10D13A-MNT

ATSAMD10D13A-MUT

ATSAMD10D13A-SSNT

ATSAMD10D13A-SSUT

ATSAMD10D14A-MNT

ATSAMD10D14A-MUT

ATSAMD10D14A-MUTB5

ATSAMD10D14A-SSNT

ATSAMD10D14A-SSUT

ATSAMD10D14A-UUT

ATSAMD10D14A-UUTB5

ATSAMD10D14A-UUTBN

ATSAMD10D14A-W-NG

### SAM D10 Series Family Silicon Errata and Data Sheet Clarification

The SAM D10 Series family of devices that you have received conform functionally to the current Device Data Sheet (Atmel-42242H-SAM-D10-Datasheet\_09/2016), except for the anomalies described in this document.

#### **New Silicon Errata Issues**

Note:

This document provides information on new errata issues for the SAM D10 Series of devices. Please refer to the current device data sheet for all pre-existing silicon errata issues.

#### 1. Module: BOD12

On External Reset, the BOD12 reset cause can also be triggered.

#### Work around

Ignore the BOD12 reset cause if External reset cause is set.

#### Affected Silicon Revisions

| Α | В |  |  |  |

|---|---|--|--|--|

| Χ |   |  |  |  |

## 2. Module: SERCOM I<sup>2</sup>C STATUS.CLKHOLD bit

The SERCOM I<sup>2</sup>C STATUS.CLKHOLD bit can be written, whereas it is a read-only status bit in both Host and Client modes.

#### Work around

Do not clear the STATUS.CLKHOLD bit to preserve the current clock hold state.

#### Affected Silicon Revisions

| Α | В |  |  |  |

|---|---|--|--|--|

| Χ | Х |  |  |  |

#### 3. Module: Device Standby Wakeup

Upon wakeup from standby with the Arm® Core register PRIMASK = 1, the first instruction fetched by the CPU in Flash memory will be the first instruction following the Wait For Interrupt (WFI) instruction. This instruction may be returned corrupted and lead to unpredictable behavior.

If the PRIMASK = 0, the first instruction fetched by the CPU will be the first instruction of the interrupt handler. This one will be correctly returned to the CPU.

#### Work around

The following two possible workarounds can be used independently:

- Disable Flash sleep in Standby Sleep mode (SLEEPPRM = DISABLED).

- 2. Place the standby sleep function in SRAM and make sure that at least one dummy Flash fetch is completed before exiting the function. This can be achieved by reading 2 data in memory, with addresses separated by at least the cache size. Because the first read could be a cache hit, the second one will be a cache miss and will generate a real read in memory.

The following code example may be used:

```

__attribute__((noinline, section(".ramfunc")))

void ram_sleep(void)

{

__DSB();

__WFI();

//

```

The following sequence ensures that the Flash is ready before returning from the RAM code:

```

#define CACHE_SIZE_IN_BYTES 64

((volatile unsigned int

*)FLASH_ADDR)[CACHE_SIZE_IN_BYTES/

sizeof(unsigned int)];

//will read a word at FLASH_ADDR +

0x40 in this case

```

```

((volatile unsigned int

*)FLASH_ADDR)[(CACHE_SIZE_IN_BYTES*2

)/sizeof(unsigned int)];

//will read a word at FLASH_ADDR +

0x80 in this case

}

```

#### Affected Silicon Revisions

| Α | В |  |  |  |

|---|---|--|--|--|

| Χ | Χ |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the Device Data Sheet (Atmel-42242H-SAM-D10-Datasheet\_09/2016).

Note:

Corrections in tables and paragraphs are shown in **BOLD**. Where possible, the original bold text formatting has been removed for clarity.

#### 1. Module: Package Marking Information

In the current device data sheet, the SAM D10 Package Marking Information is missing. The information is as follows:

All devices are marked with the Atmel logo, a shortened ordering code and additional marking (the two last lines).

### YYWW R ARM XXXXXX CC

#### Where:

"Y" or "YY": Manufacturing Year (last OR two last digit(s))

• "WW": Manufacturing Week

· "R": Revision

"XXXXXX": Lot number"CC": Internal Code

#### 2. Module: OSC32K and XOSC32K EN1K bit

The OSC32K and XOSC32K EN1K bits and the associated 1.024 kHz clock outputs are referenced several times in the device data sheet. The OSC32K and XOSC32K EN1K bits and the associated 1.024 kHz clock outputs are not implemented for this device.

#### 3. Module: OSCULP32K Characteristics

The value for the minimum output frequency is incorrect. The corrected information is shown in **BOLD** below:

TABLE 34-43: ULTRA-LOW POWER INTERNAL 32 KHz RC OSCILLATOR CHARACTERISTICS

| Symbol | Parameter           | Conditions                                                                              | Min. | Тур.   | Max. | Units |  |

|--------|---------------------|-----------------------------------------------------------------------------------------|------|--------|------|-------|--|

| fouт   |                     | Calibrated against a 32.768 kHz reference at 25°C, over [-40, +85]C, over [1.62, 3.63]V | 27.8 | 32.768 | 37.8 |       |  |

|        | Output<br>frequency | Calibrated against a 32.768 kHz reference at 25°C, at VDD=3.3V                          | 32.5 | 32.768 | 32.8 | kHz   |  |

|        |                     | Calibrated against a 32.768 kHz reference at 25°C, over [1.62, 3.63]V                   | 31.9 | 32.768 | 33.1 |       |  |

| Duty   | Duty Cycle          |                                                                                         |      | 50     |      | %     |  |

## 4. Module: Brown-Out Detectors (BOD) Characteristics

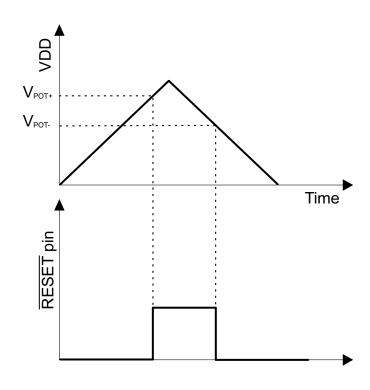

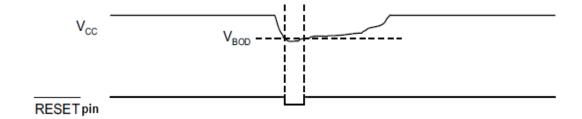

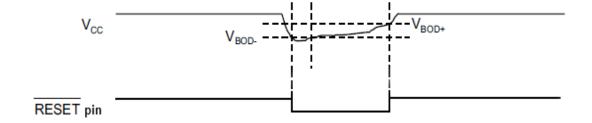

Figures 34-2, 34-3, 34-4, 39-2, 39-3 and 39-4 have an incorrect reset Polarity value. The corrected figures are as shown below:

FIGURE 34-2 and 39-2: POR OPERATING PRINCIPLE:

#### FIGURE 34-3 AND 39-3: BOD33 HYSTERESIS OFF

#### FIGURE 34-4 AND 39-4: BOD33 LEVEL VALUE

#### 5. Module: ADC Power Management

Section 30.5.2 has new information added, and is shown in **BOLD** below:

The ADC will continue to operate in any sleep modes where the selected source clock is running. The ADC's interrupts can be used to wake up the device from sleep modes (**Except the OVERRUN interrupt**). The events can trigger other operations in the system without exiting the sleep modes. Refer to "PM – Power Manager" on page 110 for details on the different sleep modes.

Section 30.6.12 has new information added and is shown in **BOLD** below:

When RUNSTDBY is one, any enabled ADC interrupt source can wake up the CPU (except the OVERRUN interrupt). While the CPU is sleeping, ADC conversion can only be triggered by events.

#### 6. Module: EVSYS USER Register Summary

The USER register is displayed incorrectly in the Register Summary. The correct USER register summary section is displayed as follows:

| 0x0120 | USER0  | 7:0 |  |  | CHANNEL[3:0]  |  |  |  |

|--------|--------|-----|--|--|---------------|--|--|--|

|        |        |     |  |  |               |  |  |  |

| 0x0136 | USER22 | 7:0 |  |  | CHANNEL [3:0] |  |  |  |

#### 7. Module: EVSYS Principle of Operation

Section 23.6.1 has some incorrect information in the second part, the corrected information is shown in **BOLD**.

The EVSYS allows for communication between peripherals through events. Peripherals that respond to events (event users) are connected to multiplexers which have all event channels as input. Each peripheral emitting events (Event Generator) can be connected to one or multiple event users, using one or multiple channels of the Event System.

#### 8. Module: NVMCTRL - CTRLA Register

Table 21-6 for the Command bit displays the Write Lock bits as a feature. The Write Lock bits are not supported on this device.

## 9. Module: NVMCTRL - NVM User Configuration

Tables 21-2 and 21-3 show incorrect values on the last row of each table. These values are not possible per the device memory density.

#### 10. Module: RTC - Overview

The overview section for the RTC had a new verbiage, which has been highlighted in **BOLD**.

The Real-Time Counter (RTC) is a 32-bit counter with a 10-bit programmable prescaler that typically runs continuously to keep track of time. The RTC can wake up the device from sleep modes using the alarm/compare wake up, periodic wake up or overflow wake up mechanisms.

# The RTC is clocked by any clock sources selectable through the Generic Clock module (GCLK), providing the signal GCLK\_RTC.

The RTC can generate periodic peripheral events from outputs of the prescaler, as well as alarm/compare interrupts and peripheral events, which can trigger at any counter value. Additionally, the timer can trigger an overflow interrupt and peripheral event, and be reset on the occurrence of an alarm/compare match. This allows periodic interrupts and peripheral events at very long and accurate intervals.

The 10-bit programmable prescaler can scale down the clock source, and hence a wide range of resolutions and time-out periods can be configured. With a 32.768 kHz clock source, the minimum counter tick interval is 30.5 µs, and time-out periods can range up to 36 hours. With the counter tick interval configured to 1s, the maximum time-out period is more than 136 years.

#### 11. Module: SYSCTRL - XOSC Register

The register description for the GAIN bit is updated. The newly added text is shown in **BOLD**.

These bits select the gain for the oscillator. The listed maximum frequencies are recommendations, and might vary based on capacitive load and crystal characteristics. Those bits must be properly configured even when the Automatic Amplitude Gain Control is active.

#### 12. Module: SYSCTRL - XOSC Register

The AMPGC bit is updated with a new note as shown below in **BOLD**.

Note: The configuration of the oscillator gain is mandatory even if AMPGC feature is enabled at startup.

## 13. Module: Debug Operation - DCFGn Register

The register is erroneously listed as Read/Write. This register is Read Only.

#### 14. Module: SERCOM I<sup>2</sup>C INTFLAG.DRDY bit

The description of the SERCOM I<sup>2</sup>C INTFLAG.DRDY bit is not complete. The **BOLD** part below needs to be added:

This flag is set when a I<sup>2</sup>C client byte transmission **or reception** is successfully completed.

## 15. Module: NVMCTRL AUX1 Device Configuration Register

Contrary to what is stated in the data sheet, the DCFG0/1 registers located in the AUX1 Area 2 are internal **read-only** registers and must not be written.

## 16. Module: DMAC SRCADDR and DSTADDR Registers' Descriptions

The description for the DMAC SRCADDR register is replaced by the following:

#### Bits 31:0 - SRCADDR[31:0] Transfer Source Address

This bit field holds the block transfer source address.

When source address incrementation is disabled (BTCTRL.SRCINC=0), SRCADDR corresponds to the last beat transfer address in the block transfer.

When source address incrementation is enabled (BTCTRL.SRCINC=1), SRCADDR is calculated as follows: If BTCTRL.STEPSEL=1:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1) \cdot 2^{STEPSIZE}$

If BTCTRL.STEPSEL=0:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1)$

- SRCADDR<sub>START</sub> is the source address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

- BEATSIZE is the configured number of bytes in a beat

- STEPSIZE is the configured number of beats for each incrementation

The description for the DMAC DSTADDR register is replaced by the following:

#### Bits 31:0 - DSTADDR[31:0] Transfer Destination Address

This bit field holds the block transfer destination address.

When destination address incrementation is disabled (BTCTRL.DSTINC=0), DSTADDR corresponds to the last beat transfer address in the block transfer.

When destination address incrementation is enabled (BTCTRL.DSTINC=1), DSTADDR is calculated as follows: If BTCTRL.STEPSEL=1:

$DSTADDR = DSTADDR_{START} + BTCNT \bullet (BEATSIZE + 1)$

If BTCTRL.STEPSEL=0:

$DSTADDR = DSTADDR_{START} + BTCNT \cdot (BEATSIZE + 1) \cdot 2^{STEPSIZE}$

- DSTADDR<sub>START</sub> is the destination address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

- · BEATSIZE is the configured number of bytes in a beat

- · STEPSIZE is the configured number of beats for each incrementation

## 17. Module: RTC and TC READREQ.RCONT bit fields

A note is added to the RTC and TC READREQ.RCONT bit fields descriptions:

For the RTC:

Note:

Once the continuous synchronization is enabled, the first write in the COUNT/CLOCK register will be stalled for a maximum of 6 APB + 6 RTC clock cycles (the time for the on-going read synchronization to complete).

For the TC:

Note:

Once the continuous synchronization is enabled, the first write in the COUNT/CCx register will be stalled for a maximum of 6

APB + 6 TC clock cycles (the time for the on-going read synchronization to complete).

# 18. Module: DMAC BASEADDR, WRBADDR and DESCADDR registers alignment

The description for the three DMAC BASEADDR, WRBADDR and DESCADDR registers erroneously states that these registers must be 128-bit aligned. These registers must be **64-bit aligned**.

## 19. Module: DAC Maximum Input Clock Frequency

The Electrical Characteristics table 34-6 erroneously defines the DAC maximum input clock as 350 kHz. This value is corrected to 48 MHz.

#### 20. Module: DAC Start Conversion Event

A note has been added to the start conversion paragraph in chapter 32.6.4.3:

Note: When a DAC Start Conversion event is enabled, only DATABUF must be written (not DATA).

The description of the EVTCTRL.STARTEI bit has been updated to:

- 0: A new conversion will not be triggered on an incoming event. Only DATA must be written (not DATABUF).

- 1: A new conversion will be triggered on an incoming event. Only DATABUF must be written (not DATA).

#### 21. Module: DAC Electrical Characteristics

The conversion rate of 350 ksps mentioned in Note 1 for the DAC Accuracy Characteristics tables 34-26 and 39-24 is incorrect. All values have been measured using a conversion rate of 35 ksps.

## 22. Module: ADC Electrical Characteristics at 85°C

The table 34-19 Operating Conditions is corrected in **BOLD** as follows:

| Symbol                      | Parameter                                                  | Conditions                                        | Min.                    | Тур.                     | Max.                    | Units  |

|-----------------------------|------------------------------------------------------------|---------------------------------------------------|-------------------------|--------------------------|-------------------------|--------|

| RES                         | Resolution                                                 | -                                                 | 8                       | -                        | 12                      | bits   |

| F <sub>CLK_ADC</sub>        | ADC Clock frequency                                        | -                                                 | 30                      | -                        | 2100                    | kHz    |

|                             | (1)                                                        | Single shot                                       | 5                       | -                        | 300                     |        |

|                             | Sample rate <sup>(1)</sup>                                 | Free running                                      | 5                       | -                        | 350 <sup>(3)</sup>      | ksps   |

|                             | Sampling time <sup>(1)</sup>                               | -                                                 | 250                     | -                        | -                       | ns     |

|                             | Sampling time with DAC as input <sup>(2)</sup>             | -                                                 | 3                       | -                        | -                       | μs     |

|                             | Sampling time with<br>Temp<br>sens as input <sup>(2)</sup> | -                                                 | 10                      | -                        | -                       | μs     |

|                             | Sampling time with<br>Bandgap<br>as input <sup>(2)</sup>   | -                                                 | 10                      | -                        | -                       | μs     |

|                             | Conversion time <sup>(1)</sup>                             | 1x Gain                                           | 6                       | -                        | -                       | cycles |

| V <sub>REF</sub>            | Voltage reference range                                    | -                                                 | 1.0                     | -                        | V <sub>DDANA</sub> -0.6 | V      |

| INT1V                       | Internal 1V reference (2,                                  | -                                                 | -                       | 1.0                      | -                       | V      |

| INTVCC0                     | Internal ratiometric reference 0 <sup>(2)</sup>            | -                                                 | -                       | V <sub>DDANA</sub> /1.48 | -                       | V      |

| INTVCC0<br>Voltage<br>Error | Internal ratiometric reference 0 <sup>(2)</sup> error      | 2.0V <v<sub>DDANA&lt;3.063<br/>V</v<sub>          | -1                      | -                        | 1                       | %      |

| INTVCC1                     | Internal ratiometric reference 1 <sup>(2)</sup>            | V <sub>DDANA</sub> >2.0V                          | -                       | V <sub>DDANA</sub> /2    | -                       | V      |

| INTVCC1<br>Voltage<br>Error | Internal ratiometric reference 1 <sup>(2)</sup> error      | 2.0V <v<sub>DDANA&lt;3.063<br/>V</v<sub>          | -1                      | -                        | 1                       | %      |

|                             | Conversion range <sup>(1)</sup>                            | Differential mode                                 | -V <sub>REF</sub> /GAIN | -                        | +V <sub>REF</sub> /GAIN | V      |

|                             | Conversion range.                                          | Single-ended mode                                 | 0.0                     | -                        | +V <sub>REF</sub> /GAIN | V      |

| C <sub>SAMPLE</sub>         | Sampling capaci-<br>tance <sup>(2)</sup>                   | -                                                 | -                       | 3.5                      | -                       | pF     |

| R <sub>SAMPLE</sub>         | Input channel source resistance <sup>(2)</sup>             | -                                                 | -                       | -                        | 3.5                     | kΩ     |

| I <sub>DD</sub>             | DC supply current <sup>(1)</sup>                           | f <sub>CLK_ADC</sub> = 2.1<br>MHzI <sup>(3)</sup> | -                       | 3.8                      | 4.5                     | mA     |

**Note 1:** These values are based on characterization. These values are not covered by test limits in production.

4: It is the buffered internal reference of 1.0V derived from the internal 1.1V bandgap reference.

<sup>2:</sup> These values are based on simulation. These values are not covered by test limits in production or characterization.

<sup>3:</sup> In this condition and for a sample rate of 350 ksps, a conversion takes 6 clock cycles of the ADC clock (conditions: 1X gain, 12-bit resolution, differential mode, free-running).

Table 34-20 Differential Mode is corrected in **BOLD** as follows:

| Symbol | Parameter                      | Conditions                                          | Min.    | Тур.   | Max.    | Units |

|--------|--------------------------------|-----------------------------------------------------|---------|--------|---------|-------|

| ENOB   | Effective Number Of Bits       | With gain compensation                              | -       | 10.5   | 10.7    | bits  |

| TUE    | Total Unadjusted Error         | 1x Gain                                             | 3.1     | 4.3    | 20      | LSB   |

| INLI   | Integral Non Linearity         | 1x Gain                                             | 1.0     | 1.3    | 6.3     | LSB   |

| DNL    | Differential Non Linearity     | 1x Gain                                             | +/-0.3  | +/-0.5 | +/-0.98 | LSB   |

|        |                                | Ext. Ref 1x                                         | -25.0   | 2.5    | +25.0   | mV    |

|        | Gain Error                     | $V_{REF} = V_{DDANA}/1.48$                          | -30.0   | -1.5   | +30.0   | mV    |

| GE     |                                | VREF = INT1V                                        | -15.0   | -5.0   | +10.0   | mV    |

|        | Gain Accuracy <sup>(4)</sup>   | Ext. Ref. 0.5x                                      | +/-0.04 | +/-0.2 | +/-1.5  | %     |

|        | Gain Accuracy.                 | Ext. Ref. 2x to 16x                                 | +/-0.1  | +/-0.4 | +/-2.0  | %     |

|        |                                | Ext. Ref. 1x                                        | -10.0   | -1.5   | +10.0   | mV    |

| OE     | Offset Error                   | $V_{REF} = V_{DDANA}/1.48$                          | -10.0   | 0.5    | +10.0   | mV    |

|        |                                | VREF = INT1V                                        | -10.0   | 3.0    | +10.0   | mV    |

| SFDR   | Spurious Free Dynamic Range    |                                                     | 62.7    | 70.4   | 75.8    | dB    |

| SINAD  | Signal-to-Noise and Distortion | 1x Gain<br>F <sub>CLK ADC</sub> = 2.1MHz            | 54.1    | 61.4   | 62.7    | dB    |

| SNR    | Signal-to-Noise Ratio          | F <sub>IN</sub> = 40kHz<br>A <sub>IN</sub> = 95%FSR | 54.5    | 63.6   | 65.6    | dB    |

| THD    | Total Harmonic Distortion      | 7IN - 99/01 GIV                                     | -74     | -70.2  | -63     | dB    |

|        | Noise RMS                      | T = 25°C                                            | 0.6     | 1.0    | 2       | mV    |

- **Note 1:** Maximum numbers are based on characterization and not tested in production, and valid for 5% to 95% of the input voltage range.

- 2: Dynamic parameter numbers are based on characterization and not tested in production.

- **3:** Respect the input common mode voltage through the following equations (where VCM\_IN is the Input channel common mode voltage):

- If  $|V_{IN}| > V_{REF}/4$

- $-V_{CM\_IN} < 0.95*V_{DDANA} + V_{REF}/4 0.75V$

- $-V_{CM\_IN} > V_{REF}/4 0.05*V_{DDANA} 0.1V$

- If  $|V_{IN}| < V_{REF}/4$

- $-V_{CM_IN} < 1.2*V_{DDANA} 0.75V$

- $-V_{CM\ IN} > 0.2*V_{DDANA} 0.1V$

- 4: The gain accuracy represents the gain error expressed in percent. Gain accuracy (%) = (Gain Error in V x 100) / (2\*Vref/GAIN)

## 23. Module: Bandgap Electrical Characteristics at 85°C

The "Bandgap Reference Characteristics" chapter and its table 34-28 "Internal 1.1V Bandgap Reference Characteristics" are both renamed to "Bandgap and Internal 1.0V Reference Characteristics".

Table 34-28 is updated as follows with corrections in **BOLD**:

| Symbol  | Parameter                                                                               | Conditions                      | Min. | Тур. | Max. | Units |  |  |

|---------|-----------------------------------------------------------------------------------------|---------------------------------|------|------|------|-------|--|--|

| Bandson | Internal 1.1V Bandgap                                                                   | Over voltage and [-40°C, +85°C] | 1.08 | 1.10 | 1.12 |       |  |  |

| Bandgap | reference                                                                               | Over voltage at 25°C            | 1.07 | 1.10 | 1.11 | .,    |  |  |

| INITAN  | Internal 1.0V reference                                                                 | Over voltage and [-40°C, +85°C] | 0.98 | 1.00 | 1.02 | _ V   |  |  |

| INT1V   | voltage <sup>(1)</sup>                                                                  | Over voltage at 25°C            | 0.97 | 1.00 | 1.01 |       |  |  |

| Note 1: | ote 1: These values are simulation based and are not covered by production test limits. |                                 |      |      |      |       |  |  |

## 24. Module: ADC Electrical Characteristics at 105°C

Table 39-17 Operating Conditions is corrected in **BOLD** as follows:

| Symbol                  | Parameter                                             | Conditions                                     | Min.                    | Тур.                     | Max.                    | Units  |

|-------------------------|-------------------------------------------------------|------------------------------------------------|-------------------------|--------------------------|-------------------------|--------|

| RES                     | Resolution                                            | -                                              | 8                       | -                        | 12                      | bits   |

| F <sub>CLK_ADC</sub>    | ADC Clock frequency                                   | -                                              | 30                      | -                        | 2100                    | kHz    |

|                         | Sample rate <sup>(1)</sup>                            | Single shot                                    | 5                       | -                        | 300                     |        |

|                         | Sample rate(*)                                        | Free running                                   | 5                       | -                        | 350 <sup>(3)</sup>      | ksps   |

|                         | Sampling time <sup>(1)</sup>                          | -                                              | 250                     | -                        | -                       | ns     |

|                         | Sampling time with DAC as input(2)                    | -                                              | 3                       | -                        | -                       | μs     |

|                         | Sampling time with Temp sens as input(2)              | -                                              | 10                      | -                        | -                       | μs     |

|                         | Sampling time with<br>Bandgap<br>as input(2)          | -                                              | 10                      | -                        | -                       | μs     |

|                         | Conversion time <sup>(1)</sup>                        | 1x Gain                                        | 6                       | -                        | -                       | cycles |

| <sup>V</sup> DDANA      | Power supply voltage                                  | T > 85°C                                       | 2.7                     |                          | 3.6                     | V      |

| <sup>∨</sup> REF        | Voltage reference range                               | -                                              | 1.0                     | -                        | V <sub>DDANA</sub> -0.6 | V      |

| INT1V                   | Internal 1V reference (2, 4)                          | -                                              | -                       | 1.0                      | -                       | V      |

| INTVCC0                 | Internal ratiometric reference 0 <sup>(2)</sup>       | -                                              | -                       | V <sub>DDANA</sub> /1.48 | -                       | V      |

| INTVCC0<br>oltage Error | Internal ratiometric reference 0 <sup>(2)</sup> error | 2.0V <v<sub>DDANA&lt;3.063V</v<sub>            | -1                      | -                        | 1                       | %      |

| INTVCC1                 | Internal ratiometric reference 1 <sup>(2)</sup>       | V <sub>DDANA</sub> >2.0V                       | -                       | V <sub>DDANA</sub> /2    | -                       | V      |

| INTVCC1<br>oltage Error | Internal ratiometric reference 1 <sup>(2)</sup> error | 2.0V <v<sub>DDANA&lt;3.063V</v<sub>            | -1                      | -                        | 1                       | %      |

|                         | Conversion range <sup>(1)</sup>                       | Differential mode                              | -V <sub>REF</sub> /GAIN | -                        | +V <sub>REF</sub> /GAIN | V      |

|                         | Conversion range.                                     | Single-ended mode                              | 0.0                     | -                        | +V <sub>REF</sub> /GAIN | V      |

| C <sub>SAMPLE</sub>     | Sampling capacitance <sup>(2)</sup>                   | -                                              | -                       | 3.5                      | -                       | pF     |

| R <sub>SAMPLE</sub>     | Input channel source resis-<br>tance <sup>(2)</sup>   | -                                              | -                       | -                        | 3.5                     | kΩ     |

| I <sub>DD</sub>         | DC supply current <sup>(1)</sup>                      | f <sub>CLK_ADC</sub> = 2.1 MHzI <sup>(3)</sup> | -                       | 3.8                      | 4.5                     | mA     |

- **Note 1:** These values are based on characterization. These values are not covered by test limits in production.

- 2: These values are based on simulation. These values are not covered by test limits in production or characterization.

- 3: In this condition and for a sample rate of 350ksps, a conversion takes 6 clock cycles of the ADC clock (conditions: 1X gain, 12-bit resolution, differential mode, free-running).

- 4: It is the buffered internal reference of 1.0V derived from the internal 1.1V bandgap reference.

Table 39-18 Differential Mode is corrected in **BOLD** as follows:

| Symbol | Parameter                      | Conditions                                           | Min.    | Тур.   | Max.    | Units |

|--------|--------------------------------|------------------------------------------------------|---------|--------|---------|-------|

| ENOB   | Effective Number Of Bits       | With gain compensation                               | -       | 10.0   | 10.4    | bits  |

| TUE    | Total Unadjusted Error         | 1x Gain                                              | 3.1     | 4.3    | 16      | LSB   |

| INLI   | Integral Non Linearity         | 1x Gain                                              | 1.0     | 1.3    | 5.0     | LSB   |

| DNL    | Differential Non Linearity     | 1x Gain                                              | +/-0.3  | +/-0.5 | +/-0.98 | LSB   |

|        |                                | Ext. Ref 1x                                          | -25.0   | 2.5    | +25.0   | mV    |

|        | Gain Error                     | V <sub>REF</sub> = V <sub>DDANA</sub> /1.48          | -30.0   | -1.5   | +30.0   | mV    |

| GE     |                                | VREF = INT1V                                         | -15.0   | -5.0   | +10.0   | mV    |

|        | Gain Accuracy <sup>(4)</sup>   | Ext. Ref. 0.5x                                       | +/-0.04 | +/-0.2 | +/-1.0  | %     |

|        | Gain Accuracy                  | Ext. Ref. 2x to 16x                                  | +/-0.1  | +/-0.4 | +/-1.5  | %     |

|        |                                | Ext. Ref. 1x                                         | -10.0   | -1.5   | +10.0   | mV    |

| OE     | Offset Error                   | V <sub>REF</sub> = V <sub>DDANA</sub> /1.48          | -10.0   | 0.5    | +10.0   | mV    |

|        |                                | VREF = INT1V                                         | -10.0   | 3.0    | +10.0   | mV    |

| SFDR   | Spurious Free Dynamic Range    |                                                      | 63.0    | 70.4   | 74.8    | dB    |

| SINAD  | Signal-to-Noise and Distortion | 1x Gain<br>F <sub>CLK ADC</sub> = 2.1 MHz            | 57.0    | 61.4   | 64.3    | dB    |

| SNR    | Signal-to-Noise Ratio          | F <sub>IN</sub> = 40 kHz<br>A <sub>IN</sub> = 95%FSR | 57.9    | 63.6   | 65.5    | dB    |

| THD    | Total Harmonic Distortion      | AIN - 93 /0F3K                                       | -74.5   | -70.2  | -64.5   | dB    |

|        | Noise RMS                      | T = 25°C                                             | 0.6     | 1.0    | 2       | mV    |

- **Note 1:** Maximum numbers are based on characterization and not tested in production, and valid for 5% to 95% of the input voltage range.

- **2:** Dynamic parameter numbers are based on characterization and not tested in production.

- 3: Respect the input common mode voltage through the following equations (where VCM\_IN is the Input channel common mode voltage):

- If  $|V_{IN}| > V_{REF}/4$

- $-V_{CM_IN} < 0.95*V_{DDANA} + V_{REF}/4 0.75V$

- $-V_{CM\ IN} > V_{REF}/4 0.05*V_{DDANA} 0.1V$

- If |V<sub>IN</sub>| < V<sub>REF</sub>/4

- $-V_{CM\ IN} < 1.2*V_{DDANA} 0.75V$

- $-V_{CM\ IN} > 0.2*V_{DDANA} 0.1V$

- **4:** The ADC channels on pins PA08, PA09, PA10, PA11 are powered from the VDDIO power supply. The ADC performance of these pins will not be the same as all the other ADC channels on pins powered from the VDDANA power supply.

- 5: The gain accuracy represents the gain error expressed in percent. Gain accuracy (%) = (Gain Error in  $\forall x 100$ ) / (2\*Vref/GAIN).

## 25. Module: Bandgap Electrical Characteristics at 105°C

The "Bandgap Reference Characteristics" chapter and its table 39-26 "Internal 1.1V Bandgap Reference Characteristics" are renamed to "Bandgap and Internal 1.0V Reference Characteristics". The table 39-26 is updated as follows with corrections in BOLD:

| Symbol  | Parameter                                                                               | Conditions                       | Min. | Тур. | Max. | Units |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------|----------------------------------|------|------|------|-------|--|--|--|--|

| Bandgap | Internal 1.1V Bandgap reference                                                         | Over voltage and [-40°C, +105°C] | 1.08 | 1.10 | 1.12 | V     |  |  |  |  |

| Бапидар | internal 1.17 bandgap reference                                                         | Over voltage at 25°C             | 1.07 | 1.10 | 1.11 |       |  |  |  |  |

| INT1V   | Internal 1.0V reference voltage (1)                                                     | Over voltage and [-40°C, +85°C]  | 0.98 | 1.00 | 1.02 |       |  |  |  |  |

| INTTV   | internal 1.0v reference voltage (1)                                                     | Over voltage at 25°C             | 0.97 | 1.00 | 1.01 |       |  |  |  |  |

| Note 1: | John 1: These values are simulation based and are not covered by production test limits |                                  |      |      |      |       |  |  |  |  |

#### APPENDIX A: REVISION HISTORY

Revision A Document (07/2019)

This is the initial released version of this document.

#### Revision B Document (03/2021)

This revision includes numerous typographical updates, along with the following new information:

The I<sup>2</sup>C standard uses the terminology "master" and "slave". The equivalent Microchip terminology used in this document is "Host" and "Client" respectively.

The following Errata were added:

- 2. Module: "SERCOM I<sup>2</sup>C STATUS.CLKHOLD bit"

- 3. Module: "Device Standby Wakeup"

Updated the following Data Sheet Clarifications with new images and descriptions:

- 2. Module: "OSC32K and XOSC32K EN1K bit"

- 4. Module: "Brown-Out Detectors (BOD) Characteristics"

- 5. Module: "ADC Power Management"

- 9. Module: "NVMCTRL NVM User Configuration"

The following Data Sheet Clarifications were added:

- 14. Module: "SERCOM I2C INTFLAG.DRDY bit"

- 15. Module: "NVMCTRL AUX1 Device Configuration Register"

- 16. Module: "DMAC SRCADDR and DSTADDR Registers' Descriptions"

- 17. Module: "RTC and TC READREQ.RCONT bit fields"

- 18. Module: "DMAC BASEADDR, WRBADDR and DESCADDR registers alignment"

- 19. Module: "DAC Maximum Input Clock Frequency"

- 20. Module: "DAC Start Conversion Event"

- 21. Module: "DAC Electrical Characteristics"

- 22. Module: "ADC Electrical Characteristics at 85°C"

- 23. Module: "Bandgap Electrical Characteristics at 85°C"

- 24. Module: "ADC Electrical Characteristics at 105°C"

- 25. Module: "Bandgap Electrical Characteristics at 105°C"

The following Data Sheet Clarifications were removed:

Module: 32 kHz Ultra-Low Power Internal Oscillator (OSCULP32K) Operation

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKiT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive,  $Crypto Companion, \ Crypto Controller, \ ds PICDEM, \ ds PICDEM.net,$ Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019-2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-7916-1

### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

**Atlanta** Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan

Tel: 86-27-5980-5300 China - Xian

Tel: 86-29-8833-7252 China - Xiamen

Tel: 86-592-2388138 **China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820