## Product Change Notification / SYST-26JLSD716

Date:

29-Mar-2021

**Product Category:**

8-bit Microcontrollers

**PCN Type:**

**Document Change**

## **Notification Subject:**

ERRATA - PIC18F65/66K40 Family Silicon Errata and Data Sheet Clarification

## **Affected CPNs:**

SYST-26JLSD716\_Affected\_CPN\_03292021.pdf SYST-26JLSD716\_Affected\_CPN\_03292021.csv

#### **Notification Text:**

SYST-26JLSD716

Microchip has released a new Product Documents for the PIC18F65/66K40 Family Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at PIC18F65/66K40 Family Silicon Errata and Data Sheet Clarification.

**Notification Status: Final**

#### **Description of Change:**

This revision includes the following updates to Data Sheet Clarifications:

- 1) Added silicon revisions 2.1.5, 2.1.6, 2.5.2, 2.6.3 2.8.1 and 2.9.1.

- 2) Data Sheet Clarifications Added Module 3.2 (Pin Diagrams), Module 3.3 (Electrical Specifications), Module 3.4 (Analogto-Digital Converter) and Module 3.5 (Capture/Compare/PWM (CCP) Module).

Impacts to Data Sheet: None

**Reason for Change:** To Improve Productivity

**Change Implementation Status:** Complete

Date Document Changes Effective: 29 Mar 2021

|                  | indvised that this is a change to the document only the product has not been changed.                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Attachment       |                                                                                                                                                                                                                             |

| PIC18F65/66K     | (40 Family Silicon Errata and Data Sheet Clarification                                                                                                                                                                      |

|                  |                                                                                                                                                                                                                             |

| Please contact y | your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                   |

| Terms and Con    | ditions:                                                                                                                                                                                                                    |

| home page sele   | eceive Microchip PCNs via email please register for our PCN email service at our PCN ect register then fill in the required fields. You will find instructions about registering for lemail service in the PCN FAQ section. |

| =                | nange your PCN profile, including opt out, please go to the PCN home page select login our myMicrochip account. Select a profile option from the left navigation bar and make selections.                                   |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                             |

#### Affected Catalog Part Numbers (CPN)

PIC18F65K40-E/MR

PIC18F65K40-E/PT

PIC18F65K40-I/MR

PIC18F65K40-I/PT

PIC18F65K40T-E/PT

PIC18F65K40T-I/MR

PIC18F65K40T-I/PT

PIC18F66K40-E/MR

PIC18F66K40-E/PT

PIC18F66K40-E/PTVAO

PIC18F66K40-I/MR

PIC18F66K40-I/PT

PIC18F66K40T-E/PT

PIC18F66K40T-E/PTVAO

PIC18F66K40T-I/MR

PIC18F66K40T-I/PT

PIC18LF65K40-E/MR

PIC18LF65K40-E/PT

PIC18LF65K40-I/MR

PIC18LF65K40-I/PT

PIC18LF65K40T-I/MR

PIC18LF65K40T-I/PT

PIC18LF66K40-E/MR

PIC18LF66K40-E/PT

PIC18LF66K40-I/MR

PIC18LF66K40-I/PT

PIC18LF66K40T-I/MR

PIC18LF66K40T-I/PT

Date: Monday, March 29, 2021

# PIC18(L)F65/66K40

# PIC18(L)F65/66K40 Family Silicon Errata and Data Sheet Clarification

The PIC18(L)F65/66K40 devices that you have received conform functionally to the current device data sheet (DS40001842D), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in the table below.

The errata described in this document will be addressed in future revisions of the PIC18(L)F65/66K40 silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current.

**Table 1. Silicon Device Identification**

| Part Number  | Device ID | Revision ID |        |

|--------------|-----------|-------------|--------|

|              |           | A3          | A4     |

| PIC18F65K40  | 0x6B00    | 0xA003      | 0xA004 |

| PIC18LF65K40 | 0x6B60    | 0xA003      | 0xA004 |

| PIC18F66K40  | 0x6AE0    | 0xA003      | 0xA004 |

| PIC18LF66K40 | 0x6B40    | 0xA003      | 0xA004 |

## 1. Silicon Issue Summary

Table 1-1. Silicon Issue Summary

| Module                               | Feature                                       | Item No.     | Issue Summary                                                                                                   | Affected<br>Revisions |    |

|--------------------------------------|-----------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|----|

|                                      |                                               |              |                                                                                                                 | А3                    | A4 |

| Analog-to-Digital<br>Converter (ADC) | ADC Conversion                                | 2.1.1        | Delay of one instruction cycle required prior to setting the ADGO bit when using ADCRC as the ADCC clock source | Х                     |    |

| Analog-to-Digital<br>Converter (ADC) | Computation<br>Overflow Bit                   | 2.1.2        | The Computation Overflow bit may be erroneously set by the ADFLTR                                               | X                     |    |

| Analog-to-Digital<br>Converter (ADC) | ADCRC Oscillator<br>Operation in<br>Sleep     | 2.1.3        | The ADCRC oscillator does not stop after conversion is complete in Sleep mode                                   | Х                     | Х  |

| Analog-to-Digital<br>Converter (ADC) | ADC Conversion with FVR                       | 2.1.4        | Using FVR as the ADC positive voltage reference can cause missing codes                                         | Х                     | Х  |

| Analog-to-Digital<br>Converter (ADC) | ADC conversion with F <sub>OSC</sub> as clock | 2.1.5        | The ADGO bit remains set when using F <sub>OSC</sub> as clock source with clock divider                         | Х                     | X  |

| Analog-to-Digital<br>Converter (ADC) | ADC operation in Burst Average mode           | 2.1.6        | The ADCNT register does not increment past '0b1' in Burst Average mode with double sampling enabled             | Х                     | X  |

| PIC18 Debug<br>Executive             | Data Write Match<br>Breakpoints               | 2.2.1        | Data write match breakpoints do not work when used on a location GSR space                                      | Х                     |    |

| PIC18 Core                           | TBLRD                                         | 2.3.1        | TBLRD requires NVMREG value to point to appropriate memory                                                      | X                     |    |

| Program Flash<br>Memory (PFM)        | Endurance of PFM Cell                         | 2.4.1        | Endurance of the PFM cell is lower than specified                                                               | X                     | Х  |

| MSSP                                 | SMBus 2.0<br>Voltage Level                    | 2.5.1        | Input low-voltage threshold level is dependent on $V_{\rm DD}$                                                  | X                     | Х  |

| MSSP                                 | SPI                                           | 2.5.2        | SSPBUF may become corrupted                                                                                     | X                     | Х  |

| Electrical<br>Specifications         | Min V <sub>DD</sub><br>Specification          | 2.6.1        | V <sub>DDMIN</sub> specifications are changed for LF devices only for -40°C and 0°C                             |                       | Х  |

| Electrical<br>Specifications         | FVR Specification                             | 2.6.2        | FVR specifications require use above -20°C                                                                      | Х                     | Х  |

| Electrical<br>Specifications         | Analog-to-Digital<br>Converter                | 2.6.3        | ADC offset error specification is +/-3.0 LSb                                                                    | X                     | X  |

| Timer0                               | Clock Source                                  | 2.7.1        | Operation of Timer0 is incorrect when F <sub>OSC</sub> /4 is used as the clock source                           | Х                     | Х  |

| Windowed<br>Watchdog Timer           | WWDT operation in Doze mode                   | 2.8.1        | Erroneous window violation error occurs in Doze mode                                                            | X                     | Х  |

| NVM                                  | NVMERR bit operation                          | 2.9.1        | NVMERR bit is set incorrectly due to specific Reset events                                                      | Х                     | Х  |

| Note: Only those is                  | ssues indicated in th                         | e last colui | mn apply to the current silicon revision.                                                                       |                       |    |

#### 2. Silicon Errata Issues

**Notice:** This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the bold font in the following tables apply to the current silicon revision.

## 2.1 Module: ADCC - Analog-to-Digital Converter with Computation

#### 2.1.1 ADC Conversion

When using the ADCRC as the clock source for ADCC, there is a delay of one instruction cycle between the user setting the ADGO bit and being able to read it set. This can lead to a false conversion complete scenario (i.e., ADGO being cleared), depending if the user code has a bit clear test BTFSC instruction on the ADGO bit, immediately after setting the ADGO bit. See code example below.

```

BSF ADCONO, ADGO ; Start conversion

BTSFC ADCONO, ADGO ; Is conversion done?

GOTO $-1 ; No, test again

```

#### Work around

Add a NOP instruction after setting the ADGO bit and before testing the bit for completion of conversion. See code example below.

```

BSF ADCONO, ADGO ; Start conversion

NOP

BTSFC ADCONO, ADGO ; Is conversion done?

GOTO $-1 ; No, test again

```

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

| X  |            |  |  |  |

#### 2.1.2 Computation Overflow Bit

If the sign bit of ADFLTR (bit 7 of ADFLTRH) is set, the Computation Overflow bit will also be set, even though this is not a legitimate case of an overflow event.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  |    |  |  |  |

#### 2.1.3 ADCRC Oscillator Operation in Sleep

If the part is in Sleep and the ADCRC oscillator is used as clock source to the ADC, the oscillator continues to run after the conversion is complete. This will increase the current consumption in Sleep mode. The oscillator will stop after the device exits Sleep mode and resumes normal code execution.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

#### 2.1.4 Missing Codes with FVR Reference

Using the FVR as the positive voltage reference for the ADC can cause an increase in missing codes.

#### Work around

#### Method 1:

Increase the bit conversion time, known as T<sub>AD</sub>, to 8 µs or higher.

#### Method 2:

Use  $V_{DD}$  as the positive voltage reference to the ADC.

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

| X  | X          |  |  |  |

#### 2.1.5 ADC GO Bit May Remain Set When the Clock Source is Fosc

When using  $F_{OSC}$  as the clock source (ADCON0.CS = 0) and any clock divider setting other than  $F_{OSC}/2$  is selected, the ADGO bit remains set and the conversion does not complete.

#### Work around

#### Method 1:

When using  $F_{OSC}$  as the clock source (ADCON0.CS = 0), clear the ADCLK register value to zero (ADCLK.CS = 0) and ensure that the  $F_{OSC}$  frequency does not violate any timing requirements for the ADC.

#### Method 2:

Use ADCRC as the clock source (ADCON0.CS = 1).

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

| X  | X          |  |  |  |

#### 2.1.6 ADCC Burst Average Mode

When the ADCC is operated in Burst Average mode (ADMD = 0b011 in the ADCON2 register) while enabling noncontinuous operation and double-sampling (ADCONT = 0 in the ADCON0 register and ADDSEN = 1 in the ADCON1 register), the value in the ADCNT register does not increment beyond '0b1' toward the value in the ADRPT register.

#### Work around

When operating the ADCC in Burst Average mode with double-sampling, enable continuous operation of the module (ADCONT = 1 in the ADCON0 register) and set the Stop-on-Interrupt bit (the ADSOI bit in the ADCON3 register). After the interrupt occurs, perform appropriate threshold calculations in the software and retrigger ADCC as necessary.

Alternatively, if the CPU is in Low-Power Sleep mode, the ADCC in noncontinuous Burst Average mode can be operated with a single ADC conversion (ADDSEN = 0 in the ADCON1 register). Doing so compromises noise immunity for lower power consumption by preventing the device from waking up to perform threshold calculations in the software.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | Х  |  |  |  |

## 2.2 Module: PIC18 Debug Executive

#### 2.2.1 Data Write Match Breakpoints

If the data in a GPR location is modified using any arithmetic instruction like INCF, ADDWF, SETF, CLRF, etc., the data write match breakpoint does not work. It works with MOVF, which moves the data into the same memory location. See code examples below.

1.

| MOVLB<br>CLRF<br>LOOP | 0x00<br>0x08 |                                                   |  |

|-----------------------|--------------|---------------------------------------------------|--|

| INCF                  | 0x08         | ;Doesn't break when data                          |  |

|                       |              | breakpoint set @ 0x08<br>with data match for 0xAA |  |

| GOTO LOOP             |              |                                                   |  |

2.

| MOVLB<br>MOVLW | 0x00<br>0xAA |                                         |  |

|----------------|--------------|-----------------------------------------|--|

| MOVF           | 0x08         | ;Breaks when data breakpoint set @ 0x08 |  |

|                |              | with data match for 0xAA                |  |

| GOTO LOOP      |              |                                         |  |

#### Work around

Use data write breakpoints without matching wherever possible.

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

| Х  |            |  |  |  |

#### 2.3 Module: PIC18 Core

#### 2.3.1 TBLRD Requires NVMREG Value to Point to Appropriate Memory

The affected silicon revisions of the PIC18(L)F65/66K40 devices improperly require the NVMREG[1:0] bits in the NVMCON register to be set for TBLRD access of the various memory regions. The issue is most apparent in compiled C programs when the user defines a const type and the compiler uses <code>TBLRD</code> instructions to retrieve the data from Program Flash Memory (PFM). The issue is also apparent when the user defines an array in RAM for which the compiler creates start-up code, executed before main(), that uses <code>TBLRD</code> instructions to initialize RAM from PFM.

#### Work around

Assembly code:

Set the NVMREG[1:0] bits to select the appropriate memory region before executing TBLRD instructions.

C code:

Create an assembly file named powerup.as and include this file with the other files in the project. This file will change the NVMREG[1:0] bits to point to program Flash before any code is executed. Contents of the powerup.as file:

```

#include <xc.inc>

GLOBAL    powerup, start

PSECT    powerup, class=CODE, delta=1, reloc=2

powerup:

BSF    NVMCON1, 7

GOTO    start

end

```

If there is a need to change the NVMREG[1:0] value to anything other than '10' and the Interrupt Service Routine uses constants or literal strings, then interrupts must be disabled before the change and restored to '10' before interrupts are enabled.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  |    |  |  |  |

## 2.4 Module: PFM - Program Flash Memory

#### 2.4.1 Endurance of PFM is Lower than Specified

The Flash memory cell endurance specification (Parameter MEM30) is 1K cycles.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

#### 2.5 Module: MSSP

#### 2.5.1 SMBus 2.0 Voltage Level

The input low-voltage threshold level (V<sub>IL</sub>) depends on V<sub>DD</sub>, as follows:

$$V_{IL}$$

= 0.7 for  $V_{DD}$  < 4V

$V_{IL}$  = 0.8 for  $V_{DD}$  > 4V

#### Work around

None.

#### **Affected Silicon Revisions**

| A3 A4 |

|-------|

|-------|

| X | X |  |  |  |

|---|---|--|--|--|

#### 2.5.2 MSSP SPI Client Mode

When operating in SPI Client mode, if the incoming SCK clock signal arrives during any of the conditions below, the SSPBUF Transmit Shift Register (TSR) may become corrupted. The byte transmitted to the client cannot be ensured to be correct, and the state of the WCOL bit may or may not indicate a write collision.

These conditions include:

- · A write to an SFR

- · A write to RAM following an SFR read

- · A write to RAM prior to an SFR read

#### Work around

#### Method 1 (Interrupt based using SS):

- 1. Connect the SS line to both the SS input and either an INT or IOC input pin.

- Enable INT or IOC interrupts (interrupt on falling edge if available, otherwise check that SS == 0 when the interrupt occurs).

- 3. Load SSPBUF with the data to be transmitted.

- 4. Continue program execution.

- 5. When the Interrupt Service Routine (ISR) is invoked, do either of the following:

- 5.1. Add a delay that ensures the first SCK clock will be complete, or

- 5.2. Poll SSPSTAT.BF (while(BF == 0)), and wait for the transmission/reception to complete.

#### Method 2 (Bit polling based using $\overline{SS}$ ):

- 1. Load SSPBUF with the data to be transmitted.

- 2. Poll the  $\overline{SS}$  line and wait for the  $\overline{SS}$  to go active (while(!PORTx. $\overline{SS}$  == 0)).

- 3. When  $\overline{SS}$  is active ( $\overline{SS} == 0$ ), do either of the following:

- 3.1. Add a delay that ensures the first SCK clock will be complete, or

- 3.2. Poll SSPSTAT.BF (while(BF == 0)), and wait for the transmission/reception to complete.

Once one of these two methods are complete, it is safe to return to program execution.

#### Method 3 (SS not available):

- 1. Load SSPBUF with the data to be transmitted.

- 2. Poll SSPSTAT.BF (while(BF == 0)), and wait for the transmission/reception to complete.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

## 2.6 Module: Electrical Specifications

#### 2.6.1 Min V<sub>DD</sub> Specification (LF Devies Only)

V<sub>DDMIN</sub> specifications are changed for LF devices only at -40°C and 0°C as below.

$V_{DDMIN}$  for -40°C to 0°C = 2.3V

$V_{DDMIN}$  for 0°C to 25°C = 2.1V

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

|    | X          |  |  |  |

## 2.6.2 FVR - Fixed Voltage Reference

At temperatures below -20°C, the output voltage for the FVR may be greater than the levels specified in the data sheet. This will apply to all three gain amplifier settings, (1X, 2X, 4X). The affected parameter numbers found in the data sheet are: FVR01 (1X gain setting), FVR02 (2X gain setting), and FVR03 (4X gain setting).

#### Work around

At temperatures above -20°C, the stated tolerances in the data sheet remain in effect. Operate the FVR only at temperatures above -20°C.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

### 2.6.3 ADC - Analog-to-Digital Converter

The table containing the Offset Error specification (AD04: EOFF) for the Analog-to-Digital Converter is modified. The updated value for Offset Error specification is +/- 3.0 LSb.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | <b>A</b> 4 |  |  |  |

|----|------------|--|--|--|

| X  | X          |  |  |  |

#### 2.7 Module: Timer0

#### 2.7.1 Clock Source

Clearing the T0ASYNC bit in the T0CON1 register when Timer0 is configured to use  $F_{OSC}/4$  may cause incorrect behavior. This issue is only valid when FOSC/4 is used as the clock source.

#### Work around

Set the T0ASYNC bit in the T0CON1 register when using F<sub>OSC</sub>/4 as the Timer0 clock.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

## 2.8 Module: Windowed Watchdog Timer (WWDT)

#### 2.8.1 Window Operation in Doze Mode

When the Windowed mode of operation is enabled in Doze mode, a window violation error is issued even though the window is open and has been armed. This condition occurs only when the window size is set to a value other than 100% open.

#### Work around

#### Method 1:

Use the Windowed mode of operation in any mode other than Doze. If disabling the Doze mode is not an option, use the WWDT module without the window being enabled.

#### Method 2:

If the device is in Doze mode, perform the arming process for the window in Normal mode and return to the Doze mode.

#### Method 3:

If there is an Interrupt Service Routine (ISR) in the application code, the arming within the window can be done inside the ISR with the ROI bit of the CPUDOZE register being set.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

## 2.9 Module: Nonvolatile Memory (NVM)

#### 2.9.1 **NVMERR**

When a Reset is issued while an NVM high-voltage operation is in progress, the NVMERR bit in the NVMCON0 register is set as expected. After clearing the NVMERR bit, if a Reset reoccurs, the NVMERR bit is set again regardless of whether an NVM operation is in progress or not. A successful write operation will clear the NVMERR condition.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| X  | Х  |  |  |  |

## 3. Data Sheet Clarifications

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS40001842D):

#### Note:

Corrections are shown in bold. Where possible, the original bold text formatting has been removed for clarity.

#### 3.1 Module: Core Features

#### 3.1.1 Operating Speed

The bullet point mentioning the operating speed on page 1 is incorrect. The correct text is shown below.

- · Operating Speed

- DC-64 MHz clock input

- 62.5 ns minimum instruction cycle

#### 3.2 Module: Pin Allocation Tables

#### 3.2.1 ADC Channel Selection

Table 1 on pg 8, incorrectly mentions that ANF0, ANF3 and ANF7 are possible ADC input channels. These are reserved connections and are not available as ADC inputs. The correct list of available ADC input channels can be found in "Section 33.1.2 Channel Selection" on pg. 627 and 628.

## 3.3 Module: Electrical Specifications

#### 3.3.1 ADC Offset Error

Table 38-13 containing the Offset Error Specification (AD04 :  $E_{OFF}$ ) for the Analog-to-Digital Converter is modified. The updated value for Offset Error Specification (AD04) is  $\pm 2.5$  LSb.

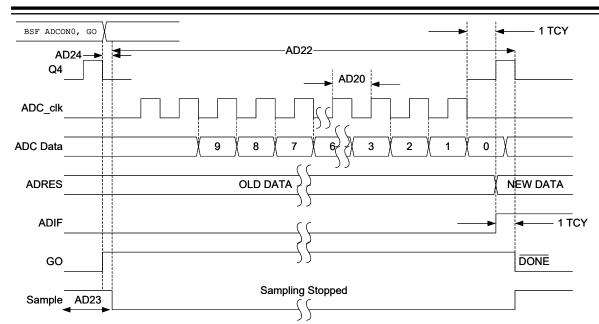

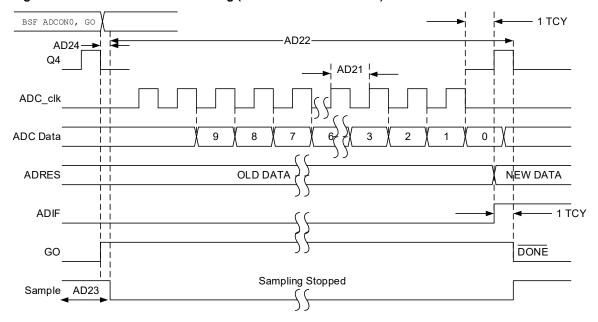

#### 3.3.2 ADC Conversion Timing Diagram

Refer to the images below for corrections of Figure 38-10 and Figure 38-11. Previously, the parameter numbers were incorrect.

Figure 38-10: ADC Conversion Timing (ADC Clock Fosc-Based)

Figure 38-11: ADC Conversion Timing (ADC Clock from ADCRC)

#### 3.3.3 Comparator Offset Error

Table 38-15 containing the Input Offset Voltage Error Specification (CM01 : V<sub>IOFF</sub>) for the Comparator is modified.

The updated value for Input Offset Voltage Specification (CM01) is ±60mV.

#### 3.3.4 I/O Ports - I<sup>2</sup>C Threshold Values

Table 38-4 containing the Input Low Voltage with  $I^2C$  levels specification (D303 :  $V_{IL}$ ) for the I/O ports is modified. Refer to the table below for the updated value.

| Param No. | Sym.                                  | Characteristic               | Min.              | Typ.† | Max.                 | Units | Conditions                    |  |  |  |

|-----------|---------------------------------------|------------------------------|-------------------|-------|----------------------|-------|-------------------------------|--|--|--|

|           |                                       |                              | Input Low Voltage |       |                      |       |                               |  |  |  |

| D303      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                              | I/O PORT:         |       |                      |       |                               |  |  |  |

|           | V <sub>IL</sub>                       | with I <sup>2</sup> C levels | _                 | _     | 0.3 V <sub>DD</sub>  | V     | $2.0V \le V_{DD} \le 5.5V$    |  |  |  |

|           |                                       | with i-C levels              | _                 | _     | 0.25 V <sub>DD</sub> | V     | 1.8V ≤ V <sub>DD</sub> < 2.0V |  |  |  |

## 3.4 Module: Analog-to-Digital Converter

#### 3.4.1 ADC Clock Period vs Device Frequency

The ADCLK value for  $F_{OSC}/16$  in Table 31-2 is incorrect. The correct value can be found in the table below.

|                        | ck Period<br><sub>AD</sub> ) | Device Frequency (F <sub>osc</sub> ) |                            |                       |                       |                        |                        |                            |  |

|------------------------|------------------------------|--------------------------------------|----------------------------|-----------------------|-----------------------|------------------------|------------------------|----------------------------|--|

| ADC<br>Clock<br>Source | ADCLK                        | 64 MHz                               | 32 MHz                     | 20 MHz                | 16 MHz                | 8 MHz                  | 4 MHz                  | 1 MHz                      |  |

| F <sub>OSC</sub> /2    | 000000                       | 31.25<br>ns <sup>(2)</sup>           | 62.5 ns <sup>(2)</sup>     | 100 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>  | 500 ns <sup>(2)</sup>  | 2.0 µs                     |  |

| F <sub>OSC</sub> /4    | 000001                       | 62.5 ns <sup>(2)</sup>               | 125 ns <sup>(2)</sup>      | 200 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup>  | 1.0 µs                 | 4.0 µs                     |  |

| F <sub>OSC</sub> /6    | 000010                       | 125 ns <sup>(2)</sup>                | 187.5<br>ns <sup>(2)</sup> | 300 ns <sup>(2)</sup> | 375 ns <sup>(2)</sup> | 750 ns <sup>(2)</sup>  | 1.5 µs                 | 6.0 µs                     |  |

| F <sub>OSC</sub> /8    | 000011                       | 187.5<br>ns <sup>(2)</sup>           | 250 ns <sup>(2)</sup>      | 400 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup> | 1.0 µs                 | 2.0 µs                 | 8.0 µs <sup>(3)</sup>      |  |

|                        |                              |                                      |                            |                       |                       |                        |                        |                            |  |

| F <sub>OSC</sub> /16   | 000111                       | 250 ns <sup>(2)</sup>                | 500 ns <sup>(2)</sup>      | 800 ns <sup>(2)</sup> | 1.0 µs                | 2.0 µs                 | 4.0 µs                 | 16.0 µs <sup>(3)</sup>     |  |

|                        |                              |                                      |                            |                       |                       |                        |                        |                            |  |

| F <sub>OSC</sub> /128  | 111111                       | 2.0 µs                               | 4.0 µs                     | 6.4 µs                | 8.0 µs                | 16.0 μs <sup>(3)</sup> | 32.0 µs <sup>(2)</sup> | 128.0<br>µs <sup>(2)</sup> |  |

| FRC                    | ADCS=1                       | 1.0-6.0<br>µs                        | 1.0-6.0<br>µs              | 1.0-6.0<br>µs         | 1.0-6.0<br>μs         | 1.0-6.0<br>µs          | 1.0-6.0<br>µs          | 1.0-6.0<br>µs              |  |

#### Note:

- 1. See T<sub>AD</sub> parameter in the "Electrical Specifications" section for FRC source typical T<sub>AD</sub> value.

- 2. These values violate the required T<sub>AD</sub> time.

- 3. Outside the recommended T<sub>AD</sub> time.

- 4. The ADC clock period (T<sub>AD</sub>) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock F<sub>OSC</sub>. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

# PIC18(L)F65/66K40

**Data Sheet Clarifications**

## 3.4.2 ADCRS Bits Description in the ADCON2 Register

The description for the ADCRS[2:0] bits in the ADCON2 register is incorrect. The correct description is mentioned below.

#### 3.4.2.1 ADCON2

Name: ADCON2

Bits 6:4 - ADCRS[2:0] ADC Accumulated Calculation Right Shift Select bits

| Value  | Condition             | Description                                                                             |

|--------|-----------------------|-----------------------------------------------------------------------------------------|

| 1 to 6 | ADMD = 'b100          | Low-pass filter time constant is 2 <sup>ADCRS</sup> , filter gain is 1:1 <sup>(2)</sup> |

| 1 to 6 | ADMD = 'b011 to 'b001 | The accumulated value is right-shifted by ADCRS (divided by 2 <sup>ADCRS</sup> )(1,2)   |

| X      | ADMD = 'b000          | These bits are ignored                                                                  |

## 3.4.3 ADC Precharge Time Control Register

Refer to the register below for the modified description of the ADPRE register.

#### 3.4.3.1 ADPRE

Name: ADPRE Offset: 0xF5E

ADC Precharge Time Control Register

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     | ,   |     | ADPR | E[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 7:0 - ADPRE[7:0] Precharge Time Select bits

#### Table 3-1.

| ADPRE | Precharge Time                |                              |  |  |  |

|-------|-------------------------------|------------------------------|--|--|--|

| ADFRE | ADCS != F <sub>RC</sub>       | ADCS = F <sub>RC</sub>       |  |  |  |

| 255   | 255 clock of F <sub>OSC</sub> | 255 clock of F <sub>RC</sub> |  |  |  |

| 254   | 254 clock of F <sub>OSC</sub> | 254 clock of F <sub>RC</sub> |  |  |  |

|       |                               |                              |  |  |  |

| 2     | 2 clock of F <sub>OSC</sub>   | 2 clock of F <sub>RC</sub>   |  |  |  |

| 1     | 1 clock of F <sub>OSC</sub>   | 1 clock of F <sub>RC</sub>   |  |  |  |

| 0     | Not included in the d         | ata conversion cycle         |  |  |  |

## 3.4.4 ADC Acquisition Time Control Register

Refer to the register below for the modified description of the ADACQ register.

#### 3.4.4.1 ADACQ

Name: ADACQ Offset: 0xF5C

ADC Acquisition Time Control Register

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | ADAC | Q[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 7:0 - ADACQ[7:0] Acquisition (charge share time) Select bits

#### Table 3-2.

| ADACQ | Acquisition Time                                         |                              |  |  |  |

|-------|----------------------------------------------------------|------------------------------|--|--|--|

| ADACQ | ADCS != F <sub>RC</sub>                                  | ADCS = F <sub>RC</sub>       |  |  |  |

| 255   | 255 clock of F <sub>OSC</sub>                            | 255 clock of F <sub>RC</sub> |  |  |  |

| 254   | 254 clock of F <sub>OSC</sub>                            | 254 clock of F <sub>RC</sub> |  |  |  |

|       |                                                          |                              |  |  |  |

| 2     | 2 clock of F <sub>OSC</sub>                              | 2 clock of F <sub>RC</sub>   |  |  |  |

| 1     | 1 clock of F <sub>OSC</sub>                              | 1 clock of F <sub>RC</sub>   |  |  |  |

| 0     | Not included in the data conversion cycle <sup>(1)</sup> |                              |  |  |  |

#### Note:

1. If ADPRE is not equal to '0', then ADACQ =  $0b0000\_0000$  means Acquisition Time is 256 clocks of  $F_{OSC}$  or  $F_{RC}$ .

## 3.5 Module: CCP - Capture/Compare/PWM Module

#### 3.5.1 Module Registers

The description for the CCPTMRS0 and CCPTMRS1 registers is missing in the data sheet. The description for this register is mentioned below.

Each CCP/PWM module has an independent timer selection that can be accessed using the CxTSEL or PxTSEL bits. The default timer selection is TMR1 when using Capture/Compare mode and TMR2 when using PWM mode in the CCPx module. The default timer selection for the PWM module is always TMR2.

#### 3.5.1.1 CCPTMRS1

Name: CCPTMRS1

CCP Timers Selection Register1

| Bit    | 7 | 6 | 5     | 4       | 3     | 2       | 1    | 0       |

|--------|---|---|-------|---------|-------|---------|------|---------|

|        |   |   | P7TSI | EL[1:0] | P6TSE | EL[1:0] | C5TS | EL[1:0] |

| Access |   |   | R/W   | R/W     | R/W   | R/W     | R/W  | R/W     |

| Reset  |   |   | 0     | 1       | 0     | 1       | 0    | 1       |

#### Bits 2:3, 4:5 - PnTSEL PWMn Timer Selection bits

| Value | Description          |

|-------|----------------------|

| 11    | PWMn based on Timer8 |

| 10    | PWMn based on Timer6 |

| 01    | PWMn based on Timer4 |

| 00    | PWMn based on Timer2 |

## Bits 0:1 - CnTSEL[1:0] CCPn Timer Selection bits

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 11    | CCPn is based off Timer7 in Capture/Compare mode and Timer8 in PWM mode |

| 10    | CCPn is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode |

| 01    | CCPn is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode |

| 00    | CCPn is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode |

#### 3.5.1.2 CCPTMRS0

Name: CCPTMRS0

CCP Timers Selection Register0

| Bit    | 7           | 6   | 5           | 4   | 3           | 2   | 1           | 0   |

|--------|-------------|-----|-------------|-----|-------------|-----|-------------|-----|

|        | C4TSEL[1:0] |     | C3TSEL[1:0] |     | C2TSEL[1:0] |     | C1TSEL[1:0] |     |

| Access | R/W         | R/W | R/W         | R/W | R/W         | R/W | R/W         | R/W |

| Reset  | 0           | 1   | 0           | 1   | 0           | 1   | 0           | 1   |

## Bits 0:1, 2:3, 4:5, 6:7 - CnTSEL CCPn Timer Selection bits

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 11    | CCPn is based off Timer7 in Capture/Compare mode and Timer8 in PWM mode |

| 10    | CCPn is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode |

| 01    | CCPn is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode |

| 00    | CCPn is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode |

# 4. Appendix A: Revision History

| Doc Rev. | Date    | Comments                                                                                                                                                                                                                                                            |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F        | 03/2021 | Added silicon revisions 2.1.5, 2.1.6, 2.5.2, 2.6.3 2.8.1 and 2.9.1. Data Sheet Clarifications: Added Module 3.2 (Pin Diagrams), Module 3.3 (Electrical Specifications), Module 3.4 (Analog-to-Digital Converter) and Module 3.5 (Capture/Compare/PWM (CCP) Module). |

| E        | 06/2018 | Data Sheet Clarifications: Added Module 2: Pin Allocation Tables (ADC Channel Selection).                                                                                                                                                                           |

| D        | 05/2018 | Added Module 7: Electrical Specifications (FVR) and Module 8: Timer0. Data Sheet Clarifications: Added Module 1 (Core Features).                                                                                                                                    |

| С        | 03/2017 | Added Module 6: Electrical Specifications for LF Devices Only. Other minor corrections.                                                                                                                                                                             |

| В        | 12/2016 | Added modules 1.3. ADCRC Oscillator Operation in Sleep, 1.4. ADC Conversion with FVR, and 5. MSSP to the Silicon Errata Issues section. Other minor corrections.                                                                                                    |

| Α        | 09/2016 | Initial release of this document.                                                                                                                                                                                                                                   |

## The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features

of the Microchip devices. We believe that these methods require using the Microchip products in a manner

outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code

protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

## **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5524-7839-3

| Quality         | / Manad    | rement  | <b>System</b> |

|-----------------|------------|---------|---------------|

| <b>Q</b> uality | , iviaiias | gonioni | Cystein       |

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|---------------------------|-----------------------|-------------------------|-----------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614         | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071         | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| Dallas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000         | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983         | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis              | China - Xiamen        |                         | Tel: 31-416-690399    |

| Noblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323         | China - Zhuhai        |                         | Norway - Trondheim    |

| Fax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| Tel: 317-536-2380         |                       |                         | Poland - Warsaw       |

| Los Angeles               |                       |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest   |

| Tel: 949-462-9523         |                       |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608         |                       |                         | Spain - Madrid        |

| Tel: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510         |                       |                         | Sweden - Gothenberg   |

| New York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000         |                       |                         | Sweden - Stockholm    |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110         |                       |                         | UK - Wokingham        |

| Tel: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980         |                       |                         |                       |

| Fax: 905-695-2078         |                       |                         |                       |