# MicroZed™ Zynq™ Evaluation and Development and System on Module Hardware User Guide

Version 1.6

# **Document Control**

**Document Version:** 1.6

**Document Date:** 01/22/2015

# **Prior Version History**

| Version | Date       | Comment                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 08/02/2013 | Initial MicroZed Hardware User Guide                                                                                                                                                                                                                                                                                                                                                         |

| 1.1     | 08/09/2013 | microSD 32 GB support noted; USB OTG not supported due to USB connector; DDR3 uses 1.5V SSTL; Added GND and Vcc connections to JX1 and JX2 connections, re-ordered numerically by JX1/JX2 pin numbers; Updated 1.8V current estimate since it is the DDR Termination LDO input; updated mechanical drawings with all measurements in inches; Corrected independence of Bank 13 voltage rail. |

| 1.2     | 11/26/2013 | Updated Table 12 & 13 SOC Pin numbers & names. Added vertical dimensions to Mechanical section.                                                                                                                                                                                                                                                                                              |

| 1.3     | 12/18/2013 | Updated table 13, PMOD header to FPGA pin numbers.                                                                                                                                                                                                                                                                                                                                           |

| 1.4     | 01/28/2014 | Updated based on feedback: Pgs: 11, 16, 21.                                                                                                                                                                                                                                                                                                                                                  |

| 1.5     | 06/18/2014 | Added Tables 1 and 2; Clarified Kit vs. SOM product inclusions; Updated USB Device mode instructions; Updated 1.35V DDR3 operation; Updated 12V Vin option; Added Rev F TI level translator for SD card interface; Clarified temperature range of microSD card connector;                                                                                                                    |

| 1.6     | 01/22/2015 | Added industrial cost-optimized SOMs to product table; added note that cost-optimized SOMs default to QSPI boot mode. Added note about WebPack and option to purchase Vivado Debug EF-VIVADO-DEBUG-NL                                                                                                                                                                                        |

# **Contents**

| 1 | Intro           | oduc  | ction                                  | 5   |  |

|---|-----------------|-------|----------------------------------------|-----|--|

|   | 1.1 Definitions |       |                                        |     |  |

|   | 1.2             | Fea   | tures                                  | 7   |  |

|   | 1.3             | Zyn   | q Bank Pin Assignments                 | 9   |  |

| 2 | Fun             | ctio  | nal Description                        | 10  |  |

|   | 2.1             | All F | Programmable SoC                       | 10  |  |

|   | 2.2             | Men   | nory                                   | 10  |  |

|   | 2.2.            | 1     | DDR3                                   | 10  |  |

|   | 2.2.2           | 2     | SPI Flash                              | 12  |  |

|   | 2.2.3           | 3     | microSD Card Interface                 | 12  |  |

|   | 2.3             | USE   | 3                                      | 14  |  |

|   | 2.3.            | 1     | USB Host 2.0                           | 14  |  |

|   | 2.3.2           | 2     | USB-to-UART Bridge                     | 16  |  |

|   | 2.3.3           | 3     | USB circuit protection                 | 17  |  |

|   | 2.4             | Cloc  | ck source                              | 17  |  |

|   | 2.5             | Res   | et Sources                             | 17  |  |

|   | 2.5.            | 1     | Power-on Reset (PS_POR_B)              | 17  |  |

|   | 2.5.2           | 2     | Program_B, DONE, PUDC_B, INIT_B        | 17  |  |

|   | 2.5.3           | 3     | Processor Subsystem Reset              | 18  |  |

|   | 2.6             | Use   | r I/O                                  | 19  |  |

|   | 2.6.            | 1     | User Push Button                       | 19  |  |

|   | 2.6.2           | 2     | User LED                               | 19  |  |

|   | 2.7             | 10/1  | 00/1000 Ethernet PHY                   | 19  |  |

|   | 2.8             | Exp   | ansion Headers                         | 21  |  |

|   | 2.8.1           | 1     | Digilent Pmod™ Compatible Header (2x6) | 21  |  |

|   | 2.8.2           | 2     | MicroHeaders                           | 22  |  |

|   | 2.9             | Con   | figuration Modes                       | 27  |  |

|   | 2.9.            | 1     | JTAG                                   | 29  |  |

|   | 2.10            | Pow   | /er                                    | 29  |  |

|   | 2.10            | .1    | Primary Power Input                    | 29  |  |

|   | 2.10            | .2    | Using 12V for Vin                      | 31  |  |

|   | 2.10            | .3    | Regulators                             | 32  |  |

|   | 2.10            | .4    | Sequencing                             | 35  |  |

|   | 2.10            | .5    | Bypassing/Decoupling                   | 36  |  |

|   | 2.10            | .6    | Power Good LED                         | 37  |  |

|   | 2.10            | .7    | Power Estimation                       | 37  |  |

|   | 2.10            | .8    | XADC Power Configuration               | .38 |  |

|   | 2.10 | 0.9 Battery Backup for Device Secure Boot Encryption Key | 38 |

|---|------|----------------------------------------------------------|----|

|   | 2.10 | 0.10 Cooling Fan                                         | 38 |

| 3 |      | ng-7000 AP SoC I/O Bank Allocation                       |    |

|   | 3.1  | PS MIO Allocation                                        | 39 |

|   | 3.2  | Zynq-7000 AP SoC Bank Voltages                           | 41 |

| 4 | Jun  | nper Settings                                            | 42 |

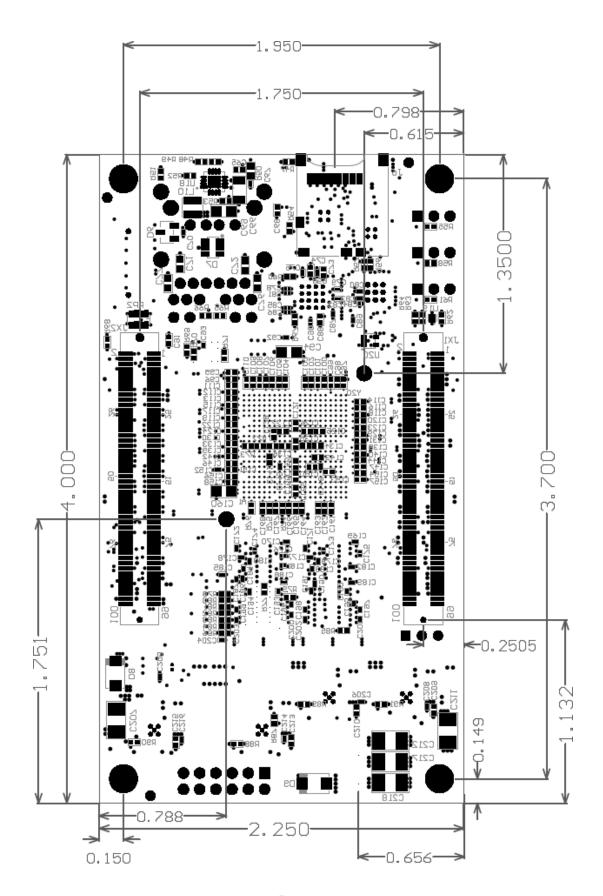

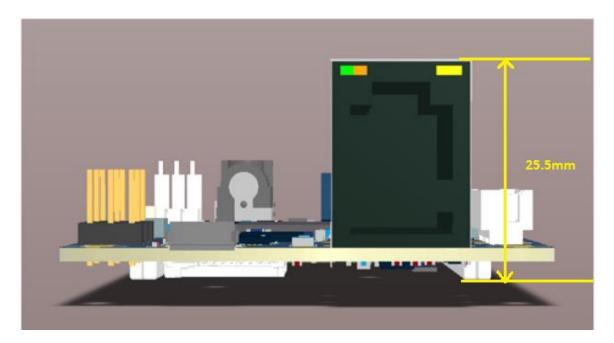

| 5 | Med  | chanical                                                 | 43 |

| 6 | Dis  | claimer                                                  | 45 |

# 1 Introduction

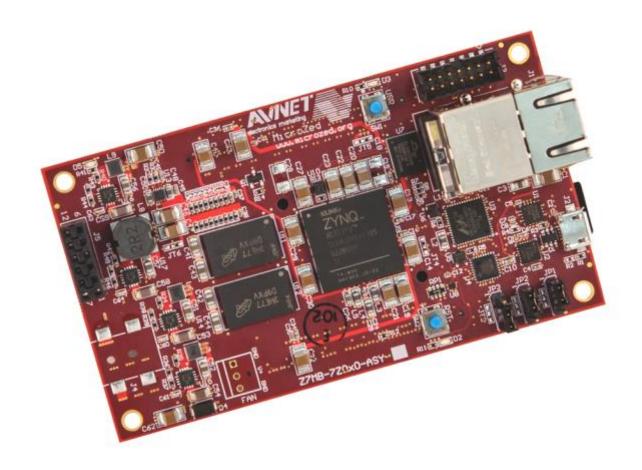

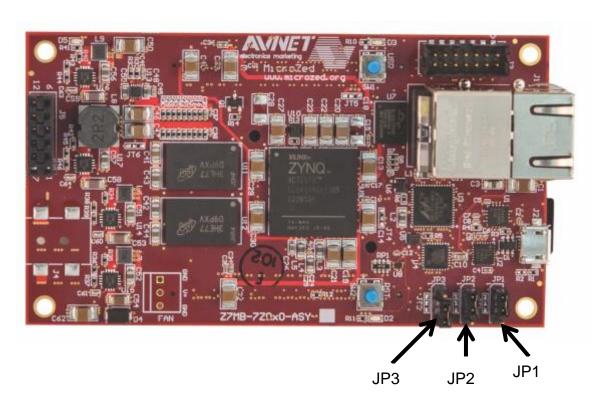

The MicroZed is a low cost evaluation board and system on module (SOM) targeted for broad use in many applications. This document covers the following products.

Table 1 - MicroZed Products

| Name                                   | Part Number            | Zynq Device      | Tested<br>Temperature<br>Range |

|----------------------------------------|------------------------|------------------|--------------------------------|

| Evaluation Kit                         | AES-Z7MB-7Z010-G       | XC7Z010-1CLG400C | 0° to 70° C                    |

| 7010 SOM                               | AES-Z7MB-7Z010-SOM-G   | XC7Z010-1CLG400C | 0° to 70° C                    |

| 7010 Industrial SOM                    | AES-Z7MB-7Z010-SOM-I-G | XC7Z010-1CLG400I | -40° to 85° C*                 |

| 7010 Cost-Optimized SOM                | AES-Z7MB-7Z010-C01-G   | XC7Z010-1CLG400C | 0° to 70° C                    |

| 7010 Industrial Cost-<br>Optimized SOM | AES-Z7MB-7Z010-C01-I-G | XC7Z010-1CLG400I | -40° to 85° C*                 |

| 7020 SOM                               | AES-Z7MB-7Z020-SOM-G   | XC7Z020-1CLG400C | 0° to 70° C                    |

| 7020 Industrial SOM                    | AES-Z7MB-7Z020-SOM-I-G | XC7Z020-1CLG400I | -40° to 85° C*                 |

| 7020 Cost-Optimized SOM                | AES-Z7MB-7Z020-C01-G   | XC7Z020-1CLG400C | 0° to 70° C                    |

| 7020 Industrial Cost-<br>Optimized SOM | AES-Z7MB-7Z020-C01-I-G | XC7Z020-1CLG400I | -40° to 85° C*                 |

<sup>\*</sup>Except for the microSD card connector which is only rated -25° to 85° C

# 1.1 Definitions

# **Table 2 – Product Definitions**

| Name                              | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Evaluation Kit                    | The evaluation kit version of MicroZed includes the Zynq 7010 device as well as several other items to make out-of-box evaluation simpler. These extra items include a micro-USB cable, Vivado Design Edition license voucher (device-locked to the 7010), 4 GB microSD card pre-loaded with a Linux test system, and a plastic carrying box. The majority of the tutorials published at <a href="https://www.microzed.org">www.microzed.org</a> are targeted at this kit. The board included in the kit will work either as a standalone board or as a SOM plugged onto a carrier card. |

| SOM                               | System-on-module. These cards will work standalone or plugged into a carrier card. The SOM versions exclude a few items outlined in the Evaluation Kit definition above. The SOMs are intended to be sold in volume, for use with carrier cards.                                                                                                                                                                                                                                                                                                                                         |

| Industrial SOM                    | Same as the SOM, except populated entirely with components that comply with a tested temperature range of -40° to 85° C, with the exception of the microSD card connector (502570-0893) which is rated at -25° to 85° C. Avnet has tested the Industrial SOMs to this temperature range with a thorough functional test. However, Avnet does not guarantee that the industrial SOM will function to this full temperature range under all conditions. End users are still responsible for proper airflow and heat mitigation.                                                            |

| Cost-Optimized SOM                | This is identical to the SOM with the exception that all of the circuitry required for operating in standalone mode has been removed. The cost-optimized SOMs will ONLY work when plugged into a carrier card. The reduction in components allows these boards to be offered at a lower cost in volume. For a full listing of differences, see the yellow-highlighted items in the cost-optimized bill of materials.                                                                                                                                                                     |

| Industrial Cost-<br>Optimized SOM | Same as the Cost-Optimized SOM, except populated entirely with components that comply with a tested temperature range of -40° to 85° C, with the exception of the microSD card connector (502570-0893) which is rated at -25° to 85° C. Avnet has tested the Industrial SOMs to this temperature range with a thorough functional test. However, Avnet does not guarantee that the industrial Cost-Optimized SOM will function to this full temperature range under all conditions. End users are still responsible for proper airflow and heat mitigation.                              |

# 1.2 Features

The features provided by the MicroZed consist of:

- Xilinx Zynq 7010/7020 CLG400 AP SOC

- Primary configuration = QSPI Flash

- Auxiliary configuration options

- JTAG (through PL via Xilinx PC4 Header)

- microSD Card

- Memory

- 1 GB DDR3 (x32)

- 128 Mb QSPI Flash

- GB microSD Card (Evaluation Kit only, AES-Z7MB-7Z010-G)

- Interfaces

- Xilinx PC4 Header for programming

- Accesses Programmable Logic (PL) JTAG

- Processing System (PS) JTAG pins connected through Digilent Pmod<sup>™</sup> compatible interface

- 10/100/1000 Ethernet

- USB Host 2.0

- microSD Card

- USB 2.0 Full-Speed USB-UART bridge

- One Digilent Pmod compatible interface, connected to PS MIO

- Two 100-pin MicroHeaders

- Reset Button

- 1 User Push Button

- 1 User LEDs

- DONE LED

- On-board Oscillator

- 33.333 MHz

- Power

- High-efficiency regulators for Vccint, Vccpint, Vccbram, Vccaux, Vccpaux, Vccpll, Vcco\_0, Vcco\_ddr, Vcco\_mio

- Three potential powering methods

- USB Bus Power from USB-UART interface

- Optional barrel jack and AC/DC supply

- Optional carrier card

- Software

- Vivado Design Suite

- Download from <u>www.xilinx.com/support/download.html</u>

- Request a free DVD from www.xilinx.com/onlinestore/dvd fulfillment request.htm

- Vivado Design Suite: Design Edition license voucher (node-locked, device-locked to the XC7Z010 – Evaluation Kit only, AES-Z7MB-7Z010-G)

- NOTES

- Xilinx offers the WebPack Vivado license which covers both the 7Z010 and 7Z020.

See <a href="http://www.xilinx.com/products/design\_tools/vivado-webpack.htm">http://www.xilinx.com/products/design\_tools/vivado-webpack.htm</a>

- WebPack users may purchase EF-VIVADO-DEBUG-NL for \$695 to add Vivado Logic Analyzer and Vivado Serial I/O Analyzer. Speak to your local Avnet/Silica representative or <u>click here to find this Online</u>.

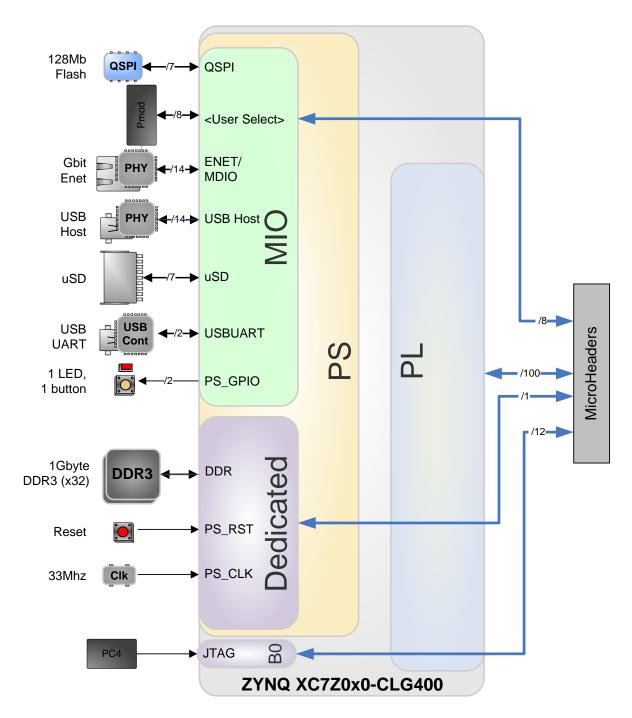

Figure 1 – MicroZed Block Diagram

# 1.3

Zynq Bank Pin Assignments

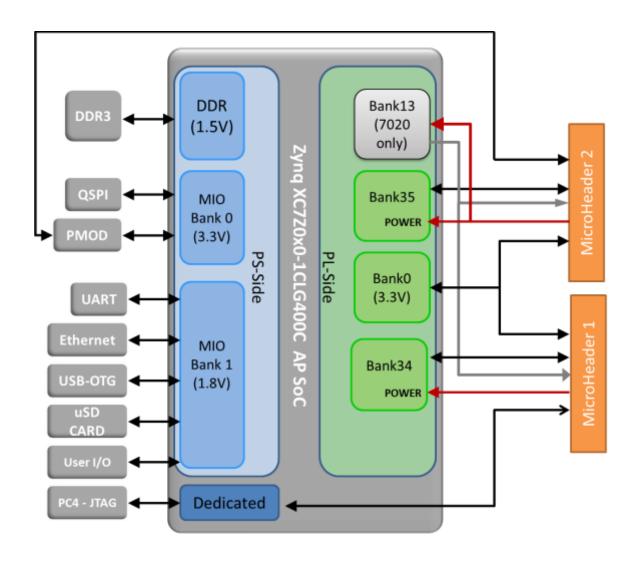

The following figure shows the Zynq bank pin assignments on the MicroZed followed by a table that shows the detailed I/O connections.

Figure 2 – Zynq CLG400 Bank Assignments

# **2 Functional Description**

# 2.1 All Programmable SoC

MicroZed includes a Xilinx Zynq XC7Z010-1CLG400C or Zynq XC7Z020-1CLG400C AP SoC. Other temperature or speed grades are available as a custom order through Avnet Engineering Services.

# 2.2 Memory

Zynq contains a hardened PS memory interface unit. The memory interface unit includes a dynamic memory controller and static memory interface modules. MicroZed takes advantage of these interfaces to provide system RAM as well as two different bootable, non-volatile memory sources.

### 2.2.1 DDR3

MicroZed includes two Micron MT41K256M16HA-125:E DDR3 memory components creating a 256M x 32-bit interface, totaling 1 GB of random access memory. The DDR3 memory is connected to the hard memory controller in the PS of the Zynq AP SoC. The PS incorporates both the DDR controller and the associated PHY, including its own set of dedicated I/Os.

Speed of up to 1,066 MT/s for DDR3 is supported.

The MicroZed DDR3 interface uses 1.5V SSTL-compatible inputs. When MicroZed was first designed, Zynq did not support 1.35V signaling. The Micron MT41K DDR3L components are 1.35V components that are backward compatible with 1.5V interfaces. Since the MicroZed release, Xilinx has qualified the Zynq-7000 DDR3 interface at 1.35V as well. Preliminary testing indicates that MicroZed operates with the Vcco\_ddr interface at 1.35V. To experiment with this, change R39 to 18.7K $\Omega$ . To request this change on a volume order, please contact customize@avnet.com.

DDR3 Termination is utilized on the MicroZed and configured for fly-by routing topology, as recommended in <u>AR55820</u>. Additionally the board trace lengths are matched, compensating for the XC7Z010-CLG400 internal package flight times, to meet the requirements listed in the Zynq-7000 AP SoC PCB Design and Pin Planning Guide (UG933).

All single-ended signals are routed with 40 ohm trace impedance. DCI resistors (VRP/VRN), as well as differential clocks, are set to 80 ohms. DDR3-CKE0 is terminated through 40 ohms to VTT as described in <u>AR51778</u>. DDR3-ODT has the same 40 ohm to VTT termination. At the time of the MicroZed design, there was a discrepancy in the Xilinx documentation regarding whether DDR3-RESET# should have 40 ohms to VTT or 4.7K ohm to GND, which is why JT6 was designed in to give both options. Xilinx has since clarified that 4.7K-ohm to GND is the correct configuration for DDR3-RESET#. See AR55616.

Each DDR3 chip has its own 240-ohm pull-down on ZQ. Note DDR-VREF is not the same as DDR-VTT.

Table 3 - DDR3 Connections

| Signal Name    | Description                             | Zynq AP SOC pin   | DDR3 pin     |

|----------------|-----------------------------------------|-------------------|--------------|

| DDR_CK_P       | Differential clock output               | L2                | J7           |

| DDR_CK_N       | Differential clock output               | M2                | K7           |

| DDR_CKE        | Clock enable                            | N3                | K9           |

| DDR_CS_B       | Chip select                             | N1                | L2           |

| DDR_RAS_B      | RAS row address select                  | P4                | J3           |

| DDR_CAS_B      | RAS column address select               | P5                | K3           |

| DDR_WE_B       | Write enable                            | M5                | L3           |

| DDR_BA[2:0]    | Bank address                            | PS_DDR_BA[2:0]    | BA[2:0]      |

| DDR_A[14:0]    | Address                                 | PS_DDR_A[14:0]    | A[14:0]      |

| DDR_ODT        | Output dynamic termination              | N5                | K1           |

| DDR_RESET_B    | Reset                                   | B4                | T2           |

| DDR_DQ[31:0]   | I/O Data                                | PS_DDR_[31:0]     | DDR3_DQ pins |

| DDR_DM[3:0]    | Data mask                               | PS_DDR_DM[3:0]    | LDM/UDM x2   |

| DDR_DQS_P[3:0] | I/O Differential data strobe            | PS_DDR_DQS_P[3:0] | UDQS/LDQS    |

| DDR_DQS_N[3:0] | I/O Differential data strobe            | PS_DDR_DQS_N[3:0] | UDQS#/LDQS#  |

| DDR_VRP        | I/O Used to calibrate input termination | H5                | N/A          |

| DDR_VRN        | I/O Used to calibrate input termination | G5                | N/A          |

| DDR_VREF[1:0]  | I/O Reference voltage                   | H6, P6            | DDR_VREF     |

### 2.2.2 SPI Flash

MicroZed features a 4-bit SPI (quad-SPI) serial NOR flash. The Spansion S25FL128S (S25FL128SAGBHI200) is used on this board. The Multi-I/O SPI Flash memory is used to provide non-volatile boot, application code, and data storage. It can be used to initialize the PS subsystem as well as configure the PL subsystem (bitstream). Spansion provides Spansion Flash File System (FFS) for use after booting the Zynq-7000 AP SoC.

- The relevant device attributes are:

- 128Mbit

- x1, x2, and x4 support

- Speeds up to 104 MHz, supporting Zynq configuration rates @ 100 MHz

- In Quad-SPI mode, this translates to 400Mbs

- Powered from 3.3V

The SPI Flash connects to the Zynq PS QSPI interface. This requires connection to specific pins in MIO Bank 0/500, specifically MIO[1:6,8] as outlined in the Zynq TRM. Quad-SPI feedback mode is used, thus qspi\_sclk\_fb\_out/MIO[8] is connected to a 20K pull-up resistor to 3.3V and nothing else. This allows a QSPI clock frequency greater than FQSPICLK2. The 20K pull-up straps vmode[1], setting the Bank 1 Voltage to 1.8V.

Table 4 – QSPI Flash Pin Assignment and Definitions

| Signal Name | Description       | Zynq Pin            | MIO | QSPI Pin |

|-------------|-------------------|---------------------|-----|----------|

| CS          | Chip Select       | A7 (MIO Bank 0/500) | 1   | 1        |

| DQ0         | Data0             | B8 (Bank MIO0/500)  | 2   | 5        |

| DQ1         | Data1             | D6 (MIO Bank 0/500) | 3   | 2        |

| DQ2         | Data2             | B7 (MIO Bank 0/500) | 4   | 3        |

| DQ3         | Data3             | A6 (MIO Bank 0/500) | 5   | 7        |

| SCK         | Serial Data Clock | A5 (MIO Bank 0/500) | 6   | 6        |

| FB Clock    | QSPI Feedback     | D5 (MIO Bank 0/500) | 8   | N/A      |

Note: The QSPI data and clock pins are shared with the vmode and BOOT MODE jumpers.

Larger Spansion devices are footprint compatible. To request a larger device on a volume order, please contact customize@avnet.com.

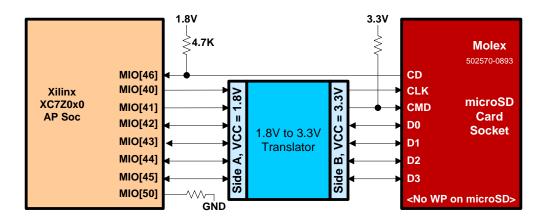

# 2.2.3 microSD Card Interface

The Zynq PS SD/SDIO peripheral controls communication with the MicroZed microSD Card. A commercial temperature grade 4GB card is included in the MicroZed Evaluation Kit (AES-Z7MB-7Z010-G). The microSD card can be used for non-volatile external memory storage as well as booting the Zynq-7000 AP SoC. PS peripheral sd0 is connected through Bank 1/501 MIO[40-46], including Card Detect. microSD cards do not include a Write Protect signal, but the Linux driver expects to have one. Therefore, MicroZed connects MIO[50] as a SD\_WP pin that simply goes to a pull-down. This signal is not connected to the microSD card in any way; it was added only for increased Linux compatibility.

The microSD Card is a 3.3V interface but is connected through MIO Bank 1/501 which is set to 1.8V. Therefore, a level shifter performs this voltage translation. MicroZed Revisions B and

C use the Maxim MAX13035EETE+. Revision F uses Texas Instruments' TXS02612. Both devices are functionally equivalent on MicroZed.

The TXS02612 includes a 6-channel SPDT switch with voltage-level translation capability. This allows a single SDIO port to be interfaced with two SDIO peripherals, although on MicroZed the port expansion is not utilized. The device is only used for voltage translation. The TXS02612 has three separate supply rails that operate over the full range of 1.1 V to 3.6 V. This allows the Zynq MIO and SDIO peripherals to operate at different supply voltages if required.

The MAX13035 is 6-channel, bidirectional level translator that provides the level shifting necessary for 100Mbps data transfer in multi-voltage systems. The MAX13035E is ideally suited for memory-card level translation, as well as generic level translation in systems with six channels.

As stated in the Zynq TRM, host mode is the only mode supported.

The MicroZed microSD Card is connected through a 8-pin micro SD card connector, J6, Molex 502570-0893. Note that this connector's supported temperature range is -25° to 85° C, even on the Industrial MicroZed SOMs. A Class 4 card or better is recommended. Up to 32 GB is supported. If a user intends to use the microSD card interface at industrial temperatures, an industrial temperature microSD card is required. Please request more information on this from your local Avnet representative.

Figure 3 - microSD Card Interface

Table 5 – microSD Card Pin Assignment and Definitions

| Signal<br>Name | Description   | Zynq Pin                                                  | MIO   | Level Shift<br>Pin | SD Card<br>Pin    |

|----------------|---------------|-----------------------------------------------------------|-------|--------------------|-------------------|

| CLK            | Clock         | D14 (MIO Bank 1/501)                                      | 40    | Pass-Thru          | 5                 |

| CMD            | Command       | C17 ((MIO Bank 1/501)                                     | 41    | Pass-Thru          | 3                 |

| Data[3:0]      | Data          | MIO Bank 1/501<br>D0: E12<br>D1: A9<br>D2: F13<br>D3: B15 | 42:45 | Pass-Thru          | Data Pins 7 8 1 2 |

| CD             | Card Detect   | D16 (MIO Bank 1/501)                                      | 46    | Pass-Thru          | CD                |

| WP             | Write Protect | B13 MIO Bank 1/501                                        | 50    | N/C                | N/C               |

### 2.3 USB

### 2.3.1 USB Host 2.0

MicroZed implements one of the two available PS USB 2.0 interfaces. An external PHY with an 8-bit ULPI interface is required. A SMSC USB3320 Standalone USB Transceiver Chip is used as the PHY. The PHY features a complete HS-USB Physical Front-End supporting speeds of up to 480Mbs. VDDio for this device can be 1.8V or 3.3V, and on MicroZed it is powered at 1.8V. The PHY is connected to MIO Bank 1/501, which is also powered at 1.8V. This is critical since a level translator cannot be used as it would impact the tight ULPI timing.

Additionally the USB chip must clock the ULPI interface which requires a 24 MHz crystal or oscillator (configured as ULPI Output Clock Mode). On MicroZed, the 24 MHz oscillator is a Discera DSC1001 CMOS oscillator.

The USB connector is Type A and is combined with the Ethernet RJ45. This combination connector is J1, Bel-Fuse 0821-1X1T-43-F.

The usb0 peripheral is used on the PS, connected through MIO[28-39] in MIO Bank 1/501. With the USB Reset signal connected to MIO[7]. Signal PS\_MIO7 is a 3.3V signal. It is ANDed with the power-on reset (PG\_MODULE) signal and then level shifted to 1.8V through U8, TI TXS0102 before connecting to the USB3320 Pin 27 RESET.

In the default Host mode, MicroZed provides the Vbus supply. In the default standalone mode where the MicroZed is powered from the USB-UART port, the amount of power available to the MicroZed is limited. Therefore, care should be taken in this USB-UART powered mode to only attach devices to the USB Host that consume less than 100 mA.

When MicroZed is powered via a carrier board or through the on-board DC barrel jack with 5V, MicroZed can deliver up to 500mA of 5V on Vbus via a pass-through resistor, R50. MicroZed also has a non-default option of being driven by a 12V input. In this case, a 12V-to-5V power supply must be populated when in Host mode. When the 12V-to-5V circuit is populated, R50 must be removed. See the schematics and Section 2.10.2 for details.

Table 6 – USB Host Pin Assignment and Definitions

| Signal Name | Description                             | Zynq Bank      | MIO   | SMSC 3320<br>Pin | USB Conn<br>Pin |

|-------------|-----------------------------------------|----------------|-------|------------------|-----------------|

| Data[7:0]   | USB Data lines                          | MIO Bank 1/501 | 28:39 | Data[7:0]        | N/C             |

| REFCLOCK    | USB Clock                               | MIO Bank 1/501 |       | 26               | N/C             |

| DIR         | ULPI DIR output signal                  | MIO Bank 1/501 |       | 31               | N/C             |

| STP         | ULPI STP input signal                   | MIO Bank 1/501 |       | 29               | N/C             |

| NXT         | ULPI NXT output signal                  | MIO Bank 1/501 |       | 2                | N/C             |

| REFSEL[2:0] | USB Chip Select                         | N/C            | N/C   | 8,11,14          | N/C             |

| DP          | DP pin of USB Connector                 |                |       | 18               | 2               |

| DM          | DM pin of USB Connector                 |                |       | 19               | 3               |

| ID          | Identification pin of the USB connector |                |       | 23               | 4               |

| RESET_B     | Reset                                   | MIO Bank 1/501 | 7**   | 27**             | N/C             |

<sup>\*\*</sup> Connected through AND-gate with PG\_MODULE through level translator (TI TXS0102DQE).

### Device Mode

MicroZed is preconfigured for USB Host mode by default. The mode can be changed to Device mode by changing the following components:

To put MicroZed in Device Mode:

- Remove C1 (100uF)

- Remove C3 (22uF)

- Remove R50

- Remove L10 (not populated by default)

- Ensure that R56 is populated with a 10KΩ resistor (Revisions prior to F-06 may have a 1KΩ resistor. See the MicroZed Errata).

Customers may request the USB Device population option for a volume purchase by contacting <a href="mailto:customize@avnet.com">customize@avnet.com</a>. Be aware that the SMSC USB3320 specifies that its ID pin (pin 23) should be connected to VDD33. Since MicroZed's default option if for the USB to be in Host mode, the ID pin is tied to GND. This does not prevent the USB3320 from operating in Device mode. However, users must ensure their LINK software is able to ignore the state of the ID pin.

### **OTG Mode**

Note that MicroZed does not support OTG mode since a 5-pin USB connector is not used, therefore the ID pin is not available to detect role change. Zynq and the SMSC PHY both support OTG mode with a USB connector that supports it.

# 2.3.2 USB-to-UART Bridge

MicroZed implements a USB-to-UART bridge connected to a PS UART peripheral. A Silicon Labs CP2104 USB-to-UART Bridge device allows connection to a host computer. The CP2104 connects to the USB Micro AB connector, J2, (FCI 10104111-0001LF). Only basic TXD/RXD connection is implemented.

Silicon Labs provides royalty-free Virtual COM Port (VCP) drivers which permit the CP210x USB-to-UART bridge to appear as a COM port to host computer communications application software (for example, HyperTerm or Tera Term). Please refer to the *Silicon Labs CP210x USB-to-UART Setup Guide* available at <a href="https://www.microzed.org">www.microzed.org</a>. Note that each CP2104 ships with a unique ID and appears as a unique device when connected to a PC. Windows will enumerate multiple MicroZed boards with a unique COM port for each one. This means that multiple MicroZeds can be connected to a single PC without issue.

The uart1 Zynq PS peripheral is accessed through MIO[48:49] in MIO Bank 1/501 (1.8V). The CP2104 features adjustable I/O voltage, so it is connected directly to Zyng.

This USB port can power the board. By USB specification, a single USB port can only supply a maximum of 500 mA @ 5V. For simply PS experimentation, this is enough. However, when powered from this port, it is recommended that less than 100mA @ 5V be consumed on the USB-Host interface. Also, if the PL fabric is exercised in the design, the 2.5W available on a single USB port may not be enough. Additional power could be obtained by switching over to a USB Y-cable (with two connections to the Host for 1A) or connecting to a USB 3.0 port. MicroZed is also designed to get power from the carrier card or by populating a DC barrel jack (J4).

Table 7 – CP2104 Connections

| UART Function in Zynq | Zynq Pin                | MIO | Schematic Net<br>Name | CP2104<br>Pin | UART Function in CP2104 |

|-----------------------|-------------------------|-----|-----------------------|---------------|-------------------------|

| TX, data out          | B12 (MIO Bank<br>1/501) | 48  | USB_1_RXD             | 23            | RXD, data in            |

| RX, data in           | C12 (MIO Bank<br>1/501) | 49  | USB_1_TXD             | 4             | TXD, data out           |

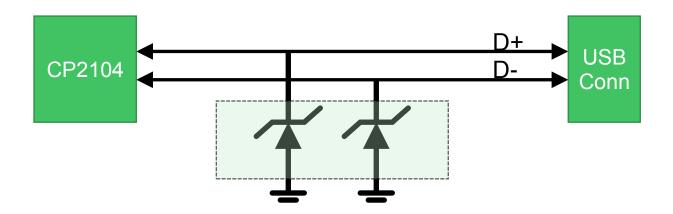

# 2.3.3 USB circuit protection

All USB data lines, D+/-, are protected with Bourns Steering Diodes, CDSOT23-SR208.

Figure 4 - ESD Protection

# 2.4 Clock source

The MicroZed connects a dedicated 33.3333 MHz clock source to the Zynq-7000 AP SoC's PS. A Discera DSC1001DI1-033.3300 with 40-ohm series termination is used. The PS infrastructure can generate up to four PLL-based clocks for the PL system. An attached carrier card can also supply clocks to the PL subsystem.

# 2.5 Reset Sources

# 2.5.1 Power-on Reset (PS\_POR\_B)

The Zynq PS supports an external power-on reset signal. The power-on reset is the master reset of the entire chip. This signal resets every register in the device capable of being reset. On MicroZed this signal, labeled PG\_MODULE, is connected to the power good output of the final stage of the power regulation circuitry. These power supplies have open drain outputs that pull this signal low until the output voltage is valid. If a carrier card is connected to MicroZed, the carrier card should also wire-OR to this net and not release it until the carrier card power is also good. Other IC's on MicroZed are reset by this signal as well.

To stall Zynq boot-up, this signal should be held low. No other signal (SRST, PROGRAM\_B, INIT\_B) is capable of doing this as in other FPGA architectures.

# 2.5.2 Program\_B, DONE, PUDC\_B, INIT\_B

INIT\_B, Program\_B\_0 and PUDC\_B all have 4.7K-ohm pull-ups to 3.3V. INIT\_B, PUDC\_B and DONE signals are routed to the carrier card via the MicroHeaders, JX1 and JX2.

When PL configuration is complete, a blue LED D2, labeled DONE, will light.

# 2.5.3 Processor Subsystem Reset

System reset, labeled PS\_SRST#, resets the processor as well as erases all debug configurations. The external system reset allows the user to reset all of the functional logic within the device without disturbing the debug environment. For example, the previous break points set by the user remain valid after system reset. Due to security concerns, system reset erases all memory content within the PS, including the OCM. The PL is also reset in system reset. System reset does not re-sample the boot mode strapping pins.

This active-low signal can be asserted by a pushbutton, SW2. Through an open-drain buffer, this signal also connects to the carrier card via the MicroHeader and the PC4 JTAG interface.

Note: This signal cannot be asserted while the boot ROM is executing following a POR reset. If PS\_SRST\_B is asserted while the boot ROM is running through a POR reset sequence it will trigger a lock-down event preventing the boot ROM from completing. To recover from lockdown the device either needs to be power cycled or PS\_POR\_B needs to be asserted.

# 2.6 User I/O

# 2.6.1 User Push Button

MicroZed provides 1 user GPIO push button to the Zynq-7000 AP SoC; interfacing to the PS. A pull-down resistor provides a known default state. Pushing the button connects the I/O to Vcco.

**Table 8 - Push Button Connections**

| Signal Name | Subsection        | MIO Pin | Zynq pin |

|-------------|-------------------|---------|----------|

| PB1         | PS (MIO Bank 500) | MIO[51] | B9       |

# 2.6.2 User LED

The MicroZed has one user LED. A logic high from the Zynq-7000 AP SoC I/O causes the LED to turn on.

Table 9 - LED Connections

| REFDES | Subsection        | MIO Pin | Zynq pin |

|--------|-------------------|---------|----------|

| D3     | PS (MIO Bank 501) | MIO[47] | B14      |

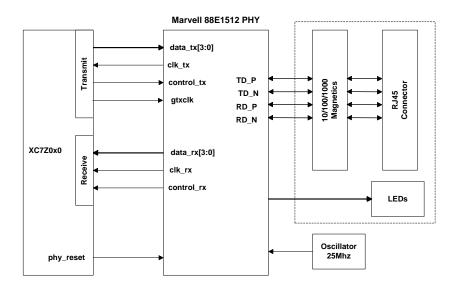

# 2.7 10/100/1000 Ethernet PHY

MicroZed implements a 10/100/1000 Ethernet port for network connection using a Marvell 88E1512 PHY. This part operates at 1.8V. The PHY connects to MIO Bank 1/501 (1.8V) and interfaces to the Zynq-7000 AP SoC via RGMII.

The RJ-45 connector, J1 (BEL 0821-1X1T-43-F), is shared with the USB-Host interface. The RJ-45 integrates two status indicator LEDs that indicate traffic and valid link state.

A high-level block diagram the 10/100/1000 Ethernet interface is shown in the following figure.

Figure 5 – 10/100/1000 Ethernet Interfac

Zynq requires a voltage reference for RGMII interfaces. Thus PS\_MIO\_VREF, E11, is tied to 0.9V, half the bank voltage of MIO Bank 1/501. The 0.9V is generated through a resistor divider.

The 88E1512 also requires a 25 MHz input clock. A Discera DSC1001DI1-025.0000 is used as this reference.

Table 10 – Ethernet PHY Pin Assignment and Definitions

| Signal Name | Description      | Zynq pin  | MIO   | 88E1512 pin |

|-------------|------------------|-----------|-------|-------------|

| RX_CLK      | Receive Clock    | B17       | 16:27 | 46          |

| RX_CTRL     | Receive Control  | D13       |       | 43          |

| RXD[3:0]    | Receive Data     | RXD0: D11 |       | 44          |

|             |                  | RXD1: A16 |       | 45          |

|             |                  | RXD2: F15 |       | 47          |

|             |                  | RXD3: A15 |       | 48          |

| TX_CLK      | Transmit Clock   | A19       |       | 53          |

| TX_CTRL     | Transmit Control | F14       |       | 56          |

| TXD[3:0]    | Transmit Data    | TXD0: E14 |       | 50          |

|             |                  | TXD1: B18 |       | 51          |

|             |                  | TXD2: D10 |       | 54          |

|             |                  | TXD3: A17 |       | 55          |

| MDIO        | Management Data  | C11       | 53    | 8           |

| MDC         | Management Clock | C10       | 52    | 7           |

| ETH_RST_N   | PHY Reset        |           |       | 16**        |

<sup>\*\*</sup> Controlled via level translator U8 and can be held low using PG\_MODULE signal.

The datasheet for the Marvell 88E1512 is not available publicly. An NDA is required for this information. Please contact your local Avnet Memec or Marvell representative for assistance.

# 2.8 Expansion Headers

# 2.8.1 Digilent Pmod™ Compatible Header (2x6)

MicroZed has one Digilent Pmod™ compatible header (2x6), J5. This is a right-angle, 0.1" female header (Bourns BCS-106-L-D-TE) that includes eight user I/O plus 3.3V and ground signals as shown in the figure below.

The Digilent Pmod compatible interface connects to the PS-side on MIO pins [0, 9-15] in MIO Bank 0/500 (3.3V). Uses for this Digilent Pmod compatible interface include PJTAG access (MIO[10-13]) as well as nine other hardened MIO peripherals (SPI, GPIO, CAN, I2C, UART, SD, QSPI, Trace, Watchdog).

These 8 MIO pins are also routed to the MicroHeader so they can be utilized on an expansion carrier card. NOTE: These MIO pins should not be simultaneously used by both the MicroZed and MicroHeader interfaces.

Figure 6 - Digilent Pmod™ Compatible Interface Connections

| <b>Table 11 –</b> | Digilent | Pmod™ ( | Compatible Interf | ace ( | Connections |

|-------------------|----------|---------|-------------------|-------|-------------|

|                   |          |         |                   |       |             |

| Pmod     | Signal Name | PS MIO Pin | Zynq pin |

|----------|-------------|------------|----------|

| J5       | PMOD_D0     | MIO 13     | E8       |

| MIO Pmod | PMOD_D1     | MIO 10     | E9       |

|          | PMOD_D2     | MIO 11     | C6       |

|          | PMOD_D3     | MIO 12     | D9       |

|          | PMOD_D4     | MIO 0      | E6       |

|          | PMOD_D5     | MIO 9      | B5       |

|          | PMOD_D6     | MIO 14     | C5       |

|          | PMOD_D7     | MIO 15     | C8       |

### 2.8.2 MicroHeaders

MicroZed features two 100-pin MicroHeaders (FCI, 61082-101400LF) for connection to expansion carrier cards. Each connector interfaces PL I/O to the carrier card as well as eight PS-MIO, two dedicated analog inputs, the four dedicated JTAG signals, power and control signals.

NOTE: The eight PS-GPIO and four JTAG signals are shared on MicroZed, thus for each interface, it can only be used on either MicroZed or the carrier card, not simultaneously.

The connectors are FCI 0.8mm Bergstak®, 100 Position, Dual Row, BTB Vertical Receptacles. These have variable stack heights from 5mm to 16mm, making it easy to connect to a variety of expansion or system boards. The carrier card can power MicroZed as an alternative to the on-board USB-UART port or DC jack. Each pin can carry 500mA of current and support I/O speeds in excess of what Zyng can achieve.

MicroZed does not power the PL VCC<sub>IO</sub> banks. This is required by the carrier card. This gives the carrier card the flexibility to control the I/O bank voltages. Separate routes/planes are used for Vcco\_34 and Vcco\_35 such that the carrier card could potentially power these independently. The 7Z010 has two PL I/O banks, banks 34 and 35, each containing 50 I/O. If populated with a 7Z020, the 7Z020 has a third I/O bank, bank 13, which is partially connected on MicroZed. Bank 13's power has an independent rail, Vcco\_13, which is powered from the Carrier.

NOTE: When used without a carrier card, the PL I/O banks are unpowered on MicroZed. However, the PL fabric is still available for custom HDL logic, without access to PL I/O.

Within a PL I/O bank, there are 50 I/O capable of up to 24 differential pairs. Differential LVDS pairs on a -1 speed grade device are capable of 950Mbps of DDR data. Each differential pair is isolated by a power or ground pin. Additionally, eight of these I/O can be connected as clock inputs (four MRCC and four SRCC inputs). Each PL bank can also be configured to be a memory interface with up to four dedicated DQS data strobes and data byte groups. Bank 35 adds the capability to use the I/O to interface up to 16 differential analog inputs. One of the differential pairs (JX1\_LVDS\_2) in Bank 34 is shared with PUDC\_B.

MicroZed was designed with MIG DDR3 memory DQ byte groups\*. The existing byte groups are defined in the table below:

Table 12 – DQ Byte Groups

| Byte Group | Zynq Pins |

|------------|-----------|------------|-----------|------------|-----------|------------|-----------|

|            | B20       |            | M20       |            | H16       | DQ[31:24]  | G15       |

|            | B19       |            | M17       |            | H17       |            | K14       |

|            | A20       | DQ[15:8]   | M18       | DQ[23:16]  | J18       |            | J14       |

| DQ[7:0]    | D19       |            | K19       |            | H18       |            | L14       |

| DQ[7.0]    | D20       |            | J19       |            | G18       |            | L15       |

|            | E18       |            | L16       |            | J20       |            | M14       |

|            | E19       |            | L17       |            | H20       |            | M15       |

|            | F16       |            | K17       |            | G19       |            | K16       |

<sup>\*</sup>As chosen by MIG 14.4 for a 7Z010-CLG400 package.

The diagram below illustrates the connections on the MicroHeader.

Bank 13 \*\*

TOTAL

8

100

**Table 13 – MicroHeader Pinout**

| Table 13 – Microneader Pillout |                                        |              |              |       |                 |                |              |

|--------------------------------|----------------------------------------|--------------|--------------|-------|-----------------|----------------|--------------|

| Micro                          | oHeader #1 (JX1)                       |              |              | Micro | Header #2 (JX2) |                |              |

| Signa                          | al Name                                | Source       | Pin<br>Count | Sign  | al Name         | Source         | Pin<br>Count |

| Ч                              | Bank 34 I/Os<br>(except for<br>PUDC_B) | Zynq Bank 34 | 49           | PL    | Bank 35 I/Os    | Zynq Bank 35   | 50           |

|                                | TMS_0                                  | Zynq Bank 0  | 5            |       | PS Pmod         | Zynq Bank 500  | 8            |

|                                | TDI_0                                  | Zynq Bank 0  |              |       | MIO[0,9-15]     |                |              |

|                                |                                        |              |              | PS    |                 |                |              |

| JTAG                           | TCK_0                                  | Zynq Bank 0  |              | O     | Init_B_0        | Zynq Bank 0    | 2            |

|                                | TDO_0                                  | Zynq Bank 0  |              |       | Vccio_EN        | Module/Carrier | 1            |

|                                | Carrier_SRST#                          | Carrier      |              |       | PG_MODULE       | Module/Carrier | 1            |

| _                              | VP_0                                   | Zynq Bank 0  | 4            |       | Vin             | Carrier        | 5            |

| Analog                         | VN_0                                   | Zynq Bank 0  |              | Power | GND             | Carrier        | 23           |

| Ane                            | DXP_0                                  | Zynq Bank 0  |              | Pov   | VCCO_35         | Carrier        | 3            |

|                                | DXN_0                                  | Zynq Bank 0  |              |       | Bank 13 pins    | Bank 13 **     | 7            |

| O                              | PUDC_B / IO                            | Zynq Bank 34 | 2            |       |                 | Total          | 100          |

| J                              | DONE                                   | Zynq Bank 0  |              |       |                 |                |              |

|                                | PWR_Enable                             | Carrier      | 1            |       |                 |                |              |

| e                              | Vin                                    | Carrier      | 4            |       |                 |                |              |

| Power                          | GND                                    | Carrier      | 23           |       |                 |                |              |

| Ф.                             | VCCO_34                                | Carrier      | 3            |       |                 |                |              |

|                                | VBATT                                  | Carrier      | 1            |       |                 |                |              |

Bank 13 pins

<sup>\*\* 7020</sup> device only

Table 14 – JX1 Connections

| Fable 14 – J SoC Pin # | MicroZed Net  | JX1   | JX1   | MicroZed Net  | SoC Pin #    |

|------------------------|---------------|-------|-------|---------------|--------------|

| 0001111#               | morozea Net   | Pin # | Pin # | morozea net   | 000 1 III #  |

| Bank 0, F9             | JTAG_TCK      | 1     | 2     | JTAG_TMS      | Bank 0, J6   |

| Bank 0, F6             | JTAG_TDO      | 3     | 4     | JTAG_TDI      | Bank 0, G6   |

| N/A                    | PWR_ENABLE    | 5     | 6     | CARRIER_SRST# | N/A          |

| N/A                    | FPGA_VBATT    | 7     | 8     | FPGA_DONE     | Bank 0, R11  |

| Bank 34, R19           | JX1_SE_0      | 9     | 10    | JX1_SE_1      | Bank 34, T19 |

| Bank 34, T11           | JX1_LVDS_0_P  | 11    | 12    | JX1_LVDS_1_P  | Bank 34, T12 |

| Bank 34, T10           | JX1_LVDS_0_N  | 13    | 14    | JX1_LVDS_1_N  | Bank 34, U12 |

| N/A                    | GND           | 15    | 16    | GND           | N/A          |

| Bank 34, U13           | JX1_LVDS_2_P  | 17    | 18    | JX1_LVDS_3_P  | Bank 34, V12 |

| Bank 34, V13           | JX1_LVDS_2_N  | 19    | 20    | JX1_LVDS_3_N  | Bank 34, W13 |

| N/A                    | GND           | 21    | 22    | GND           | N/A          |

| Bank 34, T14           | JX1_LVDS_4_P  | 23    | 24    | JX1_LVDS_5_P  | Bank 34, P14 |

| Bank 34, T15           | JX1_LVDS_4_N  | 25    | 26    | JX1_LVDS_5_N  | Bank 34, R14 |

| N/A                    | GND           | 27    | 28    | GND           | N/A          |

| Bank 34, Y16           | JX1_LVDS_6_P  | 29    | 30    | JX1_LVDS_7_P  | Bank 34, W14 |

| Bank 34, Y17           | JX1_LVDS_6_N  | 31    | 32    | JX1_LVDS_7_N  | Bank 34, Y14 |

| N/A                    | GND           | 33    | 34    | GND           | N/A          |

| Bank 34, T16           | JX1_LVDS_8_P  | 35    | 36    | JX1_LVDS_9_P  | Bank 34, V15 |

| Bank 34, U17           | JX1_LVDS_8_N  | 37    | 38    | JX1_LVDS_9_N  | Bank 34, W15 |

| N/A                    | GND           | 39    | 40    | GND           | N/A          |

| Bank 34, U14           | JX1_LVDS_10_P | 41    | 42    | JX1_LVDS_11_P | Bank 34, U18 |

| Bank 34, U15           | JX1_LVDS_10_N | 43    | 44    | JX1_LVDS_11_N | Bank 34, U19 |

| N/A                    | GND           | 45    | 46    | GND           | N/A          |

| Bank 34, N18           | JX1_LVDS_12_P | 47    | 48    | JX1_LVDS_13_P | Bank 34, N20 |

| Bank 34, P19           | JX1_LVDS_12_N | 49    | 50    | JX1_LVDS_13_N | Bank 34, P20 |

| N/A                    | GND           | 51    | 52    | GND           | N/A          |

| Bank 34, T20           | JX1_LVDS_14_P | 53    | 54    | JX1_LVDS_15_P | Bank 34, V20 |

| Bank 34, U20           | JX1_LVDS_14_N | 55    | 56    | JX1_LVDS_15_N | Bank 34, W20 |

| N/A                    | VIN_HDR       | 57    | 58    | VIN_HDR       | N/A          |

| N/A                    | VIN_HDR       | 59    | 60    | VIN_HDR       | N/A          |

| Bank 34, Y18           | JX1_LVDS_16_P | 61    | 62    | JX1_LVDS_17_P | Bank 34, V16 |

| Bank 34, Y19           | JX1_LVDS_16_N | 63    | 64    | JX1_LVDS_17_N | Bank 34, W16 |

| N/A                    | GND           | 65    | 66    | GND           | N/A          |

| Bank 34, R16           | JX1_LVDS_18_P | 67    | 68    | JX1_LVDS_19_P | Bank 34, T17 |

| Bank 34,R17            | JX1_LVDS_18_N | 69    | 70    | JX1_LVDS_19_N | Bank 34, R18 |

| N/A                    | GND           | 71    | 72    | GND           | N/A          |

| Bank 34, V17           | JX1_LVDS_20_P | 73    | 74    | JX1_LVDS_21_P | Bank 34, W18 |

| Bank 34, V18           | JX1_LVDS_20_N | 75    | 76    | JX1_LVDS_21_N | Bank 34, W19 |

| N/A                    | GND           | 77    | 78    | VCCO_34       | N/A          |

|                        |               |       |       |               |              |

Page 24

| Bank 34, N17 | JX1_LVDS_22_P   | 81 | 82  | JX1_LVDS_23_P   | Bank 34, P15 |

|--------------|-----------------|----|-----|-----------------|--------------|

| Bank 34, P18 | JX1_LVDS_22_N   | 83 | 84  | JX1_LVDS_23_N   | Bank 34, P16 |

| N/A          | GND             | 85 | 86  | GND             | N/A          |

| Bank 13, U7  | BANK13_LVDS_0_P | 87 | 88  | BANK13_LVDS_1_P | Bank 13, T9  |

| Bank 13, V7  | BANK13_LVDS_0_N | 89 | 90  | BANK13_LVDS_1_N | Bank 13, U10 |

| Bank 13, V8  | BANK13_LVDS_2_P | 91 | 92  | BANK13_LVDS_3_P | Bank 13, T5  |

| Bank 13, W8  | BANK13_LVDS_2_N | 93 | 94  | BANK13_LVDS_3_N | Bank 13, U5  |

| N/A          | GND             | 95 | 96  | GND             | N/A          |

| Bank 0, L10  | VP_0_P          | 97 | 98  | DXP_0_P         | Bank 0, M9   |

| Bank 0, K9   | VN_0_N          | 99 | 100 | DXN_0_N         | Bank 0, M10  |

Table 15 – JX2 Connections

| Table 15 – JA2 Connections |               |             |             |               |              |  |  |

|----------------------------|---------------|-------------|-------------|---------------|--------------|--|--|

| SoC Pin#                   | MicroZed Net  | JX2<br>Pin# | JX2<br>Pin# | MicroZed Net  | SoC Pin #    |  |  |

| Bank 500, E8               | PMOD_D0       | 1           | 2           | PMOD_D1       | Bank 500, E9 |  |  |

| Bank 500, C6               | PMOD_D2       | 3           | 4           | PMOD_D3       | Bank 500, D9 |  |  |

| Bank 500, E6               | PMOD_D4       | 5           | 6           | PMOD_D5       | Bank 500, B5 |  |  |

| Bank 500, C5               | PMOD_D6       | 7           | 8           | PMOD_D7       | Bank 500, C8 |  |  |

| Bank 0, R10                | INIT#         | 9           | 10          | VCCIO_EN      | N/A          |  |  |

| Bank 500, C7               | PG_MODULE     | 11          | 12          | VIN_HDR       | N/A          |  |  |

| Bank 35, G14               | JX2_SE_0      | 13          | 14          | JX2_SE_1      | Bank 35, J15 |  |  |

| N/A                        | GND           | 15          | 16          | GND           | N/A          |  |  |

| Bank 35, C20               | JX2_LVDS_0_P  | 17          | 18          | JX2_LVDS_1_P  | Bank 35, B19 |  |  |

| Bank 35, B20               | JX2_LVDS_0_N  | 19          | 20          | JX2_LVDS_1_N  | Bank 35, A20 |  |  |

| N/A                        | GND           | 21          | 22          | GND           | N/A          |  |  |

| Bank 35, E17               | JX2_LVDS_2_P  | 23          | 24          | JX2_LVDS_3_P  | Bank 35, D19 |  |  |

| Bank 35, D18               | JX2_LVDS_2_N  | 25          | 26          | JX2_LVDS_3_N  | Bank 35, D20 |  |  |

| N/A                        | GND           | 27          | 28          | GND           | N/A          |  |  |

| Bank 35, E18               | JX2_LVDS_4_P  | 29          | 30          | JX2_LVDS_5_P  | Bank 35, F16 |  |  |

| Bank 35, E19               | JX2_LVDS_4_N  | 31          | 32          | JX2_LVDS_5_N  | Bank 35, F17 |  |  |

| N/A                        | GND           | 33          | 34          | GND           | N/A          |  |  |

| Bank 35, L19               | JX2_LVDS_6_P  | 35          | 36          | JX2_LVDS_7_P  | Bank 35, M19 |  |  |

| Bank 35, L20               | JX2_LVDS_6_N  | 37          | 38          | JX2_LVDS_7_N  | Bank 35, M20 |  |  |

| N/A                        | GND           | 39          | 40          | GND           | N/A          |  |  |

| Bank 35, M17               | JX2_LVDS_8_P  | 41          | 42          | JX2_LVDS_9_P  | Bank 35, K19 |  |  |

| Bank 35, M18               | JX2_LVDS_8_N  | 43          | 44          | JX2_LVDS_9_N  | Bank 35, J19 |  |  |

| N/A                        | GND           | 45          | 46          | GND           | N/A          |  |  |

| Bank 35, L16               | JX2_LVDS_10_P | 47          | 48          | JX2_LVDS_11_P | Bank 35, K17 |  |  |

| Bank 35, L17               | JX2_LVDS_10_N | 49          | 50          | JX2_LVDS_11_N | Bank 35, K18 |  |  |

| N/A                        | GND           | 51          | 52          | GND           | N/A          |  |  |

| Bank 35, H16               | JX2_LVDS_12_P | 53          | 54          | JX2_LVDS_13_P | Bank 35, J18 |  |  |

| Bank 35, H17               | JX2_LVDS_12_N | 55          | 56          | JX2_LVDS_13_N | Bank 35, H18 |  |  |

| N/A          | VIN_HDR         | 57 | 58  | VIN_HDR         | N/A          |

|--------------|-----------------|----|-----|-----------------|--------------|

| N/A          | VIN_HDR         | 59 | 60  | VIN_HDR         | N/A          |

| Bank 35, G17 | JX2_LVDS_14_P   | 61 | 62  | JX2_LVDS_15_P   | Bank 35, F19 |

| Bank 35, G18 | JX2_LVDS_14_N   | 63 | 64  | JX2_LVDS_15_N   | Bank 35, F20 |

| N/A          | GND             | 65 | 66  | GND             | N/A          |

| Bank 35, G19 | JX2_LVDS_16_P   | 67 | 68  | JX2_LVDS_17_P   | Bank 35, J20 |

| Bank 35, G20 | JX2_LVDS_16_N   | 69 | 70  | JX2_LVDS_17_N   | Bank 35, H20 |

| N/A          | GND             | 71 | 72  | GND             | N/A          |

| Bank 35, K14 | JX2_LVDS_18_P   | 73 | 74  | JX2_LVDS_19_P   | Bank 35, H15 |

| Bank 35, J14 | JX2_LVDS_18_N   | 75 | 76  | JX2_LVDS_19_N   | Bank 35, G15 |

| N/A          | GND             | 77 | 78  | VCCO_35         | N/A          |

| N/A          | VCCO_35         | 79 | 80  | VCCO_35         | N/A          |

| Bank 35, N15 | JX2_LVDS_20_P   | 81 | 82  | JX2_LVDS_21_P   | Bank 35,L14  |

| Bank 35, N16 | JX2_LVDS_20_N   | 83 | 84  | JX2_LVDS_21_N   | Bank 35,L15  |

| N/A          | GND             | 85 | 86  | GND             | N/A          |

| Bank 35, M14 | JX2_LVDS_22_P   | 87 | 88  | JX2_LVDS_23_P   | Bank 35, K16 |

| Bank 35, M15 | JX2_LVDS_22_N   | 89 | 90  | JX2_LVDS_23_N   | Bank 35, J16 |

| N/A          | GND             | 91 | 92  | GND             | N/A          |

| Bank 13, Y12 | BANK13_LVDS_4_P | 93 | 94  | BANK13_LVDS_5_P | Bank 13, V11 |

| Bank 13, Y13 | BANK13_LVDS_4_N | 95 | 96  | BANK13_LVDS_5_N | Bank 13, V10 |

| Bank 13, V6  | BANK13_LVDS_6_P | 97 | 98  | VCCO_13         | N/A          |

| Bank 13, W6  | BANK13_LVDS_6_N | 99 | 100 | BANK13_SE_0     | Bank 13, V5  |

$<sup>^{\</sup>star\star}$  Pmod\_JZ has only 7 connections thus cannot connect to QSPI or SD interfaces.

# 2.9 Configuration Modes

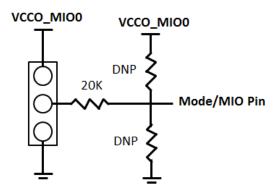

Zynq-7000 AP SoC devices use a multi-stage boot process that supports both non-secure and secure boot. The PS is the master of the boot and configuration process. Upon reset, the device mode pins are read to determine the primary boot device to be used: NOR, NAND, Quad-SPI, SD Card or JTAG. MicroZed allows 3 of those boot devices: QSPI is the default, while SD Card and JTAG boot are easily accessible by changing jumpers. The Cost-Optimized MicroZed removes the jumpers and replaces with resistors (described below) which default to QSPI boot mode.

Additionally, Zynq has Voltage Mode pins, which are fixed on MicroZed

The boot mode pins are shared with MIO[8:2]. The usage of these mode pins can be and are used as follows:

- MIO[2] / Boot\_Mode[3]

- sets the JTAG mode

- MIO[5:3] / Boot\_Mode[2:0]

- select the boot mode

- Boot\_Mode[1] is fixed since it is only required for NOR boot, which is not supported on MicroZed

- MIO[6] / Boot\_Mode[4]

- enables the internal PLL

- fixed to 'enabled' on MicroZed

- MIO[8:7] / Vmode[1:0]

- configures the I/O bank voltages

- fixed on MicroZed

- MIO Bank 0 / 500 (MIO[7] / Vmode[0]) set to '0' for 3.3V

- MIO Bank 1 / 501 (MIO[8] / Vmode[1]) set to '1' for 1.8V

All mode pins have resistor footprints such that any could be pulled either high or low through a 20 K $\Omega$  resistor if a designer chooses to experiment. By default, four mode signals are not jumper-adjustable and are populated as follows:

- MIO[3] / Boot Mode[1] is pulled low via 20 KΩ resistor.

- MIO[6] / Boot\_Mode[4] is pulled low via 20 KΩ resistor.

- MIO[7] / Vmode[0] is pulled low via 20 KΩ resistor.

- MIO[8] / Vmode[1] is pulled high via 20 K $\Omega$  resistor.

For the Evaluation Kit and the standard SOM, the other three mode signals do not populate either resistor. Instead MicroZed provides jumpers for MIO[2], MIO[4] and MIO[5].

For production, you should consider switching over to the Cost-Optimized MicroZed, where the jumpers have been replaced with the appropriate resistor population options fix the boot mode permanently to QSPI. For a custom population of the resistors for SD Card boot, please contact customize@avnet.com.

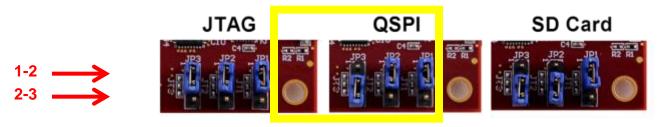

The specific resistors installed are 0-ohm CRCW04020000Z0ED at the following positions:

| <b>Boot Mode</b> | JT1       | JT2       | JT3        |

|------------------|-----------|-----------|------------|

| Cascaded JTAG    | 1-2 (low) | x         | х          |

| QSPI             | Х         | 1-2 (low) | 2-3 (high) |

If a user wishes to hand-modify (at your own risk) a cost-optimized SOM to SD Card mode, move the JT2 resistor to the 2-3 set of pads.

A diagram for the three mode signals is shown below, with the pull-up option tied to Vcco for MIO Bank 0.

Figure 7 - Configuration Mode Jumpers

The 1x3 jumper options with default positions highlighted are shown below. The default position is Cascaded JTAG Chain, QSPI Boot. Defaults highlighted in yellow below.

**Table 16 - MicroZed Configuration Modes**

|                        | JP3          | JP2          | JP1          |

|------------------------|--------------|--------------|--------------|

| Xilinx TRM→            | Boot_Mode[0] | Boot_Mode[2] | Boot_Mode[3] |

| MIO→                   | MIO[5]       | MIO[4]       | MIO[2]       |

| JTAG Mode              |              |              |              |

| Cascaded JTAG Chain    |              |              | 1-2 (0)      |

| Independent JTAG Chain |              |              | 2-3 (1)      |

| Boot Devices           |              |              |              |

| JTAG                   | 1-2 (0)      | 1-2 (0)      |              |

| Quad-SPI               | 2-3 (1)      | 1-2 (0)      |              |

| SD Card                | 2-3 (1)      | 2-3 (1)      |              |

Figure 8 – Boot Mode Jumper Settings with Cascaded JTAG Chain

Expected configuration time using a 50MB/s QSPI flash is 250ms.

Zyng has many other configuration options, MicroZed uses this configuration:

- V<sub>CCO\_0</sub> is tied to 3.3V on MicroZed.

- PUDC\_B can be pulled high or low on MicroZed via a resistor (JT4). This active-low input enables internal pull-ups during configuration on all SelectIO pins. By default, JT4 is populated with a 1K resistor in the 1-2 position, which pulls up PUDC\_B and disables the pull-ups during configuration. PUDC\_B is shared with Bank 34 I/O IO\_L3P and is connected to the MicroHeader.

- Init\_B is pulled high via a 4.7KΩ resistor (RP2.2-7), but also connected to the MicroHeader.

- Program\_B is pulled high via a 4.7KΩ resistor (RP2.4-5).

- CFGBVS is pulled high via a 4.7KΩ resistor (RP2.1-8).

The PS is responsible for reconfiguring the PL. Zynq will not automatically reconfigure the PL as in standard FPGAs by toggling PROG. Likewise, it is not possible to hold off Zynq boot up with INIT\_B as this is now done with POR. If the application needs to reconfigure the PL, the software design must do this, or you can toggle POR to restart everything. When PL configuration is complete, a blue LED, D2, will light.

# 2.9.1 JTAG

MicroZed requires an external JTAG cable for JTAG operations. MicroZed is designed with the Platform Cable JTAG connector, Molex 87832-1420 which is a 2.0mm 2x7 shrouded, polarized header. On MicroZed, this is J3 and is compatible with Xilinx Platform Cables and Digilent JTAG HS1 or HS2 Programming Cables. The JTAG Reset signal is connected to PS\_SRST\_B through an open-drain buffer.

# 2.10 Power

# 2.10.1 Primary Power Input

MicroZed is designed to be used either as a Standalone evaluation kit or as a SOM connected to a Carrier Card. Supporting these multiple use cases required the board to be designed with multiple power input sources.

The board's default primary input in standalone mode is through the USB-UART connector, J2. Alternatively, a DC barrel jack footprint is provided that is compatible with CUI PJ-002B-SMT. This allows you to power MicroZed from a compatible AC/DC 5V converter with 2.5mm inner diameter, 5.5mm outer diameter, center positive connection.

One such compatible AC/DC supply from Emerson Network Power is:

- DA12-050MP-M requires addition of plug

- Plugs

- DA-US

- DA-UK

- DA-EU

- DA-AU

- DA-ALL

Additionally, in SOM mode, MicroZed is powered by a carrier card via the MicroHeader.

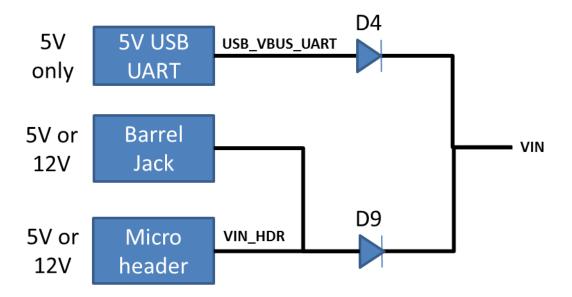

Figure 9 – Power Input Options (12V Vin not supported without modifications)

As shown in Figure 9, protection diodes were put in place to prevent one supply from back-powering another one. These diodes are Diodes Inc. B330A-13-F. It is expected that the voltage will drop ~0.5V over these diodes. At 4.5V for Vin, all regulators will continue to regulate properly.

When used as a production SOM, it is recommended that D4 be de-populated and D9 be replaced with a shunt. This is not done on the standard SOMs, but this is the case for the cost-optimized SOMs.

When powering from the USB-UART, be aware that the USB specification allows a maximum of 500mA for USB 2.0. With only 2.5W of power, the MicroZed will be able to operate in the default, out-of-box mode. During testing, the measured current of the MicroZed was 300-400mA while running a PS-only application exercising one cpu and RAM at maximum speeds. If you want to fill the PL fabric with logic, get more power on the PS Pmod or get more power on the USB-host Vbus, several options exist for standalone operation:

- Use a PC USB port that is capable of sourcing more than 500mA (or won't alert about supplying more than 500mA).

- Use a USB Y-Cable that connects to 2 ports on the PC for power. This will provide at a minimum twice the current capacity to the board (1.0 Amperes if following the USB specification, more if the PC port is not following the specification).

- Populate J4 barrel jack and use a 5V AC/DC supply rated for the projected current demand AND install the capacitors C212, C217, and C218.

- \* Please note Vcco 13, 34 and 35 will NOT be powered in the above MicroZed standalone power modes. These banks are only powered when a suitable I/O Carrier Card is used.

- Use an I/O Carrier Card, either from Avnet or one designed in-house. The Avnet Carrier Cards (IOCC, FMC) provide power to banks 13, 34 and 35.

If you intend to plug in a USB device to the USB-Host port while powered from USB-UART, it is recommended that this be a low-power device or a powered USB hub.

# 2.10.2 Using 12V for Vin

As seen in Figure 9, MicroZed was designed with a component population option for Vin to be sourced from 12V. THIS IS NOT THE DEFAULT CONFIGURATION! Modifications are required for this to work and not damage the board and plugged in USB peripherals.

When 5V is used for Vin, the input 5V is passed directly to the USB Host connector to provide to plugged in USB devices. When Vin is 12V, an additional circuit is required to regulate 5V for use by USB devices. This circuit is shown on Sheet 5 of the schematics with regulator U18.

### Changes required for all revisions:

Remove R50

### Changes required for revisions prior to F-06. Replace existing components with the following:

| # | Quantity | Designator                        | Description                    | MFG            | MFGPN               |

|---|----------|-----------------------------------|--------------------------------|----------------|---------------------|

| 1 | 5        | C67, C206,<br>C208, C214,<br>C216 | CAP SM 0.1uF 16V 10% X5R C0201 | TDK            | C0603X5R1C104K030BC |

| 2 | 4        | C209, C210,<br>C213, C215         | Cap, 2.2uF, 16V, 0402          | TAIYO<br>YUDEN | EMK105ABJ225MV-F    |

| 3 | 4        | C50, C62,<br>C207, C211           | CAP SM 100uF 16V 1210          | TAIYO<br>YUDEN | EMK325ABJ107MM-T    |

# OPTIONAL changes required for all revisions if 5V sourcing to USB Host port is required:

| # | Quantity | Designator | Description                                | MFG        | MFGPN              |

|---|----------|------------|--------------------------------------------|------------|--------------------|

| 1 | 1        | C65        | CAP SM 0.0033uF 25V 5% X7R C0402           | AVX        | 04023C332JAT2A     |

| 2 | 1        | C66        | CAP SM 10uF 25V 10% X5R C1206              | AVX        | 12063D106KAT2A     |

| 3 | 1        | C69        | CAP SM 22uF 10V 20% X5R C0805              | MURATA     | GRM219R61A226MEA0D |

| 4 | 1        | L10        | IND SM 1uH 2.35A DCR=48mOhm                | BOURN<br>S | SRN3015-1R0Y       |

| 5 | 1        | R48        | RES SM 1.78K 62mW 0.01 R0402               | VISHAY     | CRCW04021K78FKED   |

| 6 | 1        | R49        | RES SM 9.53K 62mW 0.01 R0402               | VISHAY     | CRCW04029K53FKED   |

| 7 | 1        | R52        | RES SM 100K 62mW 0.01 R0402                | VISHAY     | CRCW0402100KFKED   |

| 8 | 1        | R53        | RES SM 100K 62mW 0.01 R0402                | VISHAY     | CRCW0402100KFKED   |

| 9 | 1        | U18        | Step Down Switcher, 1A, 3V-17V, Adjustable | TI         | TLV62150RGT        |

# 2.10.3 Regulators

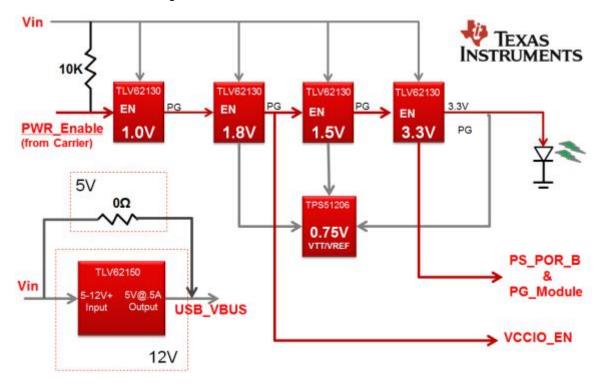

The following power solution provides the power rails of the MicroZed. Sequencing of the supplies is implemented by cascading the POWER GOOD outputs of each supply to the ENABLE input for the next supply in the sequence. 3.3V is the last supply to come up, therefore the PG for the 3.3V supply is used to drive the PG\_MODULE net and is used as the power-on reset control for Zynq(U9.pinC7), Ethernet PHY (U3.pin16), USB-Host PHY (U4.pin27) and USB\_UART (U2.pin9).

This net is also connected to the MicroHeaders so power supplies on the carrier card can also control this signal.

Figure 10 – Regulation Circuitry (VCCIO\_EN specific to Rev C)

This circuit sequences power-up of MicroZed. 1.0V comes up first, then 1.8V, then 1.5V and then 3.3V. When 3.3V is valid in standalone mode, the Power Good (Module) LED, D5, is illuminated. PG\_MODULE is connected to PS\_POR\_B on Zynq, thus when the power supplies are valid, PS\_POR\_B is released.

When plugged into a carrier card, the power good outputs of the carrier card should also be tied to the PG\_MODULE net on JX2.pin11. If the carrier card power supplies do not have power good outputs, a voltage supervisor or open-drain buffer should be used to complement this circuit.

MicroZed also provides an Enable signal to the Carrier Card to signal that Vccint and Vccaux are both up and the Carrier is free to bring up the Vcco supplies. This signal is called VCCIO\_EN and is tied to JX2.pin10.

- Rev B

- VCCIO\_EN is provided by 3.3V pull-up RP2.4-5, which is also used for PROGRAM#

- Rev C

- VCCIO\_EN is provided by the power good output of the 1.8V regulator.

The table below shows the minimum required voltage rails, currents, and tolerances.

Table 17 – Voltage Rails w/ Current Estimates

| Voltage (V)           | 7010<br>Current (A) | 7020<br>Current (A) | Tolerance | TI Part Number     |

|-----------------------|---------------------|---------------------|-----------|--------------------|

| 1.0 (Vccint)          | 1.0                 | 1.9                 | 5.00%     | TLV62130           |

| 1.5 (Vccoddr)         | 1.0                 | 1.0                 | 5.00%     | TLV62130           |

| 1.8 (Vccaux)          | 0.8                 | 0.9                 | 5.00%     | TLV62130           |

| 3.3 (Vcco/Pmod)       | 0.7                 | 0.7                 | 5.00%     | TLV62150           |

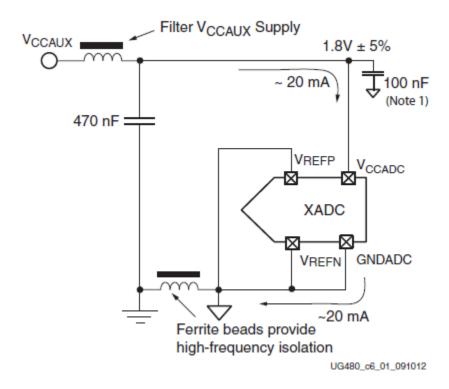

| 1.8 (analog) (Vccadc) | 0.15                | 0.15                | 5.00%     | Filtered from 1.8V |

| 0.75 (DDR3 Vtt)       | 0.400               | 0.400               | 5.00%     | TPS51206           |

| 5.0 (USB-Host Vbus)*  | 0.5                 | 0.5                 | 5.00%     | TLV62150           |

<sup>\*</sup> Not populated by default

# 2.10.4 Sequencing

When attached to a carrier card, the carrier card must provide an active-high, power enable signal, PWR\_ENABLE. This controls the first MicroZed regulator (U17, 1.0V) turning on. This should be an open drain design such that when MicroZed is in standalone mode, this signal will float high (pulled high to 5V on MicroZed via R87). This allows for the carrier card to control powering MicroZed. Thus it can be powered down in low power applications.

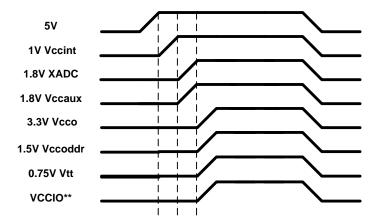

Sequencing for the power supplies follows the recommendations for the Zynq device. PS and PL INT and AUX supplies are tied together on the MicroZed platform to create a low cost design. The following diagram illustrates the supply sequencing:

<sup>\*\*</sup> VCCIO driven from carrier card.

Figure 11 - Power Sequencing

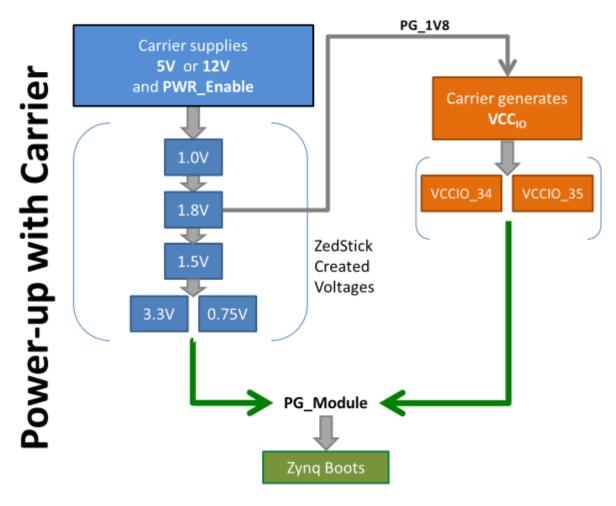

As noted above, if connected to a carrier card, the 1.8V power supply's power good output should be used to enable the VCCIO regulators.

The following diagram illustrates sequencing with a carrier card:

Figure 12 – Power Sequencing with Carrier Card

# 2.10.5 Bypassing/Decoupling

The MicroZed design follows the PCB decoupling strategy as outlined in UG933 for the 7Z020, CLG400 package. The 7Z010 MicroZed depopulates a few of these capacitors while maintaining the listed 7Z010 requirements.

|         |        |           | V <sub>CCINT</sub> |   |   | V <sub>CCBRAM</sub> |           |   | V <sub>CCAUX</sub> |   | V <sub>CCAUX_IO</sub> |   |            | V <sub>CCO</sub> per Bank |           |            | Bank 0    |           |            |          |

|---------|--------|-----------|--------------------|---|---|---------------------|-----------|---|--------------------|---|-----------------------|---|------------|---------------------------|-----------|------------|-----------|-----------|------------|----------|

| Package | Device | 680<br>μF | 330<br>μF          |   |   |                     | 100<br>μF |   |                    |   |                       |   | 0.47<br>μF | 47<br>μF                  | 4.7<br>μF | 0.47<br>μF | 100<br>μF | 4.7<br>μF | 0.47<br>μF | 47<br>μF |

| CLG400  | 7Z010  | 0         | 0                  | 1 | 2 | 3                   | 0         | 1 | 1                  | 2 | 1                     | 1 | 2          | NA                        | NA        | NA         | 1         | 3         | 5          | 1        |

| CLG400  | 7Z020  | 0         | 1                  | 0 | 5 | 7                   | 1         | 0 | 2                  | 3 | 1                     | 1 | 2          | NA                        | NA        | NA         | 1         | 3         | 5          | 1        |

Figure 13 - CLG400 PL Decoupling

|         |        | V <sub>CCPINT</sub> |           |            | V <sub>CCPAUX</sub> <sup>(2)</sup> |           |            | V <sub>CCO_DDR</sub> |           | V <sub>CCO_MIO0</sub> |           |           | V <sub>CCO_MIO1</sub> |           |           | V <sub>CCPLL</sub> <sup>(1)(3)</sup> |          |            |

|---------|--------|---------------------|-----------|------------|------------------------------------|-----------|------------|----------------------|-----------|-----------------------|-----------|-----------|-----------------------|-----------|-----------|--------------------------------------|----------|------------|

| Package | Device | 100<br>μF           | 4.7<br>μF | 0.47<br>μF | 100<br>μF                          | 4.7<br>μF | 0.47<br>μF | 100<br>μF            | 4.7<br>μF | 0.47<br>μF            | 100<br>μF | 4.7<br>μF | 0.47<br>μF            | 100<br>μF | 4.7<br>μF | 0.47<br>μF                           | 10<br>μF | 0.47<br>μF |

| CLG400  | 7Z010  | 1                   | 3         | 5          | 1                                  | 2         | 3          | 2                    | 3         | 7                     | 1         | 1         | 2                     | 1         | 2         | 3                                    | 1        | 1          |

| CLG400  | 7Z020  | 1                   | 3         | 5          | 1                                  | 2         | 3          | 2                    | 3         | 7                     | 1         | 1         | 2                     | 1         | 2         | 3                                    | 1        | 1          |

Figure 14 - CLG400 PS Decoupling

### 2.10.6 Power Good LED

A green status LED, D5, illuminates with the U16 3.3V power rail. Since this regulator is the last one in the sequence to come up, it is an effective indication that all regulators are on.

# 2.10.7 Power Estimation

The total input power budget for the 7010 MicroZed consists of two components. The first is the power required for the module components. The calculation for the 7010 MicroZed is 4.8W for the circuits themselves, including the PL fabric utilized to 85% capacity and the PS Pmod consuming 100mA. See Table 16. To be conservative, the regulation efficiency is assumed to be 80%, although we expect it is much better than that. With a 5V input supply, this results in 1.2A (4.8W / 80% / 5V).

Table 18 – Current Usage Calculation for 7010 MicroZed