# **NXP** Communicator

## P3A9606JK

Dual bidirectional I3C/I2C-bus and SPI voltage-level translator

Communicator Finalization Date: Jul 2021

Communicator Created: May 2021

Global Full Market Launch Date: Jul 2021

## P3A9606 Product Summary

The P3A9606JK is a 2-bit, dual supply translating transceiver with auto direction sensing, that enables bidirectional voltage level translation for traditional open drain l<sup>2</sup>C-bus/SMBus applications, combination open drain and push pull 12.5 MHz I3C-bus applications or push pull SPI applications (with two devices).

Both  $V_{CC}(A)$  and  $V_{CC}(B)$  can be supplied at any voltage between 0.72 V and 1.98 V making the device suitable for translating between any of the low voltage nodes (0.8 V, 1.2 V and 1.8 V).

It features two 1-bit input-output ports (An and Bn) controlled by one output enable input (OE).

### **Block Diagrams**

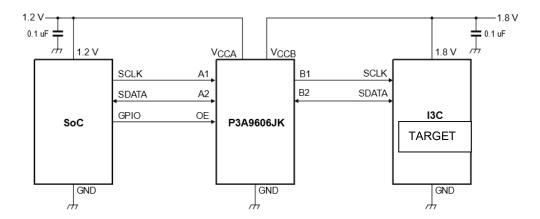

### **I3C** bus level translation

### I<sup>2</sup>C-bus level translation

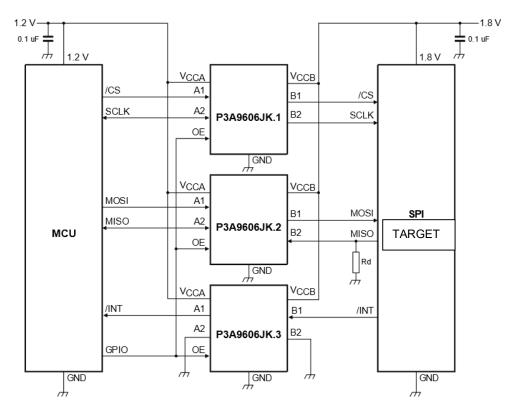

### **SPI level translation**

### P3A9606 Features

- Wide supply voltage range:

- o V<sub>CC</sub>(A): 0.72 V to 1.98 V and V<sub>CC</sub>(B): 0.72 V to 1.98 V; V<sub>CC</sub>(A) ≤ V<sub>CC</sub>(B)

- I<sub>OFF</sub> circuitry provides partial Power-down mode operation

- Inputs accept voltages up to 1.98 V and are overvoltage tolerant to 1.98 V

- Provided voltage level translation for I3C, I2C-bus, SMBus and SPI devices

- Specified from -40 °C to +85 °C and -40 °C to +125 °C

- · ESD protection:

- o HBM JESD22-A114E Class 2 exceeds 2000 V

- CDM JESD22-C101E exceeds 1000 V

- Latch-up performance exceeds 100 mA per JESD 78B Class II

- Available in X2SON8 1.35 x 1.0 x 0.32 mm package with 0.35 mm pitch

## **Target Applications**

## **Applications**

- I3C Bus, I2C-bus and SPI level translation

- Server

- Notebooks/Tablets

- Smartphones

## Part Attributes

Table 6. Recommended operating conditions<sup>[1]</sup>

| Symbol           | Parameter                           | Conditions                                                                                              | Min  | Max  | Unit |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|

| Vcca             | supply voltage A                    | V <sub>CCA</sub> ≤ V <sub>CCB</sub>                                                                     | 0.72 | 1.98 | V    |

| V <sub>CCB</sub> | supply voltage B                    | V <sub>CCA</sub> ≤ V <sub>CCB</sub>                                                                     | 0.72 | 1.98 | V    |

| VI               | input voltage                       | A port, B port and OE                                                                                   | 0    | 1.98 | V    |

| Vo               | output voltage                      | Power-down or 3-state mode;<br>V <sub>CCA</sub> = 0.72 V to 1.98 V; V <sub>CCB</sub> = 0.72 V to 1.98 V |      |      |      |

|                  |                                     | A port                                                                                                  | 0    | 1.98 | V    |

|                  |                                     | B port                                                                                                  | 0    | 1.98 | V    |

| T <sub>amb</sub> | ambient temperature                 |                                                                                                         | -40  | +125 | °C   |

| TJ               | junction temperature <sup>[2]</sup> |                                                                                                         | -40  | +125 | °C   |

| ΔυΔν             | input transition rise and fall rate | V <sub>CCA</sub> = 0.72 V to 1.98 V; V <sub>CCB</sub> = 0.72 V to 1.98 V                                | -    | <5.3 | ns/V |

Table 7 and full specifications located in the data sheet.

<sup>[1]</sup> The A and B sides of an unused I/O pair must be held in the same state, both at V<sub>CCI</sub> or both at GND.

[2] The T<sub>J</sub> limits shall be supported by proper thermal PCB design taking the power consumption and the thermal resistance as listed in <u>Table 7</u> into account.

## Development tools and Ecosystem

The P3A9606 is supported by the evaluation board listed below

| Evaluation Board | Description                                                                                                                                                          | Image  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| P3A9606JK-EVB    | Easy to use board with mounted P3A9606JK allowing connections to I <sup>2</sup> C, I3C or SPI controllers or targets for voltage translation between 0.72 V to 1.98V | PSAVOO |

## **Export Compliance**

NXP Semiconductors, makes product Export Control Classification Number (ECCN) and Harmonized Tariff Schedule (HTS) classifications available for informational purposes only and the classifications are subject to change without notice. Anyone importing or exporting/re-exporting an NXP item is solely responsible for assuring the ECCN and HTS they use is correct. Further, NXP does not provide guidance regarding the exportability of its products, software or technology. Such questions should be directed to the exporter's internal Trade Compliance organization or legal counsel.

The extended ECCN for our 5A002 devices is both a.1.a and a.1.b since we have both symmetric and asymmetric algorithms in all of our encrypted products.

Details provided in the stocking excel file. Available at https://nxp.com/Distynet

| PN                              | MSL | coo      | ECCN  | US HTS | CCATS# |

|---------------------------------|-----|----------|-------|--------|--------|

| P3A9606JKZ<br>9354 258 46431    | 1   | Thailand | -     | 854239 | NA     |

| P3A9606JK-EVB<br>935 427 961598 | NA  | China    | EAR99 | 847330 | NA     |

### **Available Documentation**

Include direct links to high value assets as well as links to NXP.com, disty extranet and channel launch repository.

Distributor extranet:

DistyNet | NXP Semiconductors

NXP.com:

www.nxp.com/P3A9606

Datasheet

P3A9606JK

Evaluation board

Tool Part Description

P3A9606JK-EVB Dual bidirectional I3C/I2C-bus and SPI voltage-level

translator

<sup>\*</sup>Please note that the Channel Launch Repository is for marketing assets like high res block diagram and board photography. This same information is also posted to the "product" launch folder on the distributor extranet for others outside of marketing who may need it.

### How to Reach Us

### Home Page:

www.nxp.com

#### Web Support:

www.nxp.com/support

#### **USA/Europe or Locations Not Listed:**

NXP Semiconductors Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.nxp.com/support

### Europe, Middle East and Africa:

NXP Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.nxp.com/support

#### Japan:

NXP Semiconductors Japan Ltd.. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 +81 3 5437 9125 support.japan@nxp.com

### Asia/Pacific:

NXP Semiconductors Hong Kong Ltd Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@nxp.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright license granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

NXP Semiconductors reserves the right to make changes without further notice to any products herein. NXP Semiconductors makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP Semiconductors assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in NXP Semiconductors data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. NXP Semiconductors does not convey any license under its patent rights nor the rights of others. NXP Semiconductors products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP Semiconductors product could create a situation where personal injury or death may occur. Should Buyer purchase or use NXP Semiconductors products for any such unintended or unauthorized application, Buyer shall indemnify and hold NXP Semiconductors and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that NXP Semiconductors was negligent regarding the design or manufacture of the part.