# Product Change Notification / SYST-04SBWB795

Date:

06-Oct-2021

# **Product Category:**

8-bit Microcontrollers

# **PCN Type:**

**Document Change**

# **Notification Subject:**

ERRATA - ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification

# **Affected CPNs:**

SYST-04SBWB795\_Affected\_CPN\_10062021.pdf SYST-04SBWB795\_Affected\_CPN\_10062021.csv

# **Notification Text:**

SYST-04SBWB795

Microchip has released a new Product Documents for the ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification.

**Notification Status: Final**

# **Description of Change:** • Added erratum:

- TCD: 2.9.4 Halting TCD and Wait for SW Restart Does Not Work if Compare Value A is '0' or Dual Slope Mode is Used

- Added data sheet clarifications:

- Memories: 3.1.1 Fuses Factory Default Values

- SLPCTRL: 3.2.1 Sleep Mode Activity Overview

- USART: 3.3.1 TXDATA Buffer

- Updated erratum:

- TWI: 2.10.1 TIMEOUT Bits in the TWI.MCTRLA Register are Not Accessible

- Removed invalid erratum:

- Start-of-Frame Detection Can Unintentionally Be Triggered in Active Mode

- Editorial updates

Impacts to Data Sheet: None

**Reason for Change:** To Improve Productivity

**Change Implementation Status:** Complete

**Date Document Changes Effective:** 6 Oct 2021

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

# **Attachments:**

ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification

Please contact your local Microchip sales office with questions or concerns regarding this notification.

# **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

# Affected Catalog Part Numbers (CPN)

ATTINY1614-SSB-VAO

ATTINY1614-SSBT-VAO

ATTINY1614-SSF

ATTINY1614-SSFR

ATTINY1614-SSN

ATTINY1614-SSNR

ATTINY1614-SSZ-VAO

ATTINY1614-SSZT-VAO

ATTINY1616-MB-VAO

ATTINY1616-MBT-V01

ATTINY1616-MBT-V03

ATTINY1616-MBT-V07

ATTINY1616-MBT-V09

ATTINY1616-MBT-V10

ATTINY1616-MBT-V11

ATTINY1616-MBT-V15

ATTINY1616-MBT-V16

ATTINY1616-MBT-VAO

ATTINY1616-MF

ATTINY1616-MFR

ATTINY1616-MN

ATTINY1616-MNR

ATTINY1616-MNRA0

ATTINY1616-MNRA1

ATTINY1616-MNRA2

ATTINY1616-MZ-VAO

ATTINY1616-MZT-V02

ATTINY1616-MZT-V04

ATTINY1616-MZT-VAO

ATTINY1616-SB-VAO

ATTINY1616-SBT-VAO

ATTINY1616-SF

ATTINY1616-SFR

ATTINY1616-SN

ATTINY1616-SNR

ATTINY1616-SZ-VAO

ATTINY1616-SZT-VAO

ATTINY1617-MB-VAO

ATTINY1617-MBT-V08

ATTINY1617-MBT-VAO

ATTINY1617-MF

ATTINY1617-MFR

ATTINY1617-MN

ATTINY1617-MNR

ATTINY1617-MZ-V06

ATTINY1617-MZ-VAO

Date: Wednesday, October 06, 2021

# SYST-04SBWB795 - ERRATA - ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification ATTINY1617-MZT-V05 ATTINY1617-MZT-V06 ATTINY1617-MZT-V12 ATTINY1617-MZT-V14 ATTINY1617-MZT-VAO

# ATtiny1614/1616/1617

# Silicon Errata and Data Sheet Clarifications

The ATtiny1614/1616/1617 devices you have received conform functionally to the current device data sheet (www.microchip.com/DS40002204), except for the anomalies described in this document. The errata described in this document will likely be addressed in future revisions of the ATtiny1614/1616/1617 devices.

### Notes:

- · This document summarizes all the silicon errata issues from all the silicon revisions, previous as well as current

- Refer to the Device/Revision ID section in the current device data sheet (www.microchip.com/DS40002204) for more detailed information on Device Identification and Revision IDs for your specific device, or contact your local Microchip sales office for assistance

# 1. Silicon Issue Summary

# Legend

- Erratum is not applicable.

- **X** Erratum is applicable.

| Peripheral Short Description |                                                                                                       | Valid for Silicon Revision |        |

|------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|--------|

|                              |                                                                                                       | Rev. A                     | Rev. B |

| Device                       | 2.2.1 Writing the OSCLOCK Fuse in FUSE.OSCCFG to '1' Prevents Automatic Loading of Calibration Values | Х                          | X      |

|                              | 2.3.1 AC Interrupt Flag Not Set Unless Interrupt is Enabled                                           | X                          | X      |

| AC                           | 2.3.2 False Triggers May Occur Under Certain Conditions                                               | X                          | -      |

|                              | 2.3.3 False Triggering When Sweeping Negative Input of the AC When the Low-Power Mode is Disabled     | Х                          | -      |

|                              | 2.4.1 SAMPDLY and ASDV Does Not Work Together With SAMPLEN                                            | Χ                          | Χ      |

|                              | 2.4.2 Pending Event Stuck When Disabling the ADC                                                      | X                          | X      |

|                              | 2.4.3 ADC Functionality Cannot be Ensured with CLKADC Above 1.5 MHz and a Setting of 25% Duty Cycle   | Х                          | X      |

| ADC                          | 2.4.4 ADC Performance Degrades with CLKADC Above 1.5 MHz and VDD < 2.7V $$                            | X                          | Х      |

|                              | 2.4.5 ADC Interrupt Flags Cleared When Reading RESH                                                   | Х                          | Х      |

|                              | 2.4.6 Changing ADC Control Bits During Free-Running Mode not Working                                  | X                          | Х      |

|                              | 2.4.7 One Extra Measurement Performed After Disabling ADC Free-Running Mode                           | Х                          | Х      |

|                              | 2.4.8 ADC Wake-Up with WCMP                                                                           | X                          | Χ      |

|                              | 2.5.1 Connecting LUTs in Linked Mode Requires OUTEN Set to '1'                                        | X                          | Х      |

| CCL                          | 2.5.2 D-latch is Not Functional                                                                       | Х                          | Х      |

|                              | 2.5.3 The CCL Must be Disabled to Change the Configuration of a Single LUT                            | X                          | X      |

| RTC                          | 2.6.1 Any Write to the RTC.CTRLA Register Resets the RTC and PIT Prescaler                            | X                          | X      |

|                              | 2.6.2 Disabling the RTC Stops the PIT                                                                 | Х                          | Х      |

| TCA                          | 2.7.1 Restart Will Reset Counter Direction in NORMAL and FRQ Mode                                     | X                          | X      |

|                              | 2.8.1 Minimum Event Duration Must Exceed the Selected Clock Period                                    | X                          | X      |

|                              | 2.8.2 The TCB Interrupt Flag is Cleared When Reading CCMPH                                            | Х                          | Х      |

| тсв                          | 2.8.3 TCB Input Capture Frequency and Pulse-Width Measurement Mode Not Working with Prescaled Clock   | X                          | X      |

|                              | 2.8.4 The TCA Restart Command Does Not Force a Restart of TCB                                         | Х                          | Х      |

|                              | 2.8.5 CCMP and CNT Registers Operate as 16-Bit Registers in 8-Bit PWM Mode                            | Х                          | Х      |

# ATtiny1614/1616/1617

# Silicon Issue Summary

| continued  |                                                                                |                |              |

|------------|--------------------------------------------------------------------------------|----------------|--------------|

| Peripheral | Short Description                                                              | Valid for Sili | con Revision |

|            |                                                                                | Rev. A         | Rev. B       |

|            | 2.9.1 TCD Event Output Lines May Give False Events                             | Х              | X            |

| TCD        | 2.9.2 TCD Auto-Update Not Working                                              | Х              | -            |

|            | 2.9.3 Asynchronous Input Events Not Working When TCD Counter Prescaler is Used | X              | X            |

|            | 2.10.1 TIMEOUT Bits in the TWI.MCTRLA Register are Not Accessible              | X              | Х            |

| TWI        | 2.10.2 TWI Master Mode Wrongly Detects the Start Bit as a Stop Bit             | X              | X            |

| IVVI       | 2.10.3 TWI Smart Mode Gives Extra Clock Pulse                                  | X              | Х            |

|            | 2.10.4 The TWI Master Enable Quick Command is Not Accessible                   | X              | X            |

|            | 2.11.1 TXD Pin Override Not Released When Disabling the Transmitter            | Х              | Х            |

|            | 2.11.2 Full Range Duty Cycle Not Supported When Validating LIN Sync Field      | X              | X            |

| USART      | 2.11.3 Frame Error on a Previous Message May Cause False Start Bit Detection   | X              | X            |

|            | 2.11.4 Open-Drain Mode Does Not Work When TXD is Configured as Output          | Х              | X            |

# 2. Silicon Errata Issues

# 2.1 Errata Details

- Erratum is not applicable.

- X Erratum is applicable.

# 2.2 Device

# 2.2.1 Writing the OSCLOCK Fuse in FUSE.OSCCFG to '1' Prevents Automatic Loading of Calibration Values

Writing the OSCLOCK fuse in FUSE.OSCCFG to '1' prevents the automatic loading of calibration values from the signature row. The device will run with an uncalibrated OSC20M oscillator.

### **Work Around**

Do not use OSCLOCK for locking the oscillator calibration value. The oscillator calibration value can be locked by writing LOCK in CLKCTRL.OSC20MCALIBB to '1'.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.3 AC - Analog Comparator

# 2.3.1 AC Interrupt Flag Not Set Unless Interrupt is Enabled

ACn.STATUS.CMP is not set if the ACn.INTCTRL.CMP is not set.

### **Work Around**

Enable ACn.INTCTRL.CMP or use ACn.STATUS.STATE for polling.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

### 2.3.2 False Triggers May Occur Under Certain Conditions

False triggers may occur on falling input pin:

- If the slew rate on the input signal is greater than 2 V/µs for common-mode voltage below 0.5V

- If the slew rate on the input signal is greater than 10 V/µs for common-mode voltage above 0.5V

- If the slew rate on the input signal is greater than 10 V/µs for any common-mode voltage and Low-Power mode is enabled

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | -      |

# 2.3.3 False Triggering When Sweeping Negative Input of the AC When the Low-Power Mode is Disabled

A false trigger may occur if sweeping the negative input of the AC with a negative slope, and the AC has Low-Power mode disabled.

### **Work Around**

Enable Low-Power mode in AC.CTRLA.LPMODE.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | -      |

# 2.4 ADC - Analog-to-Digital Converter

# 2.4.1 SAMPDLY and ASDV Does Not Work Together With SAMPLEN

Using SAMPCTRL.SAMPLEN at the same time as CTRLD.SAMPDLY or CTRLD.ASDV will cause an unpredictable sampling length.

### **Work Around**

When setting SAMPCTRL.SAMPLEN greater than 0x0, the CTRLD.SAMPDLY and CTRLD.ASDV must be cleared.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.4.2 Pending Event Stuck When Disabling the ADC

If the ADC is disabled during an event-triggered conversion, the event will not be cleared.

# **Work Around**

Clear ADC.EVCTRL.STARTEI and wait for the conversion to complete before disabling the ADC.

# **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| Х      | X      |

# 2.4.3 ADC Functionality Cannot be Ensured with CLK<sub>ADC</sub> Above 1.5 MHz and a Setting of 25% Duty Cycle

The ADC functionality cannot be ensured if CLK<sub>ADC</sub> > 1.5 MHz with ADCn.CALIB.DUTYCYC set to '1'.

# **Work Around**

If ADC is operated with CLK<sub>ADC</sub> > 1.5 MHz, ADCn.CALIB.DUTYCYC must be set to '0' (50% duty cycle).

### Affected Silicon Revisions

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.4.4 ADC Performance Degrades with $CLK_{ADC}$ Above 1.5 MHz and $V_{DD}$ < 2.7V

The ADC INL performance degrades if CLK<sub>ADC</sub> > 1.5 MHz and ADCn.CALIB.DUTYCYC set to '0' for V<sub>DD</sub> < 2.7V.

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.4.5 ADC Interrupt Flags Cleared When Reading RESH

ADCn.INTFLAGS.RESRDY and ADCn.INTFLAGS.WCOMP are cleared when reading ADCn.RESH.

#### Work Around

In 8-bit mode, read ADCn.RESH to clear the flag or clear the flag directly.

### Affected Silicon Revisions

| Rev. A | Rev. B |

|--------|--------|

| Х      | Х      |

# 2.4.6 Changing ADC Control Bits During Free-Running Mode not Working

If the control signals are changed during Free-Running mode, the new configuration is not ensured in the next measurement. This is valid for the ADCn.CTRLB, ADCn.CTRLC, ADCn.SAMPCTRL, ADCn.MUXPOS, ADCn.WINLT or ADCn.WINHT registers.

### **Work Around**

Disable ADC Free-Running mode before updating the ADCn.CTRLB, ADCn.CTRLC, ADCn.SAMPCTRL, ADCn.MUXPOS, ADCn.WINLT or ADCn.WINHT registers.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.4.7 One Extra Measurement Performed After Disabling ADC Free-Running Mode

The ADC may perform one additional measurement after clearing ADCn.CTRLA.FREERUN.

### **Work Around**

Write ADCn.CTRLA.ENABLE to '0' to stop the Free-Running mode immediately.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.4.8 ADC Wake-Up with WCMP

When waking up from Standby sleep mode with ADC WCMP interrupt, the ADC is disabled for a few cycles before the device enters Active mode. A new INITDLY is required before the next conversion.

#### **Work Around**

Use INITDLY before the next conversion.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.5 CCL - Configurable Custom Logic

# 2.5.1 Connecting LUTs in Linked Mode Requires OUTEN Set to '1'

Connecting the LUTs in linked mode requires LUTnCTRLA.OUTEN set to '1' for the LUT providing the input source.

#### **Work Around**

Use an event channel to link the LUTs, or do not use the corresponding I/O pin for other purposes.

#### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

### 2.5.2 D-latch is Not Functional

The CCL D-latch is not functional.

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | Х      |

# 2.5.3 The CCL Must be Disabled to Change the Configuration of a Single LUT

To reconfigure a LUT, the CCL peripheral must first be disabled (write ENABLE in CCL.CTRLA to '0'). Writing ENABLE to '0' will disable all the LUTs, and affects the LUTs not under reconfiguration.

### **Work Around**

None

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.6 RTC - Real-Time Counter

# 2.6.1 Any Write to the RTC.CTRLA Register Resets the RTC and PIT Prescaler

Any write to the RTC.CTRLA register resets the 15-bit prescaler resulting in a longer period on the current count or period.

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.6.2 Disabling the RTC Stops the PIT

Writing RTC.CTRLA.RTCEN to '0' will stop the PIT.

Writing RTC.PITCTRLA.PITEN to '0' will stop the RTC.

### **Work Around**

Do not disable the RTC or the PIT if any of the modules are used.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.7 TCA - Timer/Counter A

### 2.7.1 Restart Will Reset Counter Direction in NORMAL and FRQ Mode

When the TCA is configured to the NORMAL or FRQ mode (WGMODE in TCAn.CTRLB is ' $0 \times 0$ ' or ' $0 \times 1$ '), a RESTART command or Restart event will reset the direction to default. The default is counting upwards.

# **Work Around**

None.

# **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.8 TCB - Timer/Counter B

### 2.8.1 Minimum Event Duration Must Exceed the Selected Clock Period

Event detection will fail if TCBn receives an input event with a high/low period shorter than the period of the selected clock source (CLKSEL in TCBn.CTRLA). This applies to the TCB modes (CNTMODE in TCBn.CTRLB) *Time-Out Check* and *Input Capture Frequency and Pulse-Width Measurement*.

### **Work Around**

Ensure that the high/low period of input events is equal to or longer than the selected clock source (CLKSEL in TCBn.CTRLA) period.

### Affected Silicon Revisions

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.8.2 The TCB Interrupt Flag is Cleared When Reading CCMPH

TCBn.INTFLAGS.CAPT is cleared when reading TCBn.CCMPH instead of CCMPL.

#### **Work Around**

Read both TCBn.CCMPL and TCBn.CCMPH.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| Х      | X      |

# 2.8.3 TCB Input Capture Frequency and Pulse-Width Measurement Mode Not Working with Prescaled Clock

The TCB Input Capture Frequency and Pulse-Width Measurement mode may lock to Freeze state if CLKSEL in TCB.CTRLA is set to any other value than 0x0.

### **Work Around**

Only use CLKSEL equal to 0x0 when using Input Capture Frequency and Pulse-Width Measurement mode.

# **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

### 2.8.4 The TCA Restart Command Does Not Force a Restart of TCB

The TCA restart command does not force restarting the TCB when TCB is running in SYNCUPD mode. TCB is restarted only after a TCA OVF.

# **Work Around**

None

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.8.5 CCMP and CNT Registers Operate as 16-Bit Registers in 8-Bit PWM Mode

When the TCB operates in 8-bit PWM mode (CNTMODE in TCBn.CTRLB is ' $0 \times 7$ '), the low and high bytes for the CNT and CCMP registers operate as 16-bit registers for read and write. They cannot be read or written independently.

### **Work Around**

Use 16-bit register access. Refer to the data sheet for further information.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

### 2.9 TCD - Timer/Counter D

### 2.9.1 TCD Event Output Lines May Give False Events

The TCD event output lines can give false events.

### **Work Around**

Use the delayed event functionality with a minimum of one cycle delay.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.9.2 TCD Auto-Update Not Working

The TCD auto-update feature is not working.

#### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | -      |

# 2.9.3 Asynchronous Input Events Not Working When TCD Counter Prescaler is Used

When configuring the TCD to use asynchronous input events (CFG in TCDn.EVCTRLx is '0x2') and the TCD Counter Prescaler (CNTPRES in TCDn.CTRLA) is different from '0x0' events can be missed.

### **Work Around**

Use the TCD Synchronization Prescaler (SYNCPRES in TCDn.CTRLA) instead of the TCD Counter Prescaler. Alternatively, use synchronous input events (CFG in TCDn.EVCTRLx is not '0x2') if the input events are longer than one CLK\_TCD\_CNT cycle.

# **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| Х      | X      |

# 2.9.4 Halting TCD and Wait for SW Restart Does Not Work if Compare Value A is '0' or Dual Slope Mode is Used

Halting TCD and wait for software restart (INPUTMODE in TCDn.INPUTCTRLA is '0x7') does not work if compare value A is '0' (CMPASET in TCDn.CMPASET is '0x0') or Dual Slope mode is used (WGMODE in TCDn.CTRLB is '0x3').

### **Work Around**

Configure the compare value A (CMPASET in TCDn.CMPASET) to be different from '0' and do not use Dual Slope mode (WGMODE in TCDn.CTRLB is not '0x3').

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.10 TWI - Two-Wire Interface

# 2.10.1 TIMEOUT Bits in the TWI.MCTRLA Register are Not Accessible

The TIMEOUT bits in the TWI.MCTRLA register are not accessible from the software.

### **Work Around**

When initializing TWI, set BUSSTATE in TWI.MSTATUS to an IDLE state by writing 0x1 to it.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| Х      | X      |

# 2.10.2 TWI Master Mode Wrongly Detects the Start Bit as a Stop Bit

If TWI is enabled in Master mode followed by an immediate write to the MADDR register, the bus monitor recognizes the Start bit as a Stop bit.

### **Work Around**

Wait for a minimum of two clock cycles from TWI.MCTRLA.ENABLE until TWI.MADDR is written.

# **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.10.3 TWI Smart Mode Gives Extra Clock Pulse

TWI Master with Smart mode enabled gives an extra clock pulse on the SCL line after sending NACK.

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.10.4 The TWI Master Enable Quick Command is Not Accessible

TWI.MCTRLA.QCEN is not accessible from the software.

### **Work Around**

None.

### Affected Silicon Revisions

| Rev. A | Rev. B |

|--------|--------|

| X      | Х      |

# 2.11 USART - Universal Synchronous and Asynchronous Receiver and Transmitter

# 2.11.1 TXD Pin Override Not Released When Disabling the Transmitter

The USART will not release the TXD pin override if:

- The USART transmitter is disabled by writing the TXEN bit in USART.CTRLB to '0' while the USART receiver is disabled (RXEN in USART.CTRLB is '0')

- Both the USART transmitter and receiver are disabled at the same time by writing the TXEN and RXEN bits in USART.CTRLB to '0'

#### **Work Around**

There are two possible work arounds:

- Make sure the receiver is enabled (RXEN in USART.CTRLB is '1') while disabling the transmitter (writing TXEN in USART.CTRLB to '0')

- Writing to any register in the USART after disabling the transmitter will start the USART for long enough to release the pin override of the TXD pin

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# 2.11.2 Full Range Duty Cycle Not Supported When Validating LIN Sync Field

For the LIN sync field, the USART validates each bit to be within ±15% instead of the time between falling edges as described in the LIN specification, which allows a minimum duty cycle of 43.5% and a maximum duty cycle of 57.5%.

### **Work Around**

None.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

### 2.11.3 Frame Error on a Previous Message May Cause False Start Bit Detection

A false start bit detection will trigger if receiving a frame with RXDATAH.FERR set and reading the RXDATAL before the RxD line goes high.

# **Work Around**

Wait for the RXD pin to go high before reading RXDATA by, for instance, polling the bit in PORTn.IN where the RXD pin is located.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |

|--------|--------|

| X      | X      |

# ATtiny1614/1616/1617

Silicon Errata Issues

# 2.11.4 Open-Drain Mode Does Not Work When TXD is Configured as Output

When the USART TXD pin is configured as an output, it can drive the pin high regardless of whether the Open-Drain mode is enabled or not.

### **Work Around**

Configure the TXD pin as an input by writing the corresponding bit in PORTx.DIR to '0' when using Open-Drain mode.

### **Affected Silicon Revisions**

| Rev. A | Rev. B |  |

|--------|--------|--|

| X      | X      |  |

#### 3. **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (www.microchip.com/DS40002204).

Note: Corrections are shown in bold. Where possible, the original bold text formatting has been removed for clarity.

#### 3.1 **Memories**

#### 3.1.1 **Fuses - Factory Default Values**

A clarification has been made for the Fuse Description section in regards to the fuse default values. The data sheet refers to these values as reset values when they should have been given as factory-programmed values. Also, they are given in both hexadecimal and binary values, which contradict each other.

The following sentence has been added to each sub-section of the *Fuse Description* section.

The default value given in this fuse description is the factory-programmed value and should not be mistaken for the Reset value.

The table below lists the reset values given by the data sheet and the actual factory-programmed default values.

| Fuse    | Stated Reset Value in Data Sheet |            | Actual Factory Default on Device |             |  |

|---------|----------------------------------|------------|----------------------------------|-------------|--|

|         | Hexadecimal                      | Binary     | Hexadecimal                      | Binary      |  |

| WDTCFG  | -                                | `b00000000 | 0x00                             | , роооооооо |  |

| BODCFG  | -                                | `b00000000 | 0x00                             | `ь00000000  |  |

| OSCCFG  | -                                | `b0XXXXX10 | 0x10                             | `ь00000010  |  |

| TCD0CFG | -                                | `b00000000 | 0x00                             | , роооооооо |  |

| SYSCFG0 | 0xC4                             | `b11XX01X0 | 0xF6                             | `b11110110  |  |

| SYSCFG1 | -                                | `bXXXXX111 | 0x07                             | `ь00000111  |  |

| APPEND  | -                                | `b00000000 | 0x00                             | `ъ00000000  |  |

| BOOTEND | -                                | `b00000000 | 0x00                             | `ъ00000000  |  |

| LOCKBIT | -                                | `b00000000 | 0xC5                             | `b11000101  |  |

#### 3.2 **SLPCTRL - Sleep Controller**

#### 3.2.1 **Sleep Mode Activity Overview**

A clarification has been made to Table 11-1 Sleep Mode Activity Overview, where the single table has been split into three separate tables for clarity. Functional changes are shown in **bold**.

Table 3-1. Sleep Mode Activity Overview for Peripherals

| Peripheral | Active in Sleep Mode |                  |                  |

|------------|----------------------|------------------|------------------|

|            | ldle                 | Standby          | Power-Down       |

| CPU        | -                    | -                | -                |

| RTC        | X                    | X <sup>(1)</sup> | X <sup>(2)</sup> |

| WDT        | X                    | X                | X                |

| BOD        | X                    | X                | X                |

| continued             |                      |                  |            |  |

|-----------------------|----------------------|------------------|------------|--|

| Peripheral            | Active in Sleep Mode |                  |            |  |

|                       | ldle                 | Standby          | Power-Down |  |

| EVSYS                 | x                    | x                | x          |  |

| CCL                   | X                    | X <sup>(1)</sup> | -          |  |

| ACn                   |                      |                  |            |  |

| ADCn/PTC              |                      |                  |            |  |

| TCBn                  |                      |                  |            |  |

| All other peripherals | X                    | -                | -          |  |

### Notes:

- 1. Set the RUNSTBY bit of the corresponding peripheral to enter the active state.

- 2. PIT only.

Table 3-2. Sleep Mode Activity Overview for Clock Sources

| Clock Source                  | Active in Sleep Mode |                  |                  |

|-------------------------------|----------------------|------------------|------------------|

|                               | ldle                 | Standby          | Power-Down       |

| Main clock source             | X                    | X <sup>(1)</sup> | -                |

| RTC clock source              | X                    | X <sup>(1)</sup> | X <sup>(2)</sup> |

| WDT oscillator                | X                    | X                | X                |

| BOD oscillator <sup>(3)</sup> | x                    | x                | x                |

| CCL clock source              | x                    | X <sup>(1)</sup> | -                |

# Notes:

- 1. Set the RUNSTBY bit of the corresponding peripheral to enter the active state.

- 2. PIT only

- 3. The BOD oscillator runs only in Sampled mode.

Table 3-3. Sleep Mode Wake-Up Sources

| Wake-Up Sources                 | Active in Sleep Mode |                  |            |

|---------------------------------|----------------------|------------------|------------|

|                                 | Idle                 | Standby          | Power-Down |

| PORT Pin Interrupt              | X                    | ×                | χ(1)       |

| BOD VLM interrupt               | Х                    | x                | x          |

| RTC interrupts                  | X                    | X <sup>(2)</sup> | X(3)       |

| TWIn Address Match interrupt    | X                    | X                | X          |

| USARTn Start-of-Frame interrupt | -                    | X                | -          |

| TCBn interrupts                 | Х                    | X <sup>(2)</sup> | -          |

| ADCn/PTC interrupts             | Х                    | X <sup>(2)</sup> | -          |

| ACn interrupts                  | Х                    | X <sup>(4)</sup> | -          |

| All other interrupts            | Х                    | -                | -          |

### Notes:

- 1. Configure the I/O pin according to Asynchronous Sensing Pin Properties in the PORT section.

- 2. The RUNSTBY bit of the corresponding peripheral must be set to enter the active state.

- 3. PIT only.

- 4. When the RUNSTDBY bit is set, the AC will operate without updating its Status register or triggering interrupts. If another peripheral has requested CLK\_PER, the AC will use the clock to update the Status register and trigger interrupts.

# 3.3 USART - Universal Synchronous and Asynchronous Receiver and Transmitter

# 3.3.1 TXDATA Buffer

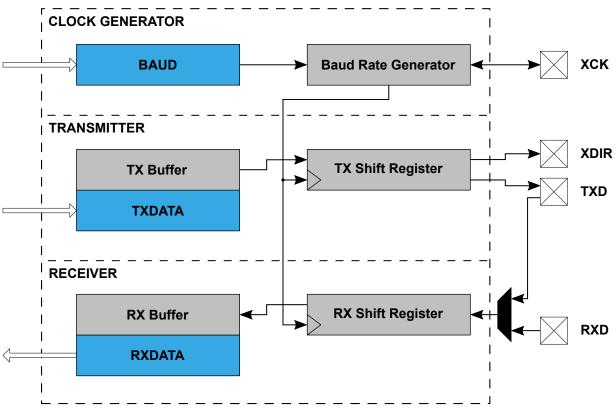

The block diagram is missing that USART TX is double-buffered from Figure 25-1 in the data sheet. The figure below shows the added **TX Buffer**.

Figure 3-1. Block Diagram

The following text is changed in the *Overview* section:

The transmitter consists of a two-level write buffer.

The following text is changed in the *Data Transmission* section:

The data transmission is initiated by loading the **Transmit Data (USARTn.TXDATAL and USARTn.TXDATAH)** registers with the data to be sent. The data in the **Transmit Data registers are moved to the TX Buffer** once emptied and then to the Shift register once it is empty and ready to send a new frame.

**Errata**

# 4. Document Revision History

**Note:** The document revision is independent of the silicon revision.

# 4.1 Revision History

| Doc.<br>Rev. | Date    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| С            | 09/2021 | Added erratum:     TCD: 2.9.4 Halting TCD and Wait for SW Restart Does Not Work if Compare Value A is '0' or Dual Slope Mode is Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|              |         | <ul> <li>Added data sheet clarifications:         <ul> <li>Memories: 3.1.1 Fuses - Factory Default Values</li> <li>SLPCTRL: 3.2.1 Sleep Mode Activity Overview</li> <li>USART: 3.3.1 TXDATA Buffer</li> </ul> </li> <li>Updated erratum:         <ul> <li>TWI: 2.10.1 TIMEOUT Bits in the TWI.MCTRLA Register are Not Accessible</li> </ul> </li> <li>Removed invalid erratum:         <ul> <li>Start-of-Frame Detection Can Unintentionally Be Triggered in Active Mode</li> </ul> </li> <li>Editorial updates</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| В            | 11/2020 | <ul> <li>Added die revision B to document</li> <li>Added errata:         <ul> <li>CCL: The CCL Must be Disabled to Change the Configuration of a Single LUT</li> <li>TCA: Restart Will Reset Counter Direction in NORMAL and FRQ Mode</li> <li>TCB: CCMP and CNT Registers Operate as 16-Bit Registers in 8-Bit PWM Mode</li> <li>TCD: Asynchronous Input Events Not Working When TCD Counter Prescaler is Used</li> <li>USART: Start-of-Frame Detection Can Unintentionally be Enabled in Active Mode when RXCIF is '0'</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| A            | 05/2020 | <ul> <li>Initial document release</li> <li>The content of the document has been restructured from:         <ul> <li>ATtiny1614 Silicon Errata and Data Sheet Clarification</li> <li>ATtiny1616/3216 Silicon Errata and Data Sheet Clarification</li> <li>ATtiny1617/3217 Silicon Errata and Data Sheet Clarification</li> </ul> </li> <li>ATtiny1614/1616/1617 Silicon Errata and Data Sheet Clarification (this document)</li> <li>ATtiny3216/3217 Silicon Errata and Data Sheet Clarification</li> <li>Refer to 4.2 Appendix - Obsolete Revision History for further details.</li> <li>The following items are referring to changes between the latest revisions of the obsolete documents and this document:         <ul> <li>Added errata:</li> <li>Device: Writing the OSCLOCK Fuse in FUSE.OSCCFG to '1' Prevents Automatic Loading of Calibration Values</li> <li>USART: Open-Drain Mode Does Not Work When TXD is Configured as Output</li> </ul> </li> <li>Removed data sheet clarifications, as the data sheet has been updated with correct information</li> </ul> |  |  |  |

Errata

# 4.2 Appendix - Obsolete Revision History

**Notes:** Due to document structure change from pin organized documents, the following document history is provided as a reference.

- ATtiny1614 Silicon Errata and Data Sheet Clarification (DS40002119B)

- ATtiny1616/3216 Silicon Errata and Data Sheet Clarification (DS40002120B)

- ATtiny1617/3217 Silicon Errata and Data Sheet Clarification (DS40002121B)

# 4.2.1 Obsolete Document DS40002119

| Doc Rev. | Date    | Comments                                                                                                                                                                                                                                                                                |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 10/2019 | <ul> <li>Updated document template</li> <li>The ADC errata, ADC Functionality Cannot be Ensured with ADCCLK Above 1.5 MHz for All Conditions, has been split into two separate erratas and rewritten</li> <li>Added clarifications to ADC and PTC electrical characteristics</li> </ul> |

| Α        | 06/2019 | Initial document release                                                                                                                                                                                                                                                                |

### 4.2.2 Obsolete Document DS40002120

| Doc Rev. | Date    | Comments                                                                                                                                                                                                                                                                                    |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 10/2019 | <ul> <li>Updated document template</li> <li>The ADC errata, ADC Functionality Cannot be Ensured with ADCCLK Above 1.5 MHz for All Conditions, has been split into two separate erratas and rewritten</li> <li>Added clarifications to ADC, AC and PTC electrical characteristics</li> </ul> |

| Α        | 06/2019 | Initial document release                                                                                                                                                                                                                                                                    |

### 4.2.3 Obsolete Document DS40002121

| Doc Rev. | Date    | Comments                                                                                                                                                                                                                                                                                    |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 10/2019 | <ul> <li>Updated document template</li> <li>The ADC errata, ADC Functionality Cannot be Ensured with ADCCLK Above 1.5 MHz for All Conditions, has been split into two separate erratas and rewritten</li> <li>Added clarifications to ADC, AC and PTC electrical characteristics</li> </ul> |

| Α        | 06/2019 | Initial document release                                                                                                                                                                                                                                                                    |

# The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- **Local Sales Office**

- Embedded Solutions Engineer (ESE)

- **Technical Support**

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/ design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-5224-8908-5

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                                        |

|---------------------------|-----------------------|-------------------------|-----------------------------------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels                                |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39                          |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393                         |

| el: 480-792-7200          | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen                          |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910                             |

| echnical Support:         | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829                             |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo                               |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820                           |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris                                |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20                         |

| Ouluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79                         |

| el: 678-957-9614          | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching                            |

| ax: 678-957-1455          | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700                             |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan                                |

| el: 512-257-3370          | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400                          |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn                           |

| Vestborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400                            |

| el: 774-760-0087          | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe                           |

| ax: 774-760-0088          | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370                            |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich                              |

| tasca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0                          |

| el: 630-285-0071          | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44                         |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim                           |

| )allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560                          |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana                             |

| el: 972-818-7423          | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705                           |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan                                 |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611                           |

| lovi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781                           |

| el: 248-848-4000          | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova                                |

| louston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286                           |

| el: 281-894-5983          | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen                          |

| ndianapolis               | China - Xiamen        | 161. 04-20-3440-2100    | Tel: 31-416-690399                            |

| loblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340                            |

| el: 317-773-8323          | China - Zhuhai        |                         | Norway - Trondheim                            |

| Eax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388                              |

| el: 317-536-2380          | Tel. 00-730-3210040   |                         | Poland - Warsaw                               |

| os Angeles                |                       |                         | Tel: 48-22-3325737                            |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest                           |

| el: 949-462-9523          |                       |                         | Tel: 40-21-407-87-50                          |

| Fax: 949-462-9608         |                       |                         |                                               |

|                           |                       |                         | <b>Spain - Madrid</b><br>Tel: 34-91-708-08-90 |

| el: 951-273-7800          |                       |                         |                                               |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91                          |

| el: 919-844-7510          |                       |                         | Sweden - Gothenberg                           |

| lew York, NY              |                       |                         | Tel: 46-31-704-60-40                          |

| el: 631-435-6000          |                       |                         | Sweden - Stockholm                            |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654                           |

| el: 408-735-9110          |                       |                         | UK - Wokingham                                |

| Tel: 408-436-4270         |                       |                         | Tel: 44-118-921-5800                          |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820                          |

| Геl: 905-695-1980         |                       |                         |                                               |

| ax: 905-695-2078          |                       |                         |                                               |