### Product Change Notification / SYST-09QLBY018

### Date:

11-Nov-2021

## **Product Category:**

PoE PD

## PCN Type:

**Document Change**

## **Notification Subject:**

Data Sheet - PD70101/PD70201 Datasheet

## **Affected CPNs:**

SYST-09QLBY018\_Affected\_CPN\_11112021.pdf SYST-09QLBY018\_Affected\_CPN\_11112021.csv

## Notification Text:

SYST-09QLBY018

Microchip has released a new Product Documents for the PD70101/PD70201 Datasheet of devices. If you are using one of these devices please read the document located at PD70101/PD70201 Datasheet.

#### Notification Status: Final

**Description of Change:** The following is the summary of changes in this revision. 1) Updated the figure and table in the 4. Package Specifications section. 2) Updated the 5. Recommended PCB Layout section.

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 11 Nov 2021

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

## **Attachments:**

### PD70101/PD70201 Datasheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile, including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

Affected Catalog Part Numbers (CPN)

PD701011LQ-TR PD702011LQ-TR

# PoE IEEE<sup>®</sup> 802.3af/at PD Controller

## Introduction

The PD70101 and PD70201 devices are integrated Powered Device (PD) interface and PWM controllers for a DC-DC converter used in IEEE<sup>®</sup> 802.3af and IEEE<sup>®</sup> 802.3at applications. The PD70101 device can be used for IEEE 802.3af or IEEE 802.3at Type 1 applications, while the PD70201 device can also be used in IEEE 802.3at Type 2 applications.

A single PD70201 device can be used in 4-pair applications that consume up to 47.7 W.

These devices have a number of features designed to improve efficiency and reliability:

- **Detection and Classification:** The front-end interface includes detection and classification circuitry. The detection signature resistor is disconnected upon completion of the detection phase. The system then begins the classification phase. Classification can be configured for Classes 0 to 4 via an external resistor. The PD70201 includes a two-events classification identification circuit, which generates a flag to inform the PD application whether the Power Source Equipment (PSE) is Type 1 or Type 2.

- **Capacitor:** A current-limited internal MOSFET switch charges the input capacitor of the DC-DC converter. This capacitor is discharged in a timely manner when the input power is removed.

- **Gate drivers:** The PWM DC-DC controller has two built-in gate drivers designed to swing between VCC and GND. These two out-of-phase driver stages can be configured for synchronous rectification or active clamp.

- **Peak current mode control:** The DC-DC converter employs peak current mode control for better line and load step response. The switching frequency can be set from 100 kHz to 500 kHz, enabling a size and efficiency trade off.

- Maximum duty cycle is limited to 50% to reduce the power MOSFET switch voltage to two times the input voltage; a 150V rated MOSFET can be used for the primary side switch. The secondary synchronous MOSFET voltage rating depends on the output voltage and can be higher or lower than the primary side MOSFET switch.

- **Soft-Start circuit:** The devices include a soft-start circuit to control the output voltage rise time (user settable) at start-up, and to limit the inrush current. An integrated startup bias circuit powers the DC-DC controller, until the device starts up by the voltage generated by the bootstrap circuit.

- Low Voltage Protection Warning and Monitoring: Dual Under Voltage Lock Out (UVLO), which monitors both the PoE Port Input Voltage and VCC, ensures reliable operation during any system disturbances. The PoE port UVLO has a programmable threshold and hysteresis to enable tailoring to the desired turn-on and turn-off voltage.

An internal current sense amplifier with a Kelvin connection allows the use of an extremely low resistor to measure the current sense threshold voltage (200 mV) which optimizes efficiency.

Low Power Mode operation is provided to improve efficiency under light loads such as when the PD is in standby. The user can define at what power level the unit enters low power mode by means of a single resistor value.

## Features

The following is a list of features that are supported in this device.

- Designed to support IEEE 802.3af and IEEE 802.3at standards.

- PD Detection and Programmable Classification Signature

- Two-Events Classification Flag

- Signature Resistor Disconnection after Detection

- Integrated 0.6  $\Omega$  Isolating Switch and Inrush Current Limiter

- 4-Pairs support with a single PD70201 IC for up to 48 W

- 4-Pairs support with two PD70201 ICs for up to 96 W

- Less than 10µA Offset Current during Detection

- Single DC Voltage Input (36 V 57 V)

- Wide Operating Temperature Range: -40 to 85 °C

- On-Chip Thermal Protection

- Integrated PWM 100 kHz to 500 kHz adjustable DC-DC switching frequency DC-DC frequency can be synchronized to external clock

- · Supports low power mode operation for higher efficiency

- 50% maximum duty cycle

- Soft-start circuit to control the output voltage rise time

- Two out-of-phase driver stages for efficient synchronous rectification or active clamp

- · PoE port input UVLO with programmable threshold and hysteresis

- · Internal differential amplifier simplifying non-isolated step down converter

- · Over load and short circuit protection

- 32-Pin 5 mm x 5 mm QFN Package

- RoHS Compliant

- MSL3

The following table lists the Microchip PD products offerings.

#### Table 1. Microchip Powered Device Products Offerings

| Part      | Туре               | Package             | IEEE<br>802.3af | IEEE<br>802.3at | HDBaseT<br>(PoH) | UPoE |

|-----------|--------------------|---------------------|-----------------|-----------------|------------------|------|

| PD70100   | Front end          | 3 mm × 4 mm 12L DFN | x               | —               | —                | —    |

| PD70101   | Front end + PWM    | 5 mm × 5 mm 32L QFN | x               | _               | _                | —    |

| PD70200   | Front end          | 3 mm × 4 mm 12L DFN | x               | x               | _                |      |

| PD70201   | Front end + PWM    | 5 mm × 5 mm 32L QFN | x               | x               | _                | —    |

| PD70210   | Front end          | 4 mm × 5 mm 16L DFN | x               | x               | x                | x    |

| PD70210A  | Front end          | 4 mm × 5 mm 16L DFN | x               | x               | x                | x    |

| PD70210AL | Front end          | 5 mm × 7 mm 38L QFN | x               | x               | x                | x    |

| PD70211   | Front end + PWM    | 6 mm × 6 mm 36L QFN | x               | x               | x                | x    |

| PD70224   | Ideal diode bridge | 6 mm × 8 mm 40L QFN | x               | x               | x                | x    |

# Applications

IEEE 802.3at and IEEE 802.3af powered devices such as IP phones, WLAN access points, and network cameras.

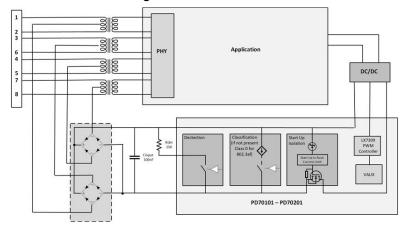

The following figure shows the basic block diagram of the PD70101/PD70201 device. **Figure 1. PD70101/PD70201 Basic Block Diagram**

Microchip offers complete reference design packages and Evaluation Boards (EVBs). For access to these design packages, device datasheets, or application notes, consult your local Microchip Client Engagement Manager or visit our website at www.microchip.com/poe. For technical support, consult your local consult your local Embedded Solutions Engineers or go to www.microchip.com/support. For help in designing the dc/dc portion of your circuit please try our MPLAB Analog Designer (MAD) tool at www.microchip.com/mad-poe.

# **Table of Contents**

| Intr | oductio        | n                                                                      | 1    |

|------|----------------|------------------------------------------------------------------------|------|

|      |                | res                                                                    |      |

|      | Applic         | ations                                                                 | 3    |

| 1.   | Funct          | onal Descriptions                                                      | 6    |

| 2.   | Electr         | cal Specifications                                                     | 7    |

|      | 2.1.           | Absolute Maximum Ratings                                               | 7    |

|      | 2.2.           | Thermal Specifications                                                 | 7    |

|      | 2.3.           | Electrical Characteristics                                             | 8    |

| 3.   | Pin Co         | onfiguration                                                           | .15  |

| 4.   | Packa          | ge Specifications                                                      | . 18 |

| 5.   | Recor          | nmended PCB Layout                                                     | .20  |

| 6.   | Theor          | y of Operation                                                         | . 22 |

|      | 6.1.           | Detection                                                              | . 22 |

|      | 6.2.           | Physical Layer Classification                                          | .22  |

|      | 6.3.           | Two-Events Detection and AT Flag                                       | . 22 |

|      | 6.4.           | Soft Start and Inrush Current Protection                               | . 23 |

|      | 6.5.           | Over-Current Protection                                                |      |

|      | 6.6.           | Power Good                                                             |      |

|      | 6.7.           | Start-Up Supply                                                        |      |

|      | 6.8.           | PD Interface Thermal Protection                                        |      |

|      | 6.9.           | Bulk Capacitor Discharge                                               |      |

|      |                | DC-DC Start-Up                                                         |      |

|      | 6.11.          | Current Limit and Short Circuit Protection<br>Low Power Mode Operation |      |

|      | 6.12.<br>6.13. |                                                                        |      |

|      |                | External Enable                                                        |      |

| 7.   |                | ng Information                                                         |      |

|      |                | ence Documents                                                         |      |

| 8.   |                |                                                                        |      |

| 9.   | Revis          | on History                                                             | . 28 |

| The  | Micro          | chip Website                                                           | .29  |

| Pro  | duct C         | nange Notification Service                                             | .29  |

| Cus  | stomer         | Support                                                                | . 29 |

| Mic  | rochip         | Devices Code Protection Feature                                        | . 29 |

| Leg  | al Noti        | ce                                                                     | 29   |

| Tra  | demark         | S                                                                      | . 30 |

| Quality Management System   | 30 |

|-----------------------------|----|

| Worldwide Sales and Service | 31 |

# 1. Functional Descriptions

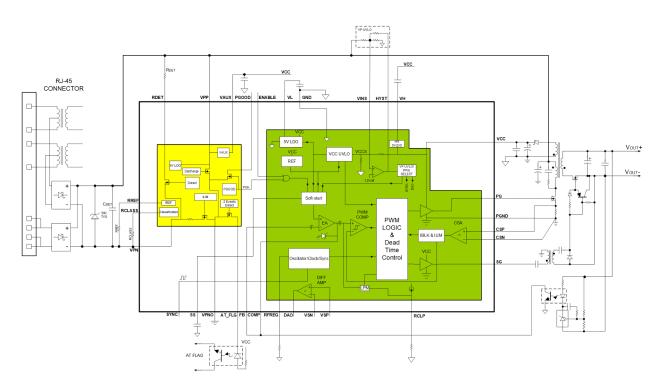

The following figure shows the functional block diagram of PD70101/PD70201 device. **Figure 1-1. Functional Block Diagram**

## 2. Electrical Specifications

The following section describes the electrical specifications of the PD70101/PD70201 device.

## 2.1 Absolute Maximum Ratings

The following table lists the absolute maximum ratings of the PD70101/PD70201 device. **Table 2-1. Absolute Maximum Ratings**

| Parameter                                                                   | Value           | Units           |

|-----------------------------------------------------------------------------|-----------------|-----------------|

| VPP, RDET, VPN_OUT (with respect to VPN_IN)                                 | –0.3 to 74      | V <sub>DC</sub> |

| RREF, RCLASS (with respect to VPN_IN)                                       | -0.3 to 6       | V               |

| PGOOD, AT_FLAG, VAUX (with respect to VPN_OUT)                              | –0.3 to 74      | V               |

| VCC (with respect to PGND)                                                  | -0.3 to 40      | V <sub>DC</sub> |

| PG, SG (with respect to PGND)                                               | -0.3 to 20      | V <sub>DC</sub> |

| VL, VSN, VSP (with respect to PGND)                                         | -0.3 to 6       | V               |

| VH (with respect to VCC)                                                    | -0.3 to VCC-6   | V <sub>DC</sub> |

| All Other Pins (with respect to GND)                                        | -0.3 to VL +0.3 | V <sub>DC</sub> |

| ESD (HBM) Protection at all I/O pins <sup>1</sup>                           | ±1              | kV              |

| Maximum Junction Temperature (T <sub>JMAX</sub> )                           | 150             | °C              |

| Operational Ambient Temperature                                             | -40 to 85       | °C              |

| Storage Temperature Range                                                   | –65 to 150      | °C              |

| Peak Package Solder Re-flow Temperature (40 seconds maximum exposure), MSL3 | 260             | °C              |

#### Note:

1. All pins except pin 2 (PGOOD) and pin 31 (VAUX). Pin 2 and 31 ESD Protection is ±150 V HBM.

Exceeding these ratings might cause damage to the device. All voltages are with respect to VPN\_IN. Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions are not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

### 2.2 Thermal Specifications

The following table lists the thermal specifications of the PD70101/PD70201 device.

#### Table 2-2. Thermal Properties

| Symbol          | Thermal Resistance  | Min | Туре | Мах | Units |

|-----------------|---------------------|-----|------|-----|-------|

| θ <sub>JC</sub> | Junction to case    |     | 5    |     | °C/W  |

| $\theta_{JP}$   | Junction to pad     |     | 4    |     | °C/W  |

| θ <sub>JA</sub> | Junction to ambient |     | 23   |     | °C/W  |

Note: The  $\theta_{Jx}$  numbers assume no forced airflow. Junction temperature is calculated using

$T_J = T_A + (P_D x \theta_{jA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51 (JEDEC) with thermal vias.

## 2.3 Electrical Characteristics

This section describes the electrical characteristics of the PD70101/PD70201 device.

The following specifications apply over the operating ambient temperature of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C (except where otherwise noted with V<sub>PP</sub> = 48 V; V<sub>EN</sub> = HIGH, F<sub>FREQ</sub> = 250 kHz). Production tests were performed at 25 °C. Unless otherwise specified, V<sub>PP</sub> is with respect to VPN\_IN and VCC is with respect to PGND.

| Table | 2-3. | PD | Interface |

|-------|------|----|-----------|

|-------|------|----|-----------|

| Symbol               | Parameter                             | Test<br>Conditions/<br>Comment                                                                                                                    | Min  | Туре | Мах  | Units |

|----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Power Supply         |                                       |                                                                                                                                                   |      |      |      |       |

| V <sub>PP</sub>      | Input voltage                         |                                                                                                                                                   | 0    | 55   | 57   | V     |

| Detection Mod        | e                                     |                                                                                                                                                   |      |      |      |       |

| DET <sub>RANGE</sub> | Detection<br>voltage range            | Measured<br>between V PP<br>and VPN IN                                                                                                            | 1.3  |      | 10.1 | V     |

| R <sub>DET-ON</sub>  | Detection<br>switch ON<br>resistance  | $\begin{array}{l} 2.5 V \leq (\Delta V_{PP} \\ to \ V_{PNIN}) \leq \\ 10.1 \ V \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$             |      |      | 50   | Ω     |

| V <sub>DET-OFF</sub> | Detection is disconnected             | Measured<br>between V <sub>PP</sub><br>and VPN <sub>IN</sub>                                                                                      | 10.1 |      | 12.8 | V     |

| R <sub>DET-OFF</sub> | Detection<br>switch OFF<br>resistance | $\begin{array}{l} 12.8 \ V \leq (\Delta V_{PP} \\ to \ VPN_{IN}) \leq \\ 57.0 \ V \\ Measured \\ between \ R_{DET} \\ and \ VPN_{IN} \end{array}$ | 2.0  |      |      | ΜΩ    |

| I <sub>OFFSET</sub>  | Input offset<br>current               | 2.5 V ≤ V <sub>PP</sub> ≤<br>10.1 V<br>-40 °C ≤ T <sub>J</sub> ≤<br>85 °C                                                                         |      |      | 16   | μA    |

| I <sub>OFFSET</sub>  |                                       | 2.5 V ≤ V <sub>PP</sub> ≤<br>10.1 V<br>-40 °C ≤ T <sub>J</sub> ≤<br>55 °C                                                                         |      |      | 10   | μA    |

| V <sub>RDET-ON</sub> | RDET<br>reconnection<br>level         | Measured<br>between V <sub>PP</sub><br>and VPN <sub>IN</sub>                                                                                      | 1.95 | 3.0  | 4.85 | V     |

| Classification       | Mode                                  |                                                                                                                                                   |      |      |      |       |

## **Electrical Specifications**

| continue                 | continued                                                                                                                                                                           |                                                                             |       |      |       |       |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|-------|-------|--|

| Symbol                   | Parameter                                                                                                                                                                           | Test<br>Conditions/<br>Comment                                              | Min   | Туре | Мах   | Units |  |

| V <sub>TH-LOW-ON</sub>   | Classification<br>current source,<br>turn ON<br>threshold<br>range<br>measured at<br>VPP                                                                                            | Turn on for<br>any I <sub>CLASS</sub><br>while V <sub>PP</sub><br>increases | 11.4  |      | 13.7  | V     |  |

| V <sub>HST</sub>         | Classification<br>disconnection<br>minimum<br>hysteresis<br>voltage                                                                                                                 | Hysteresis<br>between V TH<br>-low-on and V<br>TH -low-off                  |       | 1    |       | V     |  |

| V <sub>TH-HIGH-OFF</sub> | $\begin{array}{c} \text{Classification} \\ \text{current source,} \\ \text{turn OFF} \\ \text{threshold} \\ \text{range} \\ \text{measured at} \\ \text{V}_{\text{PP}} \end{array}$ | Turn off while<br>VPP increases                                             | 20.9  |      | 23.9  | V     |  |

| I <sub>CLASS-LIM</sub>   | Current limit threshold                                                                                                                                                             |                                                                             | 50    | 68   | 80    | mA    |  |

| I <sub>CLASS-DIS</sub>   | Input current<br>IPP when<br>classification<br>function is<br>disabled                                                                                                              | Class 0<br>R <sub>CLASS</sub> =<br>Open                                     |       |      | 3.0   | mA    |  |

| I <sub>CLASS-EN</sub>    | Input current<br>IPP when<br>classification<br>function is                                                                                                                          | Class 1<br>R <sub>CLASS</sub> = 133<br>Ω ± 1%                               | 9.5   | 10.5 | 11.5  | mA    |  |

|                          | enabled                                                                                                                                                                             | Class 2<br>R <sub>CLASS</sub> = 69.8<br>$\Omega \pm 1\%$                    | 17.5  | 18.5 | 19.5  | mA    |  |

|                          |                                                                                                                                                                                     | Class 3<br>R <sub>CLASS</sub> = 45.3<br>Ω ±1%                               | 26.5  | 28.0 | 29.5  | mA    |  |

|                          |                                                                                                                                                                                     | Class 4<br>R <sub>CLASS</sub> = 30.9<br>$\Omega \pm 1\%$                    | 38.0  | 40.0 | 42.0  | mA    |  |

|                          | R <sub>CLASS</sub><br>Voltage                                                                                                                                                       |                                                                             | 1.142 |      | 1.278 | V     |  |

| Mark                     |                                                                                                                                                                                     |                                                                             |       |      |       |       |  |

| V <sub>MARK</sub>        | Mark, working<br>range                                                                                                                                                              | V <sub>PP</sub> failing<br>edge                                             | 4.9   |      | 10.1  | V     |  |

| I <sub>MARK</sub>        | Mark current                                                                                                                                                                        |                                                                             | 0.25  |      | 4     | mA    |  |

## **Electrical Specifications**

| Symbol                 | Parameter                                                                                          | Test Conditions/Comment                                                                                               | Min  | Туре | Max  | Units |

|------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>SW- START</sub> | Isolation Switch MOSFET switches from off to I <sub>LIM-LOW</sub>                                  |                                                                                                                       | 36   |      | 42   | V     |

| V <sub>SW-OFF</sub>    | Isolation Switch MOSFET switched off                                                               |                                                                                                                       | 30.5 |      | 34.5 | V     |

| I <sub>LIM-LOW</sub>   | Startup current limit, I <sub>LIM-LOW</sub>                                                        |                                                                                                                       | 130  | 240  | 330  | mA    |

| V <sub>DIFF</sub>      | VPN_IN to VPN_OUT Threshold voltage for I <sub>LIM – LOW</sub> to I <sub>LIM-HIGH</sub> switchover | When VPNIN to VPNOUT ≤<br>VDIFF, Isolating switch switches<br>over from I <sub>LIM-LOW</sub> to I <sub>LIM-HIGH</sub> |      |      | 0.7  | V     |

| OCP                    | Over current protection limit current                                                              |                                                                                                                       | 1500 | 1800 | 2000 | mA    |

| I <sub>LOAD</sub>      | Continuous operation load                                                                          | Isolating switch at I <sub>LIM-HIGH</sub><br>PD70101                                                                  |      |      | 450  | mA    |

|                        |                                                                                                    | PD70201                                                                                                               |      |      | 1123 | mA    |

| SW-RDS <sub>ON</sub>   | Isolated Switch On resistance at I <sub>LIM-</sub><br>HIGH                                         | Total resistance between VPNIN<br>and VPNOUT<br>Isolating switch at I <sub>LIM-HIGH</sub>                             |      |      | 0.6  | Ω     |

#### Table 2-4. Isolation Switch

### Table 2-5. DC/DC Capacitor Discharge

| Symbol               | Parameter                                    | Test Conditions/Comment                                                                         | Min  | Туре | Мах  | Units |

|----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| CIN                  | DC/DC input capacitance                      | For reference only Guaranteed by design (not tested in production)                              |      | 220  | 264  | μF    |

|                      | Discharge current                            | 7.0 V $\leq$ VPP to VPNOUT $\leq$ 30 V                                                          | 22.8 | 32   | 50   | mA    |

| AT_FLAG              |                                              |                                                                                                 |      |      |      |       |

|                      | Output low voltage                           | IOL = 0.75 mA                                                                                   |      |      | 0.4  | V     |

|                      |                                              | IOL = 5 mA                                                                                      |      |      | 2.5  | V     |

|                      | Leakage current                              | VAT_FLAG = 57 V                                                                                 |      |      | 1.7  | μA    |

| PGOOD                |                                              |                                                                                                 |      |      |      |       |

|                      | Output low voltage                           | IOL = 0.75 mA                                                                                   |      |      | 0.4  | V     |

|                      |                                              | IOL MAX = 5 mA                                                                                  |      |      | 2.5  | V     |

|                      | Leakage current                              | VPGOOD = 57 V                                                                                   |      |      | 1.7  | μA    |

| Interface 1          | Thermal Shutdown                             |                                                                                                 |      |      |      |       |

|                      | Thermal Shutdown<br>Temperature <sup>1</sup> |                                                                                                 | 180  | 200  | 220  | °C    |

| VAUX (res            | pect to VPN_OUT)                             |                                                                                                 |      |      |      |       |

| VAUX- <sub>OFF</sub> | VAUX output voltage off<br>(leakage current) | PGOOD = High impedance<br>Load = 1 MΩ                                                           |      |      | 1    | V     |

| VAUX- <sub>ON</sub>  | VAUX output voltage on                       | Isolating switch at $I_{\text{LIM-HIGH}}$ and PGOOD = Low                                       | 9.8  | 10.5 | 11.8 | V     |

| I <sub>VAUXP</sub>   | Output current peak                          | Capacitor = 30 $\mu F$ When $T_{LOAD} \leq 5$ ms Isolating switch at I_LIM-HIGH and PGOOD = Low | 0    |      | 10   | mA    |

## **Electrical Specifications**

| continued          |                           |                                                                                      |     |      |     |       |  |  |  |

|--------------------|---------------------------|--------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|--|

| Symbol             | Parameter                 | Test Conditions/Comment                                                              | Min | Туре | Max | Units |  |  |  |

| I <sub>VAUXC</sub> | Output continuous current | When $T_{LOAD} \le 10 \text{ mS}$ Isolating switch at $I_{LIM}$ HIGH and PGOOD = Low | 0   |      | 2   | mA    |  |  |  |

| I <sub>VAUX</sub>  | VAUX output current limit | Isolating switch at $I_{LIM-HIGH}$ and PGOOD = Low                                   | 10  |      | 32  | mA    |  |  |  |

#### Table 2-6. DC/DC Controller

| Symbol                | Parameter                                              | Test Conditions/Comment                                                                                         | Min   | Тур   | Max   | Units |

|-----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VCC                   |                                                        |                                                                                                                 |       |       |       |       |

| VCC                   | Maximum Input Operating<br>Voltage                     |                                                                                                                 |       |       | 20    | V     |

| IVCC                  | Input Current                                          | VCC< VCC_UVLO or<br>ENABLE = Low. <sup>5</sup>                                                                  |       | 250   | 2000  | μA    |

|                       |                                                        | V <sub>ENABLE</sub> and VINS = High;<br>V <sub>VCC</sub> < VCC_UVLO_UP; -40 °C ≤<br>Temp ≤ +55 °C. <sup>5</sup> |       |       | 4.5   | mA    |

|                       |                                                        | VCC >VCC_UVLO and<br>ENABLE = High, No Load on PG,<br>SG, VL, and FSW = 500 kHz.                                |       |       | 3     | mA    |

| VCC_UVLO              | VCC UVLO Rising Threshold                              | VCC raising edge                                                                                                | 8.85  | 9.15  | 9.5   | V     |

| VCC_UVLO              | VCC UVLO Falling Threshold                             | VCC falling edge                                                                                                | 7     | 7.3   | 7.6   | V     |

| POE Port Inp          | out UVLO                                               |                                                                                                                 |       |       |       |       |

| VINS                  | UVLO Threshold                                         |                                                                                                                 | 1.171 | 1.200 | 1.229 | V     |

|                       | VINS Input Current                                     |                                                                                                                 | -0.1  |       | 0.1   | μA    |

| HYST-V <sub>OH</sub>  | HYST Output High Voltage                               | I <sub>SOURCE</sub> = 1 mA                                                                                      | 2.8   |       |       | V     |

| HYST-V <sub>OL</sub>  | HYST Output Low Voltage                                | I <sub>SINK</sub> = 3 mA                                                                                        |       |       | 0.4   | V     |

| Internal LDC          | )'s                                                    |                                                                                                                 |       |       |       |       |

| VL                    | 5 V LDO                                                | IL < 5 mA                                                                                                       | 4.75  | 5     | 5.25  | V     |

| VH                    | –5 V LDO                                               | Reference to VCC                                                                                                |       | -5    |       | V     |

| Soft-Start            |                                                        |                                                                                                                 |       |       |       |       |

| I <sub>SS_CHG</sub>   | Soft-start charging current <sup>2</sup>               | $R_{FREQ}$ = 33.2 k $\Omega$ ; $V_{SOFTSTART}$ = 0.5 V                                                          | 32    | 36    | 40    | μA    |

| I <sub>SS_DIS</sub>   | Soft-start discharging current                         | $V_{SOFTSTART}$ = 0.5 V; % of $I_{SS_{CHG}}$                                                                    |       | 10    |       | %     |

| V <sub>SS_CH</sub>    | Soft-start completion threshold <sup>1</sup>           | % of 1.2 V                                                                                                      | 90    |       | 95    | %     |

| V <sub>SS_DISCH</sub> | Soft-start discharge completion threshold <sup>1</sup> |                                                                                                                 |       | 50    |       | mV    |

| R <sub>SS_DISCH</sub> | Soft-start discharge FET on resistance                 |                                                                                                                 |       | 50    |       | Ω     |

| t <sub>DISCH</sub>    | Soft-start discharge FET on time <sup>1</sup>          | 1 cyc = 1/F <sub>FREQ</sub>                                                                                     |       | 32    |       | сус   |

## **Electrical Specifications**

| continued              |                                           |                              |      |     |      |       |  |  |

|------------------------|-------------------------------------------|------------------------------|------|-----|------|-------|--|--|

| Symbol                 | Parameter                                 | Test Conditions/Comment      | Min  | Тур | Max  | Units |  |  |

| Switching Fr           | equency and Synchronization               |                              |      |     |      |       |  |  |

| F <sub>FREQ</sub>      | Switching frequency range                 |                              | 100  |     | 500  | kHz   |  |  |

| F <sub>FREQ</sub>      | Switching frequency accuracy <sup>3</sup> | R <sub>FREQ</sub> = 33.2k    | 285  | 315 | 345  | kHz   |  |  |

| F <sub>SYNC</sub>      | Synchronization frequency range           | FSYNC > 2x F <sub>FREQ</sub> | 200  |     | 1000 | kHz   |  |  |

| V <sub>SYNC-HIGH</sub> | Synchronization voltage high threshold    |                              | 2.4  |     | 5    | V     |  |  |

| V <sub>SYNC-LOW</sub>  | Synchronization voltage low threshold     |                              |      |     | 0.8  | V     |  |  |

| PW <sub>SYNC_MIN</sub> | Synchronization minimum pulse width       |                              | 100  |     |      | ns    |  |  |

| PW <sub>SYNC_MAX</sub> | Synchronization maximum PWM duty          |                              |      |     | 90   | %     |  |  |

| I <sub>SYNC</sub>      | Synchronization input current             |                              | -1.3 |     | 1.3  | μA    |  |  |

### Table 2-7. Error Amplifier

| Symbol                 | Parameter                         | Test Conditions/Comment                                      | Min   | Туре  | Max   | Units |

|------------------------|-----------------------------------|--------------------------------------------------------------|-------|-------|-------|-------|

| Gain <sub>DC_OPL</sub> | DC Open Loop Gain <sup>1</sup>    | R <sub>LOAD</sub> = 100k                                     | 70    | 100   |       | dB    |

| AV <sub>UGBW</sub>     | Unity Gain Bandwidth <sup>1</sup> | C <sub>LOAD</sub> = 10 pF                                    | 2     | 5     |       | MHz   |

| I <sub>COMP_OUT</sub>  | Output Sourcing Current           | $0.2 \text{ V} \le \text{V}_{\text{COMP}} \le 1.3 \text{ V}$ | 110   |       | 620   | μA    |

| I <sub>COMP_IN</sub>   | Output Sink Current               | $0.2 \text{ V} \le \text{V}_{\text{COMP}} \le 1.3 \text{ V}$ | 145   |       | 495   | μA    |

| V <sub>EA_CMR</sub>    | Input Common Mode Range           |                                                              | 0     |       | 2     | V     |

| V <sub>FB</sub>        | Feedback Voltage                  | COMP shorted to FB                                           | 1.171 | 1.200 | 1.229 | V     |

| I <sub>FB</sub>        | FB Pin Input Current              |                                                              | -50   |       | 50    | nA    |

| V <sub>COMP</sub>      | Output Clamp Voltage              |                                                              | 1.8   | 2.1   | 2.6   | V     |

### Table 2-8. PWM Comparator

| Symbol            | Parameter                        | Test<br>Conditions/<br>Comment                         | Min | Туре | Мах | Units |

|-------------------|----------------------------------|--------------------------------------------------------|-----|------|-----|-------|

| V <sub>RCLP</sub> | RCLP Voltage<br>Range            |                                                        | 0   |      | 1   | V     |

| Low Power Mo      | de (Skip Pulse I                 | /lode)                                                 |     |      |     |       |

|                   | Low Power<br>Skip                | V <sub>COMP</sub> Rising<br>(% of V <sub>RCLP</sub> )  |     | 95   |     | %     |

|                   | Mode<br>Threshold <sup>1,4</sup> | V <sub>COMP</sub> Falling<br>(% of V <sub>RCLP</sub> ) |     | 90   |     | %     |

## **Electrical Specifications**

| Symbol                       | Parameter                              | Test<br>Conditions/<br>Comment | Min  | Туре | Max  | Units |

|------------------------------|----------------------------------------|--------------------------------|------|------|------|-------|

| Gain <sub>CSA</sub>          | Gain                                   | Measure at<br>DC               | 4.75 | 5.0  | 5.25 | V/V   |

| $V_{\text{CSA}\_\text{CMR}}$ | Input Common<br>Mode Range             |                                | 0    |      | 2.0  | V     |

|                              | Output Rise/<br>Fall time <sup>1</sup> | 10% to 90%                     |      |      | 75   | ns    |

| t <sub>BLANK</sub>           | Blanking<br>Time <sup>1</sup>          |                                | 50   |      | 100  | ns    |

| V <sub>ILIM_TH</sub>         | Current Limit<br>Threshold             |                                | 1.1  | 1.2  | 1.3  | V     |

| V <sub>IMAX_TH</sub>         | Current<br>Maximum<br>Threshold        |                                | 1.7  | 1.8  | 1.9  | V     |

### Table 2-9. Current Sense Amplifier and Current Limit

### Table 2-10. Differential Amplifier

| Symbol                | Parameter                            | Test<br>Conditions/<br>Comment | Min  | Туре | Мах  | Units |

|-----------------------|--------------------------------------|--------------------------------|------|------|------|-------|

| Gain <sub>DA</sub>    | Gain                                 | Measured at<br>DC              | 6.86 | 7.0  | 7.14 | V/V   |

| AV <sub>UGBW_DA</sub> | Unity Gain<br>Bandwidth <sup>1</sup> |                                |      | 5    |      | MHz   |

| V <sub>DA_CMR</sub>   | Common<br>Mode Range                 |                                | 0    |      | 3.5  | V     |

|                       | Input Offset<br>Voltage              |                                | -7   |      | 7    | mV    |

|                       | Input Bias<br>Current                |                                | -1   |      | 1    | μΑ    |

#### Table 2-11. Output Drivers

| Symbol                | Parameter                                       | Test<br>Conditions/<br>Comment | Min | Туре | Мах | Units |

|-----------------------|-------------------------------------------------|--------------------------------|-----|------|-----|-------|

| PG Rds <sub>ONH</sub> | Primary Gate<br>(PG) High On<br>Resistance      |                                |     | 10   |     | Ω     |

| PG Rds <sub>ONL</sub> | Primary Gate<br>(PG) Low On<br>Resistance       |                                |     | 5    |     | Ω     |

| SG Rds <sub>ONH</sub> | Secondary<br>Gate (SG)<br>High On<br>Resistance |                                |     | 10   |     | Ω     |

## **Electrical Specifications**

| continue              | continued                                                   |                                    |      |      |     |       |  |  |

|-----------------------|-------------------------------------------------------------|------------------------------------|------|------|-----|-------|--|--|

| Symbol                | Parameter                                                   | Test<br>Conditions/<br>Comment     | Min  | Туре | Мах | Units |  |  |

| SG Rds <sub>ONL</sub> | Secondary<br>Gate (SG) Low<br>On Resistance                 |                                    |      | 10   |     | Ω     |  |  |

| T <sub>DEAD</sub>     | Dead Time –<br>PG low to SG<br>high or SG low<br>to PG high | CLOAD on PG<br>and SG =<br>1000 pF |      | 110  |     | ns    |  |  |

|                       | PG Minimum<br>On Time                                       |                                    |      |      | 120 | ns    |  |  |

|                       | PG Maximum<br>Duty Cycle                                    |                                    | 44.5 |      | 50  | %     |  |  |

### Table 2-12. Logic (ENABLE Pin)

| Symbol          | Parameter               | Test<br>Conditions/<br>Comment | Min | Туре | Мах | Units |

|-----------------|-------------------------|--------------------------------|-----|------|-----|-------|

| V <sub>HI</sub> | Logic High<br>Threshold |                                | 2.0 |      |     | V     |

| V <sub>LO</sub> | Logic Low<br>Threshold  |                                |     |      | 0.8 | V     |

|                 | Input Current           |                                | -1  |      | 1   | μΑ    |

### Table 2-13. PWM Controller Thermal Shutdown

| Symbol            | Parameter                                     | Test<br>Conditions/<br>Comment | Min | Туре | Мах | Units |

|-------------------|-----------------------------------------------|--------------------------------|-----|------|-----|-------|

| T <sub>SD</sub>   | Thermal<br>Shutdown<br>Threshold <sup>1</sup> |                                |     | 157  |     | °C    |

| T <sub>HYST</sub> | Threshold<br>Hysteresis <sup>1</sup>          |                                |     | 15   | 30  | °C    |

#### Notes:

- 1. Guaranteed by design.

- 2. Soft start charge current equation:  $I_{ss\_chg} = 1.2V/R_{FREQ}$ .

- 3. Switching frequency equation: Freq =  $1/[(90 \text{ pF x } R_{FREQ}) + 150 \text{ ns}]$ , where Freq is (Hz).

- 4. Low power mode clamp equation:  $V_{CLAMP}$  = 0.3 \* ( $R_{RCLP}/R_{FREQ}$ ).

- 5. Minimum and maximum current are guaranteed by design.

# 3. Pin Configuration

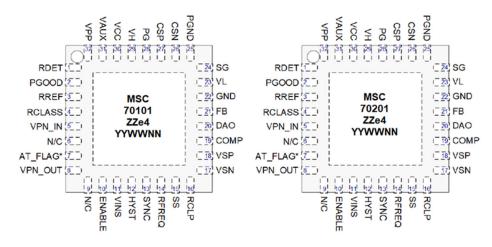

The following illustration shows the device pin diagram from the top views. **Figure 3-1. Pin Diagram**

ZZ = Random character with no meaning and  $e_4 = 2^{nd}$  level interconnect.

YY = Year, WW = Week, NNN = Trace Code

The following table lists the pin descriptions of the PD70101/PD70201 device.

### Table 3-1. Pin Descriptions

| Pin Number | PD70101 Pin<br>Name | PD70201 Pin Name | Description                                                                                                                                                                                       |

|------------|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RDET                | RDET             | Valid Detection Resistor: Connect a 24.9 k $\Omega$ , 1% resistor from this pin to VPP.                                                                                                           |

| 2          | PGOOD               | PGOOD            | Open Drain Output (active low): This flag is generated to indicate the power rails (VPN_OUT) are ready.                                                                                           |

| 3          | RREF                | RREF             | Bias current resistor for the PD Interface. Connect a 240k 1% resistor between this pin and VPN_IN.                                                                                               |

| 4          | RCLASS              | RCLASS           | Power Classification Setting: Connect external class resistor between this pin and VPN_IN.                                                                                                        |

| 5          | VPN_IN              | VPN_IN           | VPort Negative Input: Connected to the isolating switch input N-channel MOSFET source.                                                                                                            |

| 6          | N/C                 | N/C              | Not used.                                                                                                                                                                                         |

| 7          | N/C                 | AT_FLAG          | Open Drain Output (active low): This flag indicates if the chip detects an IEEE 802.3at compliant PSE.                                                                                            |

| 8          | VPN_OUT             | VPN_OUT          | VPort Negative Output: Connected to the isolating switch output. N-channel MOSFET Drain.                                                                                                          |

| 9          | N/C                 | N/C              | Not Used.                                                                                                                                                                                         |

| 10         | ENABLE              | ENABLE           | Logic level Enable input for DC-DC controller. Pulling this<br>pin to VL turns on the DC-DC controller. This allows the<br>DC-DC controller to be turned on without power to the PD<br>interface. |

# **Pin Configuration**

| continue   | d                   |                  |                                                                                                                                                                                                                                                                        |

|------------|---------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | PD70101 Pin<br>Name | PD70201 Pin Name | Description                                                                                                                                                                                                                                                            |

| 11         | VINS                | VINS             | VPP input voltage sensing for UVLO comparator. Connect to an external resistor divider from VPP to GND. Threshold is 1.2 V reference.                                                                                                                                  |

| 12         | HYST                | HYST             | Output of the VINS/UVLO comparator. This pin is used for VPP UVLO hysteresis programming.                                                                                                                                                                              |

| 13         | SYNC                | SYNC             | External Clock synchronization for the DC-DC controller.<br>Connect an external clock as defined in the EC table<br>to this pin to synchronize the DC-DC converter switching<br>frequency to this clock. PG rising edge is synchronized with<br>the clock rising edge. |

| 14         | RFREQ               | RFREQ            | DC-DC Switching Frequency Setting. Connect a resistor from this pin to GND to set the switching frequency.                                                                                                                                                             |

| 15         | SS                  | SS               | Soft-start: Connect a capacitor from this pin to GND to set<br>the soft-start time of the DC-DC converter. This capacitor is<br>charged with an internal current source to 1.2 V.                                                                                      |

| 16         | RCLP                | RCLP             | Low Power Mode Clamp. Connect a resistor from this pin to GND to program the LPM clamping voltage or connect this pin to GND to disable LPM.                                                                                                                           |

| 17         | VSN                 | VSN              | Differential Amplifier's negative input. Connect this to the junction of a resistor divider from Vo- to GND for the Direct Buck converter application.                                                                                                                 |

| 18         | VSP                 | VSP              | Differential Amplifier's positive input. Connect this to the junction of a resistor divider from Vo+ to GND for the Direct Buck converter application.                                                                                                                 |

| 19         | COMP                | COMP             | Error Amplifier Output. Short to FB pin when driven directly<br>with an optoisolator for Isolated DC-DC Converter. Connect<br>to FB via RC compensation networks for Non-Isolated<br>Direct Buck Converter.                                                            |

| 20         | DAO                 | DAO              | Differential Amplifier Output. Connect to FB (externally) for Non-Isolated Direct Buck Converter.                                                                                                                                                                      |

| 21         | FB                  | FB               | Inverting Input of the Error Amplifier. Connect to opto-<br>coupler for Isolated DC-DC. Connect to RC compensation<br>networks for Non-isolated DC-DC.                                                                                                                 |

| 22         | GND                 | GND              | This is Analog GND. Connect to a local AGND plane. Soft-<br>start capacitor and the frequency setting resistor return to<br>this local GND plane.                                                                                                                      |

| 23         | VL                  | VL               | 5 V (GND reference) internal LDO Output. Connect a 1 $\mu F$ or higher ceramic cap from VL to GND.                                                                                                                                                                     |

| 24         | SG                  | SG               | Secondary Gate Driver. Output is the compliment of PG output. Leave open (NC) if not used. SG is low when in Low Power Skip Mode.                                                                                                                                      |

| 25         | PGND                | PGND             | This is the Power Ground. Connect to a local PGND plane.<br>Input, VCC decoupling capacitors, PG and SG drivers.<br>Primary current sense resistor return to this PGND.                                                                                                |

# **Pin Configuration**

| continue   | d                   |                  |                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | PD70101 Pin<br>Name | PD70201 Pin Name | Description                                                                                                                                                                                                                                                                                                                                                            |

| 26         | CSN                 | CSN              | Negative Input of the Current Sense Amplifier. Kelvin connect to the PGND side of the primary current sense resistor.                                                                                                                                                                                                                                                  |

| 27         | CSP                 | CSP              | Positive Input of the Current Sense Amplifier. Kelvin connect to the Non-PGND side of the primary current sense resistor.                                                                                                                                                                                                                                              |

| 28         | PG                  | PG               | Primary Gate Driver. Connect to the gate of the primary side<br>Power MOSFET, directly or via a resistor.                                                                                                                                                                                                                                                              |

| 29         | VH                  | VH               | 5V High side ( VCC reference) internal LDO Output. Connect a 0.1 $\mu F$ or higher ceramic cap from VH to VCC.                                                                                                                                                                                                                                                         |

| 30         | VCC                 | VCC              | Input Supply to the DC-DC Controller. Connect a 4.7 $\mu$ F or higher ceramic capacitor from this pin to PGND. Alternately, a parallel combination of 1 $\mu$ F ceramic and greater than 10 $\mu$ F electrolytic capacitor can be used.                                                                                                                                |

| 31         | VAUX                | VAUX             | Auxiliary voltage reference to VPN_OUT; this voltage can be<br>used for DC-DC start up when operated with a bootstrapped<br>voltage source. For applications with POE power only<br>connect directly to VCC; for applications using multiple<br>power sources (such as a wall adapter), connect to VCC<br>pin through a small, low current, 30 V rated schottky diode. |

| 32         | VPP                 | VPP              | This is the positive terminal of the POE input port. Connect to the positive terminal of the input bridges at the CDET positive side.                                                                                                                                                                                                                                  |

| EP         | Exposed Pad         | Exposed Pad      | Thermal Pad; electrically connected to VPN_IN. For proper thermal management should be tied to a large copper fill or plane that is electrically connected to VPN_IN.                                                                                                                                                                                                  |

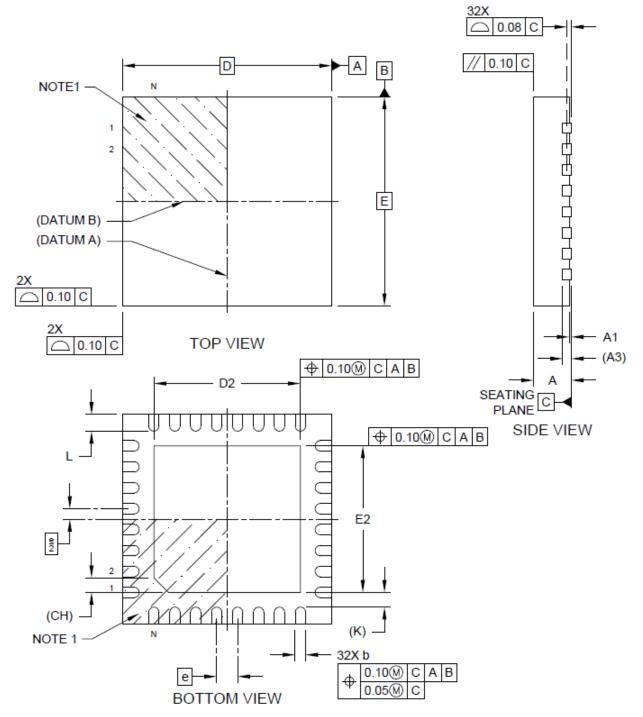

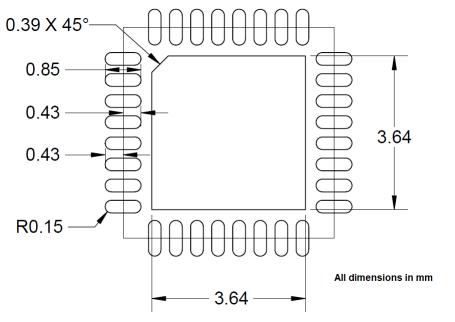

# 4. Package Specifications

The following section describes the package information of the PD70101/PD70201 device.

Figure 4-1. Package Outline Diagram

Dimensions do not include protrusions; these shall not exceed 0.155 mm (0.006") on any side; lead dimension shall not include solder coverage. Dimensions are in millimeters. Inches are for reference only.

The following table lists the dimensions for the PD70101/PD70201 package.

## Package Specifications

| Units                   |    | Millimeters |      |      |

|-------------------------|----|-------------|------|------|

| Dimension Limist        |    | Min         | Nom  | Мах  |

| Number of terminals     | Ν  | —           | 32   | —    |

| Pitch                   | е  | 0.50 BSC    |      |      |

| Overall height          | А  | 0.80        | 0.90 | 1.00 |

| Standoff                | A1 | 0.00        | 0.02 | 0.05 |

| Terminal thickness      | A3 | 0.20 REF    |      |      |

| Overall length          | D  | 5.00 BSC    |      |      |

| Exposed pad length      | D2 | 3.40        | 3.50 | 3.60 |

| Overall width           | E  | 5.00 BSC    |      |      |

| Exposed pad width       | E2 | 3.40        | 3.50 | 3.60 |

| Terminal width          | b  | 0.20        | 0.25 | 0.30 |

| Terminal length         | L  | 0.30        | 0.40 | 0.50 |

| Terminal-to-exposedp-ad | К  | 0.35 REF    |      |      |

| Index corner chamfer    | СН | 0.35 REF    |      |      |

#### Table 4-1. Package Dimensions

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- a. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- b. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 4. For the most current package drawings, please see the Microchip Packaging Specification located at www.microchip.com/packaging.

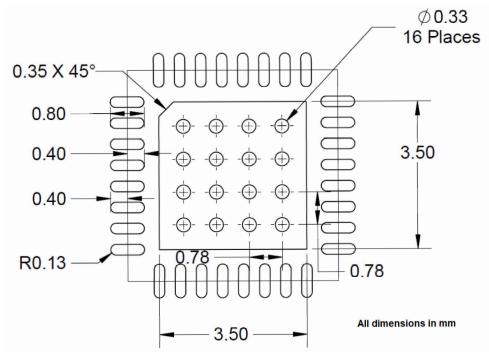

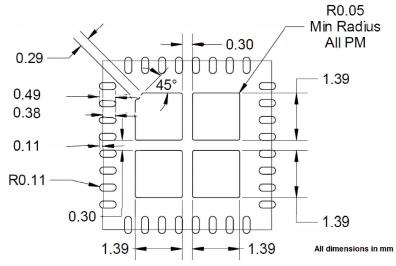

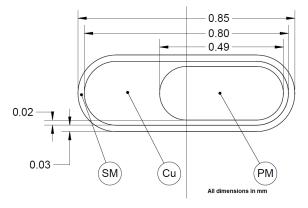

## 5. Recommended PCB Layout

The following figures show the PD70101/201 recommended PCB layout for 32-pin QFN 5 mm × 5 mm.

### Figure 5-1. Solder Mask

Figure 5-2. Top Layer Copper

#### Figure 5-3. Paste Mask

**Note:** Paste mask stencil is 5 mm thick. All paste mask openings have a radius of 0.05 mm.

#### Figure 5-4. Pin Geometry

## 6. Theory of Operation

The PD70101/PD70201 device theory of operation is described in the following sections.

The PD70101/PD70201 IC integrates IEEE 802.3af/at compliant PD front-end functions including Detection, Physical Layer Classification, Two-events Classification (PD70201 only), Power Good, Soft Start Current Limiting, Over-Current Protection, and Bulk Capacitor Discharge with a PWM controller. The integrated PWM controller function provides a PWM controller solution with a minimum requirement of external components.

### 6.1 Detection

IEEE 802.3af/at-compliant detection is provided by means of a 24.9 K $\Omega$  resistor connected between VPP and RDET pin. RDET pin is connected to VPN\_IN via an open drain MOSFET with a maximum specified RDSON of 50  $\Omega$ . Internal logic monitors VPP to VPN\_IN and connects the RDET pin to VPN\_IN when the rising VPP to VPN\_IN voltage is between 1.1 V and 10.1 V. When rising VPP to VPN\_IN voltages exceed 10.1 V, the MOSFET is switched off. Once above 10.1 V, falling VPP to VPN\_IN voltage between 2.45 V and 4.85 V will reconnect RDET pin to VPN\_IN.

### 6.2 Physical Layer Classification

Physical Layer (hardware) Classification per IEEE 802.3af/at is generated via a regulated reference voltage of 1.2 V, switched onto the RCLASS pin. Internal logic monitors the VPP to VPN\_IN voltage and connects the 1.2 V reference to RCLASS pin at a rising VPP to VPN\_IN voltage threshold between 11.4 V and 13.7 V. Once VPP to VPN\_IN has exceeded the rising threshold, there is a 1 V typical hysteresis between the VPP rising (turn-on) threshold and the VPP falling (turn-off) threshold.

The1.2 V reference stays connected to the RCLASS pin until the VPP to VPN\_IN rising voltage exceeds the upper turn-off threshold of 20.9 V to 23.9 V. The 1.2 V reference voltage is disconnected from the RCLASS pin at VPP to VPN\_IN voltages above the upper threshold.

Classification current signature is provided via a resistor connected between RCLASS pin and VPN\_IN. The classification current is therefore the current drawn by the PD70101/PD70201 IC during the classification phase, and is simply the 1.2 V reference voltage divided by the RCLASS resistor value. The maximum current available at the RCLASS pin is current limited to 68 mA (typical).

### 6.3 Two-Events Detection and AT Flag

The PD70201 IC provides IEEE 802.3at Type 2 compliant detection of the two-events classification signature, and generation of the AT flag. This feature is available on the PD70201 IC only.

The two-events classification signature is a means by which an IEEE 802.3at Type 2 Power Source can inform a compliant PD that it is AT Type 2 compliant, and as such is capable of providing AT Type 2 power levels.

The Power Source communicates the Type 2-compliant signature by toggling the VPP to VPN\_IN voltage twice (2 events) during the Physical Layer Classification phase. The VPP to VPN\_IN voltage is toggled from the Physical Layer Classification's voltage level (13.5 V to 20.9 V) down to a voltage Mark level. Voltage Mark level is specified as a VPP to VPN\_IN voltage of 4.9 V to 10.1 V.

PD70201 IC recognizes a VPP to VPN\_IN falling edge from Classification level to Mark level as being one event of the Two-Events Signature. If two such falling edges are detected, PD70201 will assert with 80 ms delay AT flag by means of an open drain MOSFET connected between AT\_FLAG pin and VPN\_OUT.

AT\_FLAG pin is active low; a low impedance state between AT\_FLAG and VPN\_OUT indicates a valid Two- Events Classification Signature was received, and the Power Source is AT Type 2 compliant.

AT\_FLAG MOSFET is capable of 5 mA of current and can be pulled up to VPP.

### 6.4 Soft Start and Inrush Current Protection

PD70101/PD70201 IC contains an internal isolation switch that provides ground isolation between power source and PD application during Detection and Classification phases. The isolation switch is a N- channel MOSFET, wired in a common source configuration where the MOSFET's Source is connected to Power Source ground at VPN\_IN, and the MOSFET's Drain is connected to application's primary ground at VPN\_OUT.

Internal logic monitors VPP to VPN\_IN voltage and keeps the MOSFET in a high impedance state until VPP to VPN\_IN voltage reaches turn-on threshold of 36 V to 42 V. Once VPP to VPN\_IN voltage exceeds this threshold, the MOSFET is switched into one of two modes.

Mode into which the MOSFET is switched is determined by the voltage developed across the MOSFET, or put another way, the VPN\_OUT to VPN\_IN differential voltage. Two modes are defined as in the following table.

#### Table 6-1. Isolation Switch Modes

| VPN_OUT to VPN_IN | Mode             | Description                                |

|-------------------|------------------|--------------------------------------------|

| ≥0.7 V            | Soft start       | Limits VPN_OUT current to 240 mA (typical) |

| ≤0.7 V            | Normal operating | Limits VPN_OUT current to 1.8 A (typical)  |

By controlling the MOSFET current based on VPN\_OUT to VPN\_IN voltage, inrush currents generated by fully discharged bulk capacitors can be limited. This method limits current to a maximum of 350 mA, compliant with IEEE 802.3af/at specification.

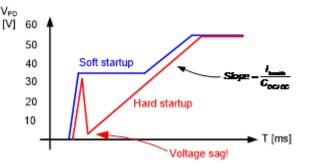

Soft Start current limiting is required to reduce occurrences of voltage sag at the PD input during device power-up. A comparison is shown in figure 3 (see page 7).

#### Figure 6-1. Comparison of Input Voltages without Soft-start (Hard Startup) and Soft-start (Soft Startup)

Once bulk capacitance has charged up to a point where VPN\_OUT to VPN\_IN differential voltage is less than 0.7 V, the isolation MOSFET is switched into normal operating mode with MOSFET current limit set at 1.8 A (typical), to provide over-current protection.

PD70101 and PD70201 ICs are different in their respective isolation MOSFET's continuous current handling capability. The maximum isolation MOSFET's continuous current handling capability is 450 mA for PD70101 and 1123 mA for PD70201.

An adequate heat sink for the PD70101/PD70201 IC's exposed pad must be provided to achieve these current levels without damaging the IC. A large, heavy copper fill area and/or a heavy ground plane with Thermal vias are recommended.

Internal logic monitoring VPP to VPN\_IN will place the isolation switch MOSFET in a high impedance state if voltage between VPP and VPN\_IN drops below 31 V to 34 V.

## 6.5 Over-Current Protection

An over-current protection is provided on the PD70101/PD70201 IC using the Isolation Switch MOSFET, which limits the VPN\_OUT current to 1.8 A during normal operation. See previous description of Soft Start.

### 6.6 Power Good

During Soft Start mode, the PD70101/PD70201 IC monitors VPN\_OUT to VPN\_IN differential voltage. When this voltage is less than 0.7 V (maximum), the IC enters normal operation mode and the isolation switch current limit is increased to 1.8 A (typical). At this same 0.7 V (maximum) threshold the Power Good signal is asserted by means of an open drain MOSFET between PGOOD and VPN\_OUT.

PGOOD pin is active low; a low impedance state between PGOOD and VPN\_OUT indicates the Soft Start mode has finished and the isolation switch has transitioned into normal operating mode.

PGOOD MOSFET can handle current of 5 mA and can be pulled up to VPP.

The application load should begin after no less than 80 ms after PGOOD is activated according to IEEE 802.3.

### 6.7 Start-Up Supply

PD70101/PD70201 IC provides a 10.5 V (typical) regulated output used as a start-up supply for the integrated DC/DC controller when VCC is provided via a bootstrap winding. This regulated supply is available at VAUX pin, and is referenced to VPN OUT pin. The VAUX start-up supply is current-limited at 10 mA (minimum).

For stability, the start-up regulator requires a minimum of 4.7 µF ceramic capacitor connected directly between VAUX and PGND pins (most applications will connect PGND to VPN\_OUT).

For applications where power to the DC-DC controller is provided by POE only, the VAUX pin is connected directly to VCC. For applications which have alternate power sources (such as a wall adaptor), the VAUX pin output is connected to the VCC pin through a series diode. This diode is typically a low current diode with a 30 V rating.

### 6.8 PD Interface Thermal Protection

Both PD70101 and PD70201 IC contain temperature sensors which individually monitor both the isolation MOSFET and the classification current source for over temperature conditions. In case of an over temperature condition, the sensor will activate protection circuitry which will disconnect its respective monitored function.

### 6.9 Bulk Capacitor Discharge

The bulk capacitor discharge circuitry eliminates the need to place a diode in series with the VPP line to prevent an application's bulk capacitance from discharging through the detection resistor and the isolation switch MOSFET's body diode. Discharge current through the detection resistor can cause failure of the detection signature in cases where a PD is connected and the bulk capacitance is not fully discharged.

During normal operation, PD70101/PD70201 IC continuously monitors voltage at VPP to VPN\_IN. Should VPP to VPN\_IN voltage fall below isolation switch turn-off threshold (31 V to 34 V), isolation switch MOSFET is immediately placed in a high-impedance state. At this point the internal logic monitors the voltage at VPP to VPN\_OUT.

If VPP to VPN\_OUT voltage is between 1.5 V to 32 V, minimum 23 mA constant current source is connected across the VPP and VPN OUT pins. This constant current source provides bulk capacitor discharge.

A 220  $\mu F$  bulk capacitance can be discharged from 32 V to 1.5 V in a maximum period of 292 ms.

### 6.10 DC-DC Start-Up

The DC-DC controller starts up when it receives the PGOOD high signal from the front-end, or ENABLE goes high provided that VCC UVLO have passed. When the PGOOD signal or ENABLE goes high, the start- up sequence begins with ramping up the SS pin from GND to 1.2 V. For isolated applications the output voltage may reach the maximum level before the SS reaches 1.2 V, depending on the output loading condition. In applications with lighter loads, the output reaches regulation level sooner than in heavy loads, as in this mode the SS voltage directly controls the peak inductor current; hence the energy is delivered to the load. The external secondary error amplifier regulates the output voltage and controls the peak inductor current via the opto-coupler across the isolation barrier.

For non-isolated applications, because the internal error amplifier is used to close the regulation loop, the output reaches the regulation level when SS reaches 1.2 V.

An additional internal offset is added to the FB to ensure that COMP does not reach its upper limit because of amplifier input offset. This offset is removed (slowly to avoid overshoot) when the SS ramp is complete.

Low Power mode is not supported during SS ramp as it is not necessary.

## 6.11 Current Limit and Short Circuit Protection

The DC-DC converter is a peak current mode controller; an internal current sense amplifier with a gain of 5 monitors the voltage across an external current sense resistor and regulates the output based on the current through the resistor. If the output of the internal current sense amplifier reaches 1.2 V, the converter will truncated the PWM output, and thus limit the output current.

If the output of the internal current sense amplifier reaches 1.8 V, the controller enters hiccup mode by discharging the SS capacitor with a constant current that equals 10% of the charging current during ramp up.

This discharge continues until VSS = 50 mV where an internal ~50  $\Omega$  MOSFET connected to SS turns on for 25 clock cycles to ensure the SS capacitor fully discharges to GND before ramping back up and restart. The converter will exit the hiccup mode when the over current condition is removed.

### 6.12 Low Power Mode Operation

The devices offer a pulse skipping operation for light load condition, referred to as Low Power Mode (LPM), to improve the efficiency of light load operation by reducing the power dissipation especially in high frequency switching. Using an external resistor from RCLP pin to GND, the user can program the output power when the unit enters pulse skipping.

Pulse skipping mode is disabled until SS ramp is completed, regardless of the LPM status.

### 6.13 Input (VPP and VCC) Under Voltage Lock Out

The PD interface circuit offers an internal PGOOD signal that can be used to start the DC-DC converter; however, the threshold of the PGOOD is fixed at VPN\_OUT-VPN\_IN  $\leq 0.7$  V. This may not fit all possible applications. Therefore, the device offers an option to have a programmable UVLO which is tied to level of VPP-VPN\_OUT, plus a programmable hysteresis. The voltage developed across a simple resistor divider is sensed at VINS, and will enable/disable the PWM controller at a nominal 1.2 V threshold. A third resistor connected between VINS and HYST pins allows programmable hysteresis. This feature enables the end user to tailor to any desired systems application's requirement for turn on and turn off time. In addition to the VPP sensing for UVLO, the devices also have VCC UVLO to ensure that the PWM controller is always properly powered during operation. These features provide robust solutions under various systems disturbances.

### 6.14 External Enable