## Product Change Notification / SYST-16YHFI013

## Date:

17-Dec-2021

## **Product Category:**

PoE PSE

## PCN Type:

**Document Change**

## **Notification Subject:**

Data Sheet - PD69101 Datasheet Document Revision

## **Affected CPNs:**

```

SYST-16YHFI013_Affected_CPN_12172021.pdf

SYST-16YHFI013_Affected_CPN_12172021.csv

```

## Notification Text:

SYST-16YHFI013

Microchip has released a new Product Documents for the PD69101 Datasheet of devices. If you are using one of these devices please read the document located at PD69101 Datasheet.

#### Notification Status: Final

#### **Description of Change:**

- 1) The following is a summary of changes in revision A of this document:

- The document was updated to latest Microchip template.

- The document number was changed from PD-000308061 to DS00004280A.

#### Impacts to Data Sheet: None

Reason for Change: To Improve Manufacturability

Change Implementation Status: Complete

#### Date Document Changes Effective: 17 Dec 2021

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

## **Attachments:**

PD69101 Datasheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile, including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

Affected Catalog Part Numbers (CPN)

PD69101ILQ-13155TR PD69101ILQ-13155TR PD69101ILQ-TR PD69101ILQ-TR

# **1-Port PSE PoE Controller Datasheet**

## Introduction

Microchip's PD69101 device is a single-port, mixed-signal, and high-voltage Power over Ethernet (PoE) driver. It is utilized in Ethernet switches and enables the network devices to share power and data over the same cable. It enables detection of IEEE<sup>®</sup> 802.3af-2003 compliant powered devices (PDs) and IEEE 802.3at high-power devices, ensuring safe power feeding and disconnection of ports, with full digital control and a minimum of external components. A plug-and-play device, the PD69101 executes all real-time functions as specified in the IEEE 802.3af-2003 (AF) and IEEE 802.3at high-power (AT) standards, including load detection, AF and AT classification, and multiple classification attempts (MCA).

Integrating power, analog, and state-of-the-art logic, the PD69101 fits into a single 24-pin plastic QFN package. The chip includes built-in internal thermal protection, and two LEDs provide port state and port type (AF/AT) indication.

PD69101 device offer the following important features.

- Designed to detect and disable disconnected ports, utilizing DC disconnection methods as specified in the AF and IEEE802.3 af/at standards.

- Low-power device using an internal  $0.34\Omega$  MOSFET and an external  $0.5\Omega$  sense resistor.

- · Optionally detects legacy/pre-standard PD devices.

- Provides overload, underload, overvoltage, overtemperature, and short-circuiting PD protection.

- Supports supply voltages ranging from 32V to 57 VDC with no need for additional power supply sources.

# Features

The PD69101 device has the following key features.

- Fully AF and AT compliant

- Includes two-event classification

- Supports pre-standard PD detection

- Single DC voltage input (32V–57 VDC)

- Supports 2-pairs

- V<sub>MAIN</sub> out-of-range protection

- Wide temperature range: -40°C to 85°C

- Overtemperature protection

- Low thermal dissipation (0.5Ω sense resistor)

- Includes on/off command pin

- 2× direct LEDs drive

- Continuous port monitoring and system data

- Configurable load current setting

- Configurable AT/AF modes

- Configurable standard and legacy detection mode

- Power soft-start mechanism

- On-chip thermal protection

- Voltage monitoring and protection

- Built-in 3.3 VDC regulator

- Internal power-on-reset

- RoHS compliant

- Low Rdson FET: 0.3Ω

- MSL3

# **Typical 2-Pair Application**

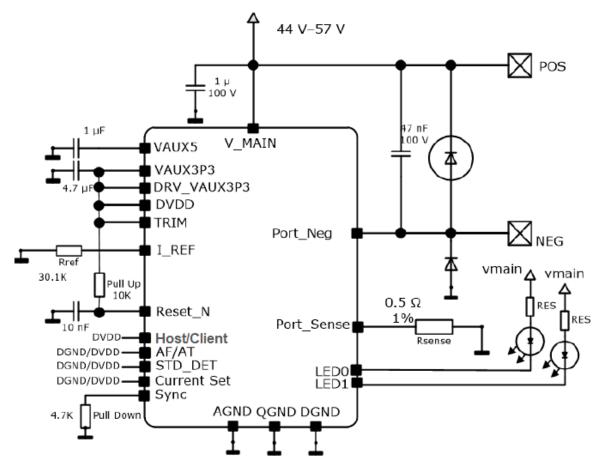

The following figure shows a typical application of simple plug-and-play PoE solution for a single Ethernet port switch or hub. POS and NEG signals must be connected to the switch RJ45 jack. AF and AT modes of operations are set through AF/AT and current-set pins (DGND or DVDD).

### Figure 1. Typical 2-Pair Application

# **Table of Contents**

| Intr                                      | Introduction1               |                                     |      |  |  |  |

|-------------------------------------------|-----------------------------|-------------------------------------|------|--|--|--|

|                                           | Featu                       | res                                 | 2    |  |  |  |

|                                           | Typica                      | al 2-Pair Application               | 3    |  |  |  |

| 1.                                        | Funct                       | onal Description                    | 5    |  |  |  |

|                                           | 1.1.                        | Logic Main Control Module           |      |  |  |  |

|                                           | 1.2.                        | Application Information             | 6    |  |  |  |

| 2.                                        | Electr                      | ical Specifications                 | 11   |  |  |  |

|                                           | 2.1.                        | Dynamic Characteristics             | 12   |  |  |  |

|                                           | 2.2.                        | Absolute Maximum Ratings            |      |  |  |  |

|                                           | 2.3.                        | Moisture Sensitivity                |      |  |  |  |

|                                           | 2.4.                        | Power Dissipation Information       | 14   |  |  |  |

| 3.                                        | Pin D                       | escriptions                         | . 15 |  |  |  |

|                                           | 3.1. CURRENT_SET and AF/AT  |                                     |      |  |  |  |

|                                           | 3.2.                        | Mode of Operation Coding            |      |  |  |  |

|                                           | 3.3.                        | LED I/Os Behavior                   | 18   |  |  |  |

| 4.                                        | Packa                       | ge Specifications                   | . 20 |  |  |  |

|                                           | 4.1.                        | RoHS and Solder Reflow Information  |      |  |  |  |

|                                           | 4.2.                        | Thermal Specifications              | . 22 |  |  |  |

|                                           | 4.3.                        | Tape and Reel—Packaging Information | .22  |  |  |  |

| 5.                                        | Order                       | ing Information                     | . 24 |  |  |  |

| 6.                                        | Revis                       | on History                          | . 25 |  |  |  |

| The                                       | Micro                       | chip Website                        | .27  |  |  |  |

| Pro                                       | duct C                      | nange Notification Service          | 27   |  |  |  |

| Cus                                       | stomer                      | Support                             | . 27 |  |  |  |

| Microchip Devices Code Protection Feature |                             |                                     |      |  |  |  |

|                                           | Legal Notice                |                                     |      |  |  |  |

| Trademarks                                |                             |                                     |      |  |  |  |

|                                           |                             |                                     |      |  |  |  |

| Quality Management System                 |                             |                                     |      |  |  |  |

| Wo                                        | Worldwide Sales and Service |                                     |      |  |  |  |

# 1. Functional Description

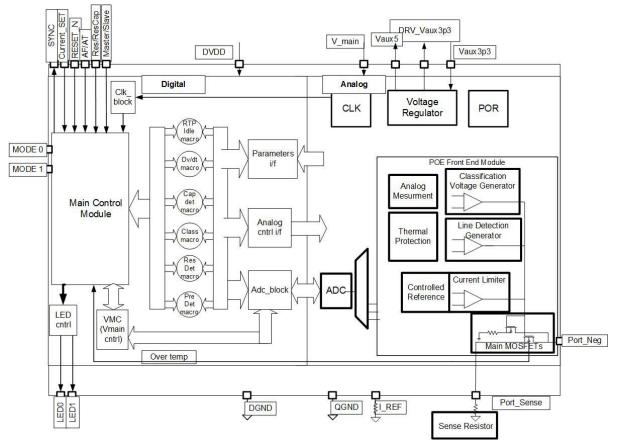

The PD69101 device has two sections, listed as follows:

- · A digital section that controls and monitors the logical PoE functions (state machines, timings, and so on)

- An analog section that performs the front-end analog PoE functionality

The following figure shows the internal functional blocks of the PD69101 device.

Figure 1-1. PD69101 Internal Block Diagram

## 1.1 Logic Main Control Module

The logic main control block includes the following digital timing mechanisms and state machines, synchronizing, and activating the PoE functions.

- Real-Time Protection (RTP)

- Start-up macro (DVDT)

- Load signature detection (RES DET)

- Classification macro (CLASS)

- Voltage and current monitoring registers (VMC)

- LEDs stream out control indications

- ADC interfacing

- Direct digital signals with analog block

#### 1.1.1 Line Detection Generator

Upon request from the main control module, four different voltage levels are generated by the line detection generator, ensuring robust AF/AT line detection functionality.

#### 1.1.2 Classification Generator

Upon request from the main control module, the state machine applies a regulated class event and mark event voltage to the ports, as required by the IEEE standard.

#### 1.1.3 Current Limiter

This circuit continuously monitors the current of powered ports and limits the current to a specific value, according to the pre-defined limits set by AF/AT and current\_set pins. In cases where the current exceeds this specific level, the system starts measuring the elapsed time. If this time period is greater than a preset threshold, the port is disconnected.

#### 1.1.4 Main MOSFET

Main power switching FET, used to control PoE current into the load.

### 1.1.5 Analog-to-Digital Converter (ADC)

A 10-bit analog-to-digital converter, used to convert analog signals into digital registers for the logic control module.

#### 1.1.6 Power-on Reset (POR)

This circuit monitors the internal 3.3 VDC levels. If this voltage drops below specific thresholds, a reset signal is generated and the PD69101s are reset.

#### 1.1.7 Voltage Regulator

The voltage regulator generates 3.3 VDC and 5 VDC for the internal circuitry. These voltages are derived from the  $V_{MAIN}$  supply.

#### 1.1.8 CLK

CLK is an internal 8 MHz clock oscillator.

### 1.2 Application Information

The PD69101 performs IEEE 802.3af and IEEE 802.3at functionality as well as legacy (capacitor) and Cisco PD detection, in addition to protections such as short circuit and dV/dT protection upon startup.

#### 1.2.1 Line Detection

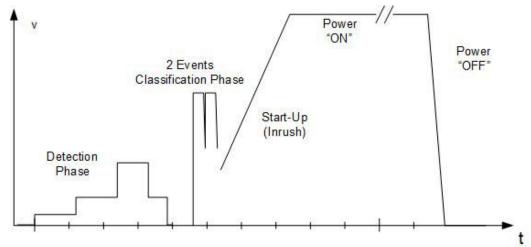

The line detection feature detects a valid AF or AT load, as specified in the AF/AT standard. The resistor value should range from 19 K $\Omega$  to 26.5 K $\Omega$ . Line detection is based on four different voltage levels generated over the PD (the load), as shown in the following figure.

#### Figure 1-2. Typical PoE Voltage Timing Diagram

### 1.2.2 Legacy (Capacitor) Detection

In cases where pin 24 is set to 0, the PD69101's detection mechanism is configured to detect and power-up legacy PDs, as well as AF/AT compliant. This mechanism also detects and powers up Cisco legacy PDs.

#### 1.2.3 Classification

The classification process takes place right after the resistor detection, is successfully completed. The main goal of the classification process is to detect the PD class, as specified in the IEEE802.3af and IEEE 802.3at standards. In IEEE 802.3af mode, the classification mechanism is based on a single voltage level (single class event). In IEEE 802.3at mode, the classification mechanism is based on two voltage levels (dual class event) as defined in IEEE 802.3at 2009. In IEEE 802.3at mode, when the PD is class 0–3, the PD69101 generates a single class event. When the PD is class 4, the PD69101 generates two class events.

#### 1.2.4 Port Start Up

Upon a successful detection and classification process, power is applied to the load through a controlled start-up mechanism. During this period, current is limited to 425 mA for a typical duration of 65 mS, which enables the PD load to charge and enter a steady state power condition.

#### 1.2.5 Over-Load Detection and Port Shut Down

After power-up, the PD69101 automatically initializes its internal protection mechanisms to monitor and disconnect power from the load in cases where extreme conditions (such as over-current or short port terminal scenarios) occur, as specified in the IEEE 802.3af/at standard.

#### 1.2.6 Disconnect Detection

The PD69101 supports the DC disconnect function as per the IEEE 802.3af/at standard. This mechanism continuously monitors the load current and disconnects power in cases where the load current is below 7.5 mA (typical) for more than 322 mS.

#### 1.2.7 Overtemperature Protection

The PD69101 has internal temperature sensors that continuously monitor junction temperature and disconnect load power when the junction temperature exceeds 200 °C. This mechanism protects the device from extreme events such as high ambient temperature or other thermo-mechanical failures that might damage the PD69101 device.

#### 1.2.8 V<sub>MAIN</sub> Out-of-Range Protection

The PD69101 automatically disconnects port power when  $V_{MAIN}$  exceeds 57.5 VDC ±0.5 VDC. This is an extremely valuable feature that protects the load, if the main power source is faulty or damaged.

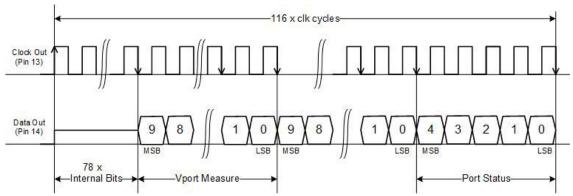

### 1.2.9 Serial Communication: Monitoring Mode

When MODE0 and MODE1 input pins are configured to serial monitoring mode (01), the PD69101 continuously and repeatedly transmits out the content of nine internal registers.

- Data out stream is transmitted through LED1 (pin 14)

- Clock out stream is transmitted through LED0 (pin 13)

- Data stream is shifted out with a 1 MHz clock (1 µsec)

- Total transaction packet length is 116 µsec

- The transmission is repeated every 1 msec

- Between transactions, the clock is held low while the data stream out is stable high/low.

Note: To exploit LED1 and LED0 to communicate and monitor transmissions, use a 1 K $\Omega$  pull-up resistor to the DVDD.

The following table lists the stream out data transmits of 116 bits, starting from MSB to LSB.

#### Table 1-1. Serial Monitoring Mode

| MSB                                      |            |            |                                                                   |                                                                    |                                                                      |                                                                                    |         | LSB         |

|------------------------------------------|------------|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------|---------|-------------|

| Internal 0                               | Internal 1 | Internal 2 | Internal 3                                                        | Internal 4                                                         | VPORT                                                                | VMAIN                                                                              | IPORT   | Port Status |

| 13 bits                                  | 10 bits    | 23 bits    | 16 bits                                                           | 16 bits                                                            | 10 bits                                                              | 10 bits                                                                            | 13 bits | 5 bits      |

| J. J |            |            | Port voltage<br>measurement<br>LSB= 58 mV<br>V= Decimal ×58<br>mV | VMAIN voltage<br>measurement<br>LSB= 58 mV<br>V= Decimal ×58<br>mV | Port current<br>measurement<br>LSB= 238 µA<br>I= Decimal ×<br>238 µA | Real-time port<br>status indication.<br>For more<br>information, see<br>Table 1-2. |         |             |

The following table lists the port status coding.

### Table 1-2. Port Status Coding

| Binary MSB to LSB | Decimal Value | Description               |

|-------------------|---------------|---------------------------|

| 00000             | 0             | PoE idle state            |

| 00001             | 1             |                           |

| 00010             | 2             |                           |

| 00011             | 3             | Searching phase           |

| 00100             | 4             | Res detection phase       |

| 00101             | 5             | Back OFF phase            |

| 00110             | 6             |                           |

| 00111             | 7             | Class phase               |

| 01000             | 8             |                           |

| 01001             | 9             | Wait for start-up         |

| 01010             | 10            |                           |

| 01100             | 11            |                           |

| 01011             | 12            | Cap detection             |

| 01101             | 13            | Start-up                  |

| 01110             | 14            |                           |

| 01111             | 15            | Ongoing                   |

| 10000             | 16            |                           |

| 10001             | 17            | UDL                       |

| 10010             | 18            | Overload or short circuit |

| 10011             | 19            | VMAIN out of range        |

| 10100             | 20            |                           |

The following figure shows the data stream out.

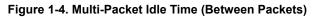

The following figure shows the multi-packet idle time between packets.

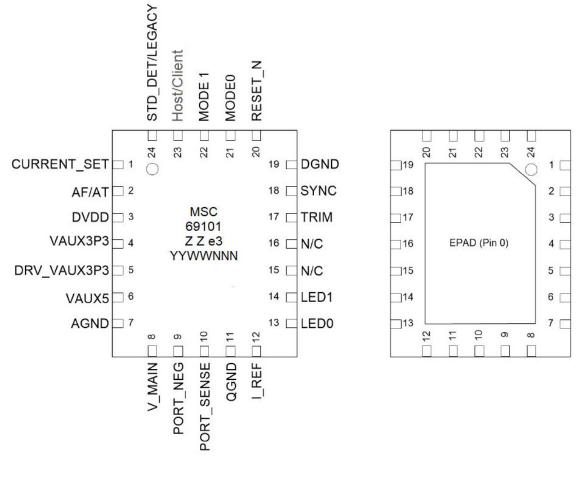

The following figure shows the data/clock typical timing.

#### Figure 1-5. Data/Clock Typical Timing

# 2. Electrical Specifications

Unless otherwise specified, the following specifications apply to the operating ambient temperature ( $T_{AMB}$ ): -40 °C to 85 °C.

| Parameter                                       | Symbol            | Test<br>Conditions/<br>Comment               | Minimum | ТурісаІ | Maximum | Unit |

|-------------------------------------------------|-------------------|----------------------------------------------|---------|---------|---------|------|

| Input voltage                                   | V <sub>MAIN</sub> | Supports full<br>IEEE 802.3<br>functionality | 32      | 55      | 57      | VDC  |

| Power supply<br>current at<br>operating<br>mode | -                 | V <sub>MAIN</sub> = 55 V                     | -       | -       | 10      | mA   |

### Table 2-1. Power Supply

### Table 2-2. Digital I/O

| Parameter                   | Symbol | Test Conditions/Comment     | Minimum | Typical | Maximum | Unit |

|-----------------------------|--------|-----------------------------|---------|---------|---------|------|

| Input logic, high threshold | VIH    | —                           | 2.2     | —       | —       | VDC  |

| Input logic, low threshold  | VIL    | —                           | _       | _       | 0.8     | VDC  |

| Input hysteresis voltage    | -      | —                           | 0.4     | 0.6     | 0.8     | VDC  |

| Input high current          | ΙΗ     | —                           | -10     | _       | 10      | μA   |

| Input low current           | ΙL     | —                           | -10     | _       | 10      | μA   |

| Output high voltage         | VOH    | For I <sub>OH</sub> = –1 mA | 2.4     | _       | _       | VDC  |

| Output low voltage          | VOL    | I <sub>OH</sub> = 1 mA      | _       | _       | 0.4     | VDC  |

### Table 2-3. PoE Load Currents

| Parameter                | Symbol                                                 | Test Conditions/Comment                                    | Minimum | Typical | Maximum | Unit |

|--------------------------|--------------------------------------------------------|------------------------------------------------------------|---------|---------|---------|------|

| AT, high limit mode      | AT_LIM_HIGH (high<br>current level, for future<br>use) | RSENSE = $0.5 \Omega 1\%$ , connected at<br>Port_Sense pin | 1.18    | 1.2     | 1.28    | A    |

| AT, medium limit<br>mode | AT_LIM_MID (medium current level, for future use)      |                                                            | 847     | 874     | 919     | mA   |

| AT, low limit mode       | AT_LIM_LOW                                             |                                                            | 706     | 722     | 767     | mA   |

| AF, limit mode           | AF_LIM                                                 |                                                            | 410     | 425     | 448     | mA   |

### Table 2-4. Main Power Switching FET

| Parameter                             | Symbol            | Typical | Unit |

|---------------------------------------|-------------------|---------|------|

| On resistance                         | R <sub>DSON</sub> | 0.3     | Ω    |

| Internal thermal protection threshold | -                 | 200     | °C   |

#### Table 2-5. LED0 and LED1 Drivers

| Parameter    | Symbol                                                | Typical | Maximum | Unit |

|--------------|-------------------------------------------------------|---------|---------|------|

| Current sink | I <sub>SINK</sub> (from V <sub>MAIN</sub> to<br>AGND) | 3       | 5       | mA   |

### 2.1 Dynamic Characteristics

The PD69101 device utilizes three current level thresholds ( $I_{MIN}$ ,  $I_{CUT}$ , and  $I_{LIM}$ ) and three timers ( $T_{MIN}$ ,  $T_{CUT}$ , and  $T_{LIM}$ ).

- Loads that consume I<sub>LIM</sub> current for more than T<sub>LIM</sub> are labeled as **short circuit state** and shut down.

- Loads that dissipate more than  $I_{CUT}$  for longer than  $T_{CUT}$  are labeled as overloads and are shut down.

- If output power is below I<sub>MIN</sub> for more than T<sub>MIN</sub>, the PD is labeled as **no load** and is shut down.

Automatic recovery from overload and no load conditions is attempted every TOVLREC periods (typically one second). Output power is limited to I<sub>LIM</sub>, which is a maximum peak current allowed at the port.

| Parameter                                        | Symbol             | Conditions                                                                                                        | Minimum | Typical | Maximum | Unit |

|--------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Automatic recovery from no load shutdown         | —                  | T <sub>UDLREC</sub> value, measured from port<br>shutdown point (can be modified<br>through control port)         |         | 1       |         | sec  |

| Cutoff timer accuracy                            | —                  | Typical accuracy of $T_{cut}$                                                                                     | —       | 2       |         | ms   |

| Inrush current                                   | I <sub>Inrsh</sub> | For t = 50 ms, $C_{load}$ = 180 $\mu$ F (max)                                                                     | 400     | _       | 450     | mA   |

| Output current operating range                   | I <sub>PORT</sub>  | Continuous operation after startup period                                                                         | 10      |         | 375     | mA   |

| Output power available operating range           | P <sub>PORT</sub>  | Continuous operation after startup period, at port output                                                         | 0.57    |         | 15.4    | W    |

| Off-mode current                                 | I <sub>MIN1</sub>  | Must disconnect for T greater than $T_{\text{UVL}}$                                                               | 0       |         | 5       | mA   |

|                                                  | I <sub>MIN1</sub>  | May or may not disconnect when T is greater than $\mathrm{T}_{\mathrm{UVL}}$                                      | 5       | 7.5     | 10      | mA   |

| PD power maintenance request drop-out time limit | T <sub>PMDO</sub>  | Buffer period to handle transitions                                                                               | 300     |         | 400     | ms   |

| Over-load current detection range                | I <sub>CUT</sub>   | Time limited to T <sub>OVL</sub>                                                                                  | 350     | _       | 400     | mA   |

| Over-load time limit                             | T <sub>OVL</sub>   | <u> </u>                                                                                                          | 50      |         | 75      | ms   |

| Turn-on rise time                                | T <sub>RISE</sub>  | From 10% to 90% of Vport (specified for PD load consisting of 100 $\mu$ F capacitor in parallel to 200 $\Omega$ ) | 15      |         |         | μs   |

| Turn-off time                                    | T <sub>OFF</sub>   | From V <sub>PORT</sub> to 2.8 VDC                                                                                 | —       |         | 500     | ms   |

| Time maintain power<br>signature                 | T <sub>MPS</sub>   | DC modulation time for DC disconnect                                                                              |         | 49      | _       | ms   |

#### Table 2-6. IEEE 802.3 af Mode Parameters

| Parameter                                        | Symbol             | Conditions                                                                                                         | Minimum | Typical | Maximum | Unit |

|--------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Automatic recovery from no load shutdown         | _                  | T <sub>UDLREC</sub> value, measured from port<br>shutdown point (can be modified<br>through control port)          |         | 1       |         | sec  |

| Cutoff timer accuracy                            |                    | Typical accuracy of T <sub>cut</sub>                                                                               | —       | 2       | _       | ms   |

| Inrush current                                   | I <sub>Inrsh</sub> | For t = 50 ms, Cload = 180 $\mu$ F (max)                                                                           | 400     | _       | 450     | mA   |

| Output current operating range                   | I <sub>PORT</sub>  | Continuous operation after startup period                                                                          | 10      |         | 725     | mA   |

| Output power available operating range           | P <sub>PORT</sub>  | Continuous operation after startup period, at port output                                                          | 0.57    |         | 36.25   | W    |

| Off-mode current                                 | I <sub>MIN1</sub>  | Must disconnect for T greater than $T_{\text{UVL}}$                                                                | 0       |         | 5       | mA   |

|                                                  | I <sub>MIN2</sub>  | May or may not disconnect when T is greater than $T_{\text{UVL}}$                                                  | 5       | 7.5     | 10      | mA   |

| PD power maintenance request drop-out time limit | T <sub>PMDO</sub>  | Buffer period to handle transitions                                                                                | 300     |         | 400     | ms   |

| Over-load current detection range                | I <sub>CUT</sub>   | Time limited to T <sub>OVL</sub>                                                                                   |         | _       | 600     | mA   |

| Over-load time limit                             | T <sub>OVL</sub>   |                                                                                                                    | 50      | _       | 75      | ms   |

| Turn-on rise time                                | T <sub>RISE</sub>  | From 10% to 90% of Vport (specified for PD load consisting of 100 $\mu$ F capacitor in parallel to 200 $\Omega$ ). | 15      |         |         | μs   |

| Turn-off time                                    | T <sub>OFF</sub>   | From V <sub>PORT</sub> to 2.8 VDC                                                                                  | —       | —       | 500     | ms   |

| Time maintain power signature                    | T <sub>MPS</sub>   | DC modulation time for DC disconnect                                                                               | _       | 49      |         | ms   |

### Table 2-7. IEEE 802.3at Mode Parameters

### 2.2 Absolute Maximum Ratings

The following table lists the absolute maximum ratings for the PD69101. Exceeding these ratings can cause damage to the device. Pin Port\_Sense is ESD sensitive and passes 500V HBM. All voltages are with respect to ground. Currents are marked positive when flowing into a specified terminal and marked negative when flowing out of a specified terminal.

#### Table 2-8. Absolute Maximum Ratings

| Parameter                                 | Rating              |

|-------------------------------------------|---------------------|

| Supply input voltage (V <sub>MAIN</sub> ) | -0.3 VDC to 74 VDC  |

| Port_Neg pin, LED0, LED1                  | -0.3 VDC to 74 VDC  |

| Port_Sense pin                            | -0.3 VDC to 3.6 VDC |

| QGND, AGND pins                           | -0.3 VDC to 0.3 VDC |

| VAUX5                                     | –0.3 V to 5.5V      |

| All other pins                            | -0.3 VDC to 3.6 VDC |

| Operating ambient temperature range       | –40 °C to 85 °C     |

| continued                              |                  |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Parameter                              | Rating           |  |  |  |

| Maximum operating junction temperature | 150 °C           |  |  |  |

| Storage temperature range              | –65 °C to 150 °C |  |  |  |

| ESD protection at all I/O pins         | ±2 KV (HBM)      |  |  |  |

## 2.3 Moisture Sensitivity

This device is rated moisture sensitivity level 3 as specified in the joint IPC and JEDEC<sup>®</sup> standard IPC/JEDEC J-STD-020. For more information, see the *IPC and JEDEC standard*.

## 2.4 Power Dissipation Information

### Table 2-9. Power Dissipation

| Parameter                                                               | Value                           |

|-------------------------------------------------------------------------|---------------------------------|

| Rsense power dissipation                                                | $0.5 \Omega \times I_{PORT^2}$  |

| Rds_ON power dissipation                                                | $0.3 \Omega \times I_{PORT^2}$  |

| Pport_AF = 15.4 W                                                       | PRsense = 51 mW (320 mA)        |

| PRds_ON                                                                 | 31 mW (320 mA)                  |

| Pport_AT = 30 W                                                         | PRsense = 180 mW (600 mA)       |

| PRds_ON                                                                 | 108 mW (600 mA)                 |

| Typical PD69101 self power dissipation (including internal regulations) | 0.5W (50 VDC)                   |

| Typical PD69101 2-pairs AF application power dissipation                | 0.5W + 51 mW + 31 mW = 0.582W   |

| Typical PD69101 2-pairs AT application power dissipation                | 0.5W + 180 mW + 108 mW = 0.788W |

## 3. Pin Descriptions

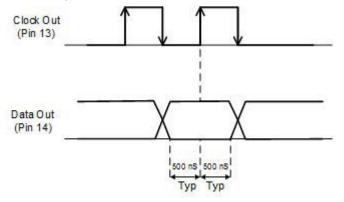

The following figure shows the device pin diagram from the top and bottom views.

### Figure 3-1. PD69101 Pinout

**Top View**

**Bottom View**

The following table lists the pin descriptions for the PD69101 device.

### Table 3-1. Pin Descriptions

| Number | Name        | Туре          | Description                                                                                                                                                                                                                   |

|--------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Exposed PAD | Analog ground | Exposed pad; metal plate<br>on the IC bottom side<br>connected to analog<br>ground.<br>A high-quality ground plane<br>(about 500 mil. inch over<br>500 mil. inch) should be<br>deployed around this pin<br>whenever possible. |

# PD69101 Pin Descriptions

| continued |             |               |                                                                                                                                                                                |

|-----------|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number    | Name        | Туре          | Description                                                                                                                                                                    |

| 1         | CURRENT_SET | Digital input | User input to set AF/AT and maximum current limit.                                                                                                                             |

| 2         |             |               | Use pull-up resistors<br>to DVDD or pull-down<br>resistors to DGND to set<br>the mode of operation as<br>shown in Table 3-2.                                                   |

| 3         | DVDD        | Power in      | Regulated input voltage<br>(3.3V) for internal digital<br>circuitry. Must be externally<br>connected to pin 4.                                                                 |

| 4         | VAUX3P3     | Power in      | Voltage regulation in 3.3 VDC. Connect to pin 5. A 4.7 $\mu$ F capacitor to AGND is recommended.                                                                               |

| 5         | DRV_VAUX3P3 | Power out     | Internal voltage regulator<br>out, 3.3 VDC.                                                                                                                                    |

|           |             |               | It must be externally connected to pin 4.                                                                                                                                      |

| 6         | VAUX5       | Power         | Regulated 5 VDC voltage filter.<br>A 1 $\mu$ F capacitor to AGND is recommended.                                                                                               |

| 7         | AGND        | Power         | Analog ground.                                                                                                                                                                 |

| 8         | V_MAIN      | Power         | Supply voltage for the internal analog circuit. Place a low-ESR bypass capacitor with low impedance trace as close as possible to AGND and this pin (not less than 1 $\mu$ F). |

| 9         | PORT_NEG    | Analog I/O    | Negative output of the port.                                                                                                                                                   |

| 10        | PORT_SENSE  | Analog input  | Sense resistor port input (connected to 0.5, 1% $\Omega$ resistor to GND).                                                                                                     |

| 11        | QGND        | Power         | Quiet analog ground; used for sensitive analog cells.                                                                                                                          |

| 12        | I_REF       | Analog I/O    | Resistor reference.<br>Connect 30.1K 1% resistor<br>to QGND.                                                                                                                   |

# PD69101 Pin Descriptions

| continued |                  |                |                                                                                                                                                                                                                                                         |

|-----------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number    | Name             | Туре           | Description                                                                                                                                                                                                                                             |

| 13<br>14  | LED1             | Open-drain I/O | Port status direct LED<br>indications. For details, see<br>Table 3-4. This is a high-<br>voltage, open-drain, active<br>low (SINK) output pin.<br>Connection to LED and<br>$V_{MAIN}$ through a ~18.2<br>K $\Omega$ (~3 mA) resistor is<br>recommended. |

| 15        | N/C              | Analog I/O     | Test pin (for production                                                                                                                                                                                                                                |

| 16        | N/C              |                | use only); keep open (not connected).                                                                                                                                                                                                                   |

| 17        | TRIM             | Analog input   | Zapping input for IC<br>production trimming. It<br>must be connected to<br>DVDD.                                                                                                                                                                        |

| 18        | SYNC             | Digital I/O    | Synchronization open-drain I/O pin between host and client. In 2-pair mode (switch), this pin should be pulled down to DGND through a $4.7 \text{ K}\Omega$ resistor.                                                                                   |

| 19        | DGND             | Digital I/O    | Digital ground.                                                                                                                                                                                                                                         |

| 20        | RESET_N          | Digital input  | Reset input/on-off command (active low).                                                                                                                                                                                                                |

| 21<br>22  | MODE 0<br>MODE 1 | Test I/O       | Configuration input pins.<br>Used to set mode of<br>operation and test mode<br>at production. Typically<br>connected to DGND. For<br>details, see Table 3-3.                                                                                            |

| 23        | Host/Client      | Digital input  | If connected to DVDD (3.3<br>VDC): host mode.<br>If connected to GND: client<br>mode.                                                                                                                                                                   |

| 24        | STD_DET/LEGACY   | Digital input  | User input pin to set the<br>chip mode of operation.<br>1: DVDD= IEEE 802.3af-<br>compliant resistor detection<br>only.<br>0: DGND= IEEE 802.3af/at<br>detection and legacy (non-<br>standard) line detection.                                          |

**Note:** 0= Connect to DGND and 1= connect to DVDD.

## 3.1 CURRENT\_SET and AF/AT

The following table lists the pins that determine the typical PD load output current.

### Table 3-2. CURRENT\_SET and AF/AT Pins

| AT/AF Pin | Current_Set Pin | Max. Current I <sub>CUT</sub><br>[mA] | Typical I <sub>LIM</sub> [mA] | IEEE 802.3                 |

|-----------|-----------------|---------------------------------------|-------------------------------|----------------------------|

| 0         | 0               | 350                                   | 425                           | AF mode (standard)         |

| 1         | 0               | 600                                   | 722                           | AT mode (standard)         |

| 1         | 1               | 720                                   | 874                           | AT mode (high<br>power)    |

| 0         | 1               | 1000                                  | 1200                          | AT mode (extra high power) |

## 3.2 Mode of Operation Coding

The following table lists the mode of operation coding options related to pins 21 and 22.

### Table 3-3. Configuration Coding

| Mode 0 | Mode 1 | Mode                   | Description                                                                                           |

|--------|--------|------------------------|-------------------------------------------------------------------------------------------------------|

| 0      | 0      | Normal operation mode  | Standard operation PoE mode.                                                                          |

|        |        |                        | LED0 and LED1 outputs<br>are used for direct LED<br>drive as described in the<br>following section.   |

| 0      | 1      | Serial monitoring mode | Standard operation PoE mode.                                                                          |

|        |        |                        | LED0 and LED1 are used<br>to continuously stream out<br>internal logic signals for<br>PoE monitoring. |

| 1      | 0      | Test mode              | Internal IC test mode; used in production only.                                                       |

| 1      | 1      | Test mode              | Internal IC test mode; used in production only.                                                       |

## 3.3 LED I/Os Behavior

The following tables list the LED I/Os behavior related to pins 13 and 14 in 2-pair application. In both application types, the LED pin is a high-voltage, open-drain, output pin, and an active low (sink) pin. That is, LED is "ON" when the I/O is pulled low.

#### Table 3-4. 2-Pair Behavior

| Status Indications | LED0 | LED1 | Notes                                                |

|--------------------|------|------|------------------------------------------------------|

| AF mode—port ON    | ON   | OFF  | Useful for bi-color LED connected from LED0 to LED1. |

| continued                                                       |               |               |                                                                            |

|-----------------------------------------------------------------|---------------|---------------|----------------------------------------------------------------------------|

| Status Indications                                              | LED0          | LED1          | Notes                                                                      |

| AT mode (class AT was detected)—port ON                         | ON            | ON            | <u> </u>                                                                   |

| AF mode—over-load or short                                      | Blink<br>1 Hz | OFF           | Blinking continues for ~2 seconds.                                         |

| AT mode—over-load or short                                      | Blink<br>1 Hz | Blink<br>1 Hz | Blinking continues for ~2 seconds.                                         |

| $V_{\text{MAIN}}$ voltage is out of range or IC overtemperature | Blink<br>4 Hz | OFF           | Blinking continues as long as overvoltage or overtemperature state exists. |

| AF mode—port OFF                                                | OFF           | ON            | Useful for bi-color LED connected from LED0 to LED1.                       |

| AT mode—port OFF                                                | OFF           | OFF           | —                                                                          |

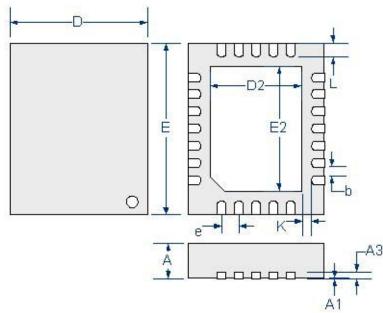

## 4. Package Specifications

This section provides the package drawing, RoHS and solder reflow information, and thermal specifications for the PD69101 device.

The following figure shows PD69101 package is a 4 mm × 5 mm, 24-pin QFN.

#### Figure 4-1. QFN Package

Dimensions do not include protrusions. It must not exceed 0.155 mm (0.006") on any side. Lead dimension must not include solder coverage.

The following table lists the dimensions for the QFN package.

#### Table 4-1. Package Dimensions

| Dimension | Millimeters |          | Inches    |           |  |

|-----------|-------------|----------|-----------|-----------|--|

| -         | Minimum     | Maximum  | Minimum   | Maximum   |  |

| A         | 0.80        | 1.00     | 0.031     | 0.039     |  |

| A1        | 0.00        | 0.05     | 0         | 0.002     |  |

| A3        | 0.20 REF    |          | 0.008 REF |           |  |

| К         | 0.20 MIN    | 0.20 MIN |           | 0.008 MIN |  |

| е         | 0.50 BSC    |          | 0.02 BSC  |           |  |

| L         | 0.30        | 0.50     | 0.012     | 0.02      |  |

| b         | 0.18        | 0.30     | 0.007     | 0.012     |  |

| D2        | 2.50        | 2.75     | 0.098     | 0.108     |  |

| E2        | 3.50        | 3.75     | 0.138     | 0.148     |  |

| D         | 4.00 BSC    |          | 0.158 BSC |           |  |

| E         | 5.00 BSC    |          | 0.197 BSC |           |  |

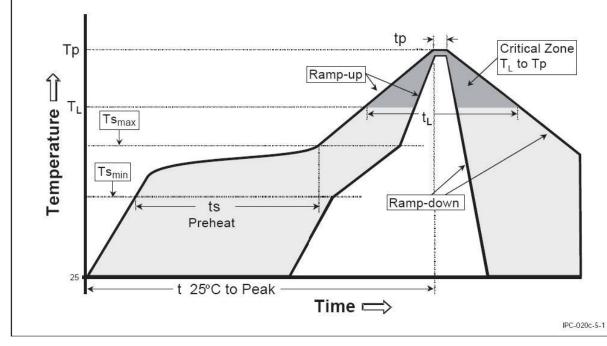

## 4.1 RoHS and Solder Reflow Information

The PD69101 device is rated RoHS 6/6. The package is lead (Pb)-free, with a 100% matter tin finish. The package peak temperature for solder reflow (40 seconds maximum exposure) is 260 °C (0 °C, -5 °C).

The following table lists the classification reflow profile information.

### Table 4-2. Classification Reflow Profiles

| Profile Feature                                                                                                                                     | Pb-Free Assembly                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Average ramp-up rate (TS $_{max}$ to T $_{p}$ )                                                                                                     | 3 °C/second max                            |

| Pre-heat:<br>Temperature minimum (TS <sub>min</sub> )<br>Temperature maximum (TS <sub>max</sub> )<br>Time (TS <sub>min</sub> to TS <sub>max</sub> ) | 150 °C<br>200 °C<br>60 seconds–180 seconds |

| Time maintained above:<br>Temperature (T <sub>L</sub> )<br>Time (t <sub>L</sub> )                                                                   | 217 °C<br>60 seconds–150 seconds           |

| Peak/classification temperature                                                                                                                     | See Figure 4-2                             |

| Time within 5 °C of actual peak temperature (tp)                                                                                                    | 20 seconds-40 seconds                      |

| Ramp-down rate                                                                                                                                      | 6 °C/second max                            |

| Time 25 °C to peak temperature                                                                                                                      | 8 minutes max                              |

Note: All temperatures refer to the top-side of the package, measured on the package body surface.

The following illustration shows the classification reflow profile of the PD69101 device.

Figure 4-2. Classification Reflow Profile Diagram

Note: Exceeding these ratings can damage the device.

## 4.2 Thermal Specifications

The following table lists the thermal specifications for the PD69101 device.

### Table 4-3. Thermal Specifications

| Parameter                                       | Value   |

|-------------------------------------------------|---------|

| Typical thermal resistance: junction to ambient | 25 °C/W |

| Typical thermal resistance: junction to case    | 4 °C/W  |

| Typical thermal resistance: junction to board   | 2 °C/W  |

The  $\theta$ JA numbers are guidelines for the thermal performance of the device/pc-board system. All specifications assume no ambient airflow.

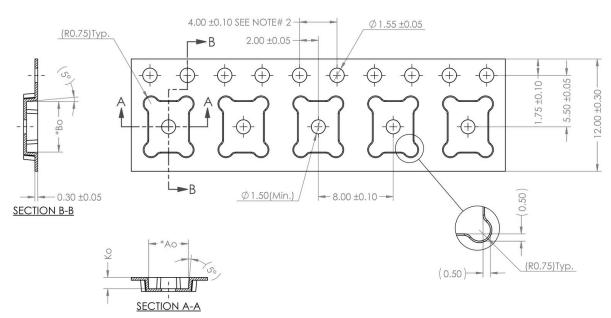

## 4.3 Tape and Reel—Packaging Information

The following section provides the tape and reel packaging information. The following figure shows the tape specification.

#### Figure 4-3. Tape Specification

The following table lists the tape mechanical data.

#### Table 4-4. Tape Mechanical Data

| Dimension | Millimeters |

|-----------|-------------|

| A0        | 4.25 ±0.10  |

| В0        | 5.40 ±0.10  |

| КО        | 1.20 ±0.10  |

| К1        | -           |

| Pitch     | 8.00 ±0.10  |

| continued |             |

|-----------|-------------|

| Dimension | Millimeters |

| Width     | 12.00 ±0.30 |

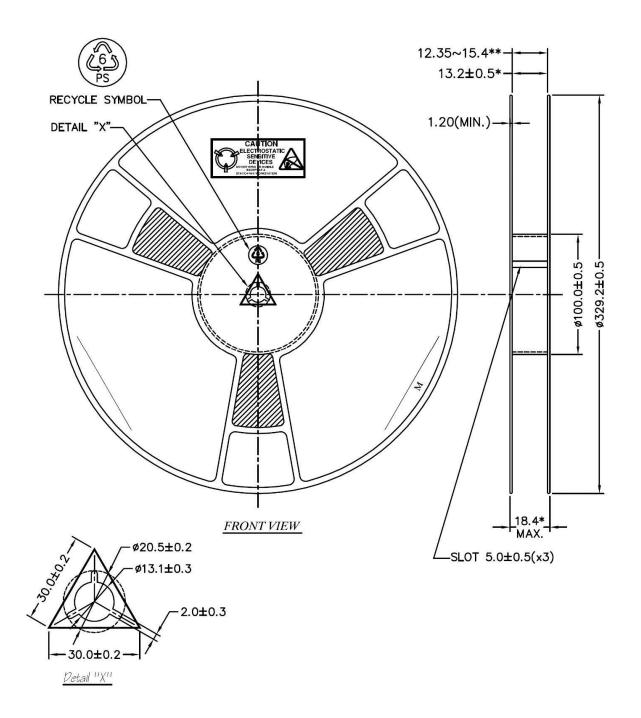

The following figure shows the reel specification.

Figure 4-4. Reel Specification

# 5. Ordering Information

The following table lists the ordering information for the PD69101 device.

### Table 5-1. Ordering Information

| Part Number   | Package          | Packaging Type | Temperature      | Part Making          |

|---------------|------------------|----------------|------------------|----------------------|

| PD69101ILQ-TR | Plastic 24-pin   | Tape and reel  | – 40 °C to 85 °C | MSC                  |

|               | QFN: 4 mm × 5 mm |                |                  | 69101                |

|               |                  |                |                  | ZZ e3 <sup>1</sup>   |

|               |                  |                |                  | YYWWNNN <sup>2</sup> |

Notes:

- 1. ZZ e3: ZZ = Random character with no meaning and e3 = Second level interconnect.

- 2. YY = Year, WW = Week, NNN = Trace Code.

# 6. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | 11/2021 | <ul> <li>The following is a summary of changes in revision A of this document:</li> <li>The document was updated to latest Microchip template.</li> <li>The document number was changed from PD-000308061 to DS00004280A.</li> </ul>                                                                                                                                                                                                                |

| 3.0      | 8/2019  | <ul> <li>The following is a summary of changes in revision 3.0 of this document.</li> <li>Changed package marking of Figure 3-1.</li> <li>Part marking was updated. For more information, see 5. Ordering Information.</li> </ul>                                                                                                                                                                                                                   |

| 2.0      | 3/2018  | <ul> <li>The following is a summary of changes in revision 2.0 of this document.</li> <li>Document format was updated.</li> <li>MSL level was updated from 1 to 3.</li> <li>4-pair application was removed.</li> <li>Tape and Reel—Packaging Information section was added. For more information, see 4.3. Tape and Reel—Packaging Information.</li> <li>Part marking is updated. For more information, see the 5. Ordering Information.</li> </ul> |

| 1.9      | 3/2014  | <ul> <li>The following is a summary of changes in revision 1.9 of this document.</li> <li>TETA JB was added.</li> <li>A typo in the ESD parameter was corrected.</li> <li>V<sub>Main</sub> out-of-range information was corrected.</li> </ul>                                                                                                                                                                                                       |

| 1.8      | 10/2013 | <ul> <li>The following is a summary of changes in revision 1.8 of this document.</li> <li>The extended input voltage range was updated to 32V–57V.</li> </ul>                                                                                                                                                                                                                                                                                       |

| continued |         |                                                                                                                                                                                     |

|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision  | Date    | Description                                                                                                                                                                         |

| 1.7       | 7/2013  | <ul><li>The following is a summary of changes in revision 1.7 of this document.</li><li>TETA JC data was added.</li></ul>                                                           |

| 1.6       | 7/2013  | <ul><li>The following is a summary of changes in revision 1.6 of this document.</li><li>The IC marking was updated.</li></ul>                                                       |

| 1.5       | 12/2010 | <ul><li>The following is a summary of changes in revision 1.5 of this document.</li><li>Parameters were updated.</li></ul>                                                          |

| 1.4       | 9/2010  | <ul><li>The following is a summary of changes in revision 1.4 of this document.</li><li>Parameters were updated.</li></ul>                                                          |

| 1.3       | 6/2010  | <ul><li>The following is a summary of changes in revision 1.3 of this document.</li><li>Parameters were updated.</li></ul>                                                          |

| 1.2       | 6/2010  | <ul><li>The following is a summary of changes in revision 1.2 of this document.</li><li>Package drawing was updated.</li></ul>                                                      |

| 1.1       | 3/2010  | <ul> <li>The following is a summary of changes in revision 1.1 of this document.</li> <li>The wave forms and functionality were updated according to evaluation results.</li> </ul> |

| 1.0       | 3/2010  | Revision 1.0 was the first publication of this document.                                                                                                                            |

# The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

<sup>©</sup> 2021, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-5224-9285-6

# Quality Management System

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| MERICAS                   | ASIA/PACIFIC                              | ASIA/PACIFIC                              | EUROPE                                    |

|---------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

|                           |                                           |                                           |                                           |

| Corporate Office          | Australia - Sydney<br>Tel: 61-2-9868-6733 | India - Bangalore<br>Tel: 91-80-3090-4444 | Austria - Wels<br>Tel: 43-7242-2244-39    |

|                           | China - Beijing                           | India - New Delhi                         | Fax: 43-7242-2244-39                      |

| handler, AZ 85224-6199    | Tel: 86-10-8569-7000                      | Tel: 91-11-4160-8631                      |                                           |

| el: 480-792-7200          |                                           |                                           | Denmark - Copenhager                      |

| ax: 480-792-7277          | China - Chengdu                           | India - Pune                              | Tel: 45-4485-5910                         |

| echnical Support:         | Tel: 86-28-8665-5511                      | Tel: 91-20-4121-0141                      | Fax: 45-4485-2829                         |

| www.microchip.com/support | China - Chongqing                         | Japan - Osaka<br>Tel: 81-6-6152-7160      | Finland - Espoo                           |

| Veb Address:              | Tel: 86-23-8980-9588                      |                                           | Tel: 358-9-4520-820                       |

| www.microchip.com         | China - Dongguan                          | Japan - Tokyo                             | France - Paris                            |

| tlanta                    | Tel: 86-769-8702-9880                     | Tel: 81-3-6880- 3770                      | Tel: 33-1-69-53-63-20                     |

| uluth, GA                 | China - Guangzhou                         | Korea - Daegu                             | Fax: 33-1-69-30-90-79                     |

| el: 678-957-9614          | Tel: 86-20-8755-8029                      | Tel: 82-53-744-4301                       | Germany - Garching                        |

| ax: 678-957-1455          | China - Hangzhou                          | Korea - Seoul                             | Tel: 49-8931-9700                         |

| ustin, TX                 | Tel: 86-571-8792-8115                     | Tel: 82-2-554-7200                        | Germany - Haan                            |

| el: 512-257-3370          | China - Hong Kong SAR                     | Malaysia - Kuala Lumpur                   | Tel: 49-2129-3766400                      |

| loston                    | Tel: 852-2943-5100                        | Tel: 60-3-7651-7906                       | Germany - Heilbronn<br>Tel: 49-7131-72400 |

| Vestborough, MA           | China - Nanjing                           | Malaysia - Penang                         |                                           |

| el: 774-760-0087          | Tel: 86-25-8473-2460                      | Tel: 60-4-227-8870                        | Germany - Karlsruhe                       |

| ax: 774-760-0088          | China - Qingdao                           | Philippines - Manila                      | Tel: 49-721-625370                        |

| Chicago                   | Tel: 86-532-8502-7355                     | Tel: 63-2-634-9065                        | Germany - Munich                          |

| asca, IL                  | China - Shanghai                          | Singapore                                 | Tel: 49-89-627-144-0                      |

| el: 630-285-0071          | Tel: 86-21-3326-8000                      | Tel: 65-6334-8870                         | Fax: 49-89-627-144-44                     |

| ax: 630-285-0075          | China - Shenyang                          | Taiwan - Hsin Chu                         | Germany - Rosenheim                       |

| allas                     | Tel: 86-24-2334-2829                      | Tel: 886-3-577-8366                       | Tel: 49-8031-354-560                      |

| ddison, TX                | China - Shenzhen                          | Taiwan - Kaohsiung                        | Israel - Ra'anana                         |

| el: 972-818-7423          | Tel: 86-755-8864-2200                     | Tel: 886-7-213-7830                       | Tel: 972-9-744-7705                       |

| ax: 972-818-2924          | China - Suzhou                            | Taiwan - Taipei                           | Italy - Milan                             |

| etroit                    | Tel: 86-186-6233-1526                     | Tel: 886-2-2508-8600                      | Tel: 39-0331-742611                       |

| ovi, MI                   | China - Wuhan                             | Thailand - Bangkok                        | Fax: 39-0331-466781                       |

| el: 248-848-4000          | Tel: 86-27-5980-5300                      | Tel: 66-2-694-1351                        | Italy - Padova                            |

| ouston, TX                | China - Xian                              | Vietnam - Ho Chi Minh                     | Tel: 39-049-7625286                       |

| el: 281-894-5983          | Tel: 86-29-8833-7252                      | Tel: 84-28-5448-2100                      | Netherlands - Drunen                      |

| Idianapolis               | China - Xiamen                            |                                           | Tel: 31-416-690399                        |

| oblesville, IN            | Tel: 86-592-2388138                       |                                           | Fax: 31-416-690340                        |

| el: 317-773-8323          | China - Zhuhai                            |                                           | Norway - Trondheim                        |

| ax: 317-773-5453          | Tel: 86-756-3210040                       |                                           | Tel: 47-72884388                          |

| el: 317-536-2380          |                                           |                                           | Poland - Warsaw                           |

| os Angeles                |                                           |                                           | Tel: 48-22-3325737                        |

| lission Viejo, CA         |                                           |                                           | Romania - Bucharest                       |

| el: 949-462-9523          |                                           |                                           | Tel: 40-21-407-87-50                      |

| ax: 949-462-9608          |                                           |                                           | Spain - Madrid                            |

| el: 951-273-7800          |                                           |                                           | Tel: 34-91-708-08-90                      |

| aleigh, NC                |                                           |                                           | Fax: 34-91-708-08-91                      |

| el: 919-844-7510          |                                           |                                           | Sweden - Gothenberg                       |

| ew York, NY               |                                           |                                           | Tel: 46-31-704-60-40                      |

| el: 631-435-6000          |                                           |                                           | Sweden - Stockholm                        |

| an Jose, CA               |                                           |                                           | Tel: 46-8-5090-4654                       |

| el: 408-735-9110          |                                           |                                           | UK - Wokingham                            |

| el: 408-436-4270          |                                           |                                           | Tel: 44-118-921-5800                      |

| anada - Toronto           |                                           |                                           | Fax: 44-118-921-5820                      |

| el: 905-695-1980          |                                           |                                           |                                           |

| ax: 905-695-2078          |                                           |                                           |                                           |

Datasheet