#### 1.8 V

#### **Features**

- Interface

- xSPI (Octal) interface

- 1.8 V interface support

- Single ended clock (CK) 11 bus signals

- Optional differential clock (CK, CK#) 12 bus signals

- Chip select (CS#)

- 8-bit data bus (DQ[7:0])

- Hardware reset (RESET#)

- Bidirectional read-write data strobe (RWDS)

- Output at the start of all transactions to indicate refresh latency

- · Output during read transactions as read data strobe

- Input during write transactions as write data mask

- Performance, power, and packages

- 200 MHz maximum clock rate

- DDR transfers data on both edges of the clock

- Data throughput up to 400 MBps (3,200 Mbps)

- Configurable burst characteristics

- Linear burst

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- 128 bytes (64 clocks)

- Hybrid option one wrapped burst followed by linear burst

- Configurable output drive strength

- Power modes

- · Hybrid sleep mode

- · Deep power down

- Array refresh

- Partial memory array (1/8, 1/4, 1/2, and so on)

- Full

- Package

- 24-ball FBGA

- Operating temperature range

- Industrial (I): -40 °C to +85 °C

- Industrial Plus (V): –40 °C to +105 °C

- Automotive, AEC-Q100 Grade 3: -40 °C to +85 °C

- Automotive, AEC-Q100 Grade 2: –40 °C to +105°C

- Automotive, AEC-Q100 Grade 1: –40 °C to +125 °C

- Technology

- 25-nm DRAM

Performance summary

### **Performance summary**

| Read transaction timings                                      | Unit    |

|---------------------------------------------------------------|---------|

| Maximum clock rate at 1.8 V V <sub>CC</sub> /V <sub>CCQ</sub> | 200 MHz |

| Maximum access time (t <sub>ACC</sub> )                       | 35 ns   |

| Maximum current consumption                | Unit        |

|--------------------------------------------|-------------|

| Burst read/write (linear burst at 200 MHz) | 22 mA/25 mA |

| Standby (105 °C)                           | 1.55 mA     |

| Deep power down (105 °C)                   | 15 μΑ       |

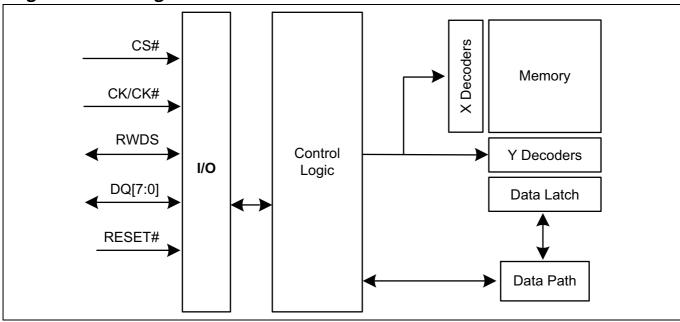

### Logic block diagram

Table of contents

### **Table of contents**

| 1 General description                                       | 5  |

|-------------------------------------------------------------|----|

| 1.1 xSPI (Octal) interface                                  |    |

| 2 Product overview                                          |    |

| 2.1 xSPI (Octal) interface                                  |    |

| 3 Signal description                                        |    |

| 3.1 Input/output summary                                    |    |

| 4 xSPI (Octal) transaction details                          |    |

| 4.1 Command/address/data bit assignments                    |    |

| 4.2 RESET ENABLE transaction                                |    |

| 4.3 RESET transaction                                       |    |

| 4.4 READ ID transaction                                     |    |

| 4.5 DEEP POWER DOWN transaction                             | 14 |

| 4.6 READ transaction                                        |    |

| 4.7 WRITE transaction                                       | 16 |

| 4.8 WRITE ENABLE transaction                                | 17 |

| 4.9 WRITE DISABLE transaction                               | 17 |

| 4.10 READ ANY REGISTER transaction                          | 17 |

| 4.11 WRITE ANY REGISTER transaction                         | 18 |

| 4.12 Data placement during memory READ/WRITE transactions   | 19 |

| 4.13 Data placement during register READ/WRITE transactions |    |

| 5 Memory space                                              | 21 |

| 5.1 xSPI (Octal) interface                                  | 21 |

| 5.2 Density and row boundaries                              | 21 |

| 6 Register space access                                     | 22 |

| 6.1 xSPI (Octal) interface                                  | 22 |

| 6.2 Device identification registers                         | 22 |

| 6.3 Device configuration registers                          |    |

| 6.3.1 Configuration register 0 (CR0)                        | 23 |

| 6.3.2 Configuration register 1                              | 26 |

| 7 Interface states                                          |    |

| 8 Power conservation modes                                  | 29 |

| 8.1 Interface standby                                       |    |

| 8.2 Active clock stop                                       | 29 |

| 8.3 Hybrid sleep                                            | 29 |

| 8.4 Deep power down                                         | 30 |

| 9 Electrical specifications                                 | 31 |

| 9.1 Absolute maximum ratings                                |    |

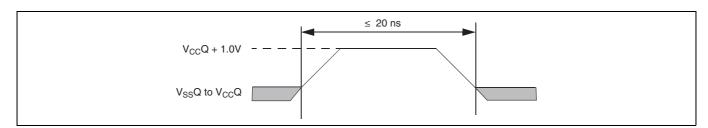

| 9.2 Input signal overshoot                                  |    |

| 9.3 Latch-up characteristics                                |    |

| 9.4 Operating ranges                                        |    |

| 9.4.1 Temperature ranges                                    |    |

| 9.4.2 Power supply voltages                                 |    |

| 9.5 DC characteristics                                      |    |

| 9.5.1 Capacitance characteristics                           |    |

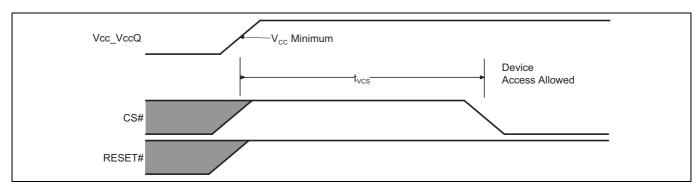

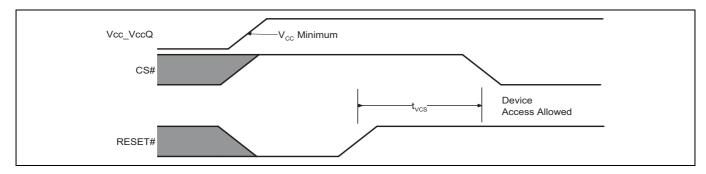

| 9.6 Power-up initialization                                 |    |

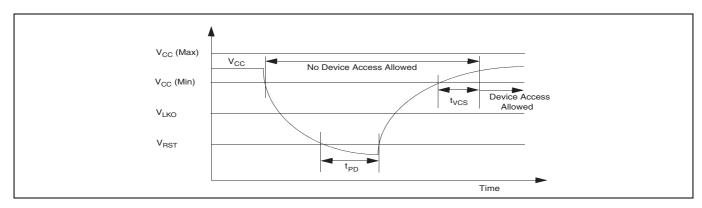

| 9.7 Power down                                              |    |

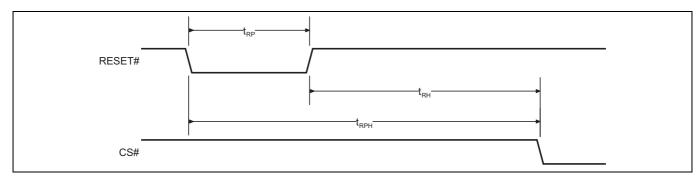

| 9.8 Hardware reset                                          |    |

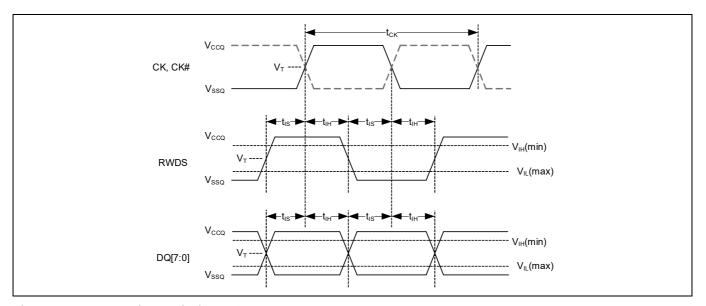

| 10 Timing specifications                                    |    |

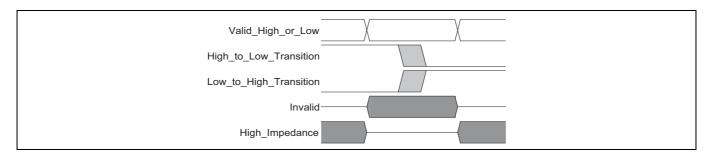

| 10.1 Key to switching waveforms                             |    |

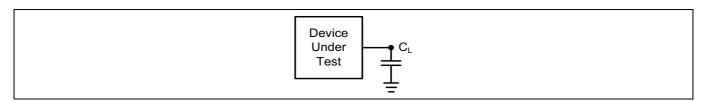

| 10.2 AC test conditions                                     |    |

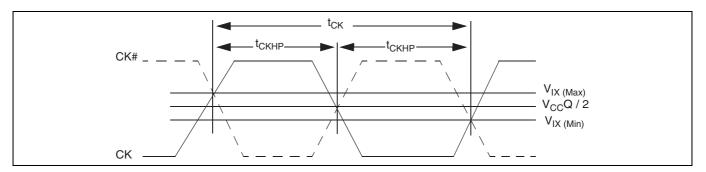

| 10.3 CLK characteristics                                    | 41 |

#### Table of contents

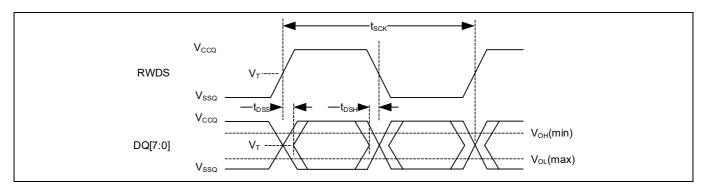

| 10.4 AC characteristics                               | 42 |

|-------------------------------------------------------|----|

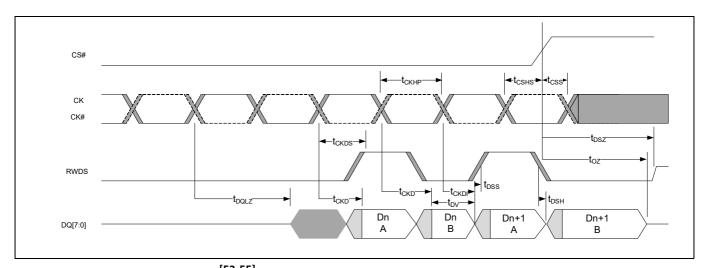

| 10.4.1 Read transactions                              | 42 |

| 10.4.2 Write transactions                             |    |

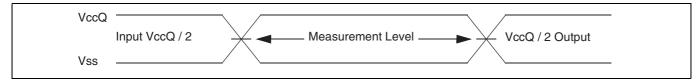

| 10.5 Timing reference levels                          |    |

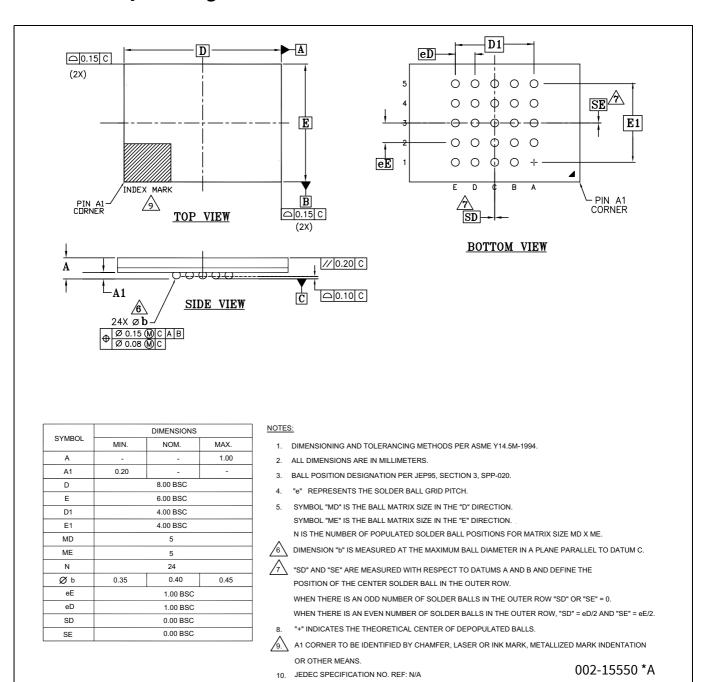

| 11 Physical interface                                 | 46 |

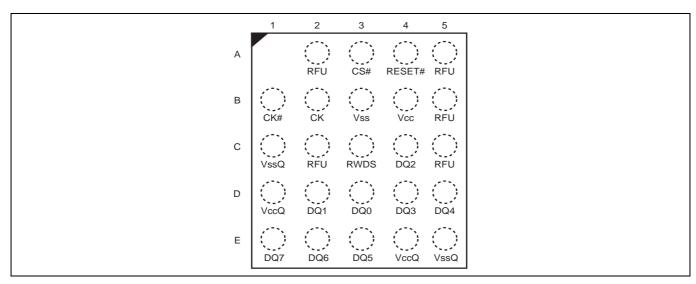

| 11.1 FBGA 24-ball 5 x 5 array footprint               |    |

| 11.2 Physical diagrams                                | 47 |

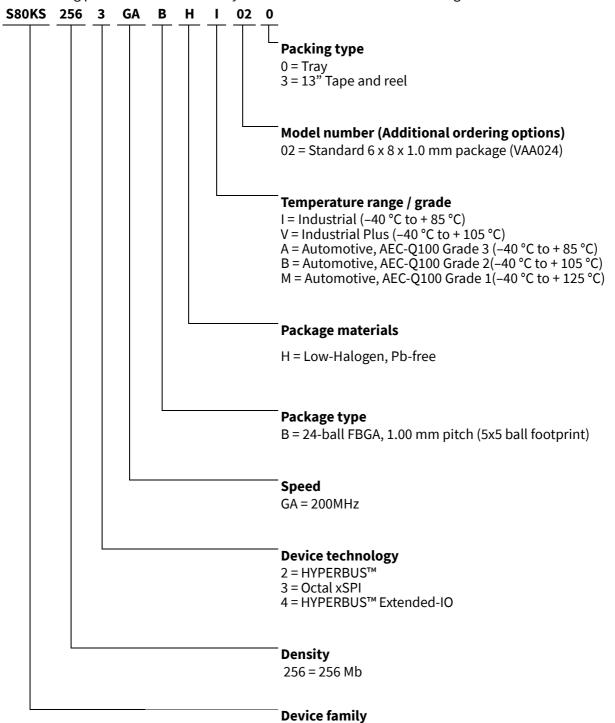

| 12 Ordering information                               |    |

| 12.1 Ordering part number                             | 48 |

| 12.2 Valid combinations                               |    |

| 12.3 Valid combinations - Automotive Grade / AEC-Q100 |    |

| 13 Acronyms                                           |    |

| 14 Document conventions                               |    |

| 14.1 Units of measure                                 |    |

| Revision history                                      |    |

infineon

General description

### 1 General description

The 256 Mb HYPERRAM™ device is a high-speed CMOS, self-refresh DRAM, with xSPI (Octal) interface. The DRAM array uses dynamic cells that require periodic refresh. Refresh control logic within the device manages the refresh operations on the DRAM array when the memory is not being actively read or written by the xSPI interface master (host). Since the host is not required to manage any refresh operations, the DRAM array appears to the host as though the memory uses static cells that retain data without refresh. Hence, the memory is more accurately described as pseudo static RAM (PSRAM).

Since the DRAM cells cannot be refreshed during a read or write transaction, there is a requirement that the host limit read or write burst transfers lengths to allow internal logic refresh operations when they are needed. The host must confine the duration of transactions and allow additional initial access latency, at the beginning of a new transaction, if the memory indicates a refresh operation is needed.

### 1.1 xSPI (Octal) interface

xSPI (Octal) is a SPI-compatible low signal count, DDR interface supporting eight I/Os. The DDR protocol in xSPI (Octal) transfers two data bytes per clock cycle on the DQ input/output signals. A read or write transaction on xSPI (Octal) consists of a series of 16-bit wide, one clock cycle data transfers at the internal RAM array with two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals. All inputs and outputs are LV-CMOS compatible. Device are available as  $1.8 \text{ V V}_{\text{CC}}/\text{V}_{\text{CCQ}}$  (nominal) for array (V<sub>CC</sub>) and I/O buffer (V<sub>CCQ</sub>) supplies, through different ordering part number (OPN).

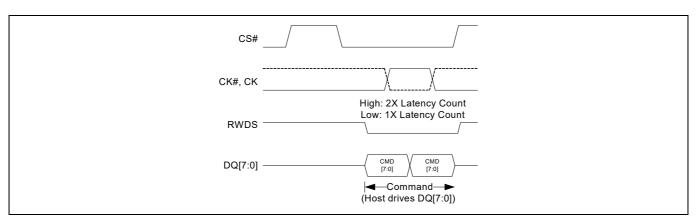

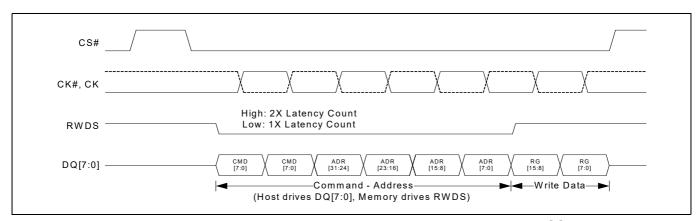

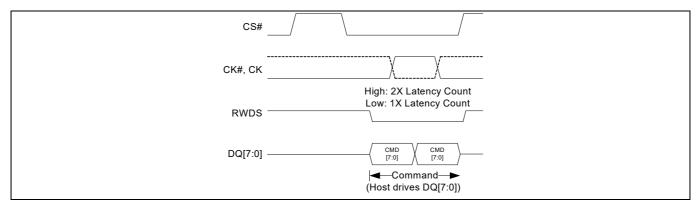

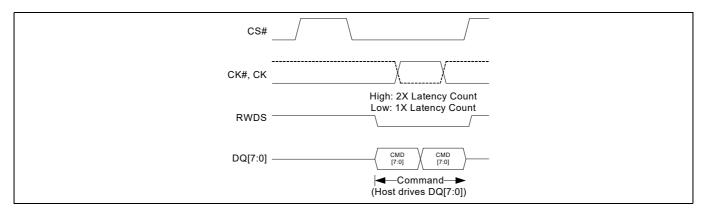

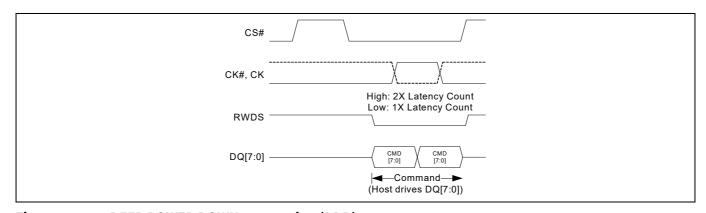

Each transaction on xSPI (Octal) must include a command whereas address and data are optional. The transactions are structures as follows:

- Each transaction begins with CS# going LOW and ends with CS# returning HIGH.

- The serial clock (CK) marks the transfer of each bit or group of bits between the host and memory. All transfers occur on every CK edge (DDR mode).

- Each transaction has a 16-bit command which selects the type of device operation to perform. The 16-bit command is based on two 8-bit opcodes. The same 8-bit opcode is sent on both edges of the clock.

- A command may be stand-alone or may be followed by address bits to select a memory location in the device to access data.

- Read transactions require a latency period after the address bits and can be zero to several CK cycles. CK must

continue to toggle during any read transaction latency period. During the command and address parts of a

transaction, the memory can indicate whether an additional latency period is needed for a required refresh time

(t<sub>RFH</sub>) which is added to the initial latency period; by driving the RWDS signal to the HIGH state.

- Write transactions to registers do not require a latency period.

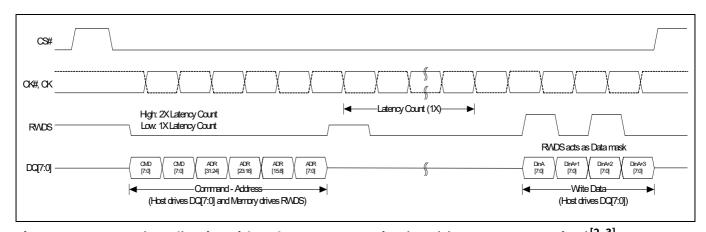

- Write transactions to the memory array require a latency period after the address bits and can be zero to several CK cycles. CK must continue to toggle during any write transaction latency period. During the command and address parts of a transaction, the memory can indicate whether an additional latency period is needed for a required refresh time (t<sub>RFH</sub>) which is added to the initial latency period by driving the RWDS signal to the HIGH state.

- In all transactions, command and address bits are shifted in the device with the most significant bits (MSb) first. The individual data bits within a data byte are shifted in and out of the device MSb first as well. All data bytes are transferred with the lowest address byte sent out first.

General description

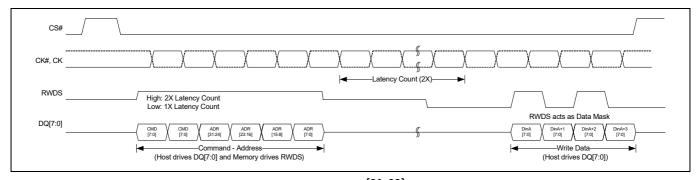

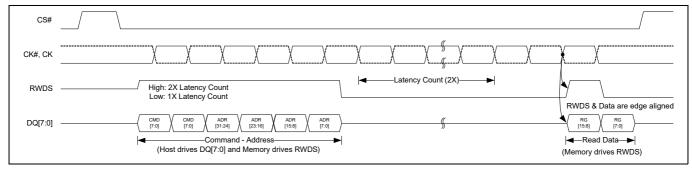

Figure 1 xSPI (Octal) command only transaction (DDR)

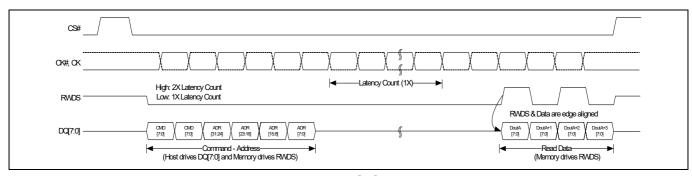

Figure 2 xSPI (Octal) write with no latency transaction (DDR) (Register writes)<sup>[1]</sup>

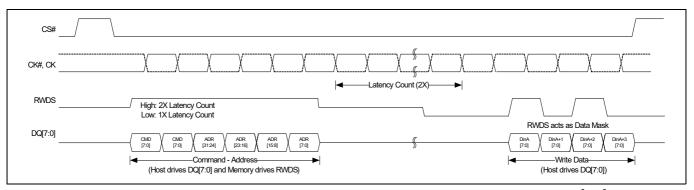

Figure 3 xSPI (Octal) write with 1X latency transaction (DDR) (Memory array writes)<sup>[2,3]</sup>

- 1. Write with no latency transaction is used for register writes only.

- 2. RWDS driven by the host.

- 3. Data DinA and DinA+2 are masked.

General description

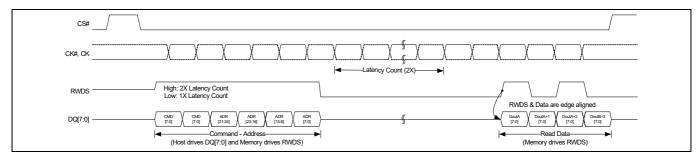

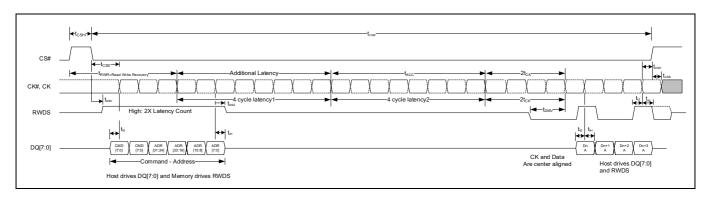

Figure 4 xSPI (Octal) write with 2X latency transaction (DDR) (Memory array writes)<sup>[4,5]</sup>

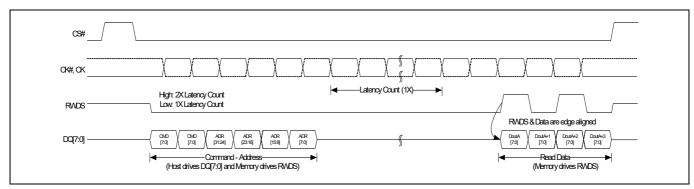

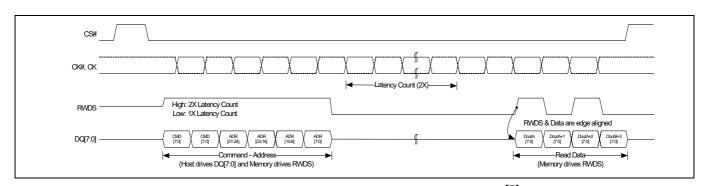

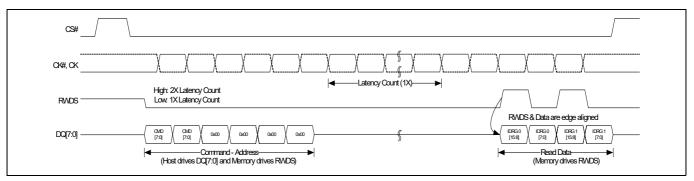

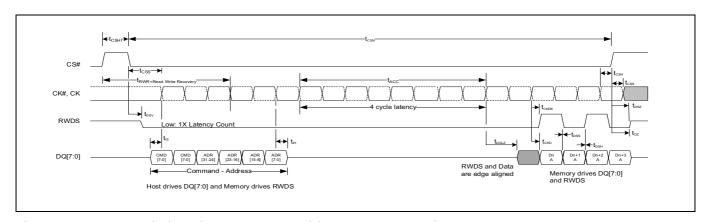

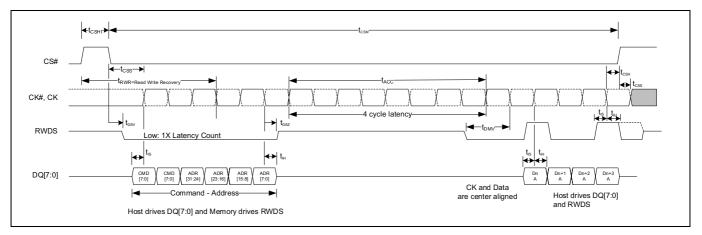

Figure 5 xSPI (Octal) read with 1X latency transaction (DDR) (All reads)<sup>[6]</sup>

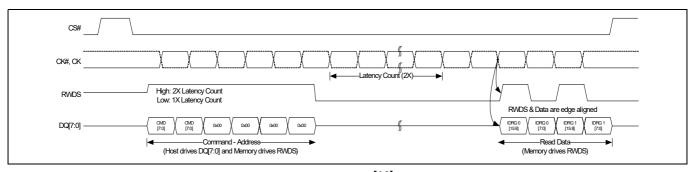

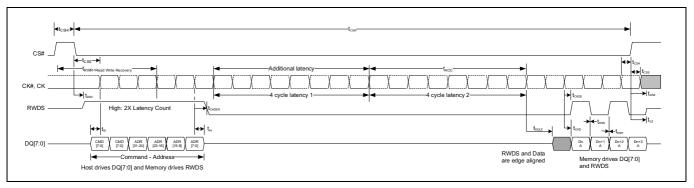

Figure 6 xSPI (Octal) read with 2X latency transaction (DDR) (All reads)<sup>[7]</sup>

- 4. RWDS driven by HYPERRAM™ during command & address cycles for 2X latency and then driven by the host for data masking.

- 5. Data DinA and DinA+2 are masked.

- 6. RWDS is driven by HYPERRAM™ phase aligned with data.

- 7. RWDS is driven by HYPERRAM™ during command & address cycles for 2X latency and then driven again phase aligned with data.

infineon

**Product overview**

#### 2 Product overview

The 256 Mb HYPERRAM™ device is 1.8 V array and I/O, synchronous self-refresh dynamic RAM (DRAM). The HYPERRAM™ device provides an xSPI (Octal) slave interface to the host system. The xSPI (Octal) interface has an 8-bit (1 byte) wide DDR data bus and use only word-wide (16-bit data) address boundaries. Read transactions provide 16 bits of data during each clock cycle (8 bits on both clock edges). Write transactions take 16 bits of data from each clock cycle (8 bits on each clock edge).

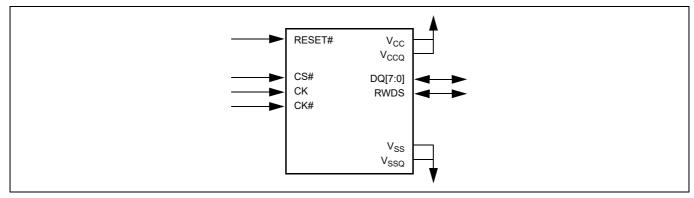

Figure 7 xSPI (Octal) HYPERRAM™ interface<sup>[8]</sup>

### 2.1 xSPI (Octal) interface

Read and write transactions require three clock cycles to define the target row/column address and then an initial access latency of  $t_{ACC}$ . During the CA part of a transaction, the memory will indicate whether an additional latency for a required refresh time ( $t_{RFH}$ ) is added to the initial latency; by driving the RWDS signal to the HIGH state. During a read (or write) transaction, after the initial data value has been output (or input), additional data can be read from (or written to) the row on subsequent clock cycles in either a wrapped or linear sequence. When configured in linear burst mode, the device will automatically fetch the next sequential row from the memory array to support a continuous linear burst. Simultaneously accessing the next row in the array while the read or write data transfer is in progress, allows for a linear sequential burst operation that can provide a sustained data rate of 400 MBps (1 byte (8 bit data bus) \* 2 (data clock edges) \* 200 MHz = 400 MBps).

#### Note

8. CK# is used in differential clock mode, but optional.

Signal description

### 3 Signal description

### 3.1 Input/output summary

The xSPI (Octal) HYPERRAM™ signals are shown in **Table 1**. Active low signal names have a hash symbol (#) suffix.

| Table 1 | I/O summary |

|---------|-------------|

|---------|-------------|

| Table 1                | I/O summary             |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                 | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| CS#                    | Input                   | <b>Chip select.</b> Bus transactions are initiated with a HIGH to LOW transition. Bus transactions are terminated with a Low to High transition. The master device has a separate CS# for each slave.                                                                                                                                                                                               |  |  |  |

| CK, CK# <sup>[9]</sup> | Input                   | Differential clock. Command, address, and data information is output with respect to the crossing of the CK and CK# signals. Use of differential clock is optional.  Single ended clock. CK# is not used, only a single ended CK is used. The clock is not required to be free-running.                                                                                                             |  |  |  |

| DQ[7:0]                | Input/output            | <b>Data input/output.</b> Command, address, and data information is transferred on these signals during read and write transactions.                                                                                                                                                                                                                                                                |  |  |  |

| RWDS                   | Input/output            | <b>Read-write data strobe.</b> During the command/address portion of all bus transactions RWDS is a slave output and indicates whether additional initial latency is required. Slave output during read data transfer, data is edge-aligned with RWDS. Slave input during data transfer in write transactions to function as a data mask. (HIGH = additional latency, LOW = no additional latency). |  |  |  |

| RESET#                 | Input, internal pull-up | Hardware RESET. When LOW, the slave device will self initialize and return to the standby state. RWDS and DQ[7:0] are placed into th HIGH-Z state when RESET# is LOW. The slave RESET# input includes weak pull-up, if RESET# is left unconnected it will be pulled up to th HIGH state.                                                                                                            |  |  |  |

| V <sub>CC</sub>        | Power supply            | Array power.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| V <sub>CCQ</sub>       | Power supply            | Input/output power.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| V <sub>SS</sub>        | Power supply            | Array ground.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| $V_{SSQ}$              | Power supply            | Input/output ground.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RFU                    | No connect              | <b>Reserved for future use</b> . May or may not be connected internally, the signal/ball location should be left unconnected and unused by PCB routing channel for future compatibility. The signal/ball may be used by a signal in the future.                                                                                                                                                     |  |  |  |

#### Note

<sup>9.</sup> CK# is used in differential clock mode, but optional connection. Tie the CK# input pin to either V<sub>CCQ</sub> or V<sub>SSQ</sub> if not connected to the host controller, but do not leave it floating.

xSPI (Octal) transaction details

### 4 xSPI (Octal) transaction details

The xSPI (Octal) master begins a transaction by driving CS# LOW while clock is idle. Then the clock begins toggling while CA words are transferred.

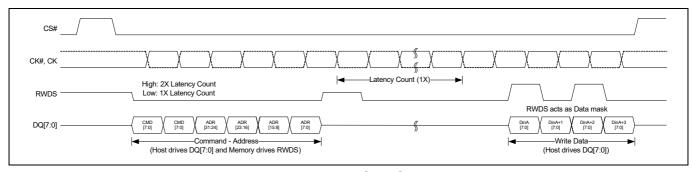

For memory read and write transactions, the xSPI (Octal) master then continues clocking for a number of cycles defined by the latency count setting in configuration register 0 (Register write transactions do not require any latency count). The initial latency count required for a particular clock frequency is based on RWDS. If RWDS is LOW during the CA cycles, one latency count is inserted. If RWDS is HIGH during the CA cycles, an additional latency count is inserted. Once these latency clocks have been completed the memory starts to simultaneously transition the RWDS and output the target data.

During the read data transfers, read data is output edge-aligned with every transition of RWDS. Data will continue to be output as long as the host continues to transition the clock while CS# is LOW. Note that burst transactions should not be so long as to prevent the memory from doing distributed refreshes.

During the write data transfers, write data is center-aligned with the clock edges. The first byte of data in each word is captured by the memory on the rising edge of CK and the second byte is captured on the falling edge of CK. RWDS is driven by the host master interface as a data mask. When data is being written and RWDS is HIGH the byte will be masked and the array will not be altered. When data is being written and RWDS is LOW the data will be placed into the array. Because the master is driving RWDS during write data transfers, neither the master nor the HYPERRAM™ device are able to indicate a need for latency within the data transfer portion of a write transaction. The acceptable write data burst length setting is also shown in configuration register 0.

Wrapped bursts will continue to wrap within the burst length and linear burst will output data in a sequential manner across row boundaries. When a linear burst read reaches the last address in the array, continuing the burst beyond the last address will provide data from the beginning of the address range. Read transfers can be ended at any time by bringing CS# HIGH when the clock is idle.

The clock is not required to be free-running. The clock may remain idle while CS# is HIGH.

xSPI (Octal) transaction details

### 4.1 Command/address/data bit assignments

### Table 2 Command set<sup>[10-14]</sup>

| Command                 | Code     | CA-Data | Address<br>(bytes) | Latency cycles | Data<br>(bytes) | Prerequisite |

|-------------------------|----------|---------|--------------------|----------------|-----------------|--------------|

| Software reset          |          |         |                    |                |                 |              |

| REST ENABLE             | 0x66     | 8-0-0   | 0                  | 0              | 0               |              |

| RESET                   | 0x99     | 8-0-0   | 0                  | 0              | 0               | RESET ENABLE |

| Identification          | '        |         | <b>'</b>           |                |                 | •            |

| READ ID <sup>[10]</sup> | 0x9F     | 8-8-8   | 4 (0x00)           | 3-7            | 4               |              |

| Power modes             |          |         | •                  |                |                 |              |

| DEEP POWER DOWN         | 0xB9     | 8-0-0   | 0                  | 0              | 0               |              |

| Read memory array       |          |         | <u>.</u>           |                |                 |              |

| READ (DDR)              | 0xEE     | 8-8-8   | 4                  | 3-7            | 1 to ∞          |              |

| Write memory array      |          |         | <u>.</u>           |                |                 |              |

| WRITE (DDR)             | 0xDE     | 8-8-8   | 4                  | 3-7            | 1 to ∞          | WRITE ENABLE |

| Write enable / disabl   | е        |         | <u>.</u>           |                |                 |              |

| WRITE ENABLE            | 0x06     | 8-0-0   | 0                  | 0              | 0               |              |

| WRITE DISABLE           | 0x04     | 8-0-0   | 0                  | 0              | 0               |              |

| Read registers          | -        |         | *                  | -              |                 |              |

| READ ANY REGISTER       | 0x65     | 8-8-8   | 4                  | 3-7            | 2               |              |

| Write registers         | <u> </u> |         | •                  |                |                 | •            |

| WRITE ANY REGISTER      | 0x71     | 8-8-8   | 4                  | 0              | 2               | WRITE ENABLE |

|                         |          |         | •                  |                |                 | •            |

- 10. The two identification registers contents are read together identification 0 followed by identification 1.

- 11. Write enable provides protection against inadvertent changes to memory or register values. It sets the internal write enable latch (WEL) which allows write transactions to execute afterwards.

- 12. Write disable can be used to disable write transactions from execution. It resets the internal write enable latch (WEL).

- 13. The WEL latch stays set to '1' at the end of any successful memory write transaction. After a power down / power up sequence, or a hardware/software reset, WEL latch is cleared to '0'.

- 14. The internal WEL latch is cleared to '0' at the end of any successful register write transaction.

xSPI (Octal) transaction details

#### 4.2 RESET ENABLE transaction

The RESET ENABLE transaction is required immediately before a RESET transaction. Any transaction other than RESET following RESET ENABLE will clear the reset enable condition and prevent a later RESET transaction from being recognized.

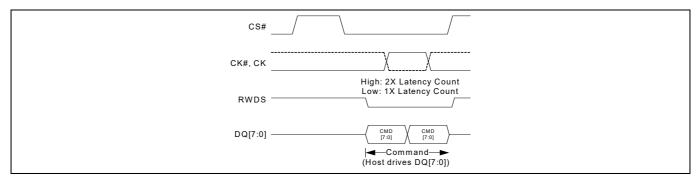

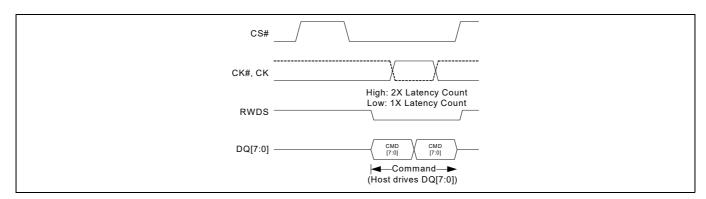

Figure 8 RESET ENABLE transaction (DDR)

#### 4.3 RESET transaction

The RESET transaction immediately following a RESET ENABLE will initiate the software reset process. The software reset provides a software method of returning the device to the standby state. During  $t_{SR}$  (400 ns, max) the device will draw  $I_{CCS}$  current. A software reset will:

- Cause the configuration registers to return to their default values

- Halt self-refresh operation during the software reset process memory array data is considered invalid After software reset finishes, the self-refresh operation will resume. Because self-refresh operation is stopped, and the self-refresh row counter is reset to its default value, some rows may not be refreshed within the required array refresh interval. This may result in the loss of DRAM array data. The host system should consider DRAM array data is lost after software reset and reload any required data.

Figure 9 RESET transaction (DDR)

xSPI (Octal) transaction details

#### 4.4 READ ID transaction

The READ ID transaction provides read access to device identification registers 0 and 1. The registers contain the manufacturer's identification along with device identification. The read data sequence is as follows.

Table 3 READ ID data sequence

| Address space | Byte order | Byte position  | Word data Bit | DQ |

|---------------|------------|----------------|---------------|----|

|               |            | 15<br>14<br>13 | 15            | 7  |

|               |            |                | 14            | 6  |

|               |            |                | 13            | 5  |

|               |            | А              | 12            | 4  |

|               |            | A              | 11 3          | 3  |

|               |            | 10             | 2             |    |

|               |            |                | 9             | 1  |

| Dogistor 0    | Dig andian |                | 8             | 0  |

| Register 0    | Big-endian |                | 7             | 7  |

|               |            |                | 6             | 6  |

|               |            |                | 5             | 5  |

|               |            |                | 4             | 4  |

|               |            | B 3 2 1        | 3             | 3  |

|               |            |                | 2             | 2  |

|               |            |                | 1             | 1  |

|               |            |                | 0             | 0  |

|               |            |                | 15            | 7  |

|               |            |                | 14            | 6  |

|               |            |                | 13            |    |

|               |            |                | 12            | 4  |

|               |            | Α              | 11            | 3  |

|               |            |                | 10            | 2  |

|               |            |                | 9             | 1  |

| D             | D: !:      |                | 8             | 0  |

| Register 1    | Big-endian |                | 7             | 7  |

|               |            |                | 6             | 6  |

|               |            |                | 5             | 5  |

|               |            | _              | 4             | 4  |

|               |            | В              | 3             | 3  |

|               |            |                | 2             | 2  |

|               |            |                | 1             | 1  |

|               |            |                | 0             | 0  |

xSPI (Octal) transaction details

Figure 10 READ ID with 1X latency transaction (DDR)<sup>[15]</sup>

Figure 11 READ ID with 2X latency transaction (DDR)<sup>[16]</sup>

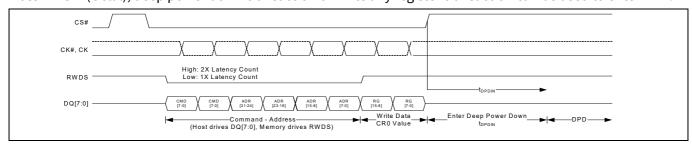

#### 4.5 DEEP POWER DOWN transaction

DEEP POWER DOWN transaction brings the device into deep power down state which is the lowest power consumption state. Writing a "0" to CR0[15] will also bring the device in deep power down state. All register contents are lost in deep power down state and the device powers-up in its default state.

Figure 12 DEEP POWER DOWN transaction (DDR)

- 15. RWDS is driven by HYPERRAM™ phase aligned with data.

- 16. RWDS is driven by HYPERRAM™ during command & address cycles for 2X latency and then is driven again phase aligned with data.

xSPI (Octal) transaction details

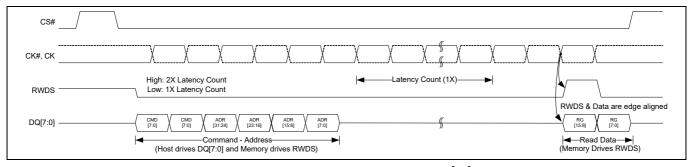

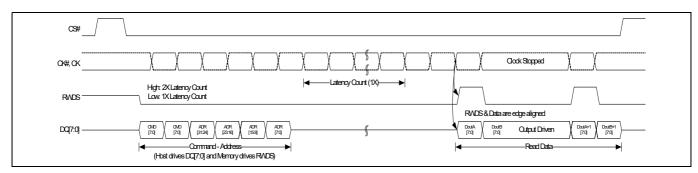

#### 4.6 READ transaction

The READ transaction reads data from the memory array. It has a latency requirement (dummy cycles) which allows the device's internal circuitry enough time to access the addressed memory location. During these latency cycles, the host can tristate the data bus DQ[7:0].

Figure 13 READ with 1X latency transaction (DDR)<sup>[17]</sup>

Figure 14 READ with 2X latency transaction (DDR)<sup>[18]</sup>

- 17. RWDS is driven by HYPERRAM™ phase aligned with data.

- 18. RWDS is driven by HYPERRAM™ during command & address cycles for 2X latency and then is driven again phase aligned with data.

xSPI (Octal) transaction details

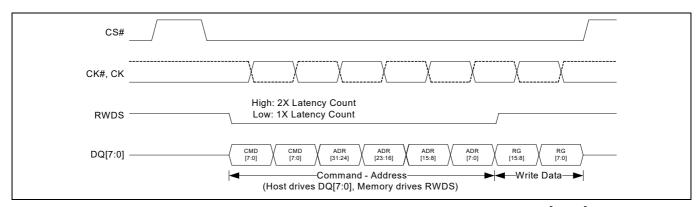

#### 4.7 WRITE transaction

The WRITE transaction writes data to the memory array. It has a latency requirement (dummy cycles) which allows the device's internal circuitry enough time to access the addressed memory location. During these latency cycles, the host can tristate the data bus DQ[7:0].

WRITE ENABLE transaction which sets the WEL latch must be executed before the first WRITE. The WEL latch stays set to '1' at the end of any successful memory write transaction. It must be reset by WRITE DISABLE transaction to prevent any inadvertent writes to the memory array.

Figure 15 WRITE with 1X latency transaction (DDR)<sup>[19, 20]</sup>

Figure 16 WRITE with 2X latency transaction (DDR)<sup>[21, 22]</sup>

- 19. RWDS is driven by the host.

- 20. Data DinA and DinA+2 are masked.

- 21. RWDS is driven by HYPERRAM™ during command and address cycles for 2X latency and then is driven by the host for data masking.

- 22. Data DinA and DinA+2 are masked.

infineon

xSPI (Octal) transaction details

#### 4.8 WRITE ENABLE transaction

The WRITE ENABLE transaction must be executed prior to any transaction that modifies data either in the memory array or the registers.

Figure 17 WRITE ENABLE transaction (DDR)

#### 4.9 WRITE DISABLE transaction

The WRITE DISABLE transaction inhibits writing data either in the memory array or the registers.

Figure 18 WRITE DISABLE transaction (DDR)

#### 4.10 READ ANY REGISTER transaction

The READ ANY REGISTER transaction reads all the device registers. It has a latency requirement (dummy cycles) which allows the device's internal circuitry enough time to access the addressed register location. During these latency cycles, the host can tristate the data bus DQ[7:0].

Figure 19 READ ANY REGISTER with 1X latency transaction (DDR)<sup>[23]</sup>

#### Note

23. RWDS is driven by HYPERRAM™ phase aligned with data.

xSPI (Octal) transaction details

Figure 20 READ ANY REGISTER with 2X latency transaction (DDR)<sup>[24]</sup>

#### 4.11 WRITE ANY REGISTER transaction

The WRITE ANY REGISTER transaction writes to the device registers. It does not have a latency requirement (dummy cycles).

Figure 21 xSPI (Octal) write with no latency transaction (DDR) (Register writes)<sup>[25, 26]</sup>

- 24. RWDS is driven by HYPERRAM™ during command & address cycles for 2X latency and then driven again phase aligned with data.

- 25. Write with no latency transaction is used for register writes only.

- 26. Data mask on RWDS is not supported.

xSPI (Octal) transaction details

### 4.12 Data placement during memory READ/WRITE transactions

Data placement during memory read/write is dependent upon the host. The device will output data (read) as it was written in (write). Hence both Big Endian and Little Endian are supported for the memory array.

Table 4 Data placement during memory READ and WRITE

| Address<br>space | Byte<br>order | Byte position | Word<br>data<br>bit | DQ     | Bit order                                                                                                                        |  |  |  |  |

|------------------|---------------|---------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  |               |               | 15                  | 7      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 14                  | 6      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 13                  | 5      |                                                                                                                                  |  |  |  |  |

|                  |               | А             | 12                  | 4      |                                                                                                                                  |  |  |  |  |

|                  |               | ,,            | 11                  | 3      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 10                  | 2      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 9                   | 1      |                                                                                                                                  |  |  |  |  |

|                  | Big-          |               | 8                   | 0      |                                                                                                                                  |  |  |  |  |

|                  | endian        |               | 7                   | 7      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 6                   | 6      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 5<br>4              | 5<br>4 |                                                                                                                                  |  |  |  |  |

|                  |               | В             | 3                   | 3      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 2                   | 2      | When data is being accessed in memory space: The first byte of each word read or written is the "A" byte and the                 |  |  |  |  |

|                  |               |               | 1                   | 1      | second is the "B" byte.                                                                                                          |  |  |  |  |

|                  |               |               | 0                   | 0      | The bits of the word within the A and B bytes depend on how to data was written. If the word lower address bits 7-0 are written. |  |  |  |  |

| Memory           |               |               | 7                   | 7      | in the A byte position and bits 15-8 are written into the B byte                                                                 |  |  |  |  |

|                  |               |               | 6                   | 6      | position, or vice versa, they will be read back in the same o                                                                    |  |  |  |  |

|                  |               |               | 5                   | 5      | So, memory space can be stored and read in either little-endian                                                                  |  |  |  |  |

|                  |               | ^             | 4                   | 4      | or big-endian order.                                                                                                             |  |  |  |  |

|                  |               | A             | 3                   | 3      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 2                   | 2      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 1                   | 1      |                                                                                                                                  |  |  |  |  |

|                  | Little-       |               | 0                   | 0      |                                                                                                                                  |  |  |  |  |

|                  | endian        |               | 15                  | 7      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 14                  | 6      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 13                  | 5      |                                                                                                                                  |  |  |  |  |

|                  |               | В             | 12                  | 4      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 11                  | 3      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 10                  | 2      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 9                   | 1      |                                                                                                                                  |  |  |  |  |

|                  |               |               | 8                   | 0      |                                                                                                                                  |  |  |  |  |

xSPI (Octal) transaction details

### 4.13 Data placement during register READ/WRITE transactions

Data placement during register read/write is Big Endian.

Table 5 Data placement during register READ/WRITE transactions

| Address<br>space | Byte<br>order | Byte position | Word data<br>bit | DQ                                                                                                             | Bit order                                                                                                           |

|------------------|---------------|---------------|------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                  |               |               | 15               | 7                                                                                                              |                                                                                                                     |

|                  |               |               | 14               | 6                                                                                                              |                                                                                                                     |

|                  |               |               | 13               | 5                                                                                                              |                                                                                                                     |

|                  |               | А             | 12               | 4                                                                                                              | When data is being accessed in register space:                                                                      |

|                  |               | A             | 11               | 3                                                                                                              | During a read transaction on the xSPI (Octal) two bytes are transferred on each clock cycle. The upper order byte A |

|                  |               |               | 10               | 2                                                                                                              | (Word[15:8]) is transferred between the rising and falling                                                          |

|                  | Big-          | 9             | 1                | edges of RWDS (edge-aligned). The lower order byte B (Word[7:0]) is transferred between the falling and rising |                                                                                                                     |

| Dogistor         |               | 8             | 0                | edges of RWDS.                                                                                                 |                                                                                                                     |

| Register         | endian        |               | 7                | 7                                                                                                              | During a write the war are are are horte A (Marel [15:0]) is trans                                                  |

|                  |               |               | 6                | 6                                                                                                              | During a write, the upper order byte A (Word[15:8]) is transferred on the CK rising edge and the lower order byte B |

|                  |               |               | 5                | 5                                                                                                              | (Word[7:0]) is transferred on the CK falling edge.                                                                  |

|                  |               |               | 4                | 4                                                                                                              | So, register space is always read and written in Big-endian order because registers have device dependent fixed bit |

|                  | В             | 3             | 3                | location and meaning definitions.                                                                              |                                                                                                                     |

|                  |               |               | 2                | 2                                                                                                              |                                                                                                                     |

|                  |               |               | 1                | 1                                                                                                              |                                                                                                                     |

|                  |               |               | 0                | 0                                                                                                              |                                                                                                                     |

Memory space

### 5 Memory space

### 5.1 xSPI (Octal) interface

Table 6 Memory space address map (byte based - 8 bits with least significant bit A(0) always set to '0')

| Unit type                 | Count                  | System byte address bits | Address bits | Notes                                                                                                                                                          |

|---------------------------|------------------------|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rows within 256 Mb device | 32,768 (rows)          | A24 - A10                | 24 - 10      | -                                                                                                                                                              |

| Row                       | 64 (half-pages)        | A9 - A4                  | 9 - 4        | Each row has 64 half-pages. Each half-page has 16 bytes. Each column has 1K bytes).                                                                            |

| Half-page                 | 16 (byte<br>addresses) | A3 - A0                  | 3 - 0        | Half-page (HP) address is also referenced as upper column address. A word within a HP address is also referenced as lower column address. A0 always set to "0" |

### 5.2 Density and row boundaries

The DRAM array size (density) of the device can be determined from the total number of system address bits used for the row and column addresses as indicated by the row address bit count and column address bit count fields in the ID0 register. For example: a 256 Mb HYPERRAM<sup>TM</sup> device has 10 column address bits and 15 row address bits for a total of 25 address bits (byte address) =  $2^{25}$  = 32M bytes (16M words). The 10 column address bits indicate that each row holds  $2^{10}$  = 1K bytes or 512 words. The row address bit count indicates there are 32768 rows to be refreshed within each array refresh interval. The row count is used in calculating the refresh interval.

Register space access

### 6 Register space access

#### 6.1 xSPI (Octal) interface

### Table 7 Register space address map (Address bit A0 always set to '0')

| Registers                              | Address (Byte addressable) |

|----------------------------------------|----------------------------|

| Identification registers 0 (ID0[15:0]) | 0x00000000                 |

| Identification registers 1 (ID1[15:0]) | 0x00000002                 |

| Configuration registers 0 (ID0[15:0])  | 0x00000004                 |

| Configuration registers 1 (ID1[15:0])  | 0x0000006                  |

### **6.2** Device identification registers

There are two read-only, nonvolatile, word registers, that provide information on the device selected when CS# is LOW. The device information fields identify:

- Manufacturer

- Type

- Density

- Row address bit count

- Column address bit count

#### Refresh type

#### Table 8 Identification register 0 (ID0) bit assignments

| Bits    | Function                 | Settings (binary)                          |

|---------|--------------------------|--------------------------------------------|

| [15:14] | Reserved                 | 00b - Default                              |

| 13      | Reserved                 | 0b - Default                               |

| [12:8]  | Row address bit count    | 01110b - Fifteen row address bits (256 Mb) |

| [7:4]   | Column address bit count | 1001b - Ten column address bits (default)  |

| [3:0]   | Manufacturer             | 0110b                                      |

ID0 value for S80KS2563 is 0x0E96.

#### Table 9 Identification register 1 (ID1) bit assignments

| Bits   | Function    | Settings (binary)         |

|--------|-------------|---------------------------|

| [15:4] | Reserved    | 0000_0000_0000b (default) |

| [3:0]  | Device type | 0001b - HYPERRAM™ 2.0     |

Register space access

### 6.3 Device configuration registers

### 6.3.1 Configuration register 0 (CR0)

Configuration register 0 (CR0) is used to define the power state and access protocol operating conditions for the HYPERRAM™ device. Configurable characteristics include:

- Wrapped burst length (16, 32, 64, or 128 byte aligned and length data group)

- Wrapped burst type

- Legacy wrap (sequential access with wrap around within a selected length and aligned group)

- Hybrid wrap (Legacy wrap once then linear burst at start of the next sequential group)

- Initial latency

- Variable latency

- Whether an array read or write transaction will use fixed or variable latency. If fixed latency is selected the memory will always indicate a refresh latency and delay the read data transfer accordingly. If variable latency is selected, latency for a refresh is only added when a refresh is required at the same time a new transaction is starting.

- · Output drive strength

- Deep power down (DPD) mode

Table 10 Configuration register 0 (CR0) bit assignments

| CR0 bit | Function                  | Settings (binary)                                                                                                                                                                                                                                                                                                            |  |

|---------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [15]    | Deep power<br>down enable | 1 - Normal operation (default). HYPERRAM™ will automatically set this value t<br>'1' after DPD exit<br>0 - Writing 0 causes the device to enter deep power down                                                                                                                                                              |  |

| [14:12] | Drive strength            | 000 - 34 ohms (default)<br>001 - 115 ohms<br>010 - 67 ohms<br>011 - 46 ohms<br>100 - 34 ohms<br>101 - 27 ohms<br>110 - 22 ohms<br>111 - 19 ohms                                                                                                                                                                              |  |

| [11:8]  | Reserved                  | 1 - Reserved (default)<br>Reserved for future use. When writing this register, these bits should be set to<br>1 for future compatibility.                                                                                                                                                                                    |  |

| [7:4]   | Initial latency           | 0000 - 5 clock latency @ 133 MHz Max frequency<br>0001 - 6 clock latency @ 166 MHz Max frequency<br>0010 - 7 clock latency @ 200 MHz Max frequency (default)<br>0011 - Reserved<br>0100 - Reserved<br><br>1101 - Reserved<br>1110 - 3 clock latency @ 85 MHz Max frequency<br>1111 - 4 clock latency @ 104 MHz Max frequency |  |

| [3]     | Fixed latency<br>enable   | 0 - Variable latency - 1 or 2 times initial latency depending on RWDS during CA cycles.<br>1 - Fixed 2 times initial latency (default)                                                                                                                                                                                       |  |

| [2]     | Hybrid burst<br>enable    | 0: Wrapped burst sequence to follow hybrid burst sequencing 1: Wrapped burst sequence in legacy wrapped burst manner (default)                                                                                                                                                                                               |  |

Register space access

Table 10 Configuration register 0 (CR0) bit assignments (continued)

| CR0 bit | Function     | Settings (binary)                                                          |  |

|---------|--------------|----------------------------------------------------------------------------|--|

| [1:0]   | Burst length | 00 - 128 bytes<br>01 - 64 bytes<br>10- 16 bytes<br>11 - 32 bytes (default) |  |

#### Wrapped burst

A wrapped burst transaction accesses memory within a group of words aligned on a word boundary matching the length of the configured group. Wrapped access groups can be configured as 16, 32, 64, or 128 bytes alignment and length. During wrapped transactions, access starts at the CA selected location within the group, continues to the end of the configured word group aligned boundary, then wraps around to the beginning location in the group, then continues back to the starting location. Wrapped bursts are generally used for critical word first instruction or data cache line fill read accesses.

#### **Hybrid burst**

The beginning of a hybrid burst will wrap within the target address wrapped burst group length before continuing to the next half-page of data beyond the end of the wrap group. Continued access is in linear burst order until the transfer is ended by returning CS# HIGH. This hybrid of a wrapped burst followed by a linear burst starting at the beginning of the next burst group, allows multiple sequential address cache lines to be filled in a single access. The first cache line is filled starting at the critical word. Then the next sequential line in memory can be read in to the cache while the first line is being processed.

Table 11 CR0[2] Control of wrapped burst sequence

| Bit    | Default value | Setting details                                                                                                                                              |  |

|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CR0[2] | 1b            | Hybrid burst enable  CR0[2] = 0: Wrapped burst sequence to follow hybrid burst sequencing  CR0[2] = 1: Wrapped burst sequence in legacy wrapped burst manner |  |

Table 12 Example wrapped burst sequences (Addressing)

| Burst type | Wrap<br>boundary<br>(bytes)    | Start address<br>(Hex) | Sequence of byte addresses (Hex) of data words                                                                                                                                                                                                                   |

|------------|--------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hybrid 64  | 64 wrap<br>once then<br>linear | XXXXXX02               | 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00 (wrap complete, now linear beyond the end of the initial 64 byte wrap group) 40, 42, 44, 46, 48, 4A, 4C, 4E, 50, 52,              |

| Hybrid 64  | 64 wrap<br>once then<br>linear | XXXXXX2E               | 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00, 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, (wrap complete, now linear beyond the end of the initial 64 byte wrap group) 40, 42, 44, 46, 48, 4A, 4B, 4C, 4D, 4E, 4F, 50, 52, |

| Hybrid 16  | 16 wrap<br>once then<br>linear | XXXXXX02               | 02, 04, 06, 08, 0A, 0C, 0E, 00<br>(wrap complete, now linear beyond the end of the initial 16 byte wrap group)<br>10, 12, 14, 16, 18, 1A,                                                                                                                        |

| Hybrid 16  | 16 wrap<br>once then<br>linear | XXXXXXOC               | 0C, 0E, 00, 02, 04, 06, 08, 0A<br>(wrap complete, now linear beyond the end of the initial 16 byte wrap<br>group)<br>10, 12, 14, 16, 18, 1A,                                                                                                                     |

Register space access

Table 12 Example wrapped burst sequences (Addressing) (continued)

| Burst type | Wrap<br>boundary<br>(bytes)    | Start address<br>(Hex) | Sequence of byte addresses (Hex) of data words                                                                                                                            |  |

|------------|--------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Hybrid 32  | 32 wrap<br>once then<br>linear | XXXXXX0A               | 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 00, 02, 04, 06, 08<br>(wrap complete, now linear beyond the end of the initial 32 byte wrap group)<br>20, 22, 24, 26, 28, 2A, |  |

| Wrap 64    | 64                             | XXXXXX02               | 2, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28<br>A, 2C, 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00,                                           |  |

| Wrap 64    | 64                             | XXXXXX2E               | 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00, 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, 2E, 30,                                   |  |

| Wrap 16    | 16                             | XXXXXX02               | 02, 04, 06, 08, 0A, 0C, 0E, 00,                                                                                                                                           |  |

| Wrap 16    | 16                             | XXXXXX0C               | 0C, 0E, 00, 02, 04, 06, 08, 0A,                                                                                                                                           |  |

| Wrap 32    | 32                             | XXXXXX0A               | 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 00, 02, 04, 06, 08,                                                                                                           |  |

| Linear     | Linear<br>burst                | XXXXXX02               | 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22,                                                                                                       |  |

#### **Initial latency**

Memory space read and write transactions or register space read transactions require some initial latency to open the row selected by the CA. This initial latency is  $t_{ACC}$ . The number of latency clocks needed to satisfy  $t_{ACC}$  depends on the clock input frequency can vary from 3 to 7 clocks. The value in CR0[7:4] selects the number of clocks for initial latency. The default value is 7 clocks, allowing for operation up to a maximum frequency of 200MHz prior to the host system setting a lower initial latency value that may be more optimal for the system.

In the event a distributed refresh is required at the time a memory space read or write transaction or register space read transaction begins, the RWDS signal goes High during the CA to indicate that an additional initial latency is being inserted to allow a refresh operation to complete before opening the selected row.

Register space write transactions always have zero initial latency. RWDS may be HIGH or LOW during the CA period. The level of RWDS during the CA period does not affect the placement of register data immediately after the CA, as there is no initial latency needed to capture the register data. A refresh operation may be performed in the memory array in parallel with the capture of register data.

#### **Fixed latency**

A configuration register option bit CR0[3] is provided to make all memory space read and write transactions or register space read transactions require the same initial latency by always driving RWDS HIGH during the CA to indicate that two initial latency periods are required. This fixed initial latency is independent of any need for a distributed refresh, it simply provides a fixed (deterministic) initial latency for all of these transaction types. Fixed latency is the default POR or reset configuration. The system may clear this configuration bit to disable fixed latency and allow variable initial latency with RWDS driven HIGH only when additional latency for a refresh is required.

#### **Drive strength**

DQ and RWDS signal line loading, length, and impedance vary depending on each system design. Configuration register bits CR0[14:12] provide a means to adjust the DQ[7:0] and RWDS signal output impedance to customize the DQ and RWDS signal impedance to the system conditions to minimize high speed signal behaviors such as overshoot, undershoot, and ringing. The default POR or reset configuration value is 000b to select the mid point of the available output impedance options.

The impedance values shown are typical for both pull-up and pull-down drivers at typical silicon process conditions, nominal operating voltage (1.8 V) and 50°C. The impedance values may vary from the typical values depending on the process, voltage, and temperature (PVT) conditions. Impedance will increase with slower process, lower voltage, or higher temperature. Impedance will decrease with faster process, higher voltage, or lower temperature.

Register space access

Each system design should evaluate the data signal integrity across the operating voltage and temperature ranges to select the best drive strength settings for the operating conditions.

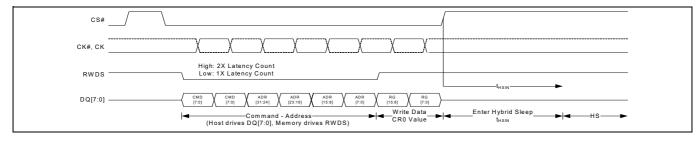

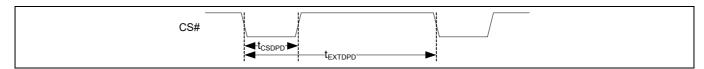

#### Deep power down

When the HYPERRAM<sup>TM</sup> device is not needed for system operation, it may be placed in a very low power consuming state called deep power down (DPD), by writing 0 to CR0[15]. When CR0[15] is cleared to 0, the device enters the DPD state within  $t_{DPDIN}$  time and all refresh operations stop. The data in RAM is lost, (becomes invalid without refresh) during DPD state. Exiting DPD requires driving CS# LOW then HIGH, POR, or a reset. Only CS# and RESET# signals are monitored during DPD mode. For additional details, see "Deep power down" on page 30.

#### 6.3.2 Configuration register 1

Configuration register 1 (CR1) is used to define the refresh array size, refresh rate and hybrid sleep for the HYPERRAM™ device. Configurable characteristics include:

- · Partial array refresh

- Hybrid sleep state

- · Refresh rate

Table 13 Configuration register 1 (CR1) bit assignments

| CR1 bit | Function                        | Setting (binary)                                                                                                                                                            |

|---------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:8]  | Reserved                        | 11111111 - Reserved (default)<br>When writing this register, these bits should keep 0xFFh for future compatibility.                                                         |

| [7]     | Burst type                      | 1 - Linear burst (default)<br>0 - Wrapped burst                                                                                                                             |

| [6]     | Master clock type               | 1 - Single ended - CK (default)<br>0 - Differential - CK#, CK                                                                                                               |

| [5]     | Hybrid sleep                    | <ul><li>1 - Causes the device to enter hybrid sleep state</li><li>0 - Normal operation (default)</li></ul>                                                                  |

| [4:2]   | Partial array<br>refresh        | 000 - Full array (default) 001 - Bottom 1/2 array 010 - Bottom 1/4 array 011 - Bottom 1/8 array 100 - none 101 - Top 1/2 array 110 - Top 1/4 array 111 - Top 1/8 array      |

| [1:0]   | Distributed refresh<br>interval | 10 - 1μs t <sub>CSM</sub> (Industrial plus temperature range devices)<br>11 - Reserved<br>00 - Reserved<br>01 - 4μs t <sub>CSM</sub> (Industrial temperature range devices) |

#### **Burst type**

Two burst types, namely linear and wrapped, are supported in xSPI (Octal) mode by HYPERRAM™. CR1[7] selects which type to use.

#### Master clock type

Two clock types, namely single ended and differential, are supported. CR1[6] selects which type to use.

- In the single ended clock mode (by default), CK# input is not enabled; hence it may be left either floating or biased to HIGH or LOW.

- In the differential clock mode (when enabled), the CK# input can't be left floating. It must be either driven by the host, or biased to HIGH or LOW.

Register space access

#### Partial array refresh

The partial array refresh configuration restricts the refresh operation in HYPERRAM™ to a portion of the memory array specified by CR1[5:3]. This reduces the standby current. The default configuration refreshes the whole array.

#### Hybrid sleep (HS)

When the HYPERRAM™ is not needed for system operation but data in the device needs to be retained, it may be placed in hybrid sleep state to save more power. Enter hybrid sleep state by writing 1 to CR1[5]. Bringing CS# LOW will cause the device to exit HS state and set CR1[5] to 0. Also, POR, or a hardware reset will cause the device to exit hybrid sleep state. Note that a POR or a hardware reset disables refresh where the memory core data can potentially get lost.

#### **Distributed refresh interval**

The HYPERRAM™ device is built with volatile DRAM array which requires periodic refresh of all bits in it. The refresh operation can be done by an internal self-refresh logic that will evenly refresh the memory array automatically. The automatic refresh operation can only be done when the memory array is not actively read or written by the host system. The refresh logic waits for the end of any active read or write before doing a refresh, if a refresh is needed at that time. If a new read or write begins before the refresh is completed, the memory will drive RWDS high during the CA period to indicate that an additional initial latency time is required at the start of the new access in order to allow the refresh operation to complete before starting the new access. The evenly distributed refresh operations require a maximum refresh interval between two adjacent refresh operations. The maximum distributed refresh interval varies with temperature as shown in **Table 14**.

Table 14 Array refresh interval per temperature

| Operating temperature           | Refresh interval t <sub>CSM</sub> | CR1[1:0] |

|---------------------------------|-----------------------------------|----------|

| T <sub>A</sub> ≤ 85 °C          | 4 μs                              | 01b      |

| 85 °C < T <sub>A</sub> ≤ 125 °C | 1 μs                              | 10b      |

The distributed refresh operation requires that the host does not perform burst transactions longer than the distributed refresh interval to prevent the memory from unable doing the distributed refreshes operation when it is needed. This sets an upper limit on the length of read and write transactions so that the automatic distributed refresh operation can be done between transactions. This limit is called the CS# low maximum time ( $t_{CSM}$ ) and the  $t_{CSM}$  will be equal to the maximum distributed refresh interval. The host system is required to respect the  $t_{CSM}$  value by terminating each transaction before violating  $t_{CSM}$ . This can be done by host memory controller splitting long transactions when reaching the  $t_{CSM}$  limit, or by host system hardware or software not performing a single burst read or write transaction that would be longer than  $t_{CSM}$ .

As noted in **Table 14**, the maximum refresh interval is longer at lower temperatures such that t<sub>CSM</sub> could be increased to allow longer transactions. The host may determine the operating temperature from a temperature sensor in the system and use the t<sub>CSM</sub> value from the table accordingly, or it may determine dynamically by reading the read only CR1[1:0] bits in order to set the distributed refresh interval prior to the HYPERRAM™ access.

Interface states

#### 7 Interface states

**Table 15** describes the required value of each signal for each interface state.

**Table 15** Interface states

| Interface state                                                 | V <sub>cc</sub> / V <sub>ccQ</sub>       | CS# | CK, CK# | DQ7-DQ0                                         | RWDS                             | RESET# |

|-----------------------------------------------------------------|------------------------------------------|-----|---------|-------------------------------------------------|----------------------------------|--------|

| Power-off                                                       | < V <sub>LKO</sub>                       | Х   | Х       | HIGH-Z                                          | HIGH-Z                           | Х      |

| Power-on (cold) reset                                           | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | Χ   | Х       | HIGH-Z                                          | HIGH-Z                           | Х      |

| Hardware (warm) reset                                           | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | Χ   | Х       | HIGH-Z                                          | HIGH-Z                           | L      |

| Interface standby                                               | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | Н   | Х       | HIGH-Z                                          | HIGH-Z                           | Н      |

| CA                                                              | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | Master<br>output valid                          | Υ                                | Н      |

| Read initial access latency<br>(data bus turn around<br>period) | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | HIGH-Z                                          | L                                | Н      |

| Write initial access latency (RWDS turn around period)          | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | HIGH-Z                                          | HIGH-Z                           | Н      |

| Read data transfer                                              | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | Slave output<br>valid                           | Slave output<br>valid<br>Z or T  | Н      |

| Write data transfer with initial latency                        | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | Master<br>output valid                          | Master<br>output valid<br>X or T | Н      |

| Write data transfer without initial latency <sup>[27]</sup>     | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Т       | Master<br>output valid                          | Slave output<br>L or HIGH-Z      | Н      |

| Active clock stop <sup>[28]</sup>                               | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | L   | Idle    | Master or<br>slave output<br>valid or<br>HIGH-Z | Y                                | Н      |

| Deep power down                                                 | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | Н   | X or T  | HIGH-Z                                          | HIGH-Z                           | Н      |

| Hybrid sleep                                                    | ≥ V <sub>CC</sub> / V <sub>CCQ</sub> min | Н   | X or T  | HIGH-Z                                          | HIGH-Z                           | Н      |

#### **Notes**

#### Legend

$L = V_{IL}$ ;  $H = V_{IH}$ ; X = either  $V_{IL}$  or  $V_{IH}$ ; Y = either  $V_{IL}$  or  $V_{IH}$  or  $V_{OL}$  or  $V_{OH}$ ; Z = either  $V_{OL}$  or  $V_{OH}$ ; L/H = rising edge; H/L = falling edge; T = Toggling during information transfer; Idle = CK is LOW and CK# is HIGH; Valid = all bus signals have stable L or H level

<sup>27.</sup> Writes without initial latency (with zero initial latency), do not have a turn around period for RWDS. The HYPERRAM™ device will always drive RWDS during the CA period to indicate whether extended latency is required. Since master write data immediately follows the CA period the HYPERRAM™ device may continue to drive RWDS LOW or may take RWDS to HIGH-Z. The master must not drive RWDS during writes with zero latency. writes with zero latency do not use RWDS as a data mask function. All bytes of write data are written (full word writes).

<sup>28.</sup> Active clock stop is described in "Active clock stop" on page 29. DPD is described in "Deep power down" on page 30

infineon

Power conservation modes

### 8 Power conservation modes

### 8.1 Interface standby

Standby is the default, low power, state for the interface while the device is not selected by the host for data transfer (CS# = HIGH). All inputs, and outputs other than CS# and RESET# are ignored in this state.

#### 8.2 Active clock stop

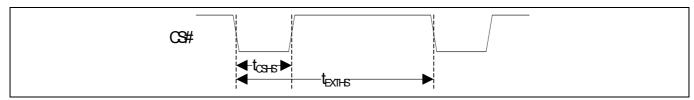

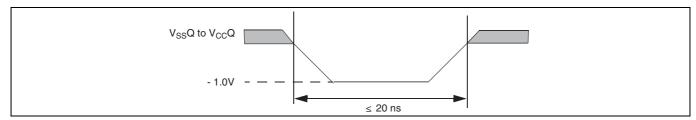

Design Note: Active Clock Stop feature is pending device characterization to determine if it will be supported. The active clock stop state reduces device interface energy consumption to the  $I_{CC6}$  level during the data transfer portion of a read or write operation. The device automatically enables this state when clock remains stable for  $t_{ACC}$  + 30 ns. While in active clock Stop state, read data is latched and always driven onto the data bus.  $I_{CC6}$  shown in "DC characteristics" on page 33.