# NI-5752/5752B Safety, Environmental, and Regulatory Information

# Contents

# NI 5752/5752B Specifications

This document lists specifications for the NI 5752/5752B adapter module. Pair these specifications with the specifications listed in your FlexRIO FPGA module specifications document or your Controller for FlexRIO specifications document.

**Caution** The protection provided by the NI 5752/5752B can be impaired if it is used in a manner not described in this document.

**Caution** To avoid permanent damage to the NI 5752/5752B, disconnect all signals connected to the NI 5752/5752B before powering down the module, and only connect signals after the module has been powered on by the FlexRIO FPGA module or the Controller for FlexRIO.

Note These specifications are characteristic at 25 °C unless otherwise noted.

**Maximum** and **minimum** specifications are warranted not to exceed these values within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

**Characteristic** specifications are unwarranted values that are representative of an average unit operating at room temperature

**Typical** specifications are unwarranted values that are representative of a majority (90%) of units within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

**Note** Using the NI 5752/5752B in a manner not described in this document may impair the protection that the NI 5752/5752B provides.

Specifications are subject to change without notice. For the most recent device specifications, visit ni.com/manuals.

## FlexRIO Documentation

| Document                                                                                | Location                                                                                                               | Description                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Getting started guide<br>for your FlexRIO FPGA<br>module or controller for<br>FlexRIO   | Available from the Start<br>menu and at ni.com/<br>manuals.                                                            | Contains installation instructions for your<br>FlexRIO system.                                                                                                                                                                                                                                |

| Specifications<br>document for your<br>FlexRIO FPGA module<br>or controller for FlexRIO | Available from the Start<br>menu and at ni.com/<br>manuals.                                                            | Contains specifications for your FlexRIO<br>FPGA module or controller for FlexRIO.                                                                                                                                                                                                            |

| Getting started guide<br>for your adapter<br>module                                     | Available from the Start<br>menu and at ni.com/<br>manuals.                                                            | Contains signal information, examples, and CLIP details for your adapter module.                                                                                                                                                                                                              |

| Specifications<br>document for your<br>adapter module                                   | Available from the Start<br>menu and at ni.com/<br>manuals.                                                            | Contains specifications for your adapter module.                                                                                                                                                                                                                                              |

| LabVIEW FPGA Module<br>Help                                                             | Embedded in <b>LabVIEW Help</b> and at ni.com/manuals.                                                                 | Contains information about the basic<br>functionality of the LabVIEW FPGA<br>Module.                                                                                                                                                                                                          |

| Real-Time Module<br>Help                                                                | Embedded in <b>LabVIEW Help</b><br>and at ni.com/manuals.                                                              | Contains information about real-time<br>programming concepts, step-by-step<br>instructions for using LabVIEW with the<br>Real-Time Module, reference information<br>about Real-Time Module VIs and<br>functions, and information about<br>LabVIEW features on real-time operating<br>systems. |

| FlexRIO Help                                                                            | Available from the Start<br>menu and at ni.com/<br>manuals.                                                            | Contains information about the FPGA<br>module front panel connectors and<br>I/O, controller for FlexRIO front panel<br>connectors and I/O, programming<br>instructions, and adapter module<br>component-level IP (CLIP).                                                                      |

| LabVIEW Examples                                                                        | Available in NI Example<br>Finder. In LabVIEW, click Help<br>> Find Examples > Hardware<br>Input and Output > FlexRIO. | Contains examples of how to run FPGA VIs<br>and Host VIs on your device.                                                                                                                                                                                                                      |

| Document             | Location                   | Description                                                         |

|----------------------|----------------------------|---------------------------------------------------------------------|

| IPNet                | Located at ni.com/ipnet.   | Contains LabVIEW FPGA functions and intellectual property to share. |

| FlexRIO product page | Located at ni.com/flexrio. | Contains product information and data sheets for FlexRIO devices.   |

Table 1. FlexRIO Documentation Locations and Descriptions

#### Absolute Maximum Ratings

**Caution** Stresses beyond those listed in this section may cause permanent damage to the adapter module. Avoid swapping the analog and digital cables because doing so will short the digital output terminals to ground.

| (AI+, AI-)             | ±2.1 V          |

|------------------------|-----------------|

|                        |                 |

| External clock input   | -0.5 V to 3.5 V |

|                        |                 |

| Digital input          | -0.5 V to 3.5 V |

|                        |                 |

| Digital output current | 2 mA            |

|                        |                 |

#### Analog Input (AI 0 to AI 31)

# **General Characteristics**

| Max input voltage swing |                                                                                                         |

|-------------------------|---------------------------------------------------------------------------------------------------------|

| Number of channels      | 32, differential, simultaneously sampled (single-ended can be achieved by setting the VGA gain to 6 dB) |

| Type of connector       | 2 VHDCI (dual stack)                                                                                    |

| Differential                 | 2 V <sub>pk-pk</sub>                                                                                                          |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Single-ended                 | 1 V <sub>pk-pk</sub>                                                                                                          |

| Gain range                   | -5 dB to 31 dB                                                                                                                |

| Gain resolution              | 0.125 dB                                                                                                                      |

| Common mode range            | ±1 VDC                                                                                                                        |

| Input impedance              | 100 Ω (AI+, AI-)                                                                                                              |

| Coupling                     | AC-coupled                                                                                                                    |

| ADC manufacturer part number | AFE5801 monolithic analog front end, including a variable gain<br>amplifier and a 12-bit differential pipelined A/D converter |

# **Specific Characteristics**

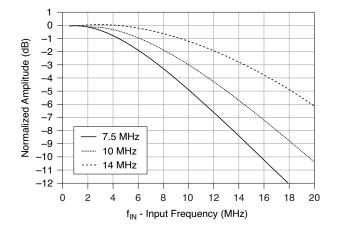

Anti-aliasing filter (-3 dB)7.5 MHz, 10 MHz, and 14 MHz

Figure 1. Anti-aliasing Filter Frequency Response -0 dB Reference at 800 kHz Amplitude

| Gain error                         |                                 |

|------------------------------------|---------------------------------|

| -5 dB to 28 dB                     | ±1.2 dB                         |

| >28 dB                             | ±1.8 dB                         |

| AC coupling cutoff                 | 16 kHz[1]                       |

| Crosstalk                          | <-75 dB at 1 MHz <sup>[2]</sup> |

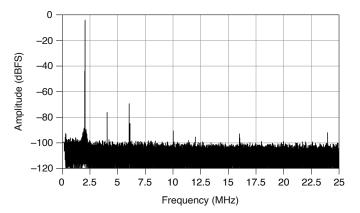

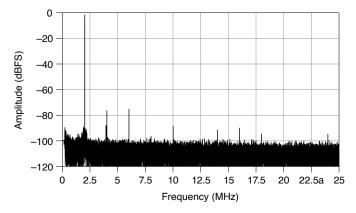

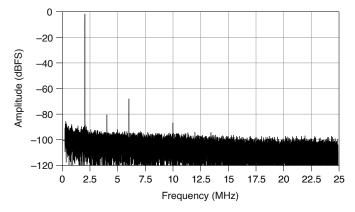

| Signal-to-noise ratio (SNR)        | 66 dBc[ <u>3]</u>               |

| Spurious-free dynamic range (SFDR) | 65 dBc [4]                      |

| Total harmonic distortion (THD)    | 64 dBc[5]                       |

| Average noise density              | 7.4 nV/√Hz <sup>[6]</sup>       |

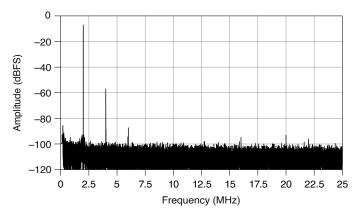

Figure 2. Characteristic Dynamic Performance, Spectrum-64,000 Samples, Coarse Gain 6 dB, 2 MHz, -1 dBFS Differential-Ended Input Signal

Figure 3. Characteristic Dynamic Performance, Spectrum-64,000 Samples, Coarse Gain 12 dB, 2 MHz, -1 dBFS Differential-Ended Input Signal

Figure 4. Characteristic Dynamic Performance, Spectrum-64,000 Samples, Coarse Gain 30 dB, 2 MHz, -1 dBFS Differential-Ended Input Signal

Figure 5. Characteristic Dynamic Performance, Spectrum-64,000 Samples, Coarse Gain 6 dB, 2 MHz, -6 dBFS Single-Ended Input Signal

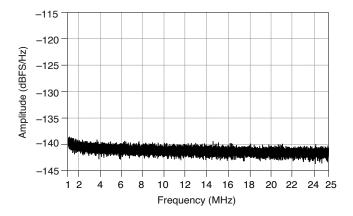

Figure 6. Characteristic Noise Density, Spectrum-64,000 Samples, Coarse Gain 0 dB

#### Sample Clock

| Sample Clock sources         | 50 MHz onboard clock, Sync Clock (PXIe_DSTARA) <sup>[7],[8]</sup> , or CLK IN <sup>[9]</sup> (front panel SMB) |

|------------------------------|----------------------------------------------------------------------------------------------------------------|

| Sample Clock frequency range | 25 MHz to 50 MHz <sup>[10]</sup>                                                                               |

## CLK IN

| Connector                                           | SMB        |

|-----------------------------------------------------|------------|

| Logic level                                         | 3.3 V CMOS |

| Minimum high-level input voltage (V <sub>IH</sub> ) | 2.2 V      |

| Maximum low-level input voltage (V <sub>IL</sub> )  | 0.6 V      |

| Input impedance                                     | > 50 kΩ    |

| Input coupling                                      | DC         |

| Duty cycle | 45% to 55% |

|------------|------------|

|            |            |

# **Digital Inputs**

| Number of channels                                        | 2     |

|-----------------------------------------------------------|-------|

| Connector                                                 | VHDCI |

| Minimum high-level input voltage ( V <sub>IH</sub> (min)) | 2.0 V |

| Maximum low-level input voltage (V <sub>IL</sub> (max))   | 0.8 V |

# Digital Outputs

| Number of channels                                        | 16                          |

|-----------------------------------------------------------|-----------------------------|

| Connector                                                 | VHDCI                       |

| Minimum high-level output voltage (V <sub>OH</sub> (min)) | 2.4 V                       |

| Maximum low-level output voltage ( V <sub>OL</sub> (max)) | 0.55 V                      |

| Maximum output current                                    | 1 mA                        |

| Minimum pulse width                                       | 10 ns                       |

| Maximum toggle frequency                                  | 1 MHz, all outputs toggling |

#### Power

| Power requirements from the FPGA device |                   |  |

|-----------------------------------------|-------------------|--|

| +12 V                                   | 200 mA, 2.4 W max |  |

| +3.3 V                                  | 878 mA, 2.9 W max |  |

| Total power                             | 5.3 W             |  |

|                                         |                   |  |

# Physical

| Dimensions             | 12.9 × 2.0 × 12.1 cm (5.1 × 0.8 × 4.7 in.)          |

|------------------------|-----------------------------------------------------|

| Weight                 | 284 g (10 oz)                                       |

| Front panel connectors | One SMB connector and three 68-pin VHDCI connectors |

#### Environment

| Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

|------------------|---------------------------------------------------|

| Pollution Degree | 2                                                 |

#### Indoor use only.

# **Operating Environment**

| Ambient temperature<br>range | 0 °C to 55 °C (Tested in accordance with IEC 60068-2-1 and<br>IEC 60068-2-2. Meets MIL-PRF-28800F Class 3 low temperature limit and<br>MIL-PRF-28800F Class 2 high temperature limit.) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relative humidity range      | 10% to 90%, noncondensing (Tested in accordance with<br>IEC 60068-2-56.)                                                                                                               |

## Storage Environment

| Ambient temperature<br>range | -20 °C to 71 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2. Meets MIL-PRF-28800F Class 3 limits.) |

|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Relative humidity range      | 5% to 95%, noncondensing (Tested in accordance with<br>IEC 60068-2-56.)                                           |

## Shock and Vibration

| Operating sho                   | ck | 30 g peak, half-sine, 11 ms pulse (Tested in accordance with<br>IEC 60068-2-27. Meets MIL-PRF-28800F Class 2 limits.)              |

|---------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------|

| <b>Random vibr</b><br>Operating |    | 0 Hz, 0.3 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64.)                                                             |

| Nonoperating                    | •  | 0 Hz, 2.4 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64. Test profile<br>ne requirements of MIL-PRF-28800F, Class 3.) |

#### **Compliance and Certifications**

## Safety

This product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:

- IEC 61010-1, EN 61010-1

- UL 61010-1, CSA C22.2 No. 61010-1

**Note** For UL and other safety certifications, refer to the product label or the <u>Online Product Certification</u> section.

## **Electromagnetic Compatibility**

This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:

- EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity

- EN 55011 (CISPR 11): Group 1, Class A emissions

- EN 55022 (CISPR 22): Class A emissions

- EN 55024 (CISPR 24): Immunity

- AS/NZS CISPR 11: Group 1, Class A emissions

- AS/NZS CISPR 22: Class A emissions

- FCC 47 CFR Part 15B: Class A emissions

- ICES-001: Class A emissions

**Note** In the United States (per FCC 47 CFR), Class A equipment is intended for use in commercial, light-industrial, and heavy-industrial locations. In Europe, Canada, Australia, and New Zealand (per CISPR 11), Class A equipment is intended for use only in heavy-industrial locations. Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medical equipment that does not intentionally generate radio frequency energy for the treatment of material or inspection/analysis purposes.

Note For EMC declarations, certifications, and additional information, refer to the <u>Online Product Certification</u> section.

# CE Compliance $C \in$

This product meets the essential requirements of applicable European Directives, as follows:

- 2014/35/EU; Low-Voltage Directive (safety)

- 2014/30/EU; Electromagnetic Compatibility Directive (EMC)

# **Online Product Certification**

Refer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit <u>ni.com/certification</u>, search by model number or product line, and click the appropriate link in the Certification column.

# **Environmental Management**

NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.

For additional environmental information, refer to the **Minimize Our Environmental Impact** web page at <u>ni.com/environment</u>. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.

#### Waste Electrical and Electronic Equipment (WEEE)

EU Customers At the end of the product life cycle, all NI products must be disposed of according to local laws and regulations. For more information about how to recycle NI products in your region, visit <u>ni.com/</u><u>environment/weee</u>.

#### 电子信息产品污染控制管理办法(中国 RoHS)

中国客户 National Instruments 符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。关于 National Instruments 中国 RoHS 合规性信息,请登录 ni.com/environment/rohs\_china。(For information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

$\frac{1}{2}$  100  $\Omega$  source assumed, AFE5801 internal VGA DC coupling enabled

<sup>2</sup> Measured on one channel with the test signal applied to another channel, with the same range setting on both channels

<sup>3</sup>-1 dBFS differential input signal, 6 dB gain, f<sub>in</sub> = 2 MHz

<sup>4</sup><sub>-</sub>-1 dBFS differential input signal, 17 dB gain, f<sub>in</sub> = 2 MHz

<sup>5</sup> -1 dBFS differential input signal, 17 dB gain, f<sub>in</sub> = 2 MHz

<sup>6</sup> Input referenced, 5 MHz, 31 dB gain, low-noise mode

<sup>7</sup> Sync Clock (PXIe\_DSTARA) is only available on NI PXI Express FlexRIO FPGA modules, such as the NI PXIe-796xR. On PXI Express modules, Sync Clock is driven by the PXIe\_DSTARA signal from the PXI/PXI Express backplane. For NI PXI modules, such as the NI PXI-795xR, and controllers for FlexRIO, such as the NI-793xR, Sync Clock (PXIe\_DSTARA) is not available.

<sup>8</sup> If you change the frequency of Sync Clock (PXIe\_DSTARA) or CLK IN (when used as the Sample Clock), you must assert ForceInit.

<sup>9</sup> If you change the frequency of Sync Clock (PXIe\_DSTARA) or CLK IN (when used as the Sample Clock), you must assert ForceInit.

$\frac{10}{10}$  If you change the frequency of Sync Clock (PXIe\_DSTARA) or CLK IN (when used as the Sample Clock), you must assert ForceInit.