## Product Change Notification / SYST-20QRVG639

## Date:

21-Jun-2023

## **Product Category:**

Ethernet PHYs

## **PCN Type:**

**Document Change**

## **Notification Subject:**

Data Sheet - LAN8670/2 10BASE-T1S Ethernet PHY Transceiver Data Sheet

## Affected CPNs:

SYST-20QRVG639\_Affected\_CPN\_06212023.pdf SYST-20QRVG639\_Affected\_CPN\_06212023.csv

## **Notification Text:**

#### SYST-20QRVG639

Microchip has released a new Datasheet for the LAN8670/2 10BASE-T1S Ethernet PHY Transceiver Data Sheet of devices. If you are using one of these devices please read the document located at LAN8670/2 10BASE-T1S Ethernet PHY Transceiver Data Sheet

Notification Status: Final

**Description of Change:** Update for silicon revision 4 (product revision C1)

Impacts to Data Sheet: See above details.

Reason for Change: To Improve Productivity Change Implementation Status: Complete

Date Document Changes Effective: 21 Jun 2023

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices::N/A

## Attachments:

## LAN8670/2 10BASE-T1S Ethernet PHY Transceiver Data Sheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

## **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections. Affected Catalog Part Numbers (CPN)

LAN8670B1-E/LMX LAN8670B1T-E/LMX LAN8670C1-E/LMX LAN8670C1-E/LMXVAO LAN8670C1T-E/LMX LAN8670C1T-E/LMXVAO LAN8672B1-E/LNX LAN8672B1T-E/LNX LAN8672C1-E/LNXVAO LAN8672C1T-E/LNXVAO

# **10BASE-T1S Ethernet PHY Transceiver**

LAN8670/2

## Description

The LAN8670/2 is a high-performance 10BASE-T1S single-pair Ethernet PHY transceiver for 10 Mbit/s halfduplex networking over a single pair of conductors. Utilizing standard Ethernet technology in sensor/ actuator networks reduces application costs by eliminating gateways necessary with legacy networking technologies. The ability to connect multiple PHYs onto a common mixing segment further saves implementation costs by reducing cabling and switch ports. The LAN8670/2 is designed for use in high-reliability cost sensitive automotive, industrial, backplane, and building automation sensor/actuator applications.

### Highlights

- High-performance 10BASE-T1S Ethernet PHY designed according to IEEE Std 802.3cg<sup>™</sup>-2019

- 10 Mbit/s over single balanced pair

- Half-duplex multidrop mixing segments up to at least 25m with up to at least 8 PHYs

- Half-duplex point-to-point link segments up to at least 15m

- Media Independent Interface (MII)

- Carrier Sense Multiple Access / Collision Detection (CSMA/CD) media access control

- Physical Layer Collision Avoidance (PLCA)

- Allows for high bandwidth utilization by avoiding collisions on the medium

- Burst mode for transmission of multiple packets for latency-sensitive applications

- Minimize latency for time-sensitive applications by assigning multiple PLCA IDs per node

- Application Controlled Media Access (ACMA) for implementation of collision-free Time-Division Multiple Access (TDMA) methods

- IEEE Std 802.1AS<sup>™</sup> / IEEE 1588<sup>™</sup> application support

- Enables high-precision clock recovery with ultralow jitter for microcontrollers without Time-Sensitive Networking (TSN) support

- Credit-based traffic shaping

- EtherGREEN<sup>™</sup> Energy Efficiency

- Low power 10BASE-T1S PHY operation

- Ultra-low power sleep mode

- Wake up triggered by either MDI activity or local WAKE\_IN

- WAKE\_OUT pulse assertion

- INH output for enable/disable of ECU supply

- Cable fault (open/short) diagnostics and Signal Quality Indication (SQI) support

- Over-temperature and under-voltage detection

- Enhanced electromagnetic compatibility / electromagnetic interference (EMC/EMI) performance

- Low RF emissions

- Digital output drive strength adjust

- Robust against injected currents and network cable shorts to ground or battery

- Simple low cost bus interface network

- Single 3.3V supply with integrated 1.8V regulator

- Small footprint 32-pin (5 x 5 mm), and 36-pin (6 x 6 mm) VQFN packages with wettable flanks

- -40°C to +125°C extended temperature range

- AEC-Q100 qualification

- Functional Safety Support (ISO 26262)

- Functional Safety Manual

- FMEDA

- Dependent Failure Analysis (DFA)

#### **Target Applications**

- In-vehicle networking and automotive zonal architecture

- Sensor/actuator networks

- Industrial control cabinets and machine control

- Building automation

- LED lighting

# Conformity

Table 1 shows the conformity relationship between data sheet, silicon, and product revisions. This data sheet applies to silicon revision 4 (0100b) as shown below.

| Product Revision <sup>1</sup> | Silicon Revision <sup>2</sup> | Data Sheet Revision |

|-------------------------------|-------------------------------|---------------------|

| A0                            | <b>Rev 0 (</b> 0000b <b>)</b> | DS60001573A         |

| B1                            | Rev 2 (0010b)                 | DS60001573B         |

| B1                            | Rev 2 (0010b)                 | DS60001573C         |

| C1                            | Rev 4 (0100b)                 | DS60001573F         |

Notes:

- 1. The product revision is noted in the package top marking.

- 2. The silicon revision is obtained by reading the Manufacturer's Model Revision from the PHY Identifier 2 register.

#### **Related Links**

9. Package Marking Information

5.1.4. PHY\_ID2

# **Table of Contents**

| Des | scriptic | on                                         | 1   |

|-----|----------|--------------------------------------------|-----|

| Cor | nformit  | ty                                         | 2   |

| 1.  | Prefa    | ce                                         | 5   |

|     | 1.1.     | General Terms                              | 5   |

|     | 1.2.     | Buffer Types                               | 6   |

|     | 1.3.     | Register Bit Types                         | 6   |

|     | 1.4.     | Reference Documents                        | 7   |

| 2.  | Introd   | duction                                    |     |

|     | 2.1.     | General Description                        | 8   |

|     | 2.2.     | The LAN8670/2 Family                       |     |

|     | 2.3.     | Example Systems                            |     |

| 3.  | Pin D    | escription and Configuration               | 12  |

|     | 3.1.     | LAN8670 Pin Assignments                    |     |

|     | 3.2.     | LAN8672 Pin Assignments                    |     |

|     | 3.3.     | Pin Descriptions                           |     |

|     | 3.4.     | Configuration Straps                       |     |

|     | 3.5.     | Pin Configuration                          |     |

| 4.  | Funct    | ional Descriptions                         | 22  |

|     | 4.1.     | Media Independent Interface (MII)          |     |

|     | 4.2.     | Serial Management Interface (SMI)          |     |

|     | 4.3.     | Interrupt Management                       |     |

|     | 4.4.     | Resets                                     |     |

|     | 4.5.     | Initialization                             |     |

|     | 4.6.     | Clock Manager                              |     |

|     | 4.7.     | Physical Layer Collision Avoidance (PLCA)  |     |

|     | 4.8.     | Application Controlled Media Access (ACMA) |     |

|     | 4.9.     | Credit Based Traffic Shaping               |     |

|     | 4.10.    | Configuration Protection                   |     |

|     |          | Time Synchronization                       |     |

|     |          | Sleep Mode                                 |     |

|     |          | signal Quality Indicator (SQI)             |     |

|     |          | Cable Fault Diagnostics                    |     |

|     |          | Safety Notifications                       |     |

| 5.  | Regist   | ter Descriptions                           | 50  |

|     | 5.1.     | SMI Basic Control and Status Registers     | 51  |

|     | 5.2.     | PMA/PMD Registers                          |     |

|     | 5.3.     | PCS Registers                              |     |

|     | 5.4.     | Miscellaneous Registers                    |     |

| 6.  | Applia   | cation Information                         | 145 |

|     | 6.1.     | MII Connectivity                           |     |

|     | 6.2.     | System Configuration without Sleep Mode    |     |

|     |          |                                            |     |

|     | 6.3.   | Power Connectivity                                 | 146   |

|-----|--------|----------------------------------------------------|-------|

|     | 6.4.   | Electromagnetic Compatibility (EMC) Considerations | 148   |

|     | 6.5.   | Crystal Oscillator Selection                       | 149   |

|     | 6.6.   | Reference Schematics                               | 150   |

| 7.  | Oper   | ational Characteristics                            | . 158 |

|     | 7.1.   | Absolute Maximum Ratings                           | . 158 |

|     | 7.2.   | Operating Conditions                               | 159   |

|     | 7.3.   | Power Consumption                                  | 159   |

|     | 7.4.   | Package Thermal Specifications                     | 160   |

|     | 7.5.   | DC Specifications (other than 10BASE-T1S PMA)      | 160   |

|     | 7.6.   | AC Specifications                                  | 162   |

|     | 7.7.   | Crystal Specifications                             | 171   |

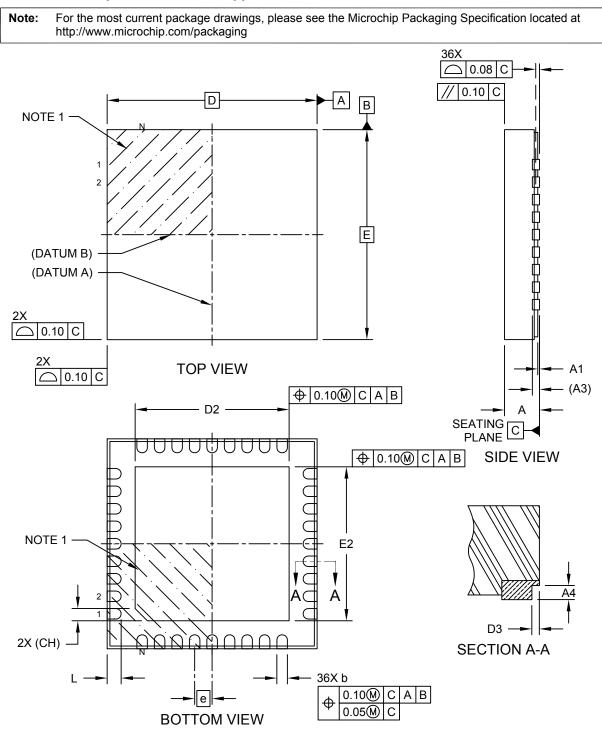

| 8.  | Packa  | aging Information                                  | . 172 |

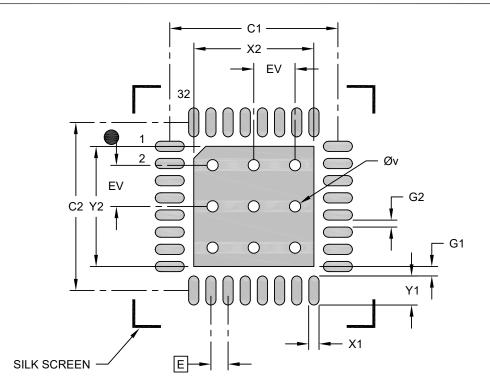

|     | 8.1.   | 32-VQFN (LAN8670 Only)                             | 172   |

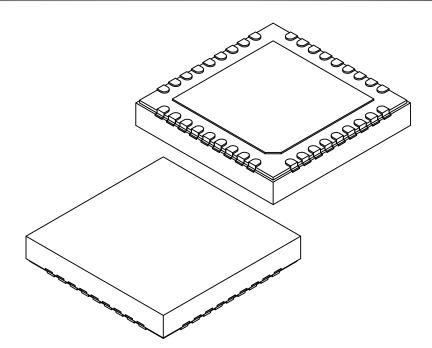

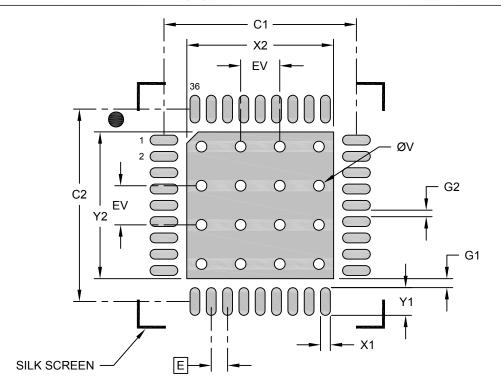

|     | 8.2.   | 36-VQFN (LAN8672 Only)                             | 175   |

| 9.  | Packa  | age Marking Information                            | . 178 |

| 10. | Data   | Sheet Revision History                             | 179   |

| Mic | rochip | o Information                                      | 180   |

|     | The N  | /icrochip Website                                  | 180   |

|     |        | uct Change Notification Service                    |       |

|     |        | omer Support                                       |       |

|     | Produ  | uct Identification System                          | . 181 |

|     | Micro  | pchip Devices Code Protection Feature              | 182   |

|     | Legal  | Notice                                             | . 182 |

|     | Trade  | emarks                                             | 182   |

|     | Quali  | ty Management System                               | . 183 |

|     | World  | dwide Sales and Service                            | 184   |

|     |        |                                                    |       |

# 1. Preface

## 1.1 General Terms

#### Table 1-1. General Terms

| Term       | Description                                                                                                                                                                                           |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10BASE-T   | 10 Mbit/s Ethernet over twisted pair, IEEE Std 802.3 <sup>™</sup> Clause 14                                                                                                                           |  |  |

| 10BASE-T1L | 10 Mbit/s Ethernet over long-reach single pair of conductors, IEEE Std 802.3 Clause 146                                                                                                               |  |  |

| 10BASE-T1S | 10 Mbit/s Ethernet over short-reach single pair of conductors, IEEE Std 802.3 Clause 147                                                                                                              |  |  |

| ACMA       | Application Controlled Media Access                                                                                                                                                                   |  |  |

| BIN        | Bus Interface Network                                                                                                                                                                                 |  |  |

| BT         | Bit Time, 100 ns for 10 Mbps Ethernet                                                                                                                                                                 |  |  |

| CSMA/CD    | Carrier Sense Multiple Access with Collision Detection                                                                                                                                                |  |  |

| CSR        | Control and Status Register                                                                                                                                                                           |  |  |

| DFA        | Dependent Failure Analysis                                                                                                                                                                            |  |  |

| FMEDA      | Failure Modes, Effects, and Diagnostic Analysis                                                                                                                                                       |  |  |

| IPG        | Inter-packet gap time (96 BT), IEEE Std 802.3 Clause 4                                                                                                                                                |  |  |

| IPG1       | Inter-packet gap time part 1 (typically 64 BT), IEEE Std 802.3 Clause 4                                                                                                                               |  |  |

| IPG2       | Inter-packet gap time part 2 (typically 32 BT), IEEE Std 802.3 Clause 4                                                                                                                               |  |  |

| LDO        | Low Dropout Regulator                                                                                                                                                                                 |  |  |

| MAC        | Media Access Controller                                                                                                                                                                               |  |  |

| MDI        | Medium Dependent Interface                                                                                                                                                                            |  |  |

| MII        | Media Independent Interface, IEEE Std 802.3 Clause 22                                                                                                                                                 |  |  |

| PCS        | Physical Coding Sublayer                                                                                                                                                                              |  |  |

| PLCA       | Physical Layer Collision Avoidance, IEEE Std 802.3 Clause 148                                                                                                                                         |  |  |

| PMA        | Physical Medium Attachment sublayer                                                                                                                                                                   |  |  |

| PMD        | Physical Medium Dependent sublayer                                                                                                                                                                    |  |  |

| POR        | Power-on Reset                                                                                                                                                                                        |  |  |

| RS         | Reconciliation Sublayer                                                                                                                                                                               |  |  |

| SC-MII     | Single Clock Media Independent Interface. This is a variant of the MII described in IEEE Std 802.3<br>Clause 22 in which the PHY drives a single clock to the MAC for both transmit and receive data. |  |  |

| SFD        | Start-of-Frame Delimiter. This is the 8-bit value indicating the end of the preamble and the beginning of an Ethernet frame.                                                                          |  |  |

| SMI        | Serial Management Interface, also known as MII Management Interface, IEEE Std 802.3 Clause 22                                                                                                         |  |  |

| STA        | Station management entity                                                                                                                                                                             |  |  |

| SQI        | Signal Quality Indicator                                                                                                                                                                              |  |  |

| TSSI       | Time Synchronization Service Interface, IEEE Std 802.3 Clause 90                                                                                                                                      |  |  |

## 1.2 Buffer Types

| Buffer     | Description                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIO        | Analog bi-directional                                                                                                                                                                                                                   |

| ICLK       | Crystal input                                                                                                                                                                                                                           |

| OCLK       | Crystal output                                                                                                                                                                                                                          |

| PD         | 55 $k\Omega$ (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are not enabled.                                                                                                          |

|            | Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |

| PU         | 55 kΩ (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are not enabled.<br>Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal                     |

|            | resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.                                                                                               |

| VI-VDDAU   | 3.3V input (VDDAU power domain)                                                                                                                                                                                                         |

| VIS-VDDP   | 3.3V Schmitt-triggered input (VDDP power domain)                                                                                                                                                                                        |

| VO-VDDP    | 3.3V output with configurable output drive (VDDP power domain)                                                                                                                                                                          |

| VOH-VDDP   | 3.3V high-speed output with configurable output drive (VDDP power domain)                                                                                                                                                               |

| VODL-VDDP  | 3.3V n-channel open-drain sink output drive (VDDP power domain)                                                                                                                                                                         |

| VODH-VDDAU | 3.3V p-channel open-drain source output drive(VDDAU power domain)                                                                                                                                                                       |

Table 1-2.

LAN8670/2

Buffer Type Descriptions

**Note:** Digital signals are not 5V tolerant unless specified.

## **1.3** Register Bit Types

The following table describes the register bit attributes used throughout this document.

| Register Bit Type<br>Notation | Register Bit Description                                                                                                                                                                           |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R                             | Read: A register or bit with this attribute can be read.                                                                                                                                           |  |  |

| W                             | Write: A register or bit with this attribute can be written.                                                                                                                                       |  |  |

| RO                            | Read Only: A register or bit with this attribute is read only; writing has no effect.                                                                                                              |  |  |

| RC                            | Read to Clear: Content is cleared after the read. Writes have no effect.                                                                                                                           |  |  |

| SC                            | <b>Self Clearing:</b> A bit with this attribute will be cleared to '0' after being written as '1'. Hardware often clears such bits following the completion of some action initiated by the write. |  |  |

| NASR                          | <b>Not Affected by Software Reset:</b> The state of NASR bits do not change on assertion of a software reset.                                                                                      |  |  |

Many of these register bit notations can be combined. Some examples of this are:

- R/W: Can be written. Will return current setting on a read.

- R/W SC: Bit is readable. When set, it will automatically be cleared by hardware once some action is complete.

## **1.4** Reference Documents

- 1. IEEE Std 802.3<sup>™</sup>-2018, IEEE Standard for Ethernet. standards.ieee.org/standard/802\_3-2018.html

- IEEE Std 802.3cg<sup>™</sup>-2019, IEEE Standard for Ethernet, Amendment 5: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors. standards.ieee.org/standard/802\_3cg-2019.html

- 3. IEEE Std 1588<sup>™</sup>-2019, IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems. standards.ieee.org/standard/1588-2019.html

- 4. IEEE Std 802.1AS<sup>™</sup>-2020, IEEE Standard for Local and Metropolitan Area Networks--Timing and Synchronization for Time-Sensitive Applications. standards.ieee.org/standard/802\_1AS-2020.html

- 5. OPEN Alliance, 10BASE-T1S Advanced Diagnostic PHY Features www.opensig.org/about/specifications/

- 6. OPEN Alliance, 10BASE-T1S System Implementation Specification www.opensig.org/about/specifications/

## 2. Introduction

## 2.1 General Description

The Microchip LAN8670/2 is a compact, low power, and cost-effective single-port 10BASE-T1S Ethernet PHY designed according to the IEEE Std 802.3cg-2019 specification. The device provides 10 Mbit/s half-duplex transmit and receive capability over a single balanced pair of conductors such as Unshielded Twisted Pair (UTP) cable. The LAN8670/2 is designed for use in applications requiring an extended temperature range (-40°C to +125°C ambient) and is optimized for AEC-Q100 automotive Grade 1 use cases. The device is also compliant to automotive and industrial EMC and EMI requirements. The single power supply and simple bus interface network simplifies its integration into small form factor applications.

The LAN8670/2 allows for the creation of both half-duplex multidrop and point-to-point network topologies. Point-to-point link segments of up to at least 15m in length are supported. The multidrop mode supports up to at least 8 PHYs connected to a common mixing segment of up to at least 25m in length. The ability to connect multiple PHYs to a common mixing segment reduces weight and implementation costs by requiring fewer connectors, individual cables and switch ports.

Access to the physical medium is managed by CSMA/CD and optionally supplemented by Physical Layer Collision Avoidance (PLCA) as per IEEE Std 802.3cg-2019. In addition to the single transmit opportunity per bus cycle in this standard, the LAN8670/2 has the ability to be configured with up to 8 additional transmit opportunities in each bus cycle. As an alternative to PLCA, the Application Controlled Media Access (ACMA) pin can be used to implement time-division multiple access (TDMA) to the physical medium.

The LAN8670/2 interfaces with an Ethernet MAC via standard MII, or via the Single Clock Media Independent Interface (SC-MII) which is similar to the MII but with fewer pins. An integrated serial management interface (SMI) provides rapid register access and configuration at up to 4 MHz.

Microchip's LAN8670/2 EtherGREEN energy efficient technology provides low power 10BASE-T1S PHY operation along with an ultra-low power sleep mode with flexible wake options.

In addition, the LAN8670/2 can be used to implement high-precision clock synchronization. This enables implementation of the IEEE Std 802.1AS profile, among others, of IEEE Std 1588 for applications utilizing AVB or other Time Sensitive Networking (TSN) standards. This feature can be used to provide a Timing Synchronization Service Interface (TSSI) as specified in IEEE Std 802.3<sup>T</sup> Clause 90 as part of a TSN implementation.

Advanced PHY diagnostics are provided, which enable troubleshooting and monitoring capabilities such as cable defect detection of shorts or opens, a receiver Signal Quality Indicator (SQI), PLCA diagnostics, over-temperature, under-voltage detection, comprehensive status interrupt support, and various loopback and test modes.

The LAN8670/2 is designed to be used in ISO 26262 Functional Safety applications. A Functional Safety Package is available, including Safety Manual; Failure Modes, Effects, and Diagnostic Analysis (FMEDA); and Dependent Failure Analysis (DFA). Please contact Microchip support for additional information.

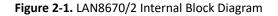

An internal block diagram of the LAN8670/2 is shown in the following figure.

### 2.2 The LAN8670/2 Family

The Microchip LAN8670/2 family includes the following devices:

- LAN8670

- LAN8672

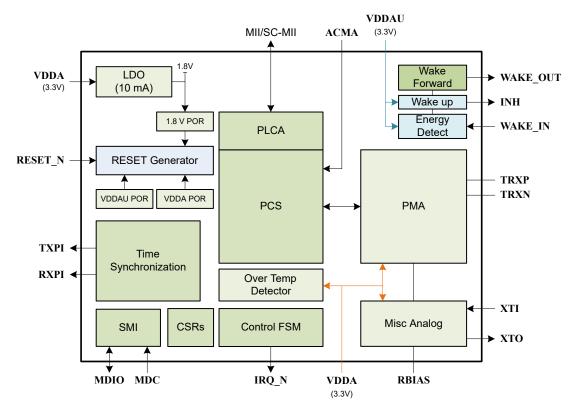

Device specific features that do not pertain to the entire LAN8670/2 family are called out independently throughout this document. Table 2-1 below provides a summary of the feature differences between family members.

Table 2-1. LAN8670/2 Family Feature Matrix

**Important:** Since some pins are shared between different modes, not all features are available simultaneously. For more information, see the Pin Description and Configuration section.

## 2.3 Example Systems

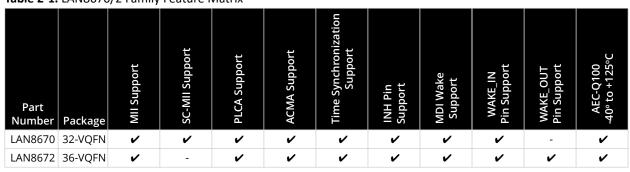

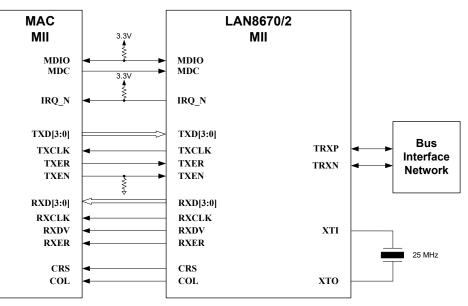

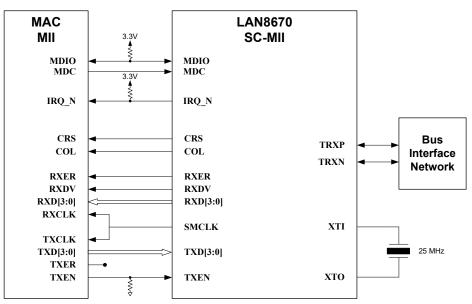

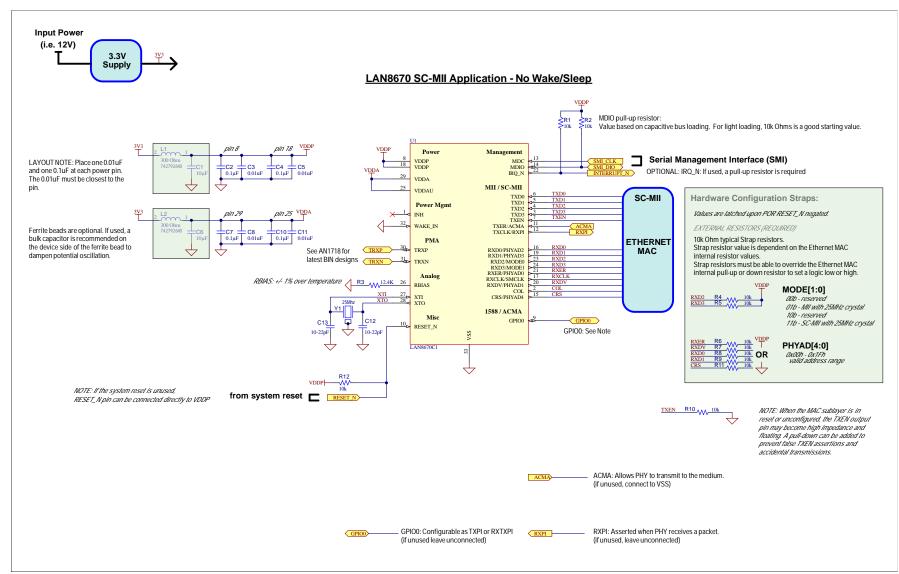

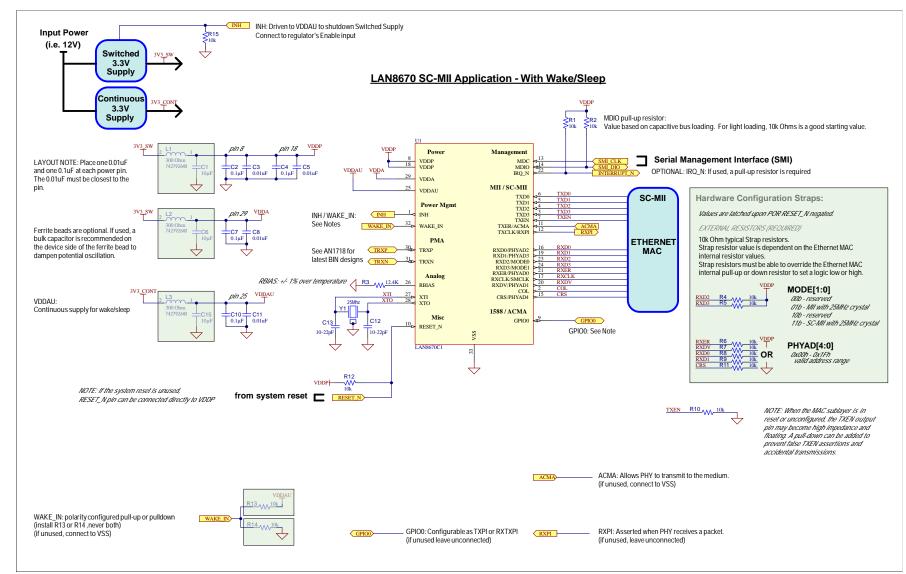

This section shows example of system block diagrams that apply to all family members.

**Note:** All family members support advanced features such as ACMA and signals for time synchronization, but they are not shown below since the pin configurations vary among the family members.

**Note:** The clock source for MII is a crystal connected between pins XTI and XTO. Additional information is available in the Pin Descriptions section.

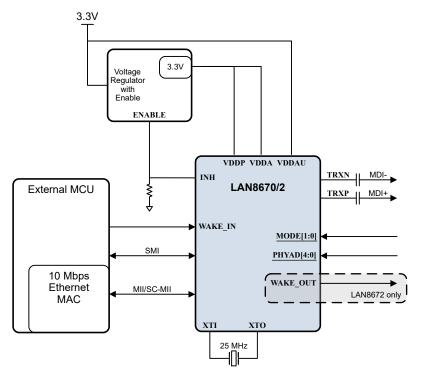

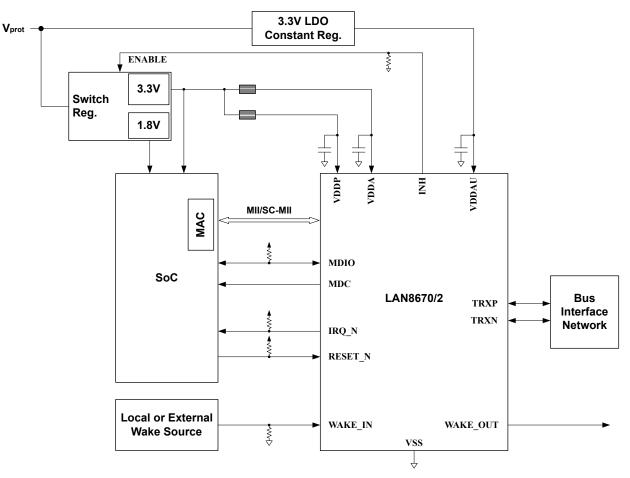

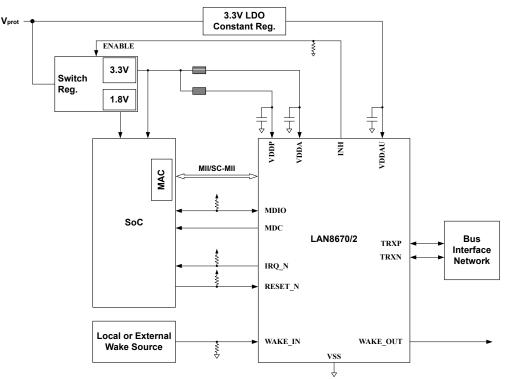

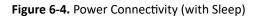

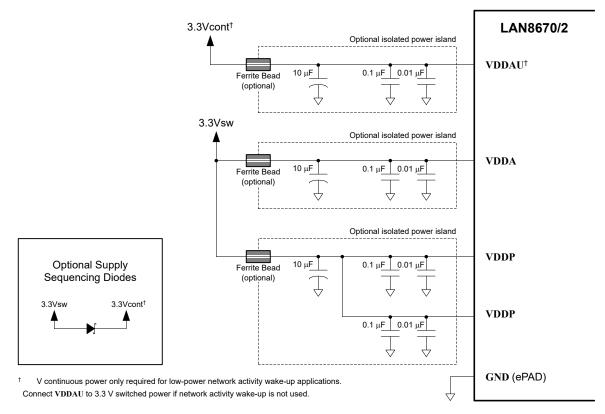

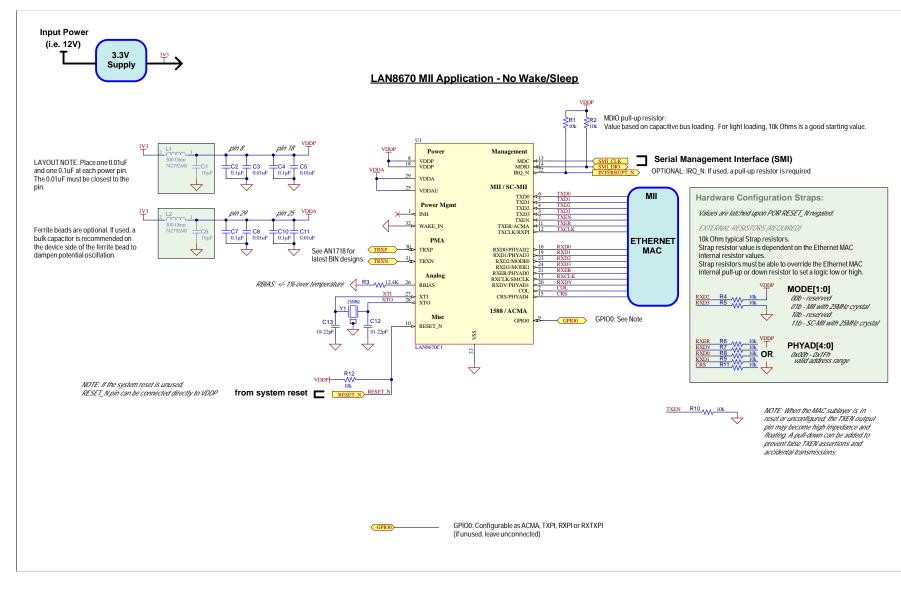

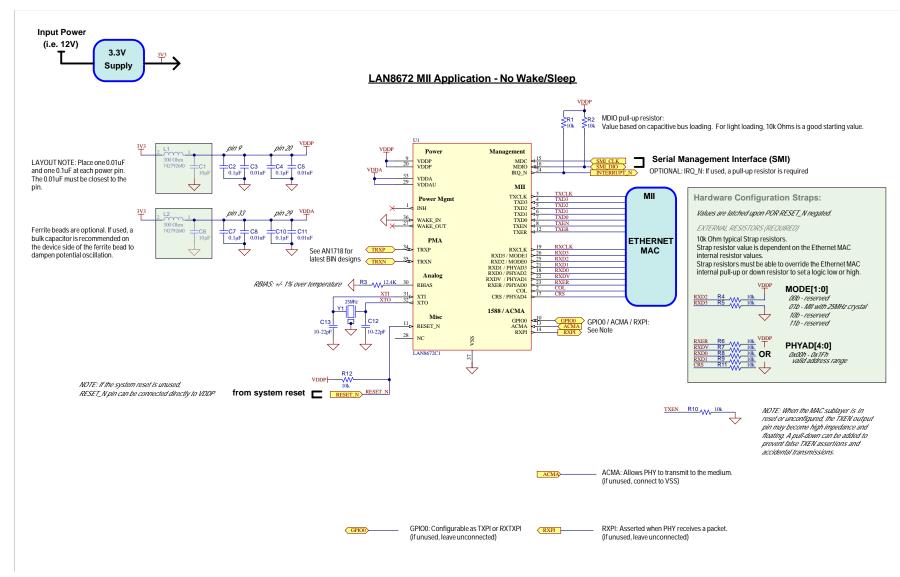

An example system-level block diagram for the LAN8670/2 is shown in Figure 2-2, below. This system does not use sleep mode, so VDDA and VDDAU can be treated as the same supply and VDDP must only be properly isolated from the analog supplies.

Figure 2-2. Simple System Using LAN8670/2

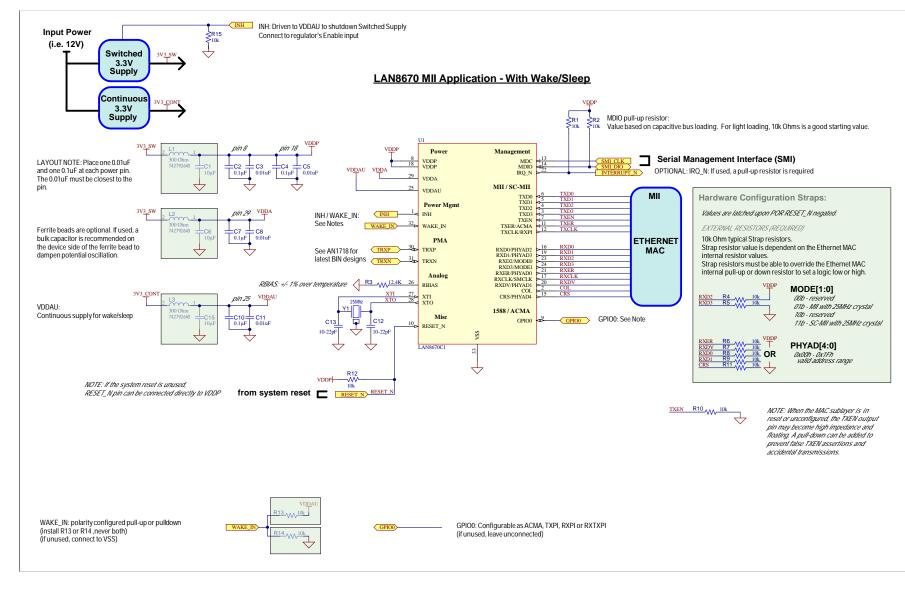

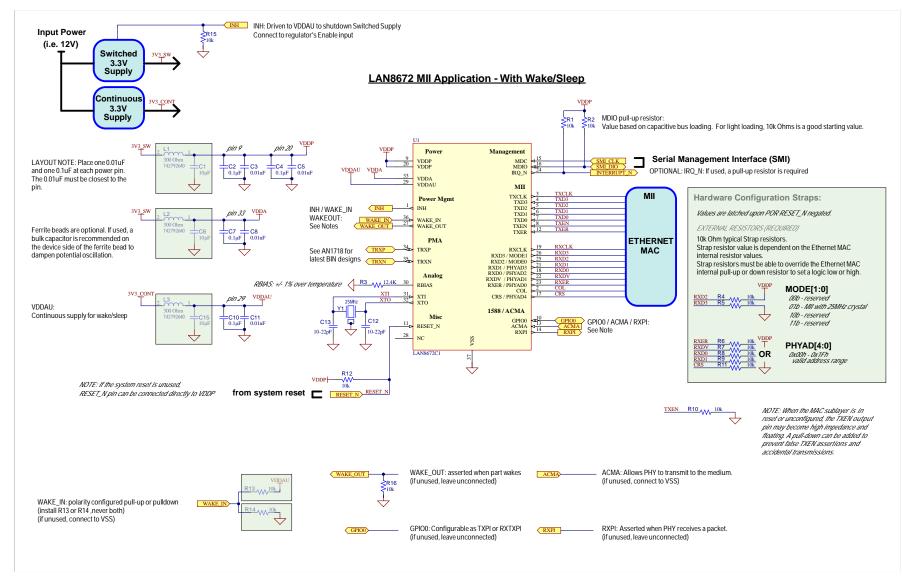

Figure 2-3 shows a system which is designed to use the low power sleep mode so the constant voltage supply VDDAU is separate from the other voltage supplies. VDDA and VDDP will be disabled in sleep mode. In this particular system, the external MCU will initiate sleep mode and then ensure that all inputs to the LAN8670/2 are high-impedance. In a system where external power supplies are required to remain active while other devices shut down, the LAN8670/2 can drive the INH pin for a programmable delay period before entering sleep mode. In this example, the external MCU will bring the LAN8670/2 out of sleep using WAKE\_IN and other devices can then be configured to be awakened via WAKE\_OUT (LAN8672 only) or activity on the MDI.

Figure 2-3. System with Sleep Mode Using LAN8670/2

## 3. Pin Description and Configuration

The pin assignments and descriptions for the LAN8670/2 are detailed in the following sections. Pin buffer type definitions are detailed in the Buffer Types section.

#### **Related Links**

1.2. Buffer Types

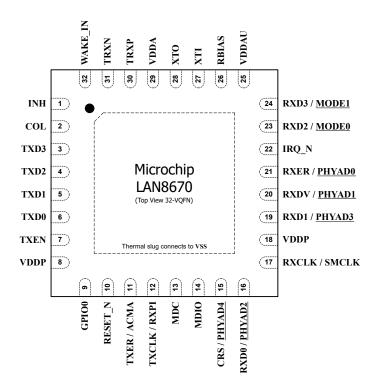

### 3.1 LAN8670 Pin Assignments

Figure 3-1. LAN8670 32-VQFN Pin Assignments

**Note:** Configuration straps are identified by an underlined signal name. Signals that function as configuration straps must be augmented with an external resistor.

Important: The exposed pad (VSS) on bottom of package must be connected to ground.

| n Num | Pin Name           | Pin Num | Pin Name            |

|-------|--------------------|---------|---------------------|

| 1     | INH                | 17      | RXCLK/SMCLK         |

| 2     | COL                | 18      | VDDP                |

| 3     | TXD3               | 19      | RXD1/ <u>PHYAD3</u> |

| 4     | TXD2               | 20      | RXDV/ <u>PHYAD1</u> |

| 5     | TXD1               | 21      | RXER/ <u>PHYAD0</u> |

| 6     | TXD0               | 22      | IRQ_N               |

| 7     | TXEN               | 23      | RXD2/ <u>MODE0</u>  |

| 8     | VDDP               | 24      | RXD3/ <u>MODE1</u>  |

| 9     | GPIO0              | 25      | VDDAU               |

| 10    | RESET_N            | 26      | RBIAS               |

| 11    | TXER/ACMA          | 27      | XTI                 |

| 12    | TXCLK/RXPI         | 28      | ХТО                 |

| 13    | MDC                | 29      | VDDA                |

| 14    | MDIO               | 30      | TRXP                |

| 15    | CRS/ <u>PHYAD4</u> | 31      | TRXN                |

| 16    | RXD0/PHYAD2        | 32      | WAKE_IN             |

#### Table 3-1. LAN8670 32-VQFN Pin Assignments

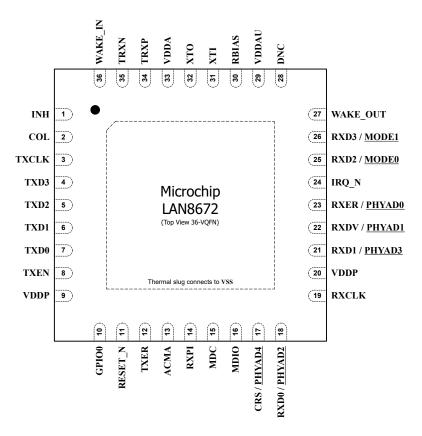

### 3.2 LAN8672 Pin Assignments

Figure 3-2. LAN8672 36-VQFN Pin Assignments

**Note:** Configuration straps are identified by an underlined signal name. Signals that function as configuration straps must be augmented with an external resistor.

**Important:** The exposed pad (VSS) on bottom of package must be connected to ground.

| n Num | Pin Name           | Pin Num | Pin Name            |

|-------|--------------------|---------|---------------------|

| 1     | INH                | 19      | RXCLK               |

| 2     | COL                | 20      | VDDP                |

| 3     | TXCLK              | 21      | RXD1/PHYAD3         |

| 4     | TXD3               | 22      | RXDV/ <u>PHYAD1</u> |

| 5     | TXD2               | 23      | RXER/PHYAD0         |

| 6     | TXD1               | 24      | IRQ_N               |

| 7     | TXD0               | 25      | RXD2/ <u>MODE0</u>  |

| 8     | TXEN               | 26      | RXD3/ <u>MODE1</u>  |

| 9     | VDDP               | 27      | WAKE_OUT            |

| 10    | GPIO0              | 28      | DNC                 |

| 11    | RESET_N            | 29      | VDDAU               |

| 12    | TXER               | 30      | RBIAS               |

| 13    | ACMA               | 31      | XTI                 |

| 14    | RXPI               | 32      | ХТО                 |

| 15    | MDC                | 33      | VDDA                |

| 16    | MDIO               | 34      | TRXP                |

| 17    | CRS/ <u>PHYAD4</u> | 35      | TRXN                |

| 18    | RXD0/PHYAD2        | 36      | WAKE_IN             |

#### Table 3-2. LAN8672 36-VQFN Pin Assignments

## 3.3 Pin Descriptions

This section contains descriptions of the various LAN8670/2 pins. The "\_N" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. For example, RESET\_N indicates that the reset signal is active low. When "\_N" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

Pin buffer type definitions are detailed in the Buffer Types section.

| Name                                | Symbol | Buffer Type    | Description                                                                                                                                                                                        |

|-------------------------------------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Data 0                     | TXD0   | VIS-VDDP<br>PD | Transmit data bus bit 0.                                                                                                                                                                           |

| Transmit Data 1                     | TXD1   | VIS-VDDP<br>PD | Transmit data bus bit 1.                                                                                                                                                                           |

| Transmit Data 2                     | TXD2   | VIS-VDDP<br>PD | Transmit data bus bit 2.                                                                                                                                                                           |

| Transmit Data 3                     | TXD3   | VIS-VDDP<br>PD | Transmit data bus bit 3.                                                                                                                                                                           |

| Transmit Error<br>(MII mode)        | TXER   | VIS-VDDP<br>PD | This input is asserted to indicate that an error was detected somewhere in the packet presently being transferred to the device.                                                                   |

|                                     |        |                | This pin is shared with the ACMA functionality on the LAN8670.                                                                                                                                     |

| Transmit Enable                     | TXEN   | VIS-VDDP<br>PD | Indicates that valid transmission data is present on TXD[3:0].                                                                                                                                     |

|                                     |        |                | <b>Note:</b> A pull-down resistor is recommended to prevent incidental transmission if the MAC does not actively pull-down or drive this pin low at all times during its reset and initialization. |

| Transmit Clock<br>(MII mode)        | TXCLK  | VO-VDDP        | <ul><li>2.5 MHz clock used to latch data from the MAC into the device.</li><li>This pin is shared with the RXPI functionality on the LAN8670.</li></ul>                                            |

| Receive Data 0                      | RXD0   | VOH-VDDP       | Receive data bus bit 0.                                                                                                                                                                            |

| Receive Data 1                      | RXD1   | VOH-VDDP       | Receive data bus bit 1.                                                                                                                                                                            |

| Receive Data 2                      | RXD2   | VO-VDDP        | Receive data bus bit 2                                                                                                                                                                             |

| Receive Data 3                      | RXD3   | VO-VDDP        | Receive data bus bit 3.                                                                                                                                                                            |

| Receive Error                       | RXER   | VOH-VDDP       | This output is asserted to indicate that an error was<br>detected somewhere in the packet presently being<br>transferred from the device.                                                          |

| Receive Data Valid                  | RXDV   | VOH-VDDP       | Indicates that recovered and decoded data is available<br>on the RXD[3:0] pins.                                                                                                                    |

| Receive Clock<br>(Mll mode)         | RXCLK  | VO-VDDP        | In MII mode, this pin is the 2.5 MHz receive clock output.                                                                                                                                         |

| Single Media Clock<br>(SC-MII mode) | SMCLK  | VO-VDDP        | In Single Clock MII mode, this pin is the 2.5 MHz clock output to be connected to the media access controller MII TXCLK and RXCLK input pins.                                                      |

Table 3-3. MII/SC-MII Signals

| continued        |        |             |                   |

|------------------|--------|-------------|-------------------|

| Name             | Symbol | Buffer Type | Description       |

| Collision Detect | COL    | VO-VDDP     | Collision Detect. |

| Carrier Sense    | CRS    | VO-VDDP     | Carrier Sense.    |

#### Table 3-4. Ethernet Transceiver Pins

| Name                                | Symbol | Buffer Type | Description                                    |  |

|-------------------------------------|--------|-------------|------------------------------------------------|--|

| Ethernet TX/RX Positive<br>Terminal | TRXP   | AIO         | Positive terminal for transmit/receive signal. |  |

| Ethernet TX/RX Negative<br>Terminal | TRXN   | AIO         | Negative terminal for transmit/receive signal. |  |

#### Table 3-5. Serial Management Interface (SMI) Pins

| Name                  | Symbol | Buffer Type           | Description                                    |

|-----------------------|--------|-----------------------|------------------------------------------------|

| SMI Data Input/Output | MDIO   | VIS-VDDP /<br>VO-VDDP | Serial Management Interface data input/output. |

| SMI Clock             | MDC    | VIS-VDDP              | Serial Management Interface clock.             |

#### Table 3-6. Power Management Pins

| Name        | Symbol   | Buffer Type | Description                                                                                                                                                                                                                                              |

|-------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inhibit     | INH      | VODH-VDDAU  | Inhibit. Used to switch on/off the main external voltage regulators.                                                                                                                                                                                     |

|             |          |             | This pin operates in the VDDAU domain.                                                                                                                                                                                                                   |

|             |          |             | RESET_N assertion does not affect the state of this pin.                                                                                                                                                                                                 |

|             |          |             | This signal is an active high P-channel open-drain<br>source output. The pin will be driven to VDDAU to<br>inhibit the shutdown of external voltage regulators.<br>When the external regulators may be shutdown, this<br>pin will become high impedance. |

|             |          |             | <b>Note:</b> When used, this pin requires a pull-down resistor.                                                                                                                                                                                          |

|             |          |             | When not used, this pin should be left unconnected.                                                                                                                                                                                                      |

| Wake Input  | WAKE_IN  | VI-VDDAU    | Wakeup Input. Asserted to move the part out of sleep.                                                                                                                                                                                                    |

|             |          |             | <b>Note:</b> When used, this pin requires a pull-up or pull-<br>down resistor, depending on the software configured<br>assertion polarity.                                                                                                               |

|             |          |             | <b>Note:</b> This pin operates in the VDDAU domain.                                                                                                                                                                                                      |

|             |          |             | When not used, this pin should be connected to VSS.                                                                                                                                                                                                      |

| Wake Output | WAKE_OUT | VO-VDDP     | Wake Output. Asserted when the part wakes out of sleep.                                                                                                                                                                                                  |

|             |          |             | <b>Note:</b> When used, this pin requires a pull-down resistor.                                                                                                                                                                                          |

|             |          |             | <b>Note:</b> This pin operates in the VDDP domain.                                                                                                                                                                                                       |

|             |          |             | When not used, this pin should be left unconnected.                                                                                                                                                                                                      |

#### Table 3-7. Application Pins

| Name                                    | Symbol | Buffer Type           | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----------------------------------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Application Controlled<br>Medium Access | ACMA   | VIS-VDDP              | Application Controlled Medium Access. When this feature is enabled, the host processor may assert this input to allow the PHY to transmit to the medium. When unused, this pin is an input and should be connected to VSS.                                                                                                                                                                                           |  |

| Receive Packet Indication               | RXPI   | VO-VDDP               | Receive Packet Indication. This pin is asserted by the<br>Time Synchronization block to indicate the reception<br>a packet. This pin may also be asserted when the P<br>receives a packet that matches a configured patter<br>The packet matching feature is typically used to trig<br>on reception of IEEE Std 802.1AS gPTP packets.<br>When unused, this pin is actively driven low and ma<br>be left unconnected. |  |

| Transmit Packet Indication              | ТХРІ   | VO-VDDP               | Transmit Packet Indication. This pin is asserted<br>by the Time Synchronization block to indicate the<br>transmission of a packet. This pin may also be asserted<br>when the PHY transmits a packet that matches a<br>configured pattern. The packet matching feature is<br>typically used to trigger on transmission of IEEE Std<br>802.1AS gPTP packets.                                                           |  |

| General Purpose Application<br>I/O      | GPIO0  | VIS-VDDP /<br>VO-VDDP | General Purpose Application I/O 0. This pin may be<br>configured as ACMA, TXPI, RXPI, or RXTXPI.<br>The host processor cannot directly drive or read this<br>pin through CSR writes or reads.<br>When unused, this pin is actively driven low and may<br>be left unconnected.                                                                                                                                        |  |

#### Table 3-8. Miscellaneous Pins

| Name                              | Symbol  | Buffer Type    | Description                                                                                                                                                                                                                     |

|-----------------------------------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External 25 MHz Crystal Input     | XTI     | ICLK           | External 25 MHz crystal input.                                                                                                                                                                                                  |

| External 25 MHz Crystal<br>Output | ХТО     | OCLK           | External 25 MHz crystal output.                                                                                                                                                                                                 |

| Interrupt                         | IRQ_N   | VODL-VDDP      | Device interrupt. Active low N-channel open-drain sink output.<br>Note: This pin requires a 10 k $\Omega$ (typical) pull-up to VDDP.                                                                                            |

| System Reset                      | RESET_N | VIS-VDDP<br>PU | System reset. This pin is active low.<br>If unused, this pin may be connected directly to VDDP.                                                                                                                                 |

| Bias Resistor                     | RBIAS   | AIO            | External bias resistor connection pin. This pin requires connection of a 12.4 k $\Omega$ resistor to ground.<br><b>Note:</b> The resistor must be within ± 1% tolerance across the entire expected operating temperature range. |

| Do Not Connect                    | DNC     | -              | The pin must be left floating externally unless otherwise directed by Microchip.                                                                                                                                                |

#### Table 3-9. Configuration Straps

| Name                                       | Symbol            | Buffer Type | Description                                                                                                                                           |

|--------------------------------------------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode<br>Configuration Straps 1-0 | <u>MODE[1:0]</u>  | VIS-VDDP    | These configuration straps are used to select<br>the device's default mode of operation. See<br>3.4. Configuration Straps for additional information. |

| PHY Address Configuration<br>Straps 4-0    | <u>PHYAD[4:0]</u> | VIS-VDDP    | These configuration straps are used to select<br>the device's default PHY SMI address. See<br>3.4. Configuration Straps for additional information.   |

#### Table 3-10. Power Pins

| Name                                          | Symbol | Description                                                                                                                                                                                                       |

|-----------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +3.3V Switchable I/O Power Supply<br>Input    | VDDP   | +3.3V I/O power supply input. When in sleep mode, this supply must be disabled.                                                                                                                                   |

| +3.3V Continuous VDDAU Power<br>Supply Input  | VDDAU  | +3.3V continuous VDDAU power supply input.<br><b>Note:</b> This supply must be provided during sleep mode.<br><b>Note:</b> When wake/sleep support is not used, this pin is connected to the same supply as VDDA. |

| +3.3V Switchable Analog Power<br>Supply Input | VDDA   | +3.3V analog power supply input. When in sleep mode, this supply must be disabled.                                                                                                                                |

| Ground                                        | VSS    | Common ground.<br><b>Note:</b> This exposed pad must be connected to the ground plane with a via array.                                                                                                           |

## 3.4 Configuration Straps

Configuration straps allow various features of the device to be automatically configured to user defined values. They are identified by an underlined signal name in the pin assignment lists. Configuration straps do not have internal resistors to prevent the signal from floating when unconnected.

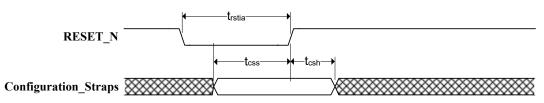

**Important:** External pull-up or pull-down resistors must be sized appropriately (10 k $\Omega$ , typical) to ensure that the configuration straps reach the required voltage level prior to latching at reset.

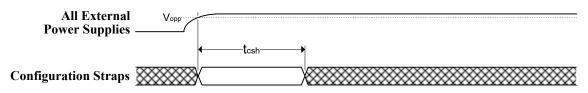

Configuration straps are latched on Power-On Reset (POR) and pin reset (RESET\_N). At the completion of the reset, that is when all power supplies are above the thresholds and the RESET\_N pin is no longer asserted, the associated register bit values are loaded.

**Note:** When a soft reset occurs via the Soft Reset bit of the Basic Control Register, the configuration of the device is determined by the contents stored in registers and is independent of the values of the configuration strap pins.

#### **Related Links**

5.1.7. STRAP\_CTRL0

### 3.4.1 Device Mode (MODE[1:0])

The <u>MODE[1:0]</u> configuration straps determine whether the interface to the MAC is MII or SC-MII, as shown in Table 3-11 below. The value can be read in the STRAP\_CTRL0 register, if needed.

**Note:** As the LAN8672 only supports operation in MII mode, the <u>MODE[1:0]</u> configuration straps must be set to 01b.

#### Table 3-11. MODE[1:0] Configuration Straps

| MODE[1:0] | Definition                                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00b       | Reserved                                                                                                                                                                 |

| 01b       | PHY is placed in MII mode                                                                                                                                                |

| 10b       | Reserved                                                                                                                                                                 |

| 11b       | PHY is placed in Single Clock MII (SC-MII) mode. (LAN8670 only)<br>The TXCLK and TXER pins are used for other features. The RXCLK pin becomes a single MII clock output. |

#### 3.4.2 PHY Address (PHYAD[4:0])

During reset, the <u>PHYAD[4:0]</u> configuration straps are pulled high or low through external resistors to give each PHY a unique SMI address. This address is latched into an internal register at the end of a hardware reset. In a multi-PHY application (such as a switch), the controller is able to manage each PHY via the unique address. Each PHY checks each management data frame for a matching address in the relevant bits. When a match is recognized, the PHY responds to that particular frame.

The LAN8670/2 SMI address must be configured using the <u>PHYAD[4:0]</u> hardware configuration straps to any value between 0x00 and 0x1F.

## 3.5 Pin Configuration

Some pins of the LAN8670/2 may take on multiple functions depending on the device and mode. The functionality of five pins of the LAN8670 varies depending upon the device mode set by the MODE[1:0] Configuration Straps. Table 3-12 shows the functionality assigned to these pins based on the configured device mode.

|                         | MII                | SC-MII  |

|-------------------------|--------------------|---------|

| Pin 11                  | TXER <sup>1</sup>  | ACMA    |

| (TXER/ACMA)             |                    |         |

| Pin 12<br>(TXCLK/RXPI)  | TXCLK <sup>2</sup> | RXPI    |

| Pin 17<br>(RXCLK/SMCLK) | RXCLK              | SMCLK   |

| Notes:                  | he used f          | or ACMA |

#### Table 3-12. LAN8670 Device Mode Pin Configuration

1. GPIO0 may be used for ACMA

2. GPIO0 may be used for RXPI

The GPIO0 pin is a multipurpose pin that can be configured as desired for multiple uses. This feature is useful for enabling specific features that would not otherwise be available for a specific device package or configuration. For example, Time Sensitive Networking (TSN) is supported through the ability to assert output signals when packets matching a specific pattern are transmitted and/or received. The GPIO0 pin may be configured as a Transmit Packet Indication (TXPI), Receive Packet Indication (RXPI), or Receive/Transmit Packet Indication (RXTXPI) output, as needed. Additionally, GPIO0 may be configured as an Application Controlled Media Access (ACMA) input pin.

The GPIO0 pin functionality is configured by writing to the GPIO0 Signal Select (GPIO0SS) field of the Pin Control (PINCTRL) register. The GPIO0 Signal Select should be configured prior to configuring and enabling the underlying Packet Pattern Matching or Application Controlled Media Access blocks.

Valid configurations for the GPIO0 pin depend on the device in use and its operating mode. When a dedicated pin is available, it must be used rather than the GPIO0 pin. Table 3-13 below shows the valid configurations for the GPIO0 pin. When a pin number is shown, this is an invalid configuration for the GPIO0 Signal Select and the designated dedicated pin must be used instead.

|         |        | LAN      | 8670     | LAN8672              |

|---------|--------|----------|----------|----------------------|

| GPIO0SS | Signal | MII      | SC-MII   | MII                  |

| 00      | RXPI   | <b>v</b> | Pin 12   | Pin 14               |

| 01      | TXPI   | <b>v</b> | <b>v</b> | <ul> <li></li> </ul> |

| 10      | RXTXPI | <b>v</b> | <b>v</b> | <b>v</b>             |

| 11      | ACMA   | <b>v</b> | Pin 11   | Pin 13               |

#### Table 3-13. GPIO0 Signals

## 4. Functional Descriptions

## 4.1 Media Independent Interface (MII)

The integrated Media Independent Interface (MII) provides a common interface between physical layer and MAC layer devices, adhering to IEEE Std 802.3-2018 *IEEE Standard for Ethernet*.

The MII includes the following interface signals:

- Transmit Data TXD[3:0]

- Transmit Enable TXEN

- Transmit Clock TXCLK

- Transmit Error TXER

- Receive Data RXD[3:0]

- Receive Data Valid RXDV

- Receive Clock RXCLK

- Receive Error RXER

- Carrier Sense CRS

- Collision Detect COL

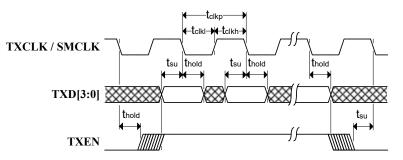

In MII mode, on the transmit path, the LAN8670/2 drives the transmit clock, TXCLK, to the controller. The controller synchronizes the transmit data to the rising edge of TXCLK and drives TXEN high to indicate valid transmit data on TXD[3:0]. The device will synchronously capture TXEN, TXER, and TXD[3:0] on the falling edge of TXCLK.

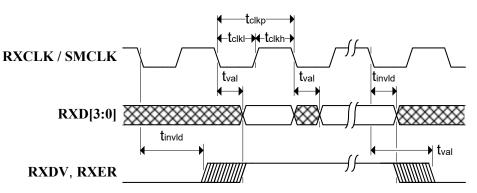

On the receive path, the device drives both the receive data, RXD[3:0], and the receive clock, RXCLK. The controller captures in the receive data on the rising edge of RXCLK when the device drives RXDV high. The device drives RXER high when a receive error is detected (e.g., an uncorrectable decoding error). The device synchronizes RXD[3:0], RXDV, and RXER to change on the falling edge of RXCLK.

The CRS and COL signals are asserted asynchronously to the clocks.

For timing information, refer to the MII Timing section. Refer to Clause 22 of the IEEE Std 802.3-2018 IEEE Standard for Ethernet specification for additional MII information.

**Note:** Many modern controllers, often found on switches, implement a reduced pin MII assuming full-duplex point-to-point operation. These interfaces, known as MII-Lite, do not include the required CRS and COL signals for 10BASE-T1S half-duplex operation. Back-to-back connection of two half-duplex devices is also not supported due to the CRS and COL requirement.

**Note:** The connection of a 10 k $\Omega$  pull-down resistor on TXEN is recommended to prevent incidental transmission if the MAC does not actively pull-down or drive this pin low at all times during its reset and initialization.

#### **Related Links**

7.6.6. MII/SC-MII Timing

#### 4.1.1 Single Clock Media Independent Interface (SC-MII)

The Single Clock Media Independent Interface (SC-MII) provides a common interface between physical layer and MAC layer devices similar to the MII but with fewer pins while maintaining compatibility with the MII. The Single Clock MII combines the Transmit Clock (TXCLK) and Receive Clock (RXCLK) into a Single Media Clock (SMCLK) and does not include the Transmit Error (TXER) pin. The result is a reduction of two pins over the standard MII which may be used for additional features.

The Single Clock MII includes the following interface signals:

- Transmit Data TXD[3:0]

- Transmit Enable TXEN

- Receive Data RXD[3:0]

- Receive Data Valid RXDV

- Receive Error RXER

- Single Media Clock SMCLK

- Carrier Sense CRS

- Collision Detect COL

In Single Clock MII mode, the LAN8670/2 drives the Single Media Clock (SMCLK) to both the controller TXCLK and RXCLK input pins. On the transmit path, the controller synchronizes the transmit data to the rising edge of the SMCLK as received at its TXCLK input. The controller drives TXEN high to indicate valid transmit data on TXD[3:0]. The device will synchronously capture TXEN and TXD[3:0] on the falling edge of TXCLK. Support for TXER is not provided in Single Clock MII mode.

On the Single Clock MII receive path, the device drives receive data, RXD[3:0], synchronously to the Single Media Clock (SMCLK). When the device drives RXDV high, the controller captures in the receive data on the rising edge of SMCLK as received at its RXCLK input. The device drives RXER high when a receive error is detected (e.g., an uncorrectable decoding error). The device synchronizes RXD[3:0], RXDV, and RXER to change on the falling edge of SMCLK.

The CRS and COL signals are asserted asynchronously to the clocks.

**Note:** The Transmit Error (TXER) pin is not available in this mode.

#### **Related Links**

7.6.6. MII/SC-MII Timing

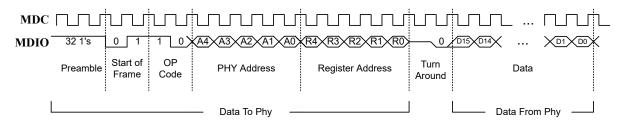

### 4.2 Serial Management Interface (SMI)

The Serial Management Interface (SMI) is used to control the device and obtain its status. This interface supports the standard PHY registers required by Clause 22 of IEEE Std 802.3, as well as "vendor-specific" registers allowed by the specification. Unimplemented registers will be read as hexadecimal "0000". Device registers are detailed in the Register Descriptions section.

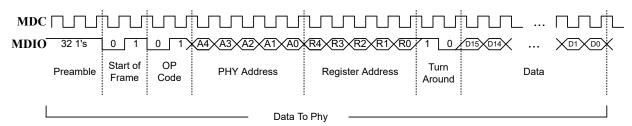

At the system level, SMI provides two signals: MDIO and MDC. The MDC signal is an aperiodic clock provided by the station management entity (STA). MDIO is a bi-directional data SMI input/output signal that receives serial data (commands) from the STA and sends serial data (status) to the STA. The minimum time between edges of the MDC is 100 ns. There is no maximum time between edges. The minimum cycle time (i.e., the time between two consecutive rising or two consecutive falling edges) is 250 ns. These modest timing requirements allow this interface to be easily driven by the I/O port of a microcontroller.

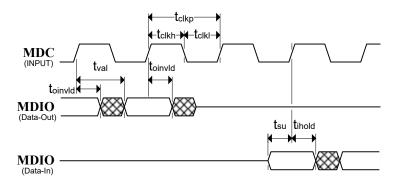

The data on the MDIO line is latched on the rising edge of the MDC. The management frame structure and timing is shown in the following figures. The timing relationships of the MDIO signals are further described in the SMI Timing section of the Operational Characteristics AC Specifications.

Figure 4-1. SMI Timing and Frame Structure - READ Cycle

Figure 4-2. SMI Timing and Frame Structure - WRITE Cycle

#### **Related Links**

5. Register Descriptions 7.6.7. SMI Timing

#### 4.2.1 Clause 45 Register Access

The LAN8670/2 only supports the MDIO management frame protocol defined in IEEE Std 802.3 Clause 22. Registers mapped into IEEE Std 802.3 Clause 45 MDIO Managed Devices (MMD) are accessed indirectly through the MMD Access Control (MMDCTRL) and MMD Access Address/Data (MMDAD) registers as described in IEEE Std 802.3 Annex 22D.

#### **MMD** Register Read

The following process is used to indirectly read Clause 45 registers using the Clause 22 access mechanism.

- 1. Write the MMD Access Control register with the MMD Function (FNCTN) field set to 00b and the Device Address (DEVID) field with the MDIO Management Device (MMD) address.

- 2. Write the address of the desired register to be read into the MMD Access Address/Data register.

- 3. Write the MMD Access Control register with the MMD Function field set to 01b, 10b, or 11b.

- 4. Read the contents of the MMD's selected register from the MMD Access Address/Data register.

Subsequent reads from the MMD Access Address/Data register will continue to reread and return the value of the selected MMD register when the MMD Function field is set to 11b or 11b. When the MMD Function field is set to 10b, the MMD register address will be incremented following every read causing subsequent reads from the MMD Access Address/Data register to return data from the next higher MMD register.

#### **MMD Register Write**

The following process is used to indirectly write Clause 45 registers using the Clause 22 access mechanism.

- 1. Write the MMD Access Control register with the MMD Function (FNCTN) field set to 00b and the Device Address (DEVID) field with the MDIO Management Device (MMD) address.

- 2. Write the address of the desired register to be written into the MMD Access Address/Data register.

- 3. Write the MMD Access Control register with the MMD Function field set to 01b, 10b, or 11b.

Subsequent writes to the MMD Access Address/Data register will continue to write to the selected MMD register when the MMD Function field is set to 01b. When the MMD Function field is set to 10b or 11b, the MMD register address will be incremented following every write causing subsequent writes to the MMD Access Address/Data register to write data to the next higher MMD register.

#### **Related Links**

5.1.5. MMDCTRL 5.1.6. MMDAD

### 4.3 Interrupt Management

The LAN8670/2 supports multiple interrupt capabilities which are not part of the IEEE 802.3 specification. An active low asynchronous interrupt signal may be generated on the IRQ\_N pin when selected status events are detected as configured by the Interrupt Mask Registers.

To assert an interrupt on IRQ\_N for a given event in the Status 1 (STS1) and Status 2 (STS2) registers, the corresponding mask bit in the Interrupt Mask 1 (IMASK1) and Interrupt Mask 2 (IMSK2) registers must be written to '0' to enable the interrupt. When the associated event occurs setting the status bit, the IRQ\_N pin will also be asserted. When the event to negate the status bit is true, or the corresponding bit in the Interrupt Mask Register is set disabling the interrupt, the IRQ\_N pin will be deasserted.

All PHY interrupts are disabled (masked) following a reset with the exception of the Reset Complete interrupt mask bit. The Reset Complete interrupt mask is '0' by default such that the IRQ\_N pin will be asserted following a reset event setting the Reset Complete status bit. This may be used to alert the station management entity that the LAN8670/2 has been reset and is available for configuration.

#### **Related Links**

- 5.4.4. STS1

- 5.4.5. STS2

- 5.4.7. IMSK1

- 5.4.8. IMSK2

### 4.4 Resets

The device provides the chip-level reset sources described in the following sections.

#### 4.4.1 Power-On Reset (POR)

A Power-On Reset occurs whenever power is initially applied to the device, or if power is removed and reapplied to the device. A timer within the device will assert the internal reset for approximately 2 ms. Configuration straps are loaded by this reset and must adhere to the timing requirements specified in Power-On Configuration Strap Timing when not using the external pin reset (RESET\_N).

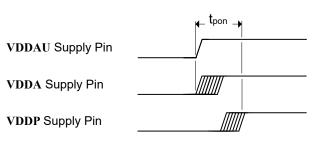

After power-on, the POR initially negates after the rising threshold is passed. In the event that the supply drops below the falling threshold, the POR asserts. The POR stays asserted until the rising threshold is once again crossed. The rising and falling thresholds are listed in Table 4-1.

| POR               | Rising Threshold <sup>1</sup> | Falling Threshold <sup>1</sup> |

|-------------------|-------------------------------|--------------------------------|

| VDDA              | 2.5V                          | 2.4V                           |

| VDDAU             | 2.5V                          | 2.4V                           |

| 1.8V <sup>2</sup> | 1.6V                          | 1.3V                           |

Table 4-1. POR Supply Thresholds

1. Rising and falling threshold voltages are design parameters and are neither tested nor characterized.

2. The internal 1.8V supply cannot be monitored externally.

#### **Related Links**

7.6.3. Power-On Configuration Strap Timing

#### 4.4.2 External Pin Reset (RESET\_N)

A hardware reset will occur when the RESET\_N pin is asserted. The RESET\_N pin must be connected externally to VDDP if unused. If used, the RESET\_N pin must be driven for a minimum period as defined in the RESET\_N Configuration Strap Timing section. Configuration straps are loaded by the reset.

#### **Related Links**

7.6.4. RESET\_N Configuration Strap Timing

#### 4.4.3 Software Reset

The software reset is available via the PHY Soft Reset (SW\_RESET) bit in the Basic Control register.

Configuration straps are not loaded by a software reset.

#### **Related Links**

5.1.1. BASIC\_CONTROL

### 4.5 Initialization

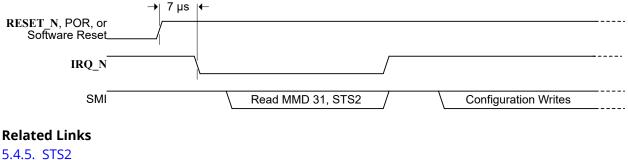

When the device is in a reset state, the IRQ\_N interrupt pin is high-impedance and will be pulled high through an external pull-up resistor. Once all device reset sources are deasserted, the device will begin its internal initialization. The device will assert the Reset Complete (RESETC) bit in the Status 2 (STS2) register to indicate that it has completed its internal initialization and is ready for configuration. As the Reset Complete status is non-maskable, the IRQ\_N pin will always be asserted and driven low following a device reset. The time required for the device to initialize once all reset sources are deasserted until the IRQ\_N pin is asserted is approximately 7 µs.

At the system level, the station management entity should respond to all assertions of the IRQ\_N pin with a read of critical status registers through the Serial Management Interface (SMI), including the Status 2 register. Upon reading of the Status 2 register, the pending Reset Complete status bit will be automatically cleared causing the IRQ\_N pin to be released and pulled high again. The station management entity may then continue to configure the device registers through the Serial Management Interface. See Figure 4-3 for an illustration of the device reset, initialization, and configuration process.

Figure 4-3. Initialization and Configuration Sequence

4.4. Resets

## 4.6 Clock Manager

The Clock Manager generates the internal clocks from an external reference source.

### 4.6.1 Crystal Pins (XTI/XTO)

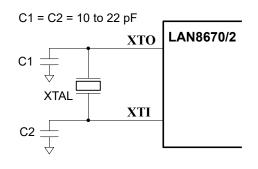

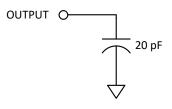

The XTI and XTO crystal oscillator pins are used to connect a 25.0 MHz crystal clock source for MII operation. The crystal oscillator should be in a fundamental, parallel resonant mode. Figure 4-4 depicts the external circuitry connected to the LAN8670/2 oscillator circuit. Since the internal inverter/amplifier is operated in its linear region, external series resistors should not be used as they will lower the gain and could cause start-up problems. Several factors must be considered when selecting a crystal including load capacitance, oscillator margin, cut, and operating temperature.

Figure 4-4. Crystal Oscillator Input

### **Related Links**

6.5. Crystal Oscillator Selection7.7. Crystal Specifications

## 4.7 Physical Layer Collision Avoidance (PLCA)

PLCA operates in conjunction with a CSMA/CD MAC to actively avoid collisions among half-duplex stations (known as PLCA nodes) allowing for greater network utilization. Each node on the network segment (i.e., collision domain) is assigned a unique Local ID. Transmit opportunities are then granted to each node in sequence based on their Local ID. The node configured as Local ID = 0is known as the *PLCA coordinator*. The role of the PLCA coordinator is to transmit a periodic synchronizing BEACON onto the physical media. All other nodes are referred to as a PLCA follower as they follow the synchronization of the coordinator. Once the BEACON has been received on the segment, all nodes begin counting transmit opportunities beginning with zero. Nodes detect their assigned transmit opportunity by counting the number of opportunities that have passed since the transmission of the BEACON by the PLCA coordinator. Each node may transmit when the number of transmit opportunities counted since the BEACON matches the Local ID assigned to the node. Within each transmit opportunity, the node assigned the current opportunity may either transmit a packet or yield. Once the node has transmitted a packet (or yielded), each node increments the transmit opportunity counter and the transmit opportunity goes to the next node. The first transmit opportunity of zero allows node with Local ID = 0 to transmit. Once a fixed number of transmit opportunities has been provided, the PLCA coordinator will transmit another BEACON starting the cycle over again. A BEACON followed by a fixed number of transmit opportunities is known as a PLCA bus cycle.

On multidrop topologies with multiple nodes connected to a shared media mixing segment, PLCA enables a fairness in opportunity to transmit such that one node cannot transmit more than one frame without each of the other nodes also being granted an opportunity to transmit. There are 2 exceptions that can be useful on multidrop segments where one or more nodes transmit more often than other nodes. PLCA allows individual nodes to be configured to transmit a burst of frames within a single transmit opportunity. The LAN8670/2 can also assign individual nodes multiple transmit opportunities within the bus cycle.

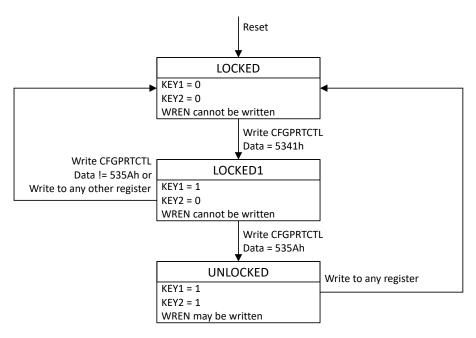

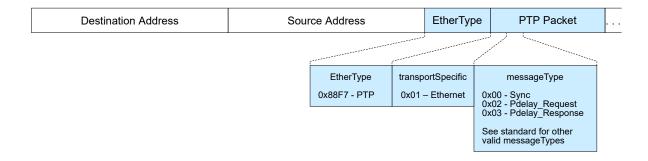

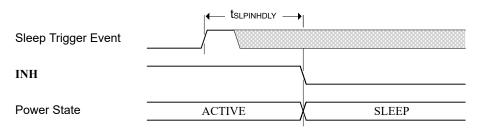

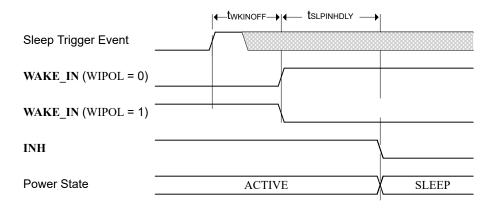

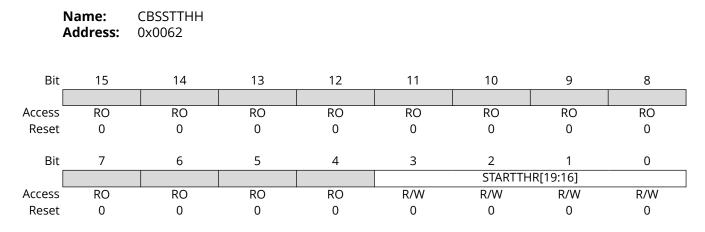

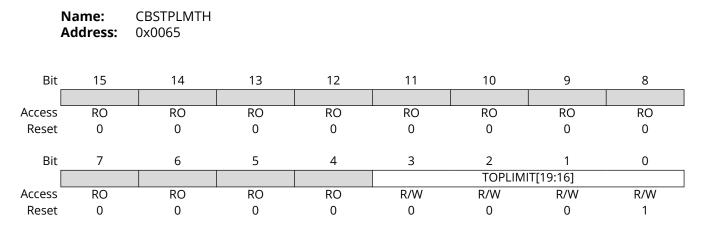

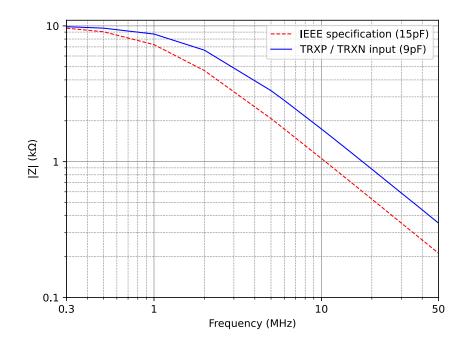

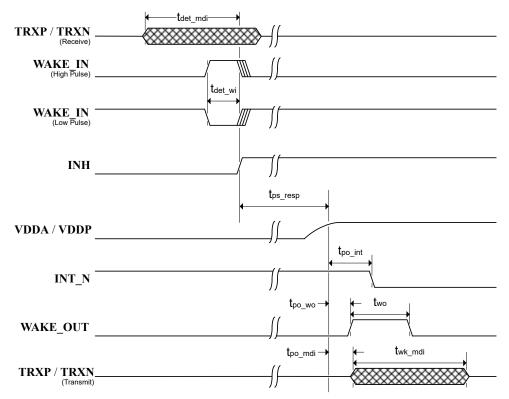

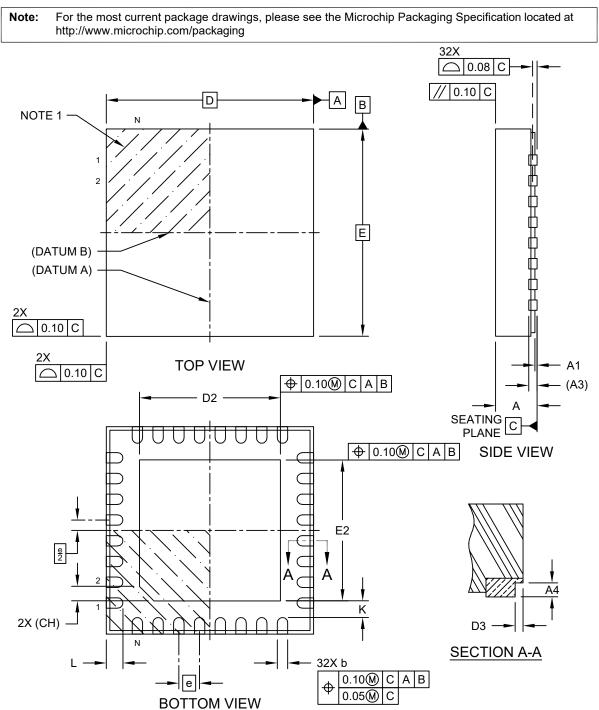

PLCA is enabled by setting the PLCA Enable bit in the PLCA Control 0 (PLCA\_CTRL0) register. The node Local ID is configured within the PLCA Local ID (ID) field of the PLCA Control 1 (PLCA\_CTRL1) register and must be unique within the PLCA network segment to successfully avoid collisions. Additionally, the Local ID must be less than the number of transmit opportunities in each bus cycle in order to be granted a transmit opportunity (see the Node Count field of the PLCA Control 1 register). When the node is configured as the PLCA coordinator, then the number of transmit opportunities within each PLCA bus cycle (period between successive BEACON transmissions) is configured in the Node Count (NCNT) field of the PLCA Control 1 register.