## **General description**

AIROC™ CYW20829 is a high-performance, ultra-low-power and "Secure" MCU + Bluetooth® LE platform, purpose-built for IoT applications. It combines a high-performance microcontroller with Bluetooth® LE (5.4) connectivity, high-performance analog-to-digital conversion audio input, I²S/PCM, CAN, LIN for automotive use cases and other standard communication and timing peripherals. CYW20829 employs high level of integration to minimize external components, reducing the device footprint and costs associated with implementing Bluetooth® Low Energy solutions. AIROC™ CYW20829 is the optimal solution for wireless input devices, remotes, keyboards, joysticks, Bluetooth® Mesh, automotive, asset tracking, and Bluetooth® LE IoT applications that need 10 dBm RF output power such as lighting and home automation.

#### **Features**

### · 32-bit application core subsystem

- 96-MHz Arm® Cortex®-M33 CPU with single-cycle multiply and memory protection unit (MPU)

- ARMv8-M architecture

- CMOS 40-nm process

- User-selectable core logic operation at either 1.1 V or 1.0 V

- Active CPU current slope with 1.1 V core operation

- Cortex®-M33: 40 μA/MHz

- Active CPU current slope with 1.0 V core operation

- Cortex®-M33: 22 μA/MHz

- Datawire (DMA) controller with 16 channels

- 32-KB cache for greater XIP performance with lower power

#### Memory subsystem

- 256-KB SRAM with power and data retention control

- OTP eFuse array for security provisioning

### · Bluetooth® Low Energy subsystem

- 2.4-GHz RF transceiver with  $50-\Omega$  antenna drive

- Digital PHY

- Link layer engine supporting master and slave modes

- Programmable TX power: up to 10 dBm

- RX sensitivity:

- LE-1 Mbps: -98 dBm

- LE-2 Mbps: -95 dBm

- Coded PHY 500 kbps (LE-LR): -101 dBm

- Coded PHY 125 kbps (LE-LR): -106 dBm

- 5.2-mA TX (0 dBm), 17.2 mA TX (10 dBm), and 5.6 mA RX (LE 1 Mbps) current with 3.0 V supply and using internal buck converter

- Link layer engine supports up to 16 connections simultaneously, four are peripheral

#### · Low-power 1.7 V to 3.6 V operation

- Six power modes for fine-grained power management

- Deep Sleep mode current of 4.5 μA with 64 KB SRAM retention

- On-chip DC-DC buck converter

infineon

#### **Features**

### · Flexible clocking options

- 8-MHz internal main oscillator (IMO) with ±2% accuracy

- Ultra-low-power 32-kHz internal low-speed oscillator (ILO)

- Two oscillators: High-frequency (24-MHz) for radio PLL and low-frequency (32-kHz watch crystal) for LPO

- 48-MHz low power IHO (internal oscillator)

- Frequency-locked loop (FLL) for multiplying IMO frequency

- Integer and fractional peripheral clock dividers

#### • Quad SPI (QSPI)/serial memory interface (SMIF)

- eXecute-In-Place (XIP) from external quad SPI flash

- On-the-fly encryption and decryption

- Support for DDR

- Supports single, dual, and quad interfaces with throughput up to 384-Mbps

#### Serial Communication

- Three run-time configurable Serial Communication Blocks (SCBs)

- First SCB: Configurable as SPI or I<sup>2</sup>C

- Second SCB: Configurable as SPI or UART

- Third SCB: Configurable as I<sup>2</sup>C or UART

### · Audio subsystem

- Two pulse density modulation (PDM) channels and one I<sup>2</sup>S channel with time division multiplexed (TDM) mode

### · Timing and pulse-width modulation

- Seven 16-bit and two 32-bit Timer/Counter Pulse-Width Modulator (TCPWM) blocks, for MCU. Multiple PWMs needed for color LEDs.

- PWM supports center-aligned, edge, and pseudo-random modes

#### ADC and MIC

- Sigma-delta switched cap ADC for audio and DC measurements

#### Up to 32 programmable GPIOs

- One I/O port (8 I/Os) enables Boolean operations on GPIO pins; available during system Deep Sleep

- Programmable drive modes, strengths, and slew rates

- Two overvoltage-tolerant (OVT) pins

- Up to six, used for SMIF

#### · Security built into platform architecture

- ROM-based root of trust via uninterruptible "Secure Boot"

- Step-wise authentication of execution images

- Secure execution of code in execute-only mode for protected routines

- All debug and test ingress paths can be disabled

- Up to four protection contexts (One available for customer code)

- Secure debug support via authenticated debug token

- Encrypted image support for external SMIF memory

#### · Cryptography hardware

- Hardware Acceleration for symmetric cryptographic methods and hash functions

- True Random Number Generation (TRNG) function

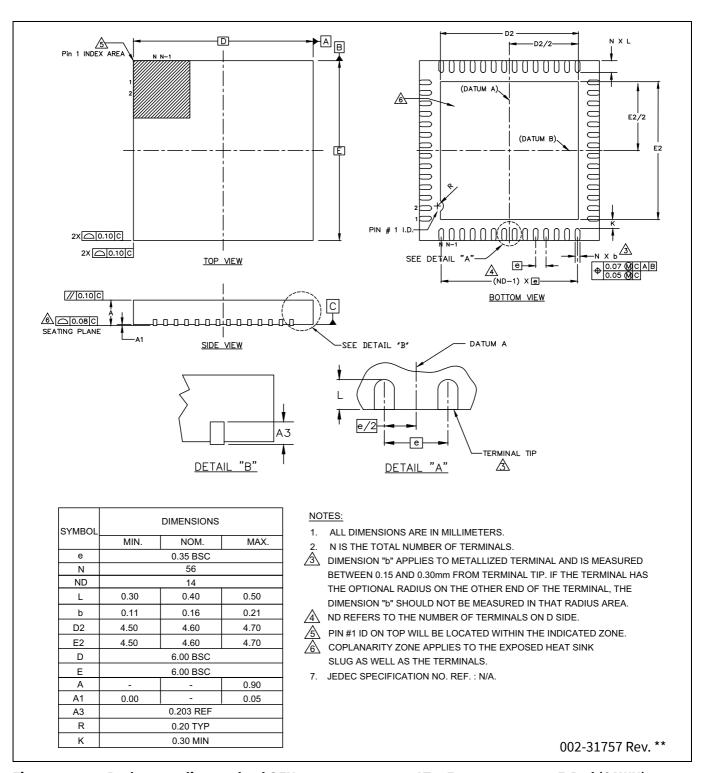

### Packages

- 56-QFN  $6 \text{ mm} \times 6 \text{ mm}$

Eclipse IDE for Modustoolbox™ software

## Eclipse IDE for Modustoolbox™ software

Modustoolbox™ software is Infineon's comprehensive collection of multi-platform tools and software libraries that enable an immersive development experience for creating converged MCU and wireless systems. It is:

- Comprehensive it has the resources you need

- Flexible you can use the resources in your own workflow

- Atomic you can get just the resources you want

Infineon provides a large collection of code repositories on GitHub. This includes:

- Board support packages (BSPs) aligned with Infineon kits

- Low-level resources, including a hardware abstraction layer (HAL) and peripheral driver library (PDL)

- Middleware enabling industry-leading features such as Bluetooth® Low Energy, and mesh networks

- An extensive set of thoroughly tested code example applications

**Note** The HAL provides a high-level, simplified interface to configure and use the hardware blocks on Infineon MCUs and SoCs. It is a generic interface that can be used across multiple product families. You can leverage the HAL's simpler and more generic interface for most of an application, even if one portion requires fine-grained control.

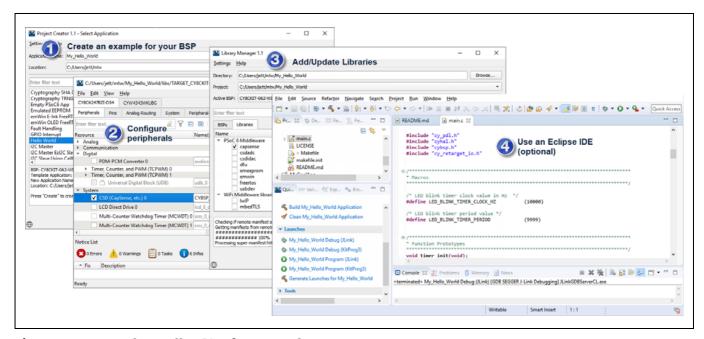

ModusToolbox™ software is IDE-neutral and easily adaptable to your workflow and preferred development environment. It includes a Project Creator, a Library Manager, a BSP Assistant, peripheral and library configurators, as well as the optional Eclipse IDE for the ModusToolbox™, as **Figure 1** shows. For information on using Infineon tools, refer to the documentation delivered with ModusToolbox™ software.

Figure 1 ModusToolbox™ software tools

Table of contents

## **Table of contents**

| General description                                |    |

|----------------------------------------------------|----|

| Features                                           |    |

| Eclipse IDE for Modustoolbox™ software             | 3  |

| Table of contents                                  |    |

| 1 Block diagram                                    | 5  |

| 2 Functional description                           | 6  |

| 2.1 CPU and memory subsystem                       | 6  |

| 3 System resources                                 |    |

| 3.1 Power system                                   | 10 |

| 3.2 Bluetooth® LE radio and subsystem              | 14 |

| 3.3 Programmable analog-to-digital converter (ADC) | 15 |

| 3.4 Programmable digital                           | 15 |

| 3.5 Fixed-function digital                         | 15 |

| 3.6 GPIO                                           |    |

| 3.7 Special-function peripherals                   | 18 |

| 4 Power supply considerations                      | 28 |

| 5 Electrical specifications                        | 29 |

| 5.1 Absolute maximum ratings                       | 29 |

| 5.2 Operating conditions                           | 30 |

| 5.3 Analog peripherals                             | 36 |

| 5.4 Digital peripherals                            | 38 |

| 5.5 Audio subsystem                                | 41 |

| 5.6 System resources                               | 44 |

| 5.7 Bluetooth® LE                                  | 49 |

| 6 Ordering information                             | 56 |

| 7 Packaging                                        | 57 |

| 8 Acronyms                                         |    |

| 9 Document conventions                             |    |

| 9.1 Units of measure                               | 62 |

| Revision history                                   |    |

Block diagram

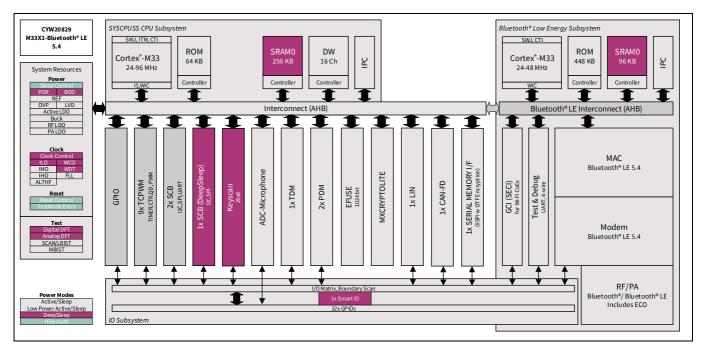

# 1 Block diagram

**Figure 2** shows the major subsystems and a simplified view of their interconnections. The color coding shows the lowest power mode where a block is still functional. For example, the SRAM is functional down to DS-RAM mode. It should also be noted that six SMIF IOs are in addition to the 26 GPIOs listed in **Figure 2**.

Figure 2 Functional block diagram

AIROC™ CYW20829 devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. All device interfaces can be permanently disabled (device security) for applications concerned about attacks due to a maliciously reprogrammed device. All programming, debug, and test interfaces are disabled when maximum device security is enabled. The security level is settable by the user.

Complete debug-on-chip functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The Eclipse IDE for ModusToolbox™ and Integrated Development Environment (IDE) provide fully integrated programming and debug support for these devices. The SWJ (SWD and JTAG) interface is fully compatible with industry-standard third party probes. With the ability to disable debug features, with very robust flash protection, and by allowing customer-proprietary functionality to be implemented in on-chip programmable blocks, CYW20829 provides a very high level of security.

**Functional description**

#### 2 **Functional description**

The following sections provide an overview of the features, capabilities and operation of each functional block identified in the block diagram in **Figure 2**. For more detailed information, refer to the following documentation:

### Board Support Package (BSP) documentation

BSPs are available on **GitHub**. They are aligned with Infineon kits and provide files for basic device functionality such as hardware configuration files, startup code, and linker files. The BSP also includes other libraries that are required to support a kit. Each BSP has its own documentation, but typically includes an API reference such as the example here. This search link finds all currently available BSPs on the Infineon GitHub site.

#### Hardware Abstraction Layer(HAL) API reference manual

The Infineon HAL provides a high-level interface to configure and use hardware blocks on Infineon MCUs. It is a generic interface that can be used across multiple product families. You can leverage the HAL's simpler and more generic interface for most of an application, even if one portion requires finer-grained control. The HAL API **Reference** provides complete details. Example applications that use the HAL download it automatically from the GitHub repository.

#### **CPU** and memory subsystem 2.1

AIROC™ CYW20829 has multiple bus masters, as Figure 2 shows. They are: CPU, datawire, QSPI, and a Crypto block. Generally, all memory and peripherals can be accessed and shared by all bus masters through multi-layer Arm® AMBA high-performance bus (AHB) arbitration. An interprocessor communication block (IPC) provides communication between the CPU and the Bluetooth® LE sub-system.

#### 2.1.1

The Cortex®-M33 has single-cycle multiply and a memory protection unit (MPU). It can run at up to 96 MHz in LP mode and 48 MHz in ULP mode. This is the main CPU, designed for a short interrupt response time, high code density, and high throughput.

Cortex®-M33 implements a version of the Thumb instruction set based on Thumb-2 technology (defined in the Army8-M architecture reference manual).

The main MCU also implements device-level security, safety, and protection features. Cortex®-M33 provides a secure, interruptible boot function. This guarantees that post boot, system integrity is checked and memory and peripheral access privileges are enforced.

The CPU has the following power draw, at V<sub>DDD</sub> = 3.0 V and using the internal buck regulator.

Table 1 Active current slope at V<sub>DDD</sub> = 3.0 V using the internal buck regulator

| System power mode |           |           |  |  |  |  |

|-------------------|-----------|-----------|--|--|--|--|

| CPU               | ULP       | LP        |  |  |  |  |

|                   | 22 μA/MHz | 40 μA/MHz |  |  |  |  |

The CPU can be selectively placed in Sleep and Deep Sleep power modes as defined by Arm<sup>®</sup>. The CPU also implements a Deep Sleep RAM (DS-RAM) mode in which almost all the circuits except RAM are powered OFF. Data in RAM is retained to maintain state. Upon exit, the CPU goes through a reset but can use the data in RAM to skip software initialization.

The CPU also has nested vectored interrupt controllers (NVIC) for rapid and deterministic interrupt response, and wakeup interrupt controllers (WIC) for CPU wakeup from Deep Sleep power mode.

CYW20829 has a debug access port (DAP) that acts as the interface for device programming and debug. An external programmer or debugger (the "host") communicates with the DAP through the device serial wire debug (SWD) or Joint Test Action Group (JTAG) interface pins. Through the DAP (and subject to device security restrictions), the host can access the device memory and peripherals as well as the registers in the CPU.

CPU debug and trace features are as follows:

• Six hardware breakpoints and four watchpoints, serial wire viewer (SWV), and printf()-style debugging through the single wire output (SWO) pin.

**Functional description**

## 2.1.2 Interrupts

The CPU has interrupt request lines (IRQ), with the interrupt source 'n' directly connected to IRQn.

Each interrupt supports eight configurable priority levels. One system interrupt can be mapped to the CPU non-maskable interrupts (NMI). Multiple interrupt sources are capable of waking the device from Deep Sleep power mode using the WIC.

### 2.1.3 Datawire

Datawire is a light weight DMA controller with 16 channels, which support CPU-independent accesses to memory and peripherals. The descriptors for the channels are in SRAM and the number of descriptors is limited only by the size of the memory. Each descriptor can transfer data in two nested loops with configurable address increments to the source and destination.

## 2.1.4 Cryptography accelerator (Cryptolite)

A combination of HW and SW is able to support several cryptographic functions. Specifically it supports the following functions:

- Encryption/decryption

- AES-128 hardware accelerator with following supported modes:

- Electronic Code Book (ECB)

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR)

- Hashing

- Secure Hash Algorithm (SHA-256) hardware accelerator

- Message Authentication Functions (MAC)

- Hashed Message Authentication Code (HMAC) acceleration using SHA-256 hardware

- True Random Number Generator (TRNG)

- Vector unit hardware accelerator

- Digital Signature Verification using RSA

- Digital Signature Verification using ECDSA

### 2.1.5 Protection units

CYW20829 has multiple types of protection to control erroneous or unauthorized access to memory and peripheral registers.

Protection units support memory and peripheral access attributes including address range, read/write, code/data, privilege level, secure/non-secure, and protection context.

Protection units are configured at "Secure Boot" to control access privileges and rights for bus masters and peripherals. Up to eight protection contexts ("Secure Boot" is in protection context 0) allow access privileges for memory and system resources to be set by the "Secure Boot" process per protection context by bus master and code privilege level. Multiple protection contexts are available.

#### 2.1.6 AES-128

AES-128 component to accelerate block cipher functionality. This functionality supports forward encryption of a single 128 bit block with a 128 bit key. SHA-256 component to accelerate hash functionality. This component supports message schedule calculation for a 512-bit message chunk and processing of a 512-bit message chunk.

**Functional description**

## 2.1.7 Vector unit (VU)

VU component to accelerate asymmetric key cryptography (for example, RSA and ECC). This component supports large integer multiplication, addition, and so on. TRNG component based on a set of ring oscillators. The TRNG includes a HW health monitor.

## 2.1.8 Controller area network flexible data-rate (CAN FD)

CYW20829 supports the CAN FD controller that supports one CAN FD channel. All CAN FD controllers are compliant with the ISO 11898-1:2015 standard; an ISO 16845:2015 certificate is available. It also implements the time-triggered CAN (TTCAN) protocol specified in ISO 11898-4 (TTCAN protocol levels 1 and 2) completely in hardware. All functions concerning the handling of messages are implemented by the RX and TX handlers. The RX handler manages message acceptance filtering, transfer of received messages from the CAN core to a message RAM, and provides receive-message status. The TX handler is responsible for the transfer of transmit messages from the message RAM to the CAN core, and provides transmit-message status.

## 2.1.9 Local interconnect network (LIN)

CYW20829 contains a LIN channel. Each channel supports transmission/reception of data following the LIN protocol according to ISO standard 17987. Each LIN channel connects to an external transceiver through a 3-pin interface (including an enable function) and supports master and slave functionality. Each block also supports classic and enhanced checksum, along with break detection during message reception and wake-up signaling. Break detection, sync field, checksum calculations, and error interrupts are handled in hardware.

## 2.1.10 Real time clock (RTC)

- · Year/Month/Date, Day-of-week, Hour:Minute:Second fields

- 12- and 24-hour formats

- Automatic leap-year correction

#### **2.1.11** Memory

CYW20829 contains the SRAM, ROM, and eFuse memory blocks.

- **SRAM**: CYW20829 has 256-KB of SRAM. Power control and retention granularity is 64-KB blocks allowing the user to control the amount of memory retained in Deep Sleep. Memory is not retained in Hibernate mode.

- **ROM**: The 64-KB ROM, also referred to as the supervisory ROM (SROM), provides code (ROM Boot) for several system functions. The ROM contains, primarily device initialization and security. ROM code is executed, in protection context 0.

- **eFuse**: A one-time programmable (OTP) eFuse array consists of 1024 bits, which are reserved for system use such as Die ID, Device ID, initial trim settings, device life cycle, and security settings. Some of the bits are available for storing security key information and hash values and can be programmed by the user for device security.

Each fuse is individually programmed; once programmed (or "blown"), its state cannot be changed. Blowing a fuse transitions it from the default state of '0' to '1'. To program an eFuse, VDDIO1 must be at 2.5 V ±5%.

Because blowing an eFuse is an irreversible process, programming is recommended only in mass production under controlled factory conditions by Infineon provided provisioning tools.

Functional description

### 2.1.12 **Boot code**

On a device reset, the boot code in ROM is the first code to execute. This code performs the following:

- Device trim setting (calibration)

- · Setting the device protection units

- Setting device access restrictions for secure life cycle states

- Configures the Debug Access Port

- In secure life cycle supports secure debug via authenticated debug token

- Configures the SMIF for external flash access

- In secure life cycle validates first user code in external flash by checking its digital signature. Supports OTF decryption of encrypted images in external flash

- Copies the application bootstrap from the external flash to SRAM and jumps to the ROM. It cannot be changed and acts as the Root of Trust in a secure system.

It should also be noted that the ROM code sets the system clock to 48 MHz IHO source.

## 2.1.13 Memory map

The 32-bit (4 GB) address space is divided into the regions shown in **Table 3**. Note that code can be executed from the Code, and Internal RAM or External flash.

Table 2 Address map

| Address range              | Name                   | Use                                                                                                                                 |

|----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 0000 – 0x1FFF FFFF  | Code                   | Program code region. It includes the exception vector table, which starts at address 0.                                             |

| 0x2000 0000 – 0x3FFF FFFF  | SRAM                   | Data region                                                                                                                         |

| 0x4000 0000 – 0x5FFF FFFF  | Peripheral             | All peripheral registers. Code cannot be executed from this region. Bit-band in this region is not supported.                       |

| 0x6000 0000 – 0x8FFF FFFF  | External NVM           | SMIF/Quad SPI, (see the "QSPI interface serial memory interface (SMIF)" on page 16 section). Code can be executed from this region. |

| 0xA000 0000 – 0xDFFF FFFF  | External Device        | Not used                                                                                                                            |

| 0xE000 0000 – 0xE00F FFFF  | Private Peripheral Bus | Provides access to peripheral registers within the CPU core.                                                                        |

| 0xE010 0A000 – 0xFFFF FFFF | Device                 | Device-specific system registers                                                                                                    |

The device memory map is shown in **Table 3**.

Table 3 Internal memory address map

| Address range              | Memory type | Size         |

|----------------------------|-------------|--------------|

| 0x0000 0000 – 0x0001 0000  | ROM         | 64 KB        |

| 0x2000 0000 - 0x 2004 0000 | SRAM        | Up to 256 KB |

System resources

## 3 System resources

## 3.1 Power system

The power system provides assurance that voltage levels are as required for each respective mode and will either delay mode entry (on power-on reset (POR), for example) until voltage levels are as required for proper function or generate resets (brown-out detect (BOD)) when the power supply drops below specified levels. The design guarantees safe chip operation between power supply voltage dropping below specified levels (for example, below 1.7 V) and the reset occurring. There are no voltage sequencing requirements.

The  $V_{DDD}$  supply (1.7 to 3.6 V) powers an on-chip buck regulator which offers a selectable (1.0Vor 1.16 V) core operating voltage (VCCD). The selection lets users choose between two system power modes:

- System Low Power (LP) operates VCCD at 1.1 V and offers high performance, with no restrictions on device configuration.

- System Ultra Low Power (ULP) operates VCCD at 1.0 V for exceptional low power, but imposes limitations on clock speeds.

The Bluetooth® radio requires 1.1 V for operation. Bluetooth® system may override user core voltage selection when the radio is turned on. System voltage will return to the user selected value automatically once Bluetooth® radio activity is completed. Refer to "Power supply considerations" on page 28 for more details.

### 3.1.1 Power modes

CYW20829 can operate in four system and three CPU power modes. These modes are intended to minimize the average power consumption in an application. For more details on power modes and other power-saving configuration options, see the relevant application note,

Power modes supported by CYW20829, in the order of decreasing power consumption, are:

- System Low Power (LP) All peripherals and CPU power modes are available at maximum speed

- System Ultra Low Power (ULP) All peripherals and CPU power modes are available, but with limited speed

- CPU Active CPU is executing code in system LP or ULP mode

- CPU Sleep CPU code execution is halted in system LP or ULP mode

- CPU Deep Sleep CPU code execution is halted and system Deep Sleep is requested in system LP or ULP mode

- System Deep Sleep Only low-frequency peripherals are available after both CPUs enter CPU Deep Sleep mode

- System Hibernate Device and I/O states are frozen and the device resets on wakeup

- Deep Sleep RAM only RAM and IO states are retained. All system activity except for select low power peripherals ceases until system exits from this state. The CPU resets upon exit but can skip software initialization since RAM is retained.

CPU Active, Sleep, and Deep Sleep are standard Arm®-defined power modes supported by the Arm® CPU instruction set architecture (ISA). System LP, ULP, Deep Sleep, Deep Sleep RAM and Hibernate modes are additional low-power modes supported by the CYW20829.

System resources

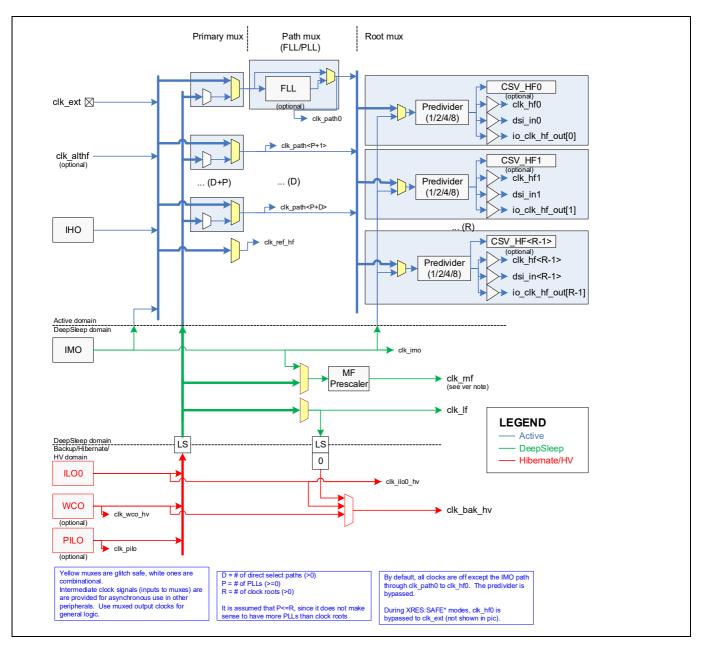

## 3.1.2 CYW20829 clock system

CYW20829 clock system consists of a combination of oscillators, external clock, and frequency-locked loop. Specifically, the following:

- Internal main oscillator (IMO)

- Internal low-speed oscillator (ILO)

- Watch crystal oscillator (WCO)

- System 24-MHz crystal oscillator

- External clock input

- One frequency-locked loop (FLL)

- Internal high-speed oscillator (IHO)

Clocks may be buffered and brought out to a pin on a smart I/O port.

**Table 4** shows the mapping of port and associated clock group mapped to peripherals.

Table 4 Mapping of clock groups to peripherals

| DCLK          | Doot als als           |             | Frequency         |                    |                                                                                                                                                                                                  |  |  |  |  |  |

|---------------|------------------------|-------------|-------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PCLK<br>group | Root clock<br>(clk_hf) | Peripherals | LP<br>(1.1 V Typ) | ULP<br>(1.0 V Typ) | Description                                                                                                                                                                                      |  |  |  |  |  |

| 0             | clk_hf0                | CPU Trace   | 24 MHz            | 24 MHz             | -                                                                                                                                                                                                |  |  |  |  |  |

|               |                        | SCB         |                   |                    |                                                                                                                                                                                                  |  |  |  |  |  |

|               |                        | TCPWM       | =                 |                    | Async peripherals: Strobe signals are driven                                                                                                                                                     |  |  |  |  |  |

| 1             | clk_hf1                | LIN         | 96 MHz            | 48 MHz             | through dividers; Interface clock is generated inside the peripheral with the                                                                                                                    |  |  |  |  |  |

|               |                        | CANFD       | -                 |                    | main group clock.                                                                                                                                                                                |  |  |  |  |  |

|               |                        | SMARTIO     |                   |                    |                                                                                                                                                                                                  |  |  |  |  |  |

|               |                        | SMIF        |                   |                    | Direct connection pass through from clk_hf.                                                                                                                                                      |  |  |  |  |  |

|               |                        | BTSS        |                   |                    | This clock is not used for interface clock,                                                                                                                                                      |  |  |  |  |  |

| 2             | clk_hf0                | СКҮРТО      | 96 MHz            | 48 MHz             | rather it is used for the MMIO clocks of SMIF,<br>BTSS and CRYPTO. BTSS uses this clock for<br>Master and Slave AHB/MMIO transactions,<br>and SMIF also uses this clock for FAST/SLOW<br>clocks. |  |  |  |  |  |

|               |                        | PDM         |                   |                    | Uses PERI ACLK with default div by 2 option,                                                                                                                                                     |  |  |  |  |  |

| 3             | clk_hf1                | TDM         | 96 MHz            | 48 MHz             | required interface frequencies are obtained by further division inside the peripheral.                                                                                                           |  |  |  |  |  |

| 4             | clk_hf2                | BTSS        | 48 MHz            | 48 MHz             | RPU clock for BTSS                                                                                                                                                                               |  |  |  |  |  |

| 5             | clk_hf3                | ADCMIC      | 24 MHz            | 24 MHz             | Direct connection for ADCMIC, main source of clk_hf3 is clk_althf which is the BTSS ECO clock.                                                                                                   |  |  |  |  |  |

| 6             | clk_hf1 SM             |             | 96 MHz            | 48 MHz             | Direct connection for SMIF and SMARTIO peripherals. This clock is an interface clocks for these peripherals.                                                                                     |  |  |  |  |  |

System resources

## 3.1.3 Internal main oscillator (IMO)

The IMO is the primary source of internal clocking. It is trimmed during testing to achieve the specified accuracy. The IMO default frequency is 8 MHz and tolerance is  $\pm 2\%$ .

## 3.1.4 Internal low-speed oscillator (ILO)

The ILO is a very low power oscillator, nominally 32 kHz, which operates in all power modes. The ILO can be calibrated against a higher accuracy clock for better accuracy.

Figure 3 CYW20829 clocking diagram with corresponding oscillators

**Note**: Using PILO as the ILO clock source will result in longer boot time.

System resources

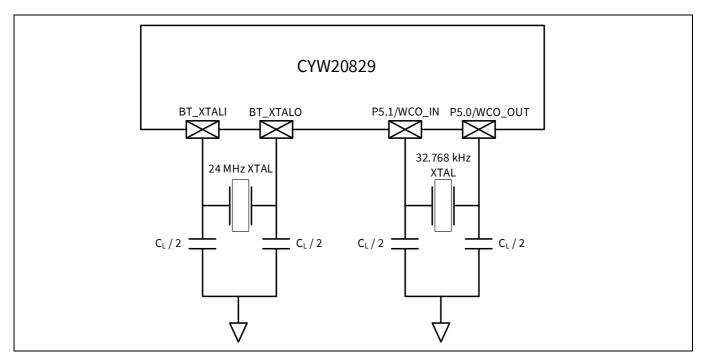

#### 3.1.5 External crystal oscillators (ECO)

Figure 4 shows all of the external crystal oscillator circuits for CYW20829. The component values shown are typical; check the ECO specifications for the crystal values, and the crystal datasheet for the load capacitor values. The ECO and WCO require balanced external load capacitors. For more information, see the HW design guidelines. Note that its performance is affected by GPIO switching noise.

Figure 4 **External oscillator**

#### Watchdog timers (WDT, MCWDT) 3.1.6

CYW20829 has one WDT and two multi-counter WDTs (MCWDTs). The WDT has a 16-bit free-running counter, Each MCWDT has two 16-bit counters and one 32-bit counter, with multiple operating modes. All of the 16-bit counters can generate a watchdog device reset. All of the counters can generate an interrupt on a match event.

The WDT is clocked by the ILO. It can do interrupt/wakeup generation in system LP/ULP, Deep Sleep, and Hibernate power modes. The MCWDTs are clocked by LFCLK (ILO or WCO). It can do periodic interrupt/wakeup generation in system LP/ULP and Deep Sleep power modes.

#### 3.1.7 **Clock dividers**

Integer and fractional clock dividers are provided for peripheral use and timing purposes. There are one or more:

- 8-bit clock dividers

- 16-bit integer clock dividers

- 16.5-bit fractional clock dividers

- 24.5-bit fractional clock divider

#### **Trigger routing** 3.1.8

CYW20829 contains a trigger multiplexer block. This is a collection of digital multiplexers and switches that are used for routing trigger signals between peripheral blocks and between GPIOs and peripheral blocks.

There are two types of trigger routing. Trigger multiplexers have reconfigurability in the source and destination. There are also hardwired switches called "one-to-one triggers", which connect a specific source to a destination. The user can enable or disable the route.

System resources

#### 3.1.9 Reset

CYW20829 can be reset from a variety of sources:

- Power-on reset (POR) to hold the device in reset while the power supply ramps up to the level required for the device to function properly. POR activates automatically at power-up.

- Brown-out detect (BOD) reset to monitor the digital voltage supply V<sub>DDD</sub> and generate a reset if V<sub>DDD</sub> falls below the minimum required logic operating voltage.

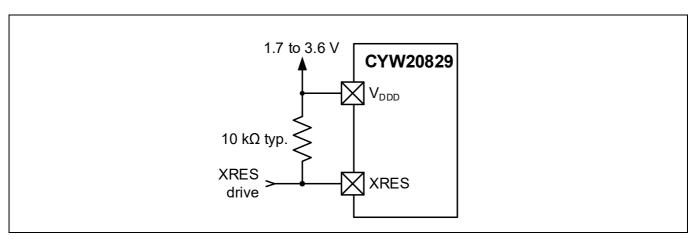

- External reset dedicated pin (XRES) to reset the device using an external source. The XRES pin is active LOW. It can be connected either to a pull-up resistor to V<sub>DDD</sub>, or to an active drive circuit, as **Figure 5** shows. If a pull-up resistor is used, select its value to minimize current draw when the pin is pulled LOW; 10 kΩ is typical.

Figure 5 XRES connection diagram

- Watchdog Timer (WDT or MCWDT) to reset the device if firmware fails to service it within a specified timeout period.

- Software-initiated reset to reset the device on demand using firmware.

- Logic-protection fault can trigger an interrupt or reset the device if unauthorized operating conditions occur; for example, reaching a debug breakpoint while executing privileged code.

- Hibernate wakeup reset to bring the device out of the system Hibernate low-power mode.

Reset events are asynchronous and guarantee reversion to a known state. Some of the reset sources are recorded in a register, which is retained through reset and allows software to determine the cause of the reset.

## 3.2 Bluetooth® LE radio and subsystem

CYW20829 incorporates a Bluetooth® 5.4 LE subsystem (BLESS) that contains the physical layer (PHY) and link layer (LL) engines with an embedded security engine. The Bluetooth® LE SS supports all Bluetooth® LE 5.4 features including LE 2 Mbps, LE Long Range, LE Advertising Extensions, LE Isochronous Channels, Periodic Advertising with Responses (PAwR), Encrypted Advertising Data, LE GATT Security Levels Characteristic and Advertising Coding Selection. Infineon also provides extensive driver library and middleware support for Bluetooth® LE; see "Eclipse IDE for Modustoolbox™ software" on page 3.

The physical layer consists of the digital PHY and the RF transceiver that transmits and receives Gaussian frequency shift keying (GFSK) packets at 1 or 2 Mbps over a 2.4 GHz ISM band, The device also supports Bluetooth® LE long range, both 500 and 125 kbps speeds.

The baseband controller is a composite hardware and firmware implementation that supports both master and slave modes. Key protocol elements, such as HCI and link control, are implemented in firmware. Time-critical functional blocks, such as encryption, CRC, data whitening, and access code correlation, are implemented in hardware (in the LL engine).

System resources

The RF transceiver contains an integrated balun, which provides a single-ended RF port pin to drive a 50  $\Omega$  antenna via a matching/filtering network. In the receive direction, this block converts the RF signal from the antenna to a digital bit stream after performing GFSK demodulation. In the transmit direction, this block performs GFSK modulation and then converts a digital baseband signal to a radio frequency before transmitting it through the antenna.

## 3.3 Programmable analog-to-digital converter (ADC)

## 3.3.1 Sigma delta ADC

The ADC block is a single switched-cap  $\Sigma$ - $\Delta$  ADC core for audio and DC measurement. It operates at the 12-MHz clock rate and has 32 DC input channels, including eight GPIO inputs. The internal bandgap reference has  $\pm 5\%$  accuracy without calibration. Different calibration and digital correction schemes can be applied to reduce ADC absolute error and improve measurement accuracy in DC.

One of three internal references may be used for the ADC reference voltage:  $V_{DDA}$ ,  $V_{DDA/2}$ , and an analog reference (AREF). AREF is nominally 1.2 V, trimmed to  $\pm 1\%$ .

## 3.4 Programmable digital

- System Deep Sleep operation

- Asynchronous or synchronous (clocked) operation

- Can be synchronous or asynchronous

## 3.5 Fixed-function digital

## 3.5.1 Timer/counter/pulse-width modulator (TCPWM) block

- The TCPWM supports the following operational modes:

- Timer-counter with compare

- Timer-counter with capture

- Quadrature decoding

- Pulse width modulation (PWM)

- Pseudo-random PWM

- PWM with dead time

- Up, down, and up/down counting modes

- Clock pre-scaling (division by 1, 2, 4, ... 64, 128)

- Double buffering of compare/capture and period values

- Underflow, overflow, and capture/compare output signals

- Supports interrupt on:

- Terminal count Depends on the mode; typically occurs on overflow or underflow

- Capture/compare The count is captured to the capture register or the counter value equals the value in the compare register

- Complementary output for PWMs

- Selectable start, reload, stop, count, and capture event signals for each TCPWM; with rising edge, falling edge, both edges, and level trigger options. The TCPWM has a Kill input to force outputs to a predetermined state.

In this device there are:

- Two 32-bit TCPWMs

- Seven 16-bit TCPWMs

System resources

## 3.5.2 Serial communication blocks (SCB)

- This product line has three SCBs:

- First SCB: Configurable as SPI or I<sup>2</sup>C

- Second SCB: Configurable as SPI or UART

- Third SCB: Configurable as I<sup>2</sup>C or UART

- One SCB (SCB #0) can operate in system Deep Sleep mode with an external clock; this SCB can be either SPI slave or I<sup>2</sup>C slave.

- I<sup>2</sup>C mode: The SCB can implement a full multi-master and slave interface (it is capable of multimaster arbitration). This block can operate at speeds of up to 1 Mbps (Fast Mode Plus). It also supports EZI2C, which creates a mailbox address range and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in the memory. The SCB supports a 256-byte FIFO for receive and transmit.

The  $I^2C$  peripheral is compatible with  $I^2C$  standard-mode, Fast Mode, and Fast Mode Plus devices. The  $I^2C$  bus I/O is implemented with GPIO in open-drain modes.

- **UART mode**: This is a full-feature UART operating at up to 8 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO 7816) protocols, all of which are minor variants of the basic UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows the addressing of peripherals connected over common Rx and Tx lines. Common UART functions such as parity error, break detect, and frame error are supported. A 256-byte FIFO allows much greater CPU service latencies to be tolerated.

- **SPI mode**: The SPI mode supports full SPI, Secure Simple Pairing (SSP) (essentially adds a start pulse that is used to synchronize SPI Codecs), and Microwire (half-duplex form of SPI). The SPI block supports an EZSPI mode in which the data interchange is reduced to reading and writing an array in memory. The SPI interface operates with a 4-MHz clock.

## 3.5.3 QSPI interface serial memory interface (SMIF)

A serial memory interface is provided, running at up to 48 MHz. It supports single, dual and quad SPI configurations, and supports up to four external memory devices. It supports two modes of operation:

- Memory-mapped I/O (MMIO), a command mode interface that provides data access via the SMIF registers and FIFOs

- Execute-in-Place (XIP), in which AHB reads and writes are directly translated to SPI read and write transfers.

In XIP mode, the external memory is mapped into the CYW20829 internal address space, enabling code execution directly from the external memory. To improve performance, a 32 KB cache is included. XIP mode also supports AES-128 based on-the-fly encryption and decryption, enabling secure storage and access of code and data in the external memory.

System resources

#### 3.6 **GPIO**

CYW20829 has up to 32 GPIOs, which implement:

- · Eight drive strength modes:

- Analog input mode (input and output buffers disabled) on some IOs

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- Strong pull-up with strong pull-down

- Weak pull-up with weak pull-down

- Hold mode for latching previous state (used for retaining the I/O state in system Hibernate and deep sleep mode)

- Selectable slew rates for dV/dt-related noise control to improve EMI

The pins are organized in logical entities called ports, which are up to eight pins in width. Data output and pin state registers store, respectively, the values to be driven on the pins and the input states of the pins.

Every pin can generate an interrupt if enabled; each port has an interrupt request (IRQ) associated with it.

The port 4 pins are capable of overvoltage-tolerant (OVT) operation, where the input voltage may be higher than  $V_{DDD}$ . OVT pins are commonly used with  $I^2C$ , to allow powering the chip OFF while maintaining a physical connection to an operating  $I^2C$  bus without affecting its functionality.

GPIO pins can be ganged to source or sink higher values of current. GPIO pins, including OVT pins, may not be pulled up higher than the absolute maximum; see "Electrical specifications" on page 29.

During power-on and reset, the pins are forced to the analog input drive mode, with input and output buffers disabled, so as not to crowbar any inputs and/or cause excess turn-on current.

A multiplexing network known as the high-speed I/O matrix (HSIOM) is used to multiplex between various peripheral and analog signals that may connect to an I/O pin.

In order to get the best performance, the following frequency and drive mode constraints may be applied. The DRIVE\_SEL values (refer to **Table 5**) represent drive strengths.

Table 5 DRIVE\_SEL values

| Ports        | Maximum frequency      | Drive strength for V <sub>DDD</sub> 2.7 V | Drive strength for V <sub>DDD</sub> > 2.7 V |

|--------------|------------------------|-------------------------------------------|---------------------------------------------|

| Ports 0, 1   | 8 MHz                  | DRIVE_SEL 2                               | DRIVE_SEL 3                                 |

| Ports 2 to 5 | 16 MHz; 24 MHz for SPI | DRIVE_SEL 2                               | DRIVE_SEL 3                                 |

System resources

## 3.7 Special-function peripherals

## 3.7.1 Audio subsystem

This subsystem consists of the following hardware blocks:

- One inter-IC sound (I<sup>2</sup>S) interface

- Two pulse-density modulation (PDM) to pulse-code modulation (PCM) decoder channels

The I<sup>2</sup>S interface implements two independent hardware FIFO buffers TX and RX, which can operate in master or slave mode. The following features are supported:

- Multiple data formats I<sup>2</sup>S, left-justified, Time Division Multiplexed (TDM) mode A, and TDM mode B

- Programmable channel/word lengths 8/16/18/20/24/32 bits

- Internal/external clock operation. Up to 192 ksps

- Interrupt mask events trigger, not empty, full, overflow, underflow, watchdog

- Configurable FIFO trigger level with datawire support

The I<sup>2</sup>S interface is commonly used to connect with audio codecs, simple DACs, and digital microphones.

The PDM-to-PCM decoder implements a single hardware Rx FIFO that decodes a stereo or mono 1-bit PDM input stream to PCM data output. The following features are supported:

- Programmable data output word length 16/18/20/24 bits

- Configurable PDM clock generation. Range from 384 kHz to 3.072 MHz

- Droop correction and configurable decimation rate for sampling; up to 48 ksps

- Programmable high-pass filter gain

- Interrupt mask events not empty, overflow, trigger, underflow

- Configurable FIFO trigger level with DMA support

The PDM-to-PCM decoder is commonly used to connect to digital PDM microphones. Up to two microphones can be connected to the same PDM data line.

System resources

# **Pinouts**

## Table 6 Packages and pin information

| Table 6              | Packages all   | u pili iiii | Offication          |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|----------------------|----------------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin name             | Pin number     | I/O         | Power domain        | Description                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Pili liallie         | QFN-56         | 1/0         | Power domain        | Description                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Microphone           | •              |             | •                   |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| MIC_P                | 54             | 1           |                     | Microphone positive input                                                                                                                                        |  |  |  |  |  |  |  |  |

| MIC_N                | 55             | <b>]</b>    | $V_{DDA}$           | Microphone negative input                                                                                                                                        |  |  |  |  |  |  |  |  |

| MIC_BIAS             | 53             | 0           | 7                   | Microphone bias supply                                                                                                                                           |  |  |  |  |  |  |  |  |

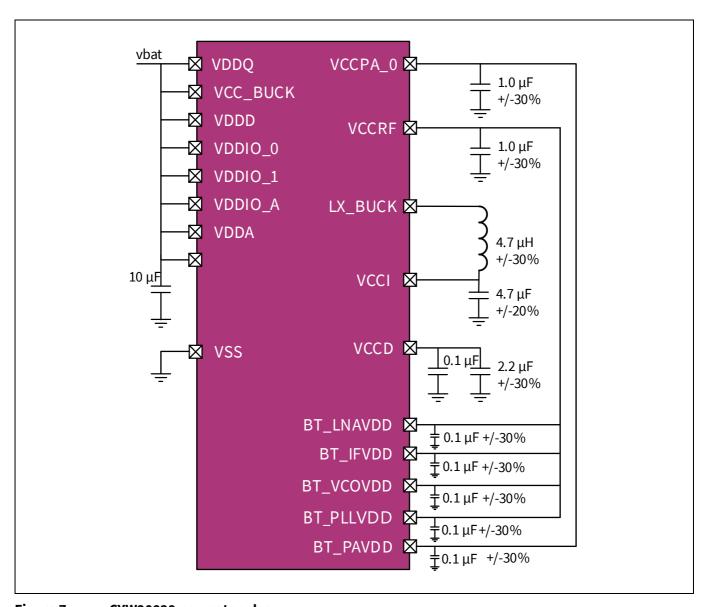

| Onboard swit         | ching regulato | r and LD0   | Os                  |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| $V_{DDQ}$            | 15             |             | _                   | External supply to PMU analog                                                                                                                                    |  |  |  |  |  |  |  |  |

| V <sub>CC_BUCK</sub> | 17             | ]'          | _                   | External supply to switching regulator                                                                                                                           |  |  |  |  |  |  |  |  |

| LX_BUCK              | 16             | 0           | _                   | Switching regulator output                                                                                                                                       |  |  |  |  |  |  |  |  |

| V <sub>CCD</sub>     | 18             | ]           | _                   | Digital LDO output                                                                                                                                               |  |  |  |  |  |  |  |  |

| V <sub>CCI</sub>     | 19             | I           | _                   | RF and digital LDO input                                                                                                                                         |  |  |  |  |  |  |  |  |

| Baseband sup         | oply           |             | •                   |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| V <sub>DDIO_0</sub>  | 42             |             | V <sub>DDIO_0</sub> | Supply for GPIO ports                                                                                                                                            |  |  |  |  |  |  |  |  |

| V <sub>DDIO_1</sub>  | 52             | ],          | V <sub>DDIO_1</sub> | Supply for GPIO ports and eFuse programming.<br>See <b>Table 9</b> for eFuse programming requirements.                                                           |  |  |  |  |  |  |  |  |

| V <sub>DDIO_A</sub>  | 7              |             | V <sub>DDIO_A</sub> | Supply for analog GPIO ports                                                                                                                                     |  |  |  |  |  |  |  |  |

| $V_{DDA}$            | 56             |             | $V_{DDA}$           | Analog power supply voltage                                                                                                                                      |  |  |  |  |  |  |  |  |

| RF power sup         | ply            |             | •                   |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| V <sub>CCRF</sub>    | 20             | 0           | _                   | RFLDO output                                                                                                                                                     |  |  |  |  |  |  |  |  |

| V <sub>DDD</sub>     | 22             | I           | _                   | PALDO and sub-system resources supply                                                                                                                            |  |  |  |  |  |  |  |  |

| V <sub>CCPA_0</sub>  | 21             | 0           | _                   | PALDO output                                                                                                                                                     |  |  |  |  |  |  |  |  |

| BT_VCOVDD            | 28             |             | BT_VCOVDD           | VCO supply                                                                                                                                                       |  |  |  |  |  |  |  |  |

| BT_LNAVDD            | 26             |             | BT_LNAVDD           | LNA supply                                                                                                                                                       |  |  |  |  |  |  |  |  |

| BT_IFVDD             | 27             | ] I         | BT_IFVDD            | IFPLL power supply                                                                                                                                               |  |  |  |  |  |  |  |  |

| BT_PLLVDD            | 29             |             | BT_PLLVDD           | RFPLL and crystal oscillator supply                                                                                                                              |  |  |  |  |  |  |  |  |

| BT_PAVDD             | 24             |             | BT_PAVDD            | Internal PA supply                                                                                                                                               |  |  |  |  |  |  |  |  |

| Radio I/O            | •              |             | •                   |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| BT_RF                | 25             | I/O         | BT_RF               | RF antenna port                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Crystal              |                |             |                     |                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| BT_XTALI             | 30             | I           | BT_PLLVDD           | Crystal oscillator input. Two external load capacitors are required to work with the crystal oscillator. The selection of the load capacitors is XTAL-dependent. |  |  |  |  |  |  |  |  |

| BT_XTALO             | 31             | 0           | 7                   | Crystal oscillator output                                                                                                                                        |  |  |  |  |  |  |  |  |

|                      |                |             |                     | •                                                                                                                                                                |  |  |  |  |  |  |  |  |

System resources

Table 6

Packages and pin information (continued)

| Table 6                         | Packages an | a pin into | ermation (continued | 1)                                                                         |

|---------------------------------|-------------|------------|---------------------|----------------------------------------------------------------------------|

| Pin name                        | Pin number  | 1/0        | Power domain        | Description                                                                |

| Pinname                         | QFN-56      | I/O        | Power domain        | Description                                                                |

| GPIO                            |             |            |                     |                                                                            |

| P0.0                            | 32          |            |                     |                                                                            |

| P0.1                            | 33          |            |                     |                                                                            |

| P0.2                            | 34          |            |                     |                                                                            |

| P0.3                            | 35          |            |                     |                                                                            |

| P0.4                            | 36          |            |                     |                                                                            |

| P0.5                            | 37          |            |                     |                                                                            |

| P1.0                            | 38          |            |                     |                                                                            |

| P1.1                            | 39          |            |                     |                                                                            |

| P1.2                            | 40          |            |                     |                                                                            |

| P1.3                            | 41          |            |                     |                                                                            |

| P1.4                            | 43          |            |                     |                                                                            |

| P1.5                            | 44          |            |                     |                                                                            |

| P1.6                            | 45          |            |                     |                                                                            |

| P2.0                            | 46          |            |                     |                                                                            |

| P2.1                            | 47          |            |                     |                                                                            |

| P2.2                            | 48          |            |                     | Conoral input and output port                                              |

| P2.3                            | 49          | I/O        |                     | General input and output port. See <b>Table 7</b> for alternate functions. |

| P2.4                            | 50          |            | $V_{DDIO}$          |                                                                            |

| P2.5                            | 51          |            |                     |                                                                            |

| P3.0                            | 1           |            |                     |                                                                            |

| P3.1                            | 2           |            |                     |                                                                            |

| P3.2                            | 3           |            |                     |                                                                            |

| P3.3                            | 4           |            |                     |                                                                            |

| P3.4                            | 5           |            |                     |                                                                            |

| P3.5                            | 6           |            |                     |                                                                            |

| P3.6                            | 8           |            |                     |                                                                            |

| P3.7                            | 9           |            |                     |                                                                            |

| P4.0                            | 13          |            |                     |                                                                            |

| P4.1                            | 14          |            |                     |                                                                            |

| P5.0/<br>WCO_OUT<br>P5.1/WCO_IN | 10          | 1          |                     |                                                                            |

|                                 | 11 12       |            |                     |                                                                            |

| P5.2                            |             |            |                     |                                                                            |

| XRES                            | 23          | I          |                     | Active-low system reset without internal pull-up resistor                  |

System resources

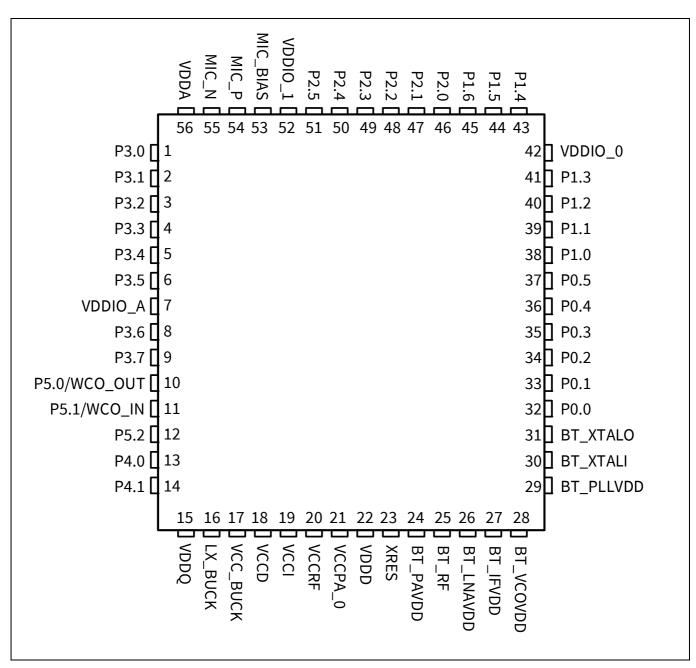

Figure 6 Device pinout for 56-QFN package

System resources

Table 7

${\bf Multiple\ alternate\ functions}^{[1]}$

| Port/<br>Pin | Ana-<br>log | ACT<br>#0                                | ACT<br>#1                                  | ACT<br>#4 | ACT<br>#5                            | ACT<br>#6 | ACT<br>#7 | ACT<br>#8                        | ACT<br>#9                        | ACT<br>#10                        | ACT<br>#11 | ACT<br>#12                            | ACT<br>#13                      | ACT<br>#14 | ACT<br>#15 | DS #2                              | DS<br>#3                 | DS #5 | DS<br>#6                         | DS #7 |

|--------------|-------------|------------------------------------------|--------------------------------------------|-----------|--------------------------------------|-----------|-----------|----------------------------------|----------------------------------|-----------------------------------|------------|---------------------------------------|---------------------------------|------------|------------|------------------------------------|--------------------------|-------|----------------------------------|-------|

| P0.0         |             | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[0]:3 | tcpw<br>m[0].l<br>ine_c<br>ompl[<br>262]:0 |           |                                      |           |           |                                  | pdm<br>pdm<br>_clk[<br>1]:0      |                                   |            | tdm.t<br>dm_t<br>x_mc<br>k[0]:0       | tdm.t<br>dm_r<br>x_mc<br>k[0]:0 |            |            | keysc<br>an.ks<br>_<br>col[2]      |                          |       | scb[0<br>].spi_<br>selec<br>t1:0 |       |

| P0.1         |             |                                          | tcpw<br>m[0].l<br>ine[25<br>6]:1           |           |                                      |           |           |                                  | pdm<br>pdm<br>_dat<br>a[1]:<br>0 |                                   |            | tdm.t<br>dm_t<br>x_sck<br>[0]:0       |                                 |            |            | keysc<br>an.ks<br>_<br>col[3]      |                          |       | scb[0<br>].spi_<br>selec<br>t2:0 |       |

| P0.2         |             | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[1]:3 | tcpw<br>m[0].l<br>ine_c<br>ompl[<br>256]:1 |           |                                      |           |           |                                  |                                  | peri.tr<br>_io_<br>input[<br>4]:0 |            | tdm.t<br>dm_t<br>x_fsy<br>nc[0]:<br>0 |                                 |            |            | keysc<br>an.ks<br>-<br>col[11<br>] | scb[0<br>].i2c_<br>scl:0 |       | scb[0<br>].spi_<br>mosi:<br>0    |       |

| P0.3         |             | tcpw<br>m[0].l<br>ine[0]<br>:4           | tcpw<br>m[0].l<br>ine[25<br>7]:1           |           |                                      |           |           | scb[1].<br>spi_se<br>lect3:<br>0 |                                  |                                   |            | tdm.t<br>dm_t<br>x_sd[<br>0]:0        |                                 |            |            | keysc<br>an.ks<br>-<br>col[12      | ].i2c_<br>sda:0          |       | scb[0<br>].spi_<br>miso:<br>0    |       |

| P0.4         |             | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[0]:4 | tcpw<br>m[0].l<br>ine_c<br>ompl[<br>257]:1 | k:0       | cpus<br>s.<br>trace<br>data[<br>3]:1 |           |           | scb[1].<br>spi_se<br>lect2:<br>0 |                                  | peri.tr<br>_io_<br>input[<br>0]:0 |            | tdm.t<br>dm_r<br>x_sck<br>[0]:0       |                                 |            |            | keysc<br>an.ks<br>-<br>row[0<br>]  |                          |       | scb[0<br>].spi_<br>clk:0         |       |

<sup>1.</sup> The notation for a signal is of the form IPName[x]. Signal\_name[u]:y.

IPName = Name of the block (such as tcpwm), x = Unique instance of the IP, Signal\_name = Name of the signal, u = Signal number where there are more than one signals for a particular signal name, y = Designates copies of the signal name.

For example, the name tcpwm[0].line\_comp[[3]:4 indicates that this is instance 0 of a tcpwm block, the signal is line\_compl # 3 (complement of the line output) and this is the fourth occurrence (copy) of the signal. Signal copies are provided to allow flexibility in routing and to maximize utilization of on-chip resources.

Table 7

**AIROC™ Bluetooth® LE 5.4 MCU**

| _ |

|---|

| Ī |

|   |

|   |

|   |

|   |

| 1 |

|   |

|   |

|   |

|   |

| Port/<br>Pin | Ana-<br>log | ACT<br>#0                                | ACT<br>#1                                  | ACT<br>#4 | ACT<br>#5                               | ACT<br>#6                 | ACT<br>#7                | ACT<br>#8                        | ACT<br>#9 | ACT<br>#10                        | ACT<br>#11                             | ACT<br>#12                            | ACT<br>#13 | ACT<br>#14 | ACT<br>#15                     | DS #2                             | DS<br>#3 | DS #5                                    | DS<br>#6                         | DS #7 |

|--------------|-------------|------------------------------------------|--------------------------------------------|-----------|-----------------------------------------|---------------------------|--------------------------|----------------------------------|-----------|-----------------------------------|----------------------------------------|---------------------------------------|------------|------------|--------------------------------|-----------------------------------|----------|------------------------------------------|----------------------------------|-------|

| P0.5         |             | tcpw<br>m[0].l<br>ine[1]<br>:4           | tcpw<br>m[0].l<br>ine[25<br>8]:1           |           | cpus<br>s.<br>trace<br>data[<br>2]:1    |                           |                          | scb[1].<br>spi_se<br>lect1:<br>0 |           | peri.tr<br>_io_<br>input[<br>1]:0 |                                        | tdm.t<br>dm_r<br>x_fsy<br>nc[0]:<br>0 |            |            | smif.<br>spihb<br>_sele<br>ct1 | keysc<br>an.ks<br>-<br>row[1<br>] |          |                                          | scb[0<br>].spi_<br>selec<br>t0:0 |       |

| P1.0         |             | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[1]:4 | tcpw<br>m[0].l<br>ine_c<br>ompl[<br>258]:1 |           | cpus<br>s.<br>trace<br>data[<br>1]:1    | scb[1].<br>uart_<br>cts:0 |                          | scb[1].<br>spi_se<br>lect0:<br>0 |           |                                   | peri.t<br>r_io_<br>outp<br>ut[0]:<br>0 | dm_r<br>x_sd[                         |            |            |                                | keysc<br>an.ks<br>-<br>row[2<br>] |          | cpuss<br>.swj_<br>swo_<br>tdo            |                                  |       |

| P1.1         |             |                                          | tcpw<br>m[0].l<br>ine[25<br>9]:1           |           | cpus<br>s.<br>trace<br>data[<br>0]:1    | scb[1].<br>uart_<br>rts:0 |                          | scb[1].<br>spi_cl<br>k:0         |           |                                   | peri.t<br>r_io_<br>outp<br>ut[1]:<br>0 |                                       |            |            |                                | keysc<br>an.ks<br>-<br>row[3<br>] |          | cpuss<br>.swj_<br>swdo<br>e_<br>tdi      |                                  |       |

| P1.2         |             | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[0]:5 | tcpw<br>m[0].l<br>ine_c<br>ompl[<br>259]:1 |           | cpus<br>s.<br>trace<br>-<br>clock<br>:1 | scb[1<br>].uart<br>_rx:0  | scb[2<br>].i2c_<br>scl:1 | scb[1].<br>spi_m<br>osi:0        |           | peri.tr<br>_io_<br>input[<br>2]:0 |                                        |                                       |            |            |                                | keysc<br>an.ks<br>-<br>row[4<br>] |          | cpuss<br>.swj_<br>swdi<br>o_tm<br>s      |                                  |       |

| P1.3         |             |                                          | tcpw<br>m[0].l<br>ine[26<br>0]:1           |           |                                         | scb[1<br>].uart<br>_tx:0  | scb[2<br>].i2c_<br>sda:1 | scb[1].<br>spi_m<br>iso:0        |           | peri.tr<br>_io_<br>input[<br>3]:0 |                                        |                                       |            |            |                                | keysc<br>an.ks<br>-<br>row[5      |          | cpuss<br>.clk_s<br>wj_s<br>wclk<br>_tclk |                                  |       |

| P1.4         |             |                                          |                                            |           |                                         |                           |                          |                                  |           |                                   | lin[0]<br>.lin_<br>en[1]<br>:0         |                                       |            |            |                                | keysc<br>an.ks<br>–<br>col[4]     |          |                                          |                                  |       |

Note

1. The notation for a signal is of the form IPName[x].signal\_name[u]:y.

IPName = Name of the block (such as tcpwm), x = Unique instance of the IP, Signal\_name = Name of the signal, u = Signal number where there are more than one signals for a particular signal name, y = Designates copies of the signal name.

For example, the name tcpwm[0].line\_compl[3]:4 indicates that this is instance 0 of a tcpwm block, the signal is line\_compl # 3 (complement of the line output) and this is the fourth occurrence (copy) of the signal. Signal copies are provided to allow flexibility in routing and to maximize utilization of on-chip resources.

Table 7

**AIROC™ Bluetooth® LE 5.4 MCU**

Infineon

P2.3 P2.4

Multiple alternate functions<sup>[1]</sup> (COntinued)

The notation for a signal is of the form IPName[x].signal\_name[u]:y.

IPName = Name of the block (such as tcpwm), x = Unique instance of the IP, Signal\_name = Name of the signal, u = Signal number where there are more than one signals for a particular signal name, y = Designates copies of the signal name.

For example, the name tcpwm[0].line\_compl[3]:4 indicates that this is instance 0 of a tcpwm block, the signal is line\_compl # 3 (complement of the line output) and this is the fourth occurrence (copy) of the signal. Signal copies are provided to allow flexibility in routing and to maximize utilization of on-chip resources.

#### Port/ **ACT ACT** ACT **ACT ACT ACT ACT** DS DS Ana-**ACT ACT ACT ACT ACT ACT** ACT #15 Pin log #0 #1 #4 #5 #6 #7 #8 #9 #10 #11 #12 #13 #14 **DS** #2 #3 DS #5 #6 **DS #7** P1.5 lin[0] tcpw keysc tcpw m[0].l m[0].l .lin\_r an.ks ine[0] ine[26 x[1]: :6 1]:1 0 col[5] P1.6 lin[0] keysc tcpw tcpw srss. m[0].l m[0].l .lin\_t an.ks cal x[1]: ine\_c ine\_c wave ompl[ col[6] ompl [0]:6 261]:1 P2.0 smif. spihb \_sele ct0 P2.1 smif. spihb dat а3 P2.2 smif. spihb dat a2 smif. spihb \_dat a1 smif. spihb dat a0 P2.5 smif. spihb clk

Table 7

Port/ Ana-

Datasheet

Multiple alternate functions<sup>[1]</sup> (COntinued)

ACT ACT

ACT ACT

ACT ACT

ACT ACT

ACT

ACT

ACT

DS

DS

| Pin  | log            | #0                                       | #1                                        | #4 | #5                                        | #6                        | #7                       | #8                               | #9                          | #10                               | #11                            | #12                              | #13    | #14                     | #15 | DS #2                              | #3 | DS #5                           | #6 | DS #7 |

|------|----------------|------------------------------------------|-------------------------------------------|----|-------------------------------------------|---------------------------|--------------------------|----------------------------------|-----------------------------|-----------------------------------|--------------------------------|----------------------------------|--------|-------------------------|-----|------------------------------------|----|---------------------------------|----|-------|

| P3.0 | ic.gpi         |                                          | tcpw<br>m[0].l<br>ine[25<br>6]:0          |    | cpus<br>s.<br>trace<br>data[<br>3]:0      | scb[2<br>].uart<br>_cts:0 |                          | scb[1].<br>spi_se<br>lect0:<br>1 |                             |                                   |                                |                                  |        | btss.<br>uart_<br>cts:0 |     | keysc<br>an.ks<br>-<br>col[13      |    |                                 |    |       |

| P3.1 |                | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[0]:0 | tcpw<br>m[0].l<br>ine_o<br>mpl[2<br>56]:0 |    | cpus<br>s.<br>trace<br>data[<br>2]:0      | scb[2<br>].uart<br>_rts:0 |                          | scb[1].<br>spi_cl<br>k:1         |                             |                                   | lin[0]<br>.lin_<br>en[0]<br>:0 |                                  |        | btss.<br>uart_<br>rts:0 |     | keysc<br>an.ks<br>-<br>col[14<br>] |    | cpuss<br>.rst_s<br>wj_tr<br>stn |    |       |

| P3.2 | ic.gpi<br>o_ad | m[0].l                                   | tcpw<br>m[0].l<br>ine[25<br>7]:0          |    | cpus<br>s.<br>trace<br>-<br>data[<br>1]:0 | scb[2<br>].uart<br>_rx:0  | scb[2<br>].i2c_<br>scl:0 | scb[1].<br>spi_m<br>osi:1        | pdm<br>pdm<br>_clk[<br>0]:0 | _io_<br>input[                    |                                | canfd<br>[0].ttc<br>an_rx<br>[0] | ic.clk | uart_                   |     | keysc<br>an.ks<br>-<br>col[15      |    |                                 |    |       |

| P3.3 | ic.gpi         | tcpw<br>m[0].l<br>ine_c<br>ompl<br>[1]:0 |                                           |    | cpus<br>s.tra<br>ce_d<br>ata[0<br>]:0     | scb[2<br>].uart<br>_tx:0  | scb[2<br>].i2c_<br>sda:0 | scb[1].<br>spi_m<br>iso:1        | .                           | peri.tr<br>_io_i<br>nput[7<br>]:0 |                                |                                  |        | btss.<br>uart_<br>txd:0 |     | keysc<br>an.ks<br>-<br>col[16<br>] |    |                                 |    |       |

| P3.4 | ic.gpi<br>o_ad | m[0].l                                   | tcpw<br>m[0].l<br>ine[25<br>8]:0          |    | cpus<br>s.<br>trace<br>_cloc<br>k:0       |                           |                          | scb[1].<br>spi_se<br>lect3:<br>1 |                             |                                   |                                |                                  |        |                         |     | keysc<br>an.ks<br>-<br>col[7]      |    |                                 |    |       |

| P3.5 | ic.gpi         |                                          |                                           |    |                                           |                           |                          | scb[1].<br>spi_se<br>lect2:<br>1 |                             |                                   |                                |                                  |        |                         |     | keysc<br>an.ks<br>–<br>col[8]      |    |                                 |    |       |

Note

1. The notation for a signal is of the form IPName[x].signal\_name[u]:y.

IPName = Name of the block (such as tcpwm), x = Unique instance of the IP, Signal\_name = Name of the signal, u = Signal number where there are more than one signals for a particular signal name, y = Designates copies of the signal name.