# **Product Change Notification / SYST-06DCTZ778**

| ח | 2 | ŧ | Δ | • |

|---|---|---|---|---|

| u | а | L | ᆫ |   |

07-Nov-2023

# **Product Category:**

General Purpose FPGAs

# **PCN Type:**

Document Change

# **Notification Subject:**

Data Sheet - AN4153: Board and Layout Design Guidelines for SmartFusion 2 SoC and IGLOO 2 FPGAs

## **Affected CPNs:**

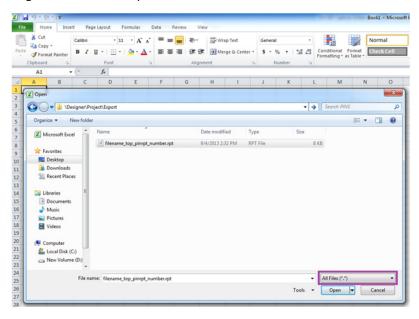

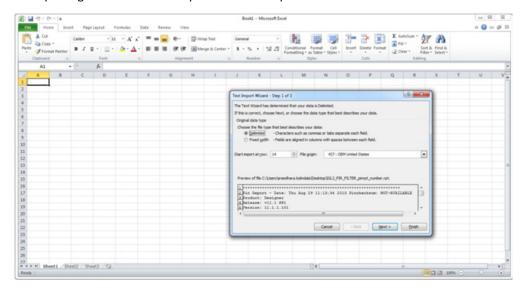

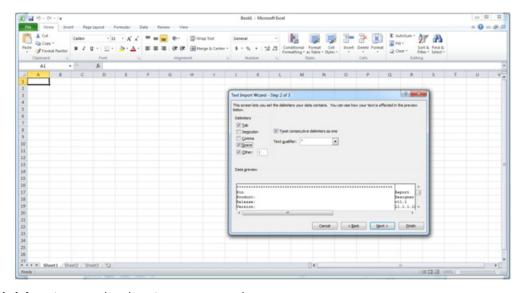

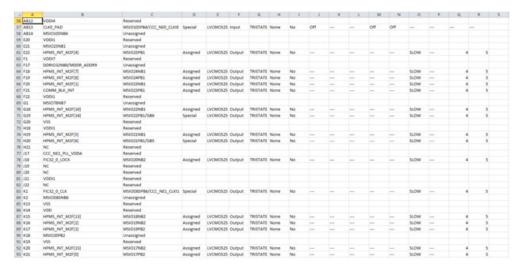

SYST-06DCTZ778\_Affected\_CPN\_11072023.pdf SYST-06DCTZ778\_Affected\_CPN\_11072023.csv

# **Notification Text:**

SYST-06DCTZ778

Microchip has released a new Datasheet for the AN4153: Board and Layout Design Guidelines for SmartFusion 2 SoC and IGLOO 2 FPGAs of devices. If you are using one of these devices please read the document located at AN4153: Board and Layout Design Guidelines for SmartFusion 2 SoC and IGLOO 2 FPGAs.

**Notification Status: Final**

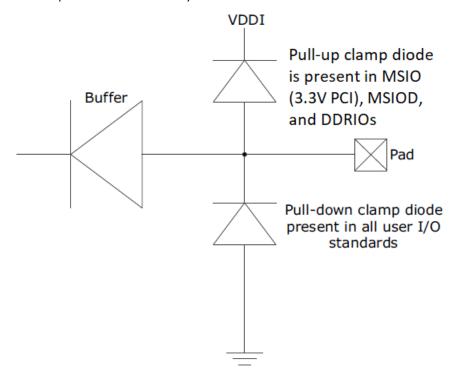

Description of Change: Revised the figure and associated text in section 1.9.1. Internal Clamp Diode Circuitry.

Impacts to Data Sheet: See above details.

Reason for Change: To improve productivity.

Change Implementation Status: Complete

Date Document Changes Effective: 07 Nov 2023

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices:: N/A

| Attachments:                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN4153: Board and Layout Design Guidelines for SmartFusion 2 SoC and IGLOO 2 FPGAs                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                             |

| Please contact your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                                                                    |

| Terms and Conditions:                                                                                                                                                                                                                                                                       |

| If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. |

| If you wish to <u>change your PCN profile, including opt out,</u> please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.                                       |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

#### Affected Catalog Part Numbers (CPN)

M2GL005-1FG484

M2GL005-1FG484I

M2GL005-1FGG484

M2GL005-1FGG484I

M2GL005-1FGG484T1

M2GL005-1TQG144

M2GL005-1TQG144I

M2GL005-1VF256

M2GL005-1VF256I

M2GL005-1VF400

M2GL005-1VF400I

M2GL005-1VFG256

M2GL005-1VFG256I

M2GL005-1VFG400

M2GL005-1VFG400I

M2GL005-FG484

M2GL005-FG484I

M2GL005-FGG484

M2GL005-FGG484I

M2GL005-TQG144

M2GL005-TQG144I

M2GL005-VF256

M2GL005-VF256I

M2GL005-VF400

M2GL005-VF400I

M2GL005-VFG256

M2GL005-VFG256I

M2GL005-VFG400

M2GL005-VFG400I

M2GL005S-1FG484

M2GL005S-1FG484I

M2GL005S-1FGG484

M2GL005S-1FGG484I

M2GL005S-1FGG484T2

M2GL005S-1TQG144

M2GL005S-1TQG144I

M2GL005S-1TQG144T2

M2GL005S-1VF256

M2GL005S-1VF256I

M2GL005S-1VF400

M2GL005S-1VF400I

M2GL005S-1VFG256

M2GL005S-1VFG256I

M2GL005S-1VFG256T2

M2GL005S-1VFG400

M2GL005S-1VFG400I

M2GL005S-1VFG400T2

M2GL005S-FG484

M2GL005S-FG484I

M2GL005S-FGG484

M2GL005S-FGG484I

M2GL005S-TQG144

MEGEOGSB TQGTTT

M2GL005S-TQG144I

M2GL005S-VF256

M2GL005S-VF256I

M2GL005S-VF400

M2GL005S-VF400I

M2GL005S-VFG256

M2GL005S-VFG256I

M2GL005S-VFG400

M2GL005S-VFG400I

M2GL010-1FG484

M2GL010-1FG484I

M2GL010-1FGG484

M2GL010-1FGG484I

M2GL010-1FGG484T1

M2GL010-1TQG144

M2GL010-1TQG144I

M2GL010-1VF256

M2GL010-1VF256I

M2GL010-1VF400

M2GL010-1VF400I

M2GL010-1VFG256

M2GL010-1VFG256I

M2GL010-1VFG400

M2GL010-1VFG400I

M2GL010-FG484

M2GL010-FG484I

M2GL010-FGG484

M2GL010-FGG484I

M2GL010-FGG484X417

M2GL010-TQG144

M2GL010-TQG144I

M2GL010S-1TQG144

M2GL010S-1TQG144I

M2GL010S-1TQG144T2

M2GL010S-TQG144

M2GL010S-TQG144I

M2GL010T-1FG484

M2GL010T-1FG484I

M2GL010T-1FG484M

M2GL010T-1FGG484

M2GL010T-1FGG484I

M2GL010T-1FGG484M

M2GL010T-1VF256

M2GL010T-1VF256I

M2GL010T-1VF400

M2GL010T-1VF400I

M2GL010T-1VFG256

M2GL010T-1VFG256I

1412 GE0101 1 41 G250

M2GL010T-1VFG400

M2GL010T-1VFG400I

M2GL010T-FG484

M2GL010T-FG484I

M2GL010T-FGG484

M2GL010T-FGG484I

M2GL010T-VF256

M2GL010T-VF256I

M2GL010TS-1FG484

M2GL010TS-1FG484I

M2GL010TS-1FG484M

M2GL010TS-1FGG484

M2GL010TS-1FGG484I

M2GL010TS-1FGG484M

M2GL010TS-1FGG484T2

M2GL010TS-1VF256

M2GL010TS-1VF256I

M2GL010TS-1VF400

M2GL010TS-1VF400I

M2GL010TS-1VFG256

M2GL010TS-1VFG256I

M2GL010TS-1VFG256T2

M2GL010TS-1VFG400

M2GL010TS-1VFG400I

M2GL010TS-1VFG400T2

M2GL010TS-FG484

M2GL010TS-FG484I

M2GL010TS-FGG484

M2GL010TS-FGG484I

M2GL010TS-VF256

M2GL010TS-VF256I

M2GL010TS-VF400

M2GL010TS-VF400I

M2GL010TS-VFG256

M2GL010TS-VFG256I

M2GL010TS-VFG400 M2GL010TS-VFG400I

M2GL025-1FCS325

M2GL025-1FCS325I

M2GL025-1FCSG325

M2GL025-1FCSG325I

M2GL025-1FG484

M2GL025-1FG484I

M2GL025-1FGG484

M2GL025-1FGG484I

M2GL025-1FGG484T1

M2GL025-1VF256

M2GL025-1VF256I

M2GL025-1VF400

M2GL025-1VF400I

M2GL025-1VFG256

M2GL025-1VFG256I

M2GL025-1VFG400

M2GL025-1VFG400I

M2GL025-FCS325

M2GL025-FCS325I

M2GL025-FCSG325

M2GL025-FCSG325I

M2GL025-FG484

M2GL025-FG484I

M2GL025-FGG484

M2GL025-FGG484I

M2GL025T-1FCS325

M2GL025T-1FCS325I

M2GL025T-1FCSG325

M2GL025T-1FCSG325I

M2GL025T-1FG484

M2GL025T-1FG484I

M2GL025T-1FG484M

M2GL025T-1FG484MX3

M2GL025T-1FGG484

M2GL025T-1FGG484I

M2GL025T-1FGG484M

M2GL025T-1VF256

M2GL025T-1VF256I

M2GL025T-1VF400

M2GL025T-1VF400I

M2GL025T-1VFG256

M2GL025T-1VFG256I

M2GL025T-1VFG400

M2GL025T-1VFG400I

M2GL025T-FCS325

M2GL025T-FCS325I

M2GL025T-FCSG325

M2GL025T-FCSG325I

M2GL025T-FG484

M2GL025T-FG484I

M2GL025T-FGG484

M2GL025T-FGG484I

M2GL025TS-1FCS325

M2GL025TS-1FCS325I

M2GL025TS-1FCSG325

M2GL025TS-1FCSG325I

M2GL025TS-1FG484

M2GL025TS-1FG484I

M2GL025TS-1FG484M

M2GL025TS-1FGG484

M2GL025TS-1FGG484I

M2GL025TS-1FGG484M

M2GL025TS-1FGG484T2

M2GL025TS-1VF256

M2GL025TS-1VF256I

M2GL025TS-1VF400

M2GL025TS-1VF400I

M2GL025TS-1VFG256

M2GL025TS-1VFG256I

M2GL025TS-1VFG256T2

M2GL025TS-1VFG400

M2GL025TS-1VFG400I

M2GL025TS-1VFG400T2

M2GL025TS-FCS325

M2GL025TS-FCS325I

M2GL025TS-FCSG325

M2GL025TS-FCSG325I

M2GL025TS-FG484

M2GL025TS-FG484I

M2GL025TS-FGG484

M2GL050-1FCS325

M2GL050-1FCS325I

M2GL050-1FCSG325

M2GL050-1FCSG325I

M2GL050-1FG484

M2GL050-1FG484I

M2GL050-1FG896

M2GL050-1FG896I

M2GL050-1FGG484

M2GL050-1FGG484I

M2GL050-1FGG896

M2GL050-1FGG896I

M2GL050-1VF400

M2GL050-1VF400I

M2GL050-1VFG400

M2GL050-1VFG400I

M2GL050-FCS325

M2GL050-FCS325I

M2GL050-FCSG325

M2GL050-FCSG325I

M2GL050-FG484

M2GL050-FG484I

M2GL050-FG896

M2GL050-FG896I

M2GL050-FGG484

M2GL050-FGG484I

M2GL050-FGG896

M2GL050-FGG896I

M2GL050T-1FCS325

M2GL050T-1FCS325I

M2GL050T-1FCSG325

M2GL050T-1FCSG325I

M2GL050T-1FG484

M2GL050T-1FG484I

M2GL050T-1FG484M

M2GL050T-1FG896

M2GL050T-1FG896I

M2GL050T-1FGG484

M2GL050T-1FGG484I

M2GL050T-1FGG484M

M2GL050T-1FGG896

M2GL050T-1FGG896I

M2GL050T-1VF400

M2GL050T-1VF400I

M2GL050T-1VFG400

M2GL050T-1VFG400I

M2GL050T-FCS325

M2GL050T-FCS325I

M2GL050T-FCSG325

M2GL050T-FCSG325I

M2GL050T-FG484

M2GL050T-FG484I

M2GL050T-FG896

M2GL050T-FG896I

M2GL050T-FGG484

M2GL050T-FGG484I

M2GL050T-FGG896

M2GL050T-FGG896I

M2GL050TS-1FCS325

M2GL050TS-1FCS325I

M2GL050TS-1FCSG325

M2GL050TS-1FCSG325I

M2GL050TS-1FG484

M2GL050TS-1FG484I

M2GL050TS-1FG484M

M2GL050TS-1FG896

M2GL050TS-1FG896I

M2GL050TS-1FGG484

M2GL050TS-1FGG484I

M2GL050TS-1FGG484M

M2GL050TS-1FGG896

M2GL050TS-1FGG896I

M2GL050TS-1VF400

M2GL050TS-1VF400I

M2GL050TS-1VFG400

M2GL050TS-1VFG400I

M2GL050TS-FCS325

M2GL050TS-FCS325I

M2GL050TS-FCSG325

M2GL050TS-FCSG325I

M2GL050TS-FG484

M2GL050TS-FG484I

M2GL050TS-FG896

M2GL050TS-FG896I

M2GL060-1FCS325

M2GL060-1FCS325I

M2GL060-1FCSG325

M2GL060-1FCSG325I

M2GL060-1FG484

M2GL060-1FG484I

M2GL060-1FG676

M2GL060-1FG676I

M2GL060-1FGG484

M2GL060-1FGG484I

M2GL060-1FGG484T1

M2GL060-1FGG676

M2GL060-1FGG676I

M2GL060-1VF400

M2GL060-1VF400I

M2GL060-1VFG400

M2GL060-1VFG400I

M2GL060-FCS325

M2GL060-FCS325I

M2GL060-FCSG325

M2GL060-FCSG325I

M2GL060-FG484

M2GL060-FG484I

M2GL060-FG676

M2GL060-FG676I

M2GL060-FGG484

M2GL060-FGG484I

M2GL060-FGG676

M2GL060-FGG676I

M2GL060T-1FCS325

M2GL060T-1FCS325I

M2GL060T-1FCSG325

M2GL060T-1FCSG325I

M2GL060T-1FG484

M2GL060T-1FG484I

M2GL060T-1FG484M

M2GL060T-1FG676

M2GL060T-1FG676I

M2GL060T-1FGG484

M2GL060T-1FGG484I

M2GL060T-1FGG484M

M2GL060T-1FGG676

M2GL060T-1FGG676I

M2GL060T-1VF400

M2GL060T-1VF400I

M2GL060T-1VFG400

M2GL060T-1VFG400I

M2GL060T-1VFG784

M2GL060T-1VFG784I

M2GL060T-FCS325

M2GL060T-FCS325I

M2GL060T-FCSG325

M2GL060T-FCSG325I

M2GL060T-FG484

M2GL060T-FG484I

M2GL060T-FG676

M2GL060T-FG676I

M2GL060T-FGG484

M2GL060T-FGG484I

M2GL060T-FGG676

M2GL060T-FGG676I

M2GL060TS-1FCS325

M2GL060TS-1FCS325I

M2GL060TS-1FCSG325

M2GL060TS-1FCSG325I

M2GL060TS-1FG484

M2GL060TS-1FG484I

M2GL060TS-1FG484M

M2GL060TS-1FG676

M2GL060TS-1FG676I

M2GL060TS-1FGG484

M2GL060TS-1FGG484I

M2GL060TS-1FGG484M

M2GL060TS-1FGG484T2

M2GL060TS-1FGG676

M2GL060TS-1FGG676I

M2GL060TS-1FGG676T2

M2GL060TS-1VF400

M2GL060TS-1VF400I

M2GL060TS-1VFG400

M2GL060TS-1VFG400I

M2GL060TS-1VFG400T2

M2GL060TS-1VFG784

M2GL060TS-1VFG784I

M2GL060TS-FCS325

M2GL060TS-FCS325I

M2GL060TS-FCSG325

M2GL060TS-FCSG325I

M2GL060TS-FG484

M2GL060TS-FG484I

M2GL060TS-FG676

M2GL060TS-FG676I

M2GL060TS-FGG484

M2GL060TS-FGG484I

M2GL090-1FCS325

M2GL090-1FCS325I

M2GL090-1FCSG325

M2GL090-1FCSG325I

M2GL090-1FG484

M2GL090-1FG484I

M2GL090-1FG676

M2GL090-1FG676I

M2GL090-1FGG484

M2GL090-1FGG484I

M2GL090-1FGG484T1

M2GL090-1FGG676

M2GL090-1FGG676I

M2GL090-FCS325

M2GL090-FCS325I

M2GL090-FCSG325

M2GL090-FCSG325I

M2GL090-FG484

M2GL090-FG484I

M2GL090-FG484IX3

M2GL090-FG676

M2GL090-FG676I

M2GL090-FGG484

M2GL090-FGG484I

M2GL090-FGG676

M2GL090-FGG676I

M2GL090T-1FCS325

M2GL090T-1FCS325I

M2GL090T-1FCSG325

M2GL090T-1FCSG325I

M2GL090T-1FG484

M2GL090T-1FG484I

M2GL090T-1FG484M

M2GL090T-1FG676

M2GL090T-1FG676I

M2GL090T-1FGG484

M2GL090T-1FGG484I

M2GL090T-1FGG484M

M2GL090T-1FGG676

M2GL090T-1FGG676I

M2GL090T-FCS325

M2GL090T-FCS325I M2GL090T-FCSG325

M2GL090T-FCSG325I

M2GL090T-FG484

M2GL090T-FG484I

M2GL090T-FG676

M2GL090T-FG676I

M2GL090T-FGG484

M2GL090T-FGG484I

M2GL090T-FGG676

M2GL090T-FGG676I

M2GL090TS-1FCS325

M2GL090TS-1FCS325I

M2GL090TS-1FCSG325

M2GL090TS-1FCSG325I

M2GL090TS-1FG484

M2GL090TS-1FG484I

M2GL090TS-1FG484M

M2GL090TS-1FG676

M2GL090TS-1FG676I

M2GL090TS-1FGG484

M2GL090TS-1FGG484I

M2GL090TS-1FGG484M

M2GL090TS-1FGG484T2

M2GL090TS-1FGG676

M2GL090TS-1FGG676I

M2GL090TS-1FGG676T2

M2GL090TS-FCS325

M2GL090TS-FCS325I

M2GL090TS-FCSG325

M2GL090TS-FCSG325I

M2GL150-1FC1152

M2GL150-1FC1152I

M2GL150-1FCG1152

M2GL150-1FCG1152I

M2GL150-1FCS536

M2GL150-1FCS536I

M2GL150-1FCSG536

M2GL150-1FCSG536I

M2GL150-1FCV484

M2GL150-1FCV484I

M2GL150-1FCVG484

M2GL150-1FCVG484I

M2GL150-FC1152

M2GL150-FC1152I

M2GL150-FCG1152

M2GL150-FCG1152I

M2GL150-FCS536

M2GL150-FCS536I

M2GL150-FCS536IX3

M2GL150-FCSG536

M2GL150-FCSG536I

M2GL150-FCV484

M2GL150-FCV484I

M2GL150-FCVG484

M2GL150-FCVG484I

M2GL150T-1FC1152

M2GL150T-1FC1152I

M2GL150T-1FC1152M

M2GL150T-1FCG1152

M2GL150T-1FCG1152I

M2GL150T-1FCG1152M

M2GL150T-1FCS536

M2GL150T-1FCS536I

M2GL150T-1FCSG536

M2GL150T-1FCSG536I

M2GL150T-1FCV484

M2GL150T-1FCV484I

M2GL150T-1FCV484M

M2GL150T-1FCVG484

M2GL150T-1FCVG484I

M2GL150T-FC1152

M2GL150T-FC1152I

M2GL150T-FCG1152

M2GL150T-FCG1152I

M2GL150T-FCS536

M2GL150T-FCS536I

M2GL150T-FCSG536

M2GL150T-FCSG536I

M2GL150T-FCV484

M2GL150T-FCV484I

M2GL150T-FCVG484

M2GL150T-FCVG484I

M2GL150TS-1FC1152

M2GL150TS-1FC1152I

M2GL150TS-1FC1152M

M2GL150TS-1FCG1152

M2GL150TS-1FCG1152I

M2GL150TS-1FCG1152M

M2GL150TS-1FCS536

M2GL150TS-1FCS536I

M2GL150TS-1FCSG536

M2GL150TS-1FCSG536I

M2GL150TS-1FCV484

M2GL150TS-1FCV484I

M2GL150TS-1FCV484M

M2GL150TS-1FCVG484

M2GL150TS-1FCVG484I

M2GL150TS-FC1152

M2GL150TS-FC1152I

M2GL150TS-FCG1152

M2GL150TS-FCG1152I

M2GL150TS-FCS536

M2GL150TS-FCS536I

M2GL150TS-FCSG536

M2GL150TS-FCSG536I

M2GL150TS-FCV484

M2GL150TS-FCV484I

M2GL150TS-FCVG484

M2GL150TS-FCVG484I

# **SmartFusion 2 and IGLOO 2 FPGA Board and Layout Design Guidelines**

**AN4153**

# Introduction (Ask a Question)

This application note provides board-level design guidelines for SmartFusion® 2 and IGLOO® 2 devices. The 2. Layout Guidelines for SmartFusion 2 and IGLOO 2-Based Board Design section describes the PCB design. These guidelines must be treated as a supplement to standard board-level design practices.

Good board design practices are required to obtain expected performance from both PCB and SmartFusion 2/ IGLOO 2 devices. High quality and reliable results depend on minimizing noise levels, preserving signal integrity, meeting impedance and power requirements.

This document assumes that the reader has a good understanding of the SmartFusion 2/IGLOO 2 devices, is experienced in digital and analog board design, and knows about the electrical characteristics of systems.

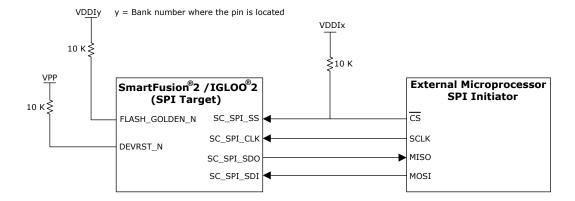

**Important:** The standard uses "Master" and "Slave." The equivalent Microchip terminology used in this document is **Initiator** and **Target**, respectively.

# **Table of Contents**

| Intr | oducti | on                                                                                        | 1     |

|------|--------|-------------------------------------------------------------------------------------------|-------|

| 1.   | Desig  | n Considerations                                                                          | 4     |

|      | 1.1.   | Power Supplies                                                                            | 4     |

|      | 1.2.   | I/O Glitch                                                                                | 7     |

|      | 1.3.   | Limiting VDD Surge Current                                                                | 14    |

|      | 1.4.   | Clocks                                                                                    | 16    |

|      | 1.5.   | Reset Circuit                                                                             | 18    |

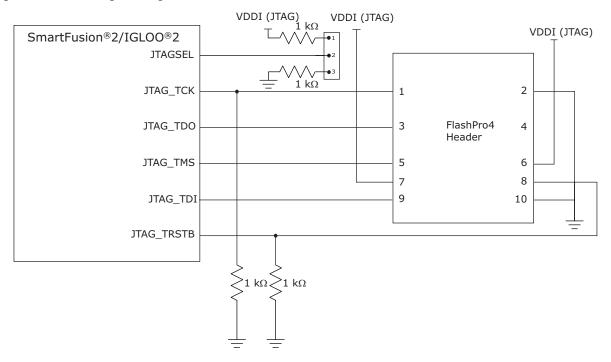

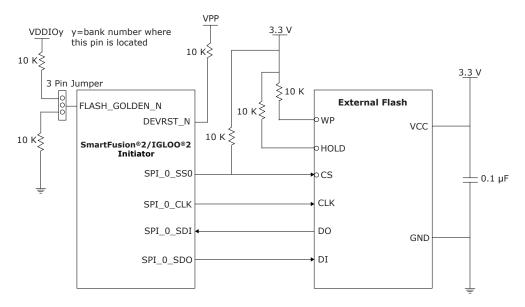

|      | 1.6.   | Device Programming                                                                        | 20    |

|      | 1.7.   | SerDes                                                                                    | 24    |

|      | 1.8.   | LPDDR, DDR2, and DDR3                                                                     | 26    |

|      | 1.9.   | User I/O and Clock Pins                                                                   | 32    |

|      | 1.10.  | Obtaining a Two-Rail Design for Non-SerDes Applications                                   | 33    |

|      | 1.11.  | Configuring Pins in Open Drain                                                            | 34    |

|      | 1.12.  | Brownout Detection (BOD)                                                                  | 34    |

|      | 1.13.  | Simultaneous Switching Noise                                                              | 35    |

| 2.   | Lavou  | at Guidelines for SmartFusion 2 and IGLOO 2-Based Board Design                            | 36    |

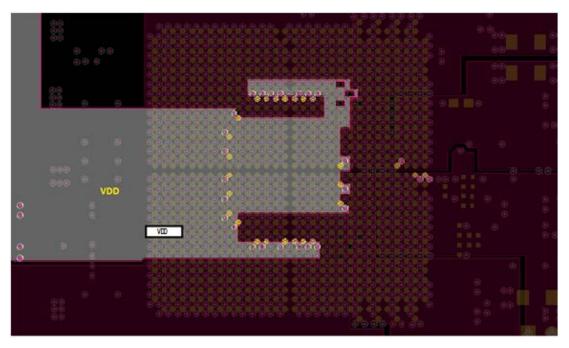

| _,   | 2.1.   | Power Supply                                                                              |       |

|      | 2.2.   | Core Supply (VDD)                                                                         |       |

|      | 2.3.   | SerDes                                                                                    |       |

|      | 2.4.   | DDR                                                                                       |       |

|      | 2.5.   | PLL                                                                                       |       |

|      | 2.6.   | I/O Power Supply                                                                          |       |

|      | 2.7.   | Programming Power Supply (VPP or VCCENVM)                                                 |       |

|      | 2.8.   | High-Speed Serial Link (SerDes)                                                           |       |

|      | 2.9.   | Considerations for Simulation                                                             |       |

|      |        | DDR3 Layout Guidelines                                                                    |       |

|      |        | References                                                                                |       |

| 3.   | PCB I  | nspection Guidelines                                                                      | 70    |

|      |        |                                                                                           |       |

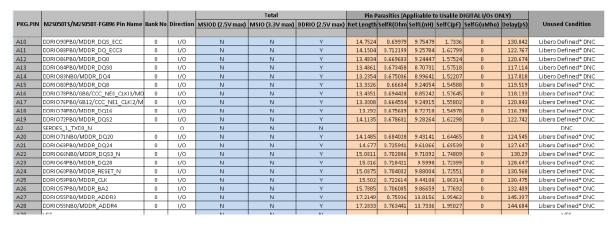

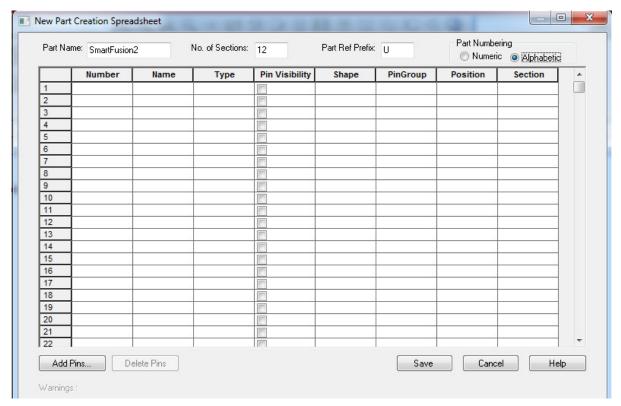

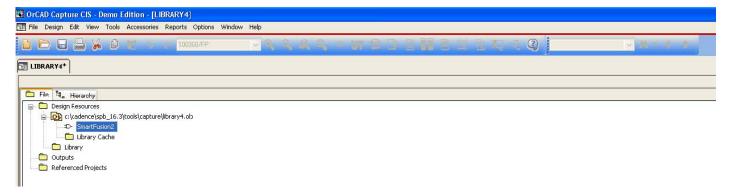

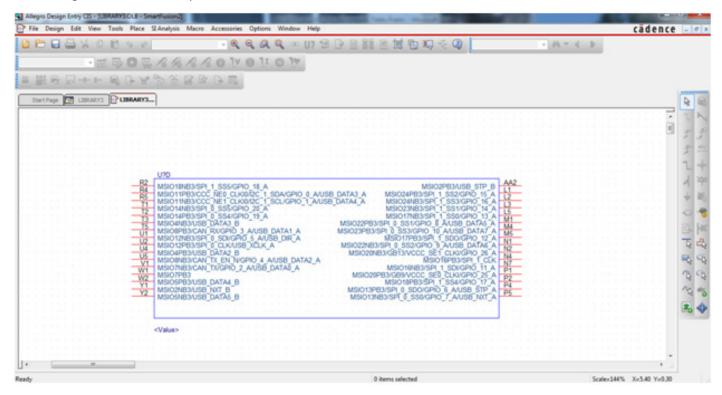

| 4.   |        | ing Schematic Symbols Using Cadence OrCAD Capture CIS for SmartFusion2 and IGLOO2 Designs |       |

|      | 4.1.   | Creating Schematic Symbols using Pin Assignment Tables (PAT)                              |       |

|      | 4.2.   | Creating Schematic Symbols with User Defined Pin Names                                    | /9    |

| 5.   | Board  | Design and Layout Checklist                                                               | 88    |

|      | 5.1.   | Prerequisites                                                                             | 88    |

|      | 5.2.   | Design Checklist                                                                          | 88    |

|      | 5.3.   | Layout Checklist                                                                          | 95    |

| 6.   | Appe   | ndix A: Special Layout Guidelines—Crystal Oscillator                                      | 97    |

| 7.   | Appe   | ndix B: Stack-Up                                                                          | 98    |

| 8.   |        | ndix C: Dielectric Material                                                               |       |

|      |        |                                                                                           |       |

| 9.   | Appe   | ndix D: Power Integrity Simulation Topology                                               | . 101 |

| 10.  | Appe   | ndix E: X-Ray Inspection                                                                  | . 102 |

| 11. Revision History                      | 103 |

|-------------------------------------------|-----|

| Microchip FPGA Support                    | 107 |

| Microchip Information                     | 107 |

| The Microchip Website                     | 107 |

| Product Change Notification Service       | 107 |

| Customer Support                          | 107 |

| Microchip Devices Code Protection Feature | 107 |

| Legal Notice                              | 108 |

| Trademarks                                |     |

| Quality Management System                 | 109 |

| Worldwide Sales and Service               | 110 |

# 1. Design Considerations (Ask a Question)

The SmartFusion2/IGLOO2 devices support various high-speed interfaces using both Double Data Rate Input/Output (DDRIO) and SerDes I/O. DDRIO is a multi-standard I/O optimized for low-power DDR, DDR2, and DDR3 performance. SerDes I/O are dedicated to high-speed serial communication protocols. The SerDes I/O supports protocols such as PCI Express 2.0, 10 Gbps attachment unit interface (XAUI), Serial Gigabit Media Independent Interface (SGMII), JESD204B, and user-defined high-speed serial protocol implementation in fabric.

Routing high-speed serial data over a PCB is a challenge as losses, dispersion, and crosstalk effects increase with speed. Channel losses and crosstalk decrease the signal-to-noise ratio and limit the data rate on the channel.

# 1.1 Power Supplies (Ask a Question)

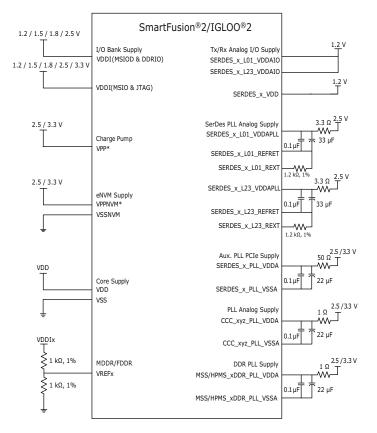

The following figure shows the typical power supply requirements for SmartFusion2/IGLOO2 devices. For more information about decoupling capacitors associated with individual power supplies, see Table 1-2.

Figure 1-1. Power Supplies

**Important:** The power supply settings for all the PLLs (Auxiliary PLL PCIe Supply, SerDes, MDDR, FDDR, and CCC) must be the same in Libero® SoC and on the board. The PLLs (Auxiliary PLL PCIe Supply, SerDes, MDDR, FDDR, and CCC) can be connected to a 2.5V or 3.3V supply.

For M2S090T(S), M2GL090T(S), M2S150T(S), and M2GL150T(S) devices, the VPP and VPPNVM must be connected to a 3.3V supply.

For the CCC\_xyz\_PLL supplies, xy refers to the location of the PLL in the device (NE/ NW/ SW) and z refers to the number associated with the PLL (0 or 1).

The PLL RC values shown in the preceding figure are applicable to all variants of SmartFusion2/ IGLOO2 devices.

When the power rails are in use, see Figure 1-1. For unused cases, see Figure 1-3. The power supply needed for IGLOO2 and SmartFusion2 FPGAs is Core VDD (Fabric voltage). Serdes\_VDD is tied to VDD internally. Therefore, the same regulator must be used to drive SERDES\_x\_VDD, SERDES x Lyz VDDAIO, and Core VDD together.

For the device-package combinations listed in the following table, the SERDES\_x\_VDD pins are shorted with VDD pins inside the package substrate to free the package pins.

**Table 1-1.** Device-Package Combinations Without SERDES x VDD Pin

| Device                                 | Package |

|----------------------------------------|---------|

| M2S025T, M2GL025T                      | FCS325  |

| M2S050T(S), M2GL050T(S)                | FCS325  |

| M2S060T(S), M2GL060T(S)                | FCS325  |

| M2S90T(S), M2GL90T(S)                  | FCS325  |

| M2S10T(S), M2GL010T(S)                 | VF256   |

| M2S025TS, M2S025T, M2GL025TS, M2GL025T | VF256   |

| M2S150T(S), M2GL150T(S)                | FCV484  |

| M2S150TS, M2S150T, M2GL150TS, M2GL150T | FCS536  |

For detailed pin descriptions, see DS0115: SmartFusion2 Pin Descriptions Datasheet or DS0124: IGLOO2 Pin Descriptions Datasheet.

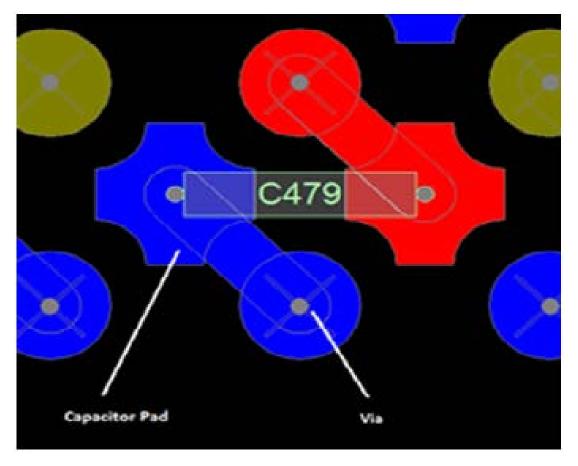

#### 1.1.1 Power Supply Decoupling (Ask a Question)

To reduce any potential fluctuation on the power supply lines, decoupling capacitors, bypass capacitors, and other power supply filtering techniques must be used.

- For values ranging from 1 nF to 100 μF, use X7R or X5R (dielectric material) type capacitors.

- For values ranging from 100 μF to 1000 μF, use tantalum capacitors.

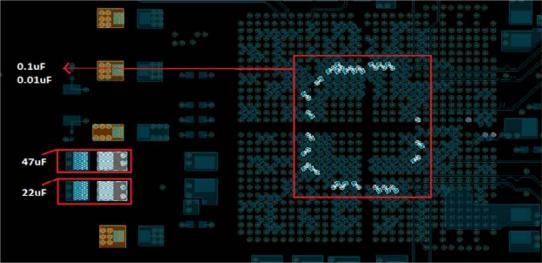

The following table lists the recommended number of PCB decoupling capacitors for an M2S050T/M2GL050T-FG896 device.

**Table 1-2.** Power Supply Decoupling Capacitors

| Pin Name | Number<br>of Pins | Ceramic Caps |        |       |       |       | Tantalur | n Caps |         |        |

|----------|-------------------|--------------|--------|-------|-------|-------|----------|--------|---------|--------|

|          |                   | 0.01 μF      | 0.1 μF | 10 μF | 33 µF | 22 μF | 47 μF    | 100 μF | 220 μF¹ | 330 µF |

| VDD      | 24                | 12           | 12     | _     | _     | _     | _        | 1      | 3       | 1      |

| VDD10    | 29                | 14           | 14     | _     | _     | _     | 2        | _      | _       | _      |

| VDDI1    | 4                 | 2            | 2      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI2    | 4                 | 2            | 2      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI3    | 5                 | 2            | 3      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI4    | 3                 | 2            | 1      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI5    | 29                | 14           | 14     | _     | _     | _     | 2        | _      | _       | _      |

| VDDI6    | 1                 | 1            | _      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI7    | 6                 | 3            | 3      | 1     | _     | _     | _        | _      | _       | _      |

| VDDI8    | 5                 | 2            | 3      | 1     | _     | _     | _        | _      | _       | _      |

| continued            | continued      |                |                |                |   |   |         |        |   |   |

|----------------------|----------------|----------------|----------------|----------------|---|---|---------|--------|---|---|

| Pin Name             | Number of Pins | Ceramic        | Caps           |                |   |   | Tantalu | m Caps |   |   |

| VDDI9                | 1              | 1              | 1              | _              | _ | _ | _       | _      | _ | _ |

| VPP                  | 4              | 2              | 2              | 1              | _ | _ | _       | _      | _ | _ |

| VREF0                | 3              | 2              | 1              | 1              | _ | _ | _       | _      | _ | _ |

| VREF5                | 3              | 2              | 1              | 1              | _ | _ | _       | _      | _ | _ |

| VPPNVM               | 1              | 1              | _              | 1              | _ | _ | _       | _      | _ | _ |

| SERDES_0_VDD         | 2              | 1              | 1              | 1 <sup>2</sup> | _ | _ | _       | _      | _ | _ |

| SERDES_1_VDD         | 2              | 1              | 1              | 12             | _ | _ | _       | _      | _ | _ |

| SERDES_0_L01_VDDAIO  | 1              | 12             | 12             | 13             | _ | _ | _       | _      | _ | _ |

| SERDES_0_L23_VDDAIO  | 1              | 1 <sup>2</sup> | 1 <sup>2</sup> | 1 <sup>3</sup> | _ | _ | _       | _      | _ | _ |

| SERDES_1_L01_VDDAIO  | 1              | 12             | 12             | 13             | _ | _ | _       | _      | _ | _ |

| SERDES_1_L23_VDDAIO  | 1              | 12             | 12             | 13             | _ | _ | _       | _      | _ | _ |

| CCC_NE0_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| CCC_NE1_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| CCC_NW0_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| CCC_NW1_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| CCC_SW0_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| CCC_SW1_PLL_VDDA     | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| MSS_FDDR_PLL_VDDA    | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| MSS_PLL_MDDR_VDDA    | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| PLL_SERDES_0_VDDA    | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

| PLL_SERDES_1_VDDA    | 1              | _              | 1              | _              | _ | 1 | _       | _      | _ | _ |

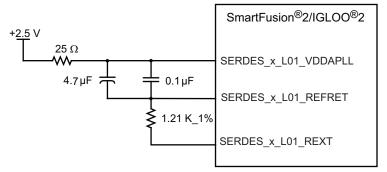

| SERDES_0_L01_VDDAPLL | 1              | _              | 1              | _              | 1 | _ | _       | _      | _ | _ |

| SERDES_0_L23_VDDAPLL | 1              | _              | 1              | _              | 1 | _ | _       | _      | _ | _ |

| SERDES_1_L01_VDDAPLL | 1              | _              | 1              | _              | 1 | _ | _       | _      | _ | _ |

| SERDES_1_L23_VDDAPLL | 1              | _              | 1              | _              | 1 | _ | _       | _      | _ |   |

#### **Notes:**

- 1.  $220 \mu F$  is used to limit surge current for the VDD supply.

- 2. Single ceramic decoupling capacitor is required for both the pins at the device.

- 3. Single ceramic decoupling capacitor is required for four pins at the device.

The following table lists the recommended decoupling capacitors for the SmartFusion2/IGLOO2 devices. For placement and routing details, see Layout Guidelines for SmartFusion2- and IGLOO2-Based Board Design.

Table 1-3. Recommended Capacitors

| Part Number        | Manufacturer | Description                          |

|--------------------|--------------|--------------------------------------|

| GRM155R71C103KA01D | Murata       | Ceramic 0.01 μF, 16V, 10%, X7R, 0402 |

| GRM155R71C104KA88D | Murata       | Ceramic 0.1 μF, 16V, 10%, X7R, 0402  |

| GRM188R60J106ME47D | Murata       | Ceramic 10 µF, 6.3V, X5R, 0603       |

| T491B475M016AT     | KEMET        | Tantalum 4.7 μF, 16V, 20%, 1411      |

| T491B226M016AT     | KEMET        | Tantalum 22 μF, 16V, 20%, 1411       |

| continued          |              |                                 |

|--------------------|--------------|---------------------------------|

| Part Number        | Manufacturer | Description                     |

| T491B476M010AT     | KEMET        | Tantalum 47 μF, 10V, 20%SMD     |

| T520V107M010ATE050 | KEMET        | Tantalum 100 μF, 10V, 20%, 2917 |

| TPSD337K010R0050   | AVX          | Tantalum 330 μF, 10V, 10%, 2917 |

## 1.1.2 Power Supply Sequencing (Ask a Question)

On detection of a power-up event, the POR circuit sends the power-on reset signal to the system controller and reset controller in the SmartFusion2/IGLOO2 devices. The power-on reset circuitry in SmartFusion2/IGLOO2 devices require the VDD and VPP supplies to ramp monotonically from 0V to the minimum recommended operating voltage within a predefined time. There is no sequencing requirement on VDD and VPP. Four ramp rate options are available during design generation:  $50 \mu s$ , 1 ms, 10 ms, and 100 ms. Each selection represents the maximum ramp rate to apply to VDD and VPP. The ramp rates can be configured by using the Libero software.

The SERDES\_VDD pins are shorted to VDD on silicon die; therefore, Microchip recommends using the same regulator to power up the VDD, SERDES\_VDD and SERDES\_VDDAIO pins. These three voltage supplies must be powered at the same voltage and must be ramped up and ramped down at the same time.

For information about the power-up to functional time sequence, see DS0128: IGLOO2 and SmartFusion2 Datasheet.

SmartFusion2 and IGLOO2 FPGAs do not have internal brown-out detection and protection circuitry. As described in section 1.12. Brownout Detection (BOD) of this document, VDD of the FPGA must be protected from any brown-out conditions. You must follow one of the following recommendations during the power-down of the SmartFusion2/IGLOO2 FPGAs:

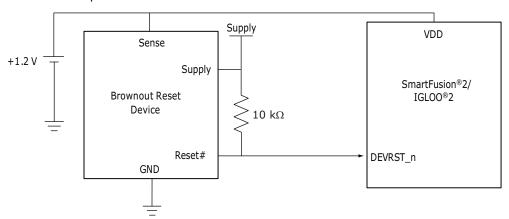

- The DEVRSTn pin of the FPGA is asserted (low) once VDD drops below the recommended operating levels.

- Or VPP rail is powered down before VDD. The VPP voltage level must drop to less than 1V before VDD can start its power-down.

If neither of the previous recommendations are followed during power-down, the FPGA device might experience malfunction that might result in partial or full erasure of user data in the eNVM.

# 1.2 I/O Glitch (Ask a Question)

Glitches were observed in SmartFusion2/IGOOL2 devices during power-up and power-down cases in different scenarios. The following sections describe the glitch observations.

#### 1.2.1 I/O Glitch During Power-Up (Ask a Question)

I/O Glitches can occur in some power-up sequences, and they can be ignored if good design practices are used.

To mitigate the I/O glitch:

- 1. Use any one of the following power-up sequence:

- a. Ensure VDD/VDDIOx powers-up before VPP (VDD/VDDIOx  $\rightarrow$  VPP). During this time, DEVRST\_N should also be de-asserted along with VPP.

- b. Assert DEVRST\_N (Keep signal Low) until all the power rails are up. Only after all power rails are up de-assert DEVRST\_N.

- 2. If power sequencing is not possible, add a 10  $K\Omega$  resistor to ground on all critical signal outputs like clocks and resets.

#### 1.2.2 I/O Glitch During Power-Down (Ask a Question)

I/O glitches can occur in some power-down sequences, and they can be ignored if good design practices are used. If the glitch on the I/Os during power-down of the FPGA cannot be ignored, the following might be used to mitigate the I/O glitch:

- 1. Add a 1 K $\Omega$  resistor to ground on all critical signal outputs such as clocks and resets and other glitch sensitive I/Os.

- 2. If possible, place the device in F\*F mode prior to power-down.

#### 1.2.3 I/O Glitch in a Blank Device (Ask a Question)

I/O glitch was observed on bank 2 of a blank device before programming. On a blank device, the I/Os are placed in the Flash\*Freeze state (tristate with weak pull-ups). When the programming starts, the I/Os transition to the boundary scan mode. On I/O bank 2, there is a race condition between exiting the Flash\*Freeze mode and the entering boundary scan mode. During this transition, the outputs on bank 2 briefly drive high until the boundary scan mode is enabled. This transition results in an I/O glitch.

To prevent this glitch, use the JTAG command to adjust the I/O drive strength to zero before programming starts.

#### 1.2.3.1 Application Impact Due to Glitch (Ask a Question)

**Application Impact:** There is no reliability impact because the duration of the I/O glitch does not exceed the datasheet overshoot specifications. The glitch amplitude tracks the VDDI bank voltage and rises slightly above the VDDI. For example, at 3.3V of VDDI, the glitch rises above 3.3V by approximately 0.3V for 5 ns. The glitch amplitude is directly proportional to the VDDI value.

**Resolution:** Regenerate the bitstream using Libero v11.8 SP1.

#### 1.2.4 I/O Glitch at Auto-Update During POR (Ask a Question)

I/O glitches are observed during POR with designs where the auto-update option is enabled. As the device powers up along with the DEVRSTb which is then in the state of being de-asserted, the I/O Glitch occurs at the beginning and end of the auto-update process.

The glitch is observed only on BANK 0, 1, and 2 of M2S005, M2S010, and M2S025 devices. The glitch is independent of the type of packages being used. This glitch is only in positive pulse (0 to 1 and then back to 0), therefore, only signals that are at logic low state will observe this glitch. The width of the glitch pulse is measured to be less than 10 ns.

To avoid this glitch:

- Place critical signal like clocks and resets on IO BANK 4, 5, 6, and 7 across the dies M2S005, M2S010, and M2S025 devices.

- Use In-Application Programming (IAP) option instead of auto-update.

- No banks on M2S060, M2S090, M2S0150 experience any glitches.

#### 1.2.5 Power Supply Flow (Ask a Question)

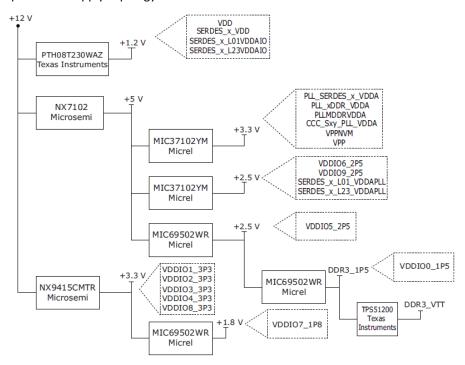

SmartFusion2/IGLOO2 FPGA devices require multiple power supplies. The following figure shows a topology for generating the required power supplies from a single 12V source. This example power supply topology is based on SmartFusion2 M2S050T-FG896 device with two SerDes channels (SERDES0 and SERDES1) and a DDR3 interface.

Figure 1-2. Example Power Supply Topology

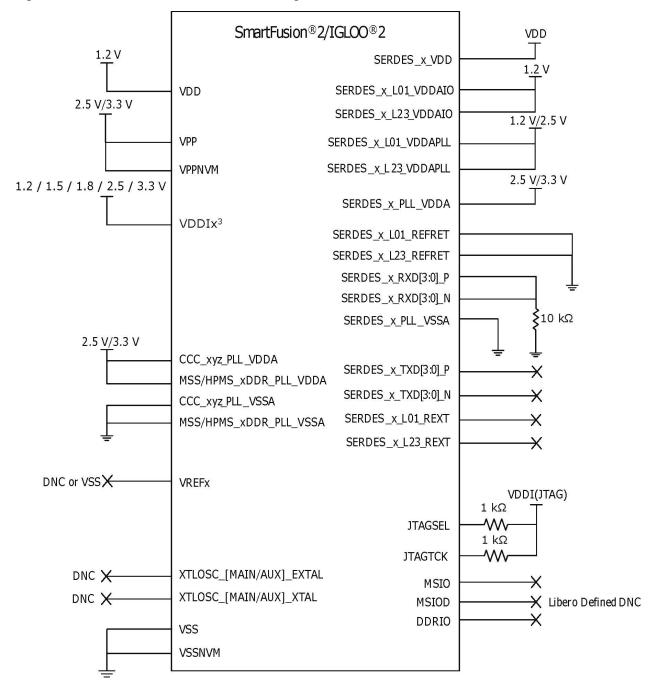

#### 1.2.6 Unused Pin Configurations (Ask a Question)

In cases where certain interfaces are not used, the associated pins need to be configured properly. For example, the pins of an unused crystal oscillator can be left floating (DNC) and must not be grounded. If a PLL is not used or bypassed, and only the divider circuitry is used, then the PLL's pins can be powered without RC filter circuitry.

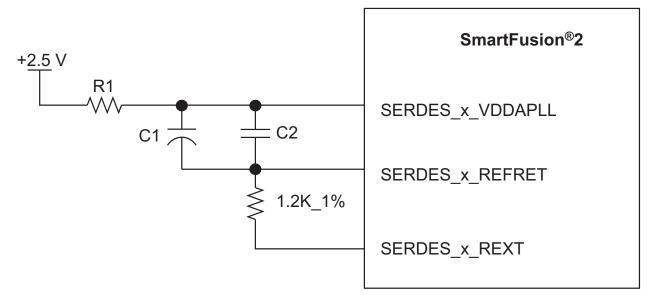

For SmartFusion2/IGLOO2 devices with multiple SerDes blocks, designers should tie off unused SerDes blocks, as shown in the following figure.

For banks configured as LPDDR or single-ended I/O (and MDDR or FDDR functionalities are not being used), VREFx can be left floating (DNC) even though the corresponding bank supply is still powered.

To allow a SmartFusion2/IGLOO2 device, to exit from reset, some of the bank supplies (VDDIx) must always be powered, even if associated bank I/Os are unused (as shown in Table 1-6 and Table 1-9).

For details on bank locations for all the devices, see DS0115: SmartFusion2 Pin Descriptions Datasheet or DS0124: IGLOO2 Pin Descriptions Datasheet.

Figure 1-3. Recommendations for Unused Pin Configurations<sup>1, 2</sup>

- 1. For M2S090T(S), M2GL090T(S), M2S150T(S), and M2GL150T(S) devices, the VPP and VPPNVM must be connected to a 3.3V supply.

- 2. SERDES\_RXD pin connections are changed to VSS through a 10 k $\Omega$  resistor to reduce the latch-up risk. This change does not affect the old board design functionality.

- 3. There are some exceptions. For recommendations on unused VDDI supplies, see the following tables. The SmartFusion2/IGLOO2 devices have multiple bank supplies. In cases where specific banks are not used, connect them as listed in the following tables. If there is no recommendation provided for a device-bank supply combination, it means that the bank is not pinned out.

Table 1-4. Recommendation for Unused Bank Supplies for FC1152, FG896, FG676, FCS536, and FCV484 Packages<sup>1</sup>

| Bank Supply        | FC1152                                         | FG896                                       | FG676                    |                          | FCS536                                         | FCV484                |  |  |

|--------------------|------------------------------------------------|---------------------------------------------|--------------------------|--------------------------|------------------------------------------------|-----------------------|--|--|

| Names <sup>2</sup> | M2S150T/                                       | M2S050T/                                    | M2S090T/                 | M2S060T/                 | M2S150T/                                       | M2S150T/              |  |  |

|                    | M2GL050T                                       | M2GL050T                                    | M2GL090T                 | M2GL060T                 | M2GL150T                                       | M2GL150               |  |  |

| VDDI0              | _                                              | Connect to VSS throu                        | gh a 10 kΩ resistor      |                          | _                                              | _                     |  |  |

| VDDI1              | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI1                    | Connect to VSS th        | or.                      |                                                |                       |  |  |

| VDDI2              | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI2                    | Must connect to<br>VDDI2 | Must connect to<br>VDDI2 | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| VDDI3              | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI3                    | Must connect to VDDI3    | Must connect to<br>VDDI3 | Connect to VSS throresistor                    | ough a 10 kΩ          |  |  |

| VDDI4              | Connect to VSS thro                            | ough a 10 kΩ resistor                       | _                        | Must connect to VDDI4    | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| VDDI5              | Connect to VSS thro                            | ect to VSS through a 10 k $\Omega$ resistor |                          |                          |                                                |                       |  |  |

| VDDI6              | Must connect to VDDI6                          | Connect to VSS throu                        | gh a 10 kΩ resistor      | Must connect to VDDI6    | Must connect to VDDI6                          |                       |  |  |

| VDDI7              | Must connect to VDDI7                          | Connect to VSS throu                        | gh a 10 kΩ resistor      |                          | Must connect to VDDI7                          | Must connect to VDDI7 |  |  |

| VDDI8              | Connect to VSS thro                            | ough a 10 kΩ resistor                       |                          |                          |                                                |                       |  |  |

| VDDI9              | Connect to VSS thro                            | ough a 10 kΩ resistor                       | _                        | Connect to VSS thro      | ough a 10 kΩ resistor                          |                       |  |  |

| VDDI10             | Connect to VSS through a 10 $k\Omega$ resistor | _                                           | _                        | _                        | Connect to VSS throresistor                    | ough a 10 kΩ          |  |  |

| VDDI11             | Connect to VSS through a 10 $k\Omega$ resistor | _                                           | _                        | _                        | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| VDDI12             | Connect to VSS through a 10 $k\Omega$ resistor | _                                           | _                        | _                        | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| VDDI13             | Connect to VSS through a 10 $k\Omega$ resistor | _                                           | _                        | _                        | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| VDDI14             | Connect to VSS through a 10 $k\Omega$ resistor | _                                           | _                        | _                        | Connect to VSS through a 10 $k\Omega$ resistor |                       |  |  |

| continued          | continued                                      |          |          |          |                                                        |          |  |  |  |  |

|--------------------|------------------------------------------------|----------|----------|----------|--------------------------------------------------------|----------|--|--|--|--|

| Bank Supply        | FC1152                                         | FG896    | FG676    |          | FCS536                                                 | FCV484   |  |  |  |  |

| Names <sup>2</sup> | M2S150T/                                       | M2S050T/ | M2S090T/ | M2S060T/ | M2S150T/                                               | M2S150T/ |  |  |  |  |

|                    | M2GL050T                                       | M2GL050T | M2GL090T | M2GL060T | M2GL150T                                               | M2GL150  |  |  |  |  |

| VDDI15             | Connect to VSS through a 10 $k\Omega$ resistor | _        | _        | _        | Connect to VSS through a $10 \text{ k}\Omega$ resistor | _        |  |  |  |  |

| VDDI16             | Connect to VSS through a 10 $k\Omega$ resistor | _        | _        | _        | Connect to VSS through a 10 $k\Omega$ resistor         |          |  |  |  |  |

| VDDI17             | Connect to VSS through a 10 $k\Omega$ resistor | _        | _        | _        | Connect to VSS through a 10 $k\Omega$ resistor         |          |  |  |  |  |

| VDDI18             | Connect to VSS through a 10 $k\Omega$ resistor | _        | _        | _        | Connect to VSS through a $10 \text{ k}\Omega$ resistor | _        |  |  |  |  |

- 1. The unused VDDI# pins must be connected to VSS through a 10 k $\Omega$  resistor. The VDDI# pins can be grouped and connected to one 10 k $\Omega$  resistor or a 10 k $\Omega$  resistor can be used for each VDDI# bank, it completely depends on the board layout. In the earlier version of the document, the unused VDDI# pins were recommended to be configured as DNC, and this cannot create functionality issue. Microchip recommends connecting to Ground through a 10 k $\Omega$  resistor to improve the board reliability.

- 2. These I/O bank supplies are mandatory power supplies and must be powered up, even if associated bank I/Os are in unused condition.

**Table 1-5.** Recommendation for Unused Bank Supplies for FG484 Package<sup>1</sup>

| Bank Supply        | FG484                                          |                                                |                                                |                                                |                                                |                                                        |  |

|--------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|--------------------------------------------------------|--|

| Names <sup>2</sup> | M2S090T/                                       | M2S060T/                                       | M2S050T/                                       | M2S025T/                                       | M2S010T/                                       | M2S005/                                                |  |

|                    | M2GL090T                                       | M2GL060T                                       | M2GL050T                                       | M2GL025T                                       | M2GL010T                                       | M2GL005                                                |  |

| VDDI0              | _                                              | _                                              | Connect to VSS th                              | rough a 10 kΩ resist                           | or                                             |                                                        |  |

| VDDI1              | Connect to VSS thre                            | ough a 10 kΩ resistor                          | Must connect to<br>VDDI1                       | Must connect to VDDI1                          | Must connect to VDDI1                          | Must connect to VDDI1                                  |  |

| VDDI2              | Must connect to VDDI2                          | Must connect to VDDI2                          | _                                              | Must connect to VDDI2                          | Must connect to VDDI2                          | Must connect to VDDI2                                  |  |

| VDDI3              | Must connect to VDDI3                          | _                                              | Must connect to VDDI3                          | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to VDDI3                          | Connect to VSS through a $10 \text{ k}\Omega$ resistor |  |

| VDDI4              | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI4                       | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI4                       | Connect to VSS through a 10 $k\Omega$ resistor | Must connect to<br>VDDI4                               |  |

| VDDI5              | Connect to VSS thro                            | ough a 10 kΩ resistor                          |                                                |                                                |                                                |                                                        |  |

| VDDI6              | Connect to VSS thre                            | Connect to VSS through a 10 $k\Omega$ resistor |                                                |                                                |                                                |                                                        |  |

| VDDI7              | Connect to VSS through a 10 kΩ resistor        |                                                |                                                |                                                |                                                |                                                        |  |

| VDDI8              | Connect to VSS thro                            | ough a 10 kΩ resistor                          |                                                | _                                              | _                                              | _                                                      |  |

| VDDI9              | _                                              | Connect to VSS through a 10 $k\Omega$ resistor | _                                              | _                                              | _                                              | _                                                      |  |

- 1. The unused VDDI# pins must be connected to VSS through a 10 k $\Omega$  resistor. The VDDI# pins can be grouped and connected to one 10 k $\Omega$  resistor or a 10 k $\Omega$  resistor can be used for each VDDI# bank, it completely depends on the board layout. In the earlier version of the document, the unused VDDI# pins were recommended to be configured as DNC, and this cannot create functionality issue. Microchip recommends connecting to Ground through a 10 k $\Omega$  resistor to improve the board reliability.

- 2. These I/O bank supplies are mandatory power supplies and must be powered up, even if associated bank I/Os are in unused condition.

Table 1-6. Recommendation for Unused Bank Supplies for VF400 and FCS325 Packages<sup>1</sup>

| Bank                         | VF400                                            |                                   |                                                |                             |                             |                                                | FCS325                                         |                                                  |                                                  |

|------------------------------|--------------------------------------------------|-----------------------------------|------------------------------------------------|-----------------------------|-----------------------------|------------------------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Supply<br>Names <sup>2</sup> | M2S060T/                                         | M2S050T/                          | M2S025T/                                       | M2S010T/                    | M2S005/                     | M2S090T/                                       | M2S060T/                                       | M2S050T/                                         | M2S025T/                                         |

|                              | M2GL060T                                         | M2GL050T                          | M2GL025T                                       | M2GL010T                    | M2GL005                     | M2GL090T                                       | M2GL060T                                       | M2GL050T                                         | M2GL025T                                         |

| VDDI0                        | _                                                | Connect to V                      | SS through a 1                                 | 0 kΩ resistor               | •                           | _                                              | _                                              | Connect to VS<br>10 kΩ resisto                   | •                                                |

| VDDI1                        | Connect to<br>VSS through<br>a 10 kΩ<br>resistor | Must<br>connect to<br>VDDI1       | Must<br>connect to<br>VDDI1                    | Must<br>connect to<br>VDDI1 | Must<br>connect to<br>VDDI1 | Connect to V<br>10 kΩ resisto                  |                                                | Must<br>connect to<br>VDDI1                      | Must<br>connect to<br>VDDI1                      |

| VDDI2                        | Must<br>connect to<br>VDDI2                      | _                                 | Must<br>connect to<br>VDDI2                    | Must<br>connect to<br>VDDI2 | Must<br>connect to<br>VDDI2 | Must<br>connect to<br>VDDI2                    | Must<br>connect to<br>VDDI2                    | Must<br>connect to<br>VDDI2                      | _                                                |

| VDDI3                        | _                                                | Must<br>connect to<br>VDDI3       | Connect to VSS through a 10 $k\Omega$ resistor |                             |                             | Must<br>connect to<br>VDDI3                    | Must<br>connect to<br>VDDI3                    | Must<br>connect to<br>VDDI3                      | Connect to<br>VSS through<br>a 10 kΩ<br>resistor |

| VDDI4                        | Must<br>connect to<br>VDDI4                      | Connect to V                      | ct to VSS through a 10 kΩ resistor             |                             |                             | Connect to VSS through a 10 $k\Omega$ resistor | Must<br>connect to<br>VDDI4                    | Connect to<br>VSS through<br>a 10 kΩ<br>resistor | Must<br>connect to<br>VDDI4                      |

| VDDI5                        | Connect to V                                     | SS through a 1                    | 0 kΩ resistor                                  |                             |                             |                                                |                                                |                                                  |                                                  |

| VDDI6                        | Connect to VSS through a 10 $k\Omega$ resistor   |                                   |                                                |                             |                             |                                                |                                                |                                                  |                                                  |

| VDDI7                        | Connect to V                                     | t to VSS through a 10 kΩ resistor |                                                |                             |                             |                                                | Connect to VSS through a 10 $k\Omega$ resistor |                                                  |                                                  |

| VDDI8                        | Connect to V:<br>10 kΩ resisto                   | •                                 | _                                              | _                           | _                           | Connect to V                                   | SS through a 1                                 | 0 kΩ resistor                                    |                                                  |

| VDDI9                        | Connect to<br>VSS through<br>a 10 kΩ<br>resistor | _                                 | _                                              | -                           | -                           | -                                              | Connect to VSS through a 10 $k\Omega$ resistor | _                                                | _                                                |

#### Important:

- 1. The unused VDDI# pins must be connected to VSS through a 10 k $\Omega$  resistor. The VDDI# pins can be grouped and connected to one 10 k $\Omega$  resistor or a 10 k $\Omega$  resistor can be used for each VDDI# bank, it completely depends on the board layout. In the earlier version of the document, the unused VDDI# pins were recommended to be configured as DNC, and this cannot create functionality issue. Microchip recommends connecting to Ground through a 10 k $\Omega$  resistor to improve the board reliability.

- 2. These I/O bank supplies are mandatory power supplies and must be powered up, even if associated bank I/Os are in unused condition.

Bank Supply Names VF256 M2S025T/ M2S010T/ M2S005S/ M2S010S/ M2S005S/ M2GL025T M2GL010T M2GL005S M2GL010S M2GL005S VDDI0 Connect to VSS through a 10 kΩ resistor VDDI1 Must connect to VDDI1 Must connect to Must connect to VDDI1 VDDI1 VDDI2 Must connect to Must connect to VDDI2 Must connect to Must connect to Must connect to VDDI2 VDDI2 VDDI2 VDDI2 VDDI3 Connect to VSS through a 10  $k\Omega$  resistor VDDI4 Must connect to Must connect to VDDI4 Must connect to Must connect to Must connect to VDDI4 VDDI4 VDDI4 VDDI4 VDDI5 Connect to VSS through a 10 k $\Omega$  resistor Connect to VSS through a 10 kΩ resistor VDDI6 Connect to VSS through a 10 kΩ resistor VDDI7 Connect to VSS through a 10  $k\Omega$  resistor Connect to VSS through a 10  $k\Omega$ resistor

**Table 1-7.** Recommendation for Unused Bank Supplies for VF256 and TQ144 Packages<sup>1</sup>

- 1. The unused VDDI# pins must be connected to VSS through a 10 k $\Omega$  resistor. The VDDI# pins can be grouped and connected to one 10 k $\Omega$  resistor or a 10 k $\Omega$  resistor can be used for each VDDI# bank, it completely depends on the board layout. In the earlier version of the document, the unused VDDI# pins were recommended to be configured as DNC, and this cannot create functionality issue. Microchip recommends connecting to Ground through a 10 k $\Omega$  resistor to improve the board reliability.

- 2. These I/O bank supplies are mandatory power supplies and must be powered up, even if associated bank I/Os are in unused condition.

# 1.3 Limiting VDD Surge Current (Ask a Question)

After device power-up, certain user-initiated functions can result in a surge current on VDD. This section describes how to minimize this surge current in SmartFusion2/IGLOO2 devices. Minimizing this surge current ensures that VDD voltage is maintained within the recommended operating range. This additional surge current does not occur during device power-up and has no effect on device reliability. If VDD voltage drops below the minimum recommended operating voltage, the FPGA may experience brownout. For more information about brownout and brownout prevention, see 1.12. Brownout Detection (BOD).

#### 1.3.1 Device Reset Induced VDD Surge Current (Ask a Question)

After device power-up, if the application asserts the DEVRST\_N pin, a surge current on VDD may be observed. This section describes how to minimize additional surge current during the device reset operation. This additional surge current does not occur during device power-up; it is applicable only when DEVRST\_N is asserted.

SmartFusion 2/IGLOO 2 device reset can be activated either directly through an external DEVRST\_N pin or indirectly through the tamper macro IP. When the device reset is asserted, the system controller immediately puts the FPGA core in the inactive state, which induces a temporary current demand on VDD. This surge current is for a very short duration and is normally handled by bulk decoupling capacitors on the power plane in a typical system. In cases where Microchip-

recommended board design guidelines cannot be implemented for decoupling capacitors for VDD (due to limited board spacing or other reasons), higher-than-expected surge current may occur during device reset.

The following table provides characterized surge current data for VDD during DEVRST\_N assertion. This data represents the worst-case condition with no decoupling capacitors on the board.

Table 1-8. Surge Current on VDD during DEVRST\_N Assertion (No Decoupling Capacitors on Board)

| Device         | Width of Surge at 50% of Pulse (μS) | Surge Current | on VDD           |                  | Units |

|----------------|-------------------------------------|---------------|------------------|------------------|-------|

|                |                                     | 0 °C to 85 °C | –40 °C to 100 °C | –55 °C to 125 °C |       |

| M2S005/M2GL005 | 2                                   | 0.5           | 0.6              | 0.6              | Α     |

| M2S010/M2GL010 | 3                                   | 0.9           | 0.9              | 0.9              | Α     |

| M2S025/M2GL025 | 6                                   | 1.7           | 1.7              | 1.7              | Α     |

| M2S050/M2GL050 | 12                                  | 3.2           | 3.2              | 3.2              | Α     |

| M2S060/M2GL060 | 12                                  | 3.2           | 3.2              | 3.2              | Α     |

| M2S090/M2GL090 | 22                                  | 4.4           | 4.6              | 4.6              | Α     |

| M2S150/M2GL150 | 42                                  | 7.0           | 7.3              | 7.3              | Α     |

The surge current data in the preceding table does not represent a typical system. To illustrate this, surge current during device reset was measured at room temperature separately for the M2S090 security evaluation kit and the M2S150 advanced development kit. These kits have decoupling capacitors according to the Microchip recommended board design guidelines. The following table lists the surge currents observed on the M2S090 security evaluation kit and the M2S150 advanced development kit. The surge current values were found to be within acceptable limits.

Table 1-9. M2S090 and M2S150 Surge Current During DEVRST\_N Assertion (With Decoupling Capacitors on Board)

| Kit                             | Width of Surge at 50% of Pulse | Surge Current |

|---------------------------------|--------------------------------|---------------|

| M2S090 Security Evaluation Kit  | 5 μs                           | 150 mA        |

| M2S150 Advanced Development Kit | 40 μs                          | 1.5A          |

#### Note:

1. The amount of bulk capacitance placed for VDD was 1–100  $\mu$ F, 3–220  $\mu$ F, and 1–330  $\mu$ F.

#### 1.3.2 System Controller Suspend Mode Exit Induced VDD Surge Current (Ask a Question)

SmartFusion2 and IGLOO2 devices support system controller suspend mode for safety critical applications. Customers using this feature can force the system controller to exit suspend mode to support system controller features including device reprogramming. Exiting suspend mode is accomplished by driving the JTAG TRSTn pin high. Exiting the device from system controller suspend mode, after device is fully operational, temporarily disables the FPGA core which results in a current surge on VDD. This surge current is for a very short duration and is normally handled by bulk decoupling capacitors on the VDD power plane in a typical system. The magnitude of this surge current is similar to the surge resulting from a DEVRST\_N assertion (Table 1-8).

The surge current can be kept within acceptable limits by adhering to VDD decoupling capacitors requirements per Microchip-recommended board design guidelines as shown in Table 1-9.

#### 1.3.3 Digest Check Inducted VDD Surge Current (Ask a Question)

The digest check system service performs on-chip NVM data integrity check on SmartFusion2 devices. The use of system services by digest check may cause additional surge current on VDD. For more information on digest check service, see the UG0450: SmartFusion2 and IGLOO2 System Controller User Guide

The following table provides surge current data recorded for VDD when system services were being used by the digest check service. To limit surge current during digest check, follow the Microchip recommended board design guidelines.

Table 1-10. Surge Current on VDD During Digest Check Using System Services (No Decoupling Capacitors on Board)

| Device         | Width of Surge at | Surge Current on V | Surge Current on VDD |                           |   |  |

|----------------|-------------------|--------------------|----------------------|---------------------------|---|--|

|                | 50% of Pulse (μS) | 0 °C to 85 °C      | -40 °C to 100 °C     | -55 °C to 125 °C<br>Units |   |  |

| M2S005/M2GL005 | 12                | 0.2                | 0.2                  | 0.2                       | Α |  |

| M2S010/M2GL010 | 12                | 0.5                | 0.5                  | 0.5                       | Α |  |

| M2S025/M2GL025 | 13                | 0.6                | 0.6                  | 0.6                       | Α |  |

| M2S050/M2GL050 | 13                | 0.9                | 0.9                  | 0.9                       | Α |  |

| M2S060/M2GL060 | 13                | 0.9                | 0.9                  | 0.9                       | Α |  |

| M2S090/M2GL090 | 20                | 1.0                | 1.0                  | 1.0                       | Α |  |

| M2S150/M2GL150 | 26                | 1.0                | 1.0                  | 1.0                       | Α |  |

# 1.4 Clocks (Ask a Question)

SmartFusion2 devices have two on-chip RC oscillators and up to two crystal oscillators for generating clocks for the on-chip resources and logic in the FPGA fabric, as listed in the following table.

#### RC Oscillators:

- 1 MHz RC oscillator

- 50 MHz RC oscillator

#### Crystal Oscillators:

- Main crystal oscillator

- Auxiliary (RTC) crystal oscillator

All IGLOO2 devices and the M2S050 SmartFusion2 device have a main crystal oscillator. They do not have an auxiliary (RTC) crystal oscillator.

Table 1-11. Clock Circuit

| Resource                   |                        | SmartFus | ion2 SoC I | Part Numb | er     |        | IGLOO2 Pa | art Number |         |         |         |

|----------------------------|------------------------|----------|------------|-----------|--------|--------|-----------|------------|---------|---------|---------|

|                            |                        | M2S005   | M2S010     | M2S025    | M2S050 | M2S150 | M2GL005   | M2GL010    | M2GL025 | M2GL050 | M2GL150 |

|                            | RC<br>Oscillators      | 2        | 2          | 2         | 2      | 2      | 2         | 2          | 2       | 2       | 2       |

| On-Chip<br>Oscillator<br>s | Crystal<br>Oscillators | 2        | 2          | 2         | 1      | 2      | 1         | 1          | 1       | 1       | 1       |

#### 1.4.1 Main Crystal Oscillator (Ask a Question)

The main crystal oscillator works with an external crystal, ceramic resonator, or a resistor-capacitor network to generate a high-precision clock in the range of 32 kHz to 20 MHz and is connected via the pins XTLOSC\_[MAIN/AUX]\_EXTAL and XTLOSC\_[MAIN/AUX]\_XTAL.

The following table lists the output frequency range of the main crystal oscillator with different possible sources.

Table 1-12. Crystal Oscillator Output Frequency Range

| Source            | Output Frequency Range |

|-------------------|------------------------|

| Crystal           | 32 kHz to 20 MHz       |

| Ceramic Resonator | 500 kHz to 4 MHz       |

| R C Circuit       | 32 kHz to 4 MHz        |

The main crystal oscillator is operated in medium gain mode when a ceramic resonator is connected between the XTLOSC\_[MAIN/AUX]\_EXTAL and XTLOSC\_[MAIN/AUX]\_XTAL pins.

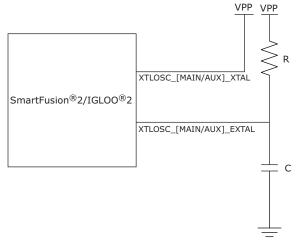

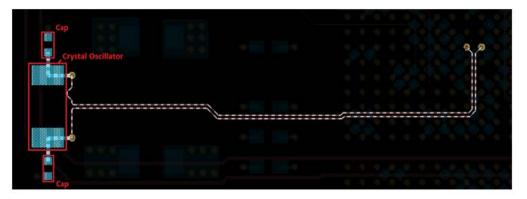

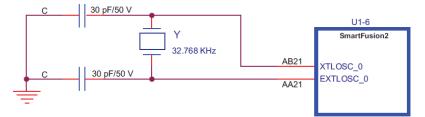

When a crystal is used, the load capacitance is determined by the external capacitors C1 and C2, internal capacitance, and stray capacitance (CS), as shown in the following figure.

Figure 1-4. Crystal Oscillator

The oscillator and the load capacitance should be used as per the recommendation of the manufacturer.

Table 1-13. Suggested Crystal Oscillator

| CRYSTAL 32.768 KHZ 12.5 pF SMD CITIZEN CMS19-32.768KEZF-UT | CRYSTAL 32.768 kHz 12.5 pF SMD | Citizen |  |

|------------------------------------------------------------|--------------------------------|---------|--|

|------------------------------------------------------------|--------------------------------|---------|--|

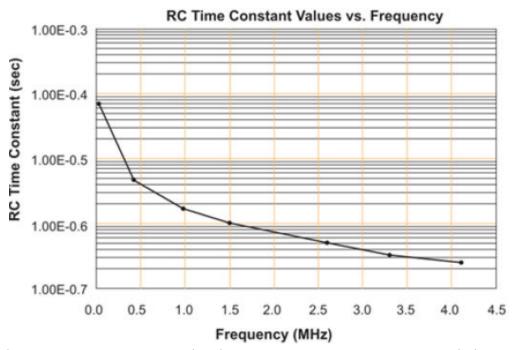

The frequency generated by an RC network is determined by the RC time constant of the selected components, as shown in the following figure.

Figure 1-5. RC Time Constant

The R and C components are connected to the XTLOSC\_[MAIN/AUX]\_EXTAL pin, with the XTLOSC\_[MAIN/AUX]\_XTAL pin connected to the power pin VPP, as shown in the following figure.

The operating mode of the main crystal oscillator is configured by the oscillator's macro available in Libero SoC.

#### 1.4.2 Auxiliary (RTC) Crystal Oscillator (Ask a Question)

The SmartFusion 2 devices, except M2S050, have an auxiliary crystal oscillator dedicated to real-time clocking as an alternative source for the 32 kHz clock. The RTC can take its 32 kHz clock source from the auxiliary crystal oscillator when the main crystal oscillator is being used.

Similar to the main crystal oscillator, the auxiliary crystal oscillator can work with an external crystal, ceramic resonator, or an RC circuit to generate a high-precision clock in the range of 32 kHz to 20 MHz. There are two I/O pads for connecting the external frequency source to the auxiliary crystal oscillator: XTLOSC\_AUX\_EXTAL and XTLOSC\_AUX\_XTAL. The output frequency range, operating modes, and characteristics for the auxiliary crystal oscillator are the same as those for the main crystal oscillator.

For detailed information, see UG0449: SmartFusion2 and IGLOO2 Clocking Resources User Guide.

Important: Auxiliary (RTC) crystal oscillator is not available in the IGLOO 2 device.

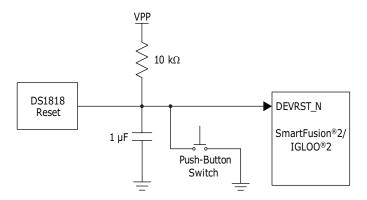

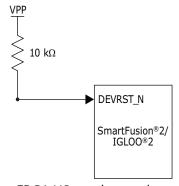

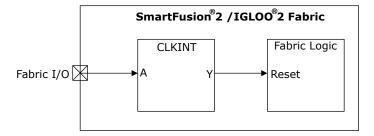

#### 1.5 Reset Circuit (Ask a Question)